J. Korean Inst. Electr. Electron. Mater. Eng. Vol. 37, No. 6, pp. 675-679 November 2024 doi: https://doi.org/10.4313/JKEM.2024.37.6.15 ISSN 1226-7945(Print), 2288-3258(Online)

# SiC 기반 MPS 다이오드 P\* 영역 최적화: BFOM 향상과 Snap-Back 현상 완화를 위한 연구

박승현, 이태희, 박세림, 윤주은, 이건희, 전지환, 오종민, 신원호, 구상모⑩

광운대학교 전자재료공학과

Optimization of the P<sup>+</sup> Region in SiC-Based MPS Diodes: Enhancing BFOM and Alleviating Snap-Back Phenomenon

Seung-Hyun Park, Tae-Hee Lee, Se-Rim Park, Ju-Eun Yun, Geon-Hee Lee, Ji-Hwan Jeon, Jong-Min Oh, Weon Ho Shin, and Sang-Mo Koo

Department of Electric Materials Engineering, Kwangwoon University, Seoul 01897, Korea

(Received June 13, 2024; Revised July 8, 2024; Accepted July 10, 2024)

Abstract: Wide bandgap (WBG) devices, especially SiC, are gaining traction as materials for high-power EV conversion devices due to their superior efficiency and switching capabilities compared to Si-based power devices. SiC allows for high power, high temperature, and high frequency applications because of its outstanding thermal conductivity, saturation velocity, and dielectric breakdown field. SiC-based MPS diodes combine the advantages of SiC-based SBDs and PiN diodes, allowing high-frequency switching operation with low leakage currents under high voltage conditions. However, MPS diodes exhibit snapback phenomena influenced by the P<sup>+</sup> region's size, necessitating optimization. A TCAD simulation studied the impact of the P<sup>+</sup> region's depth and width on MPS diode performance. Increasing the P+ width raised the On-specific resistance (Ron,sp) and lowered the maximum voltage during snapback (V<sub>snap</sub>). Increasing the depth decreased both Breakdown voltage (BV) and V<sub>snap</sub>. A trade-off between the semiconductor performance index BFOM and V<sub>snap</sub> was identified, leading to optimized dimensions. The optimized MPS diode shows a low V<sub>snap</sub> of about 3.89 V and a high BFOM of 1.72 GW·cm<sup>2</sup>, highlighting its potential as a next-generation high-performance power conversion device.

Keywords: SiC, MPS diode, Snapback, BFOM, PiN diode, Schottky barrier diode, TCAD

치 대비 더 좋은 효율을 유지하면서 매우 높은 스위칭 주파 수를 달성할 수 있으며 WBG 장치 기술이 발전하면서 생산 량 증가에 따른 비용 절감의 효과를 가져와 높은 전력 밀도 와 효율성을 가진 EV용 고전력 변환 장치의 재료로 주목 받고 있다 [1,2]. 4H-SiC silicon carbide (SiC)는 약 3.2

### ☑ Sang-Mo Koo; smkoo@kw.ac.kr

Copyright ©2024 KIEEME. All rights reserved. This is an Open-Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License (http://creativecommons.org/licenses/by-nc/3.0) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

Wide bandgap (WBG) 장치는 기존의 Si 기반 전력 장 eV의 bandgap을 가지는 WBG 물질로 Si 대비 우수한 열 전도성(~5 W/cm·K), 포화 속도(~2.7×10<sup>17</sup> cm/s) 그리고 약 10배 큰 절연 파괴 전계(~ 3 MV/cm)를 가져 고주파, 고전압, 고전류, 고온 응용을 가능하게 한다 [3].

> SiC 기반 diode는 EV용 OBC (on-board charger) 및 전력 컨버터나 정류기에 활용된다 [4,5]. SBD (Schottky barrier diode)는 Schottky contact을 형성하여 낮은 on 상태 손실을 가지면서 고주파수에서도 작동할 수 있다. 하 지만 누설 전류가 높고 항복 전압이 낮은 단점이 있다. PiN diode는 낮은 누설 전류로 높은 전압 조건에서 작동이 가

능하지만, 스위칭 시 역회복 시간이 길다는 단점이 있다. 이와는 달리 Schottky 영역과 p-i-n 구조를 병렬로 가지 는 merged p-i-n Schottky diode (MPS)는 ON 상태에 서는 SBD로, OFF 상태에서는 p-i-n diode로 작동하며 두 구조의 장점을 모두 가진다 [6,7]. 하지만 MPS diode는 PN junction의 built in potential 이상의 전압이 인가될 때, 단극 작동에서 양극 작동으로 변환되는데 이때 전압 spike와 같은 비이상적인 전류 특성을 동반하는 snapback 현상이 발생할 수 있는 문제가 존재한다 [8]. Snapback 현 상은 병렬 연결된 소자의 비이상적 전류 특성과 함께 열적 파괴를 유발할 수 있어 소자의 안정성을 확보하기 위해서 최소화되어야 한다 [9]. 특히 MPS diode에서 PN 접합의 영역과 Schottky 영역의 비율이 소자의 snapback 현상 과 전기적 특성에 영향을 미치기 때문에 MPS diode의 성 능 향상 및 snapback 현상 완화를 위해 P<sup>+</sup> 영역에 대한 최 적화가 요구된다 [8,10].

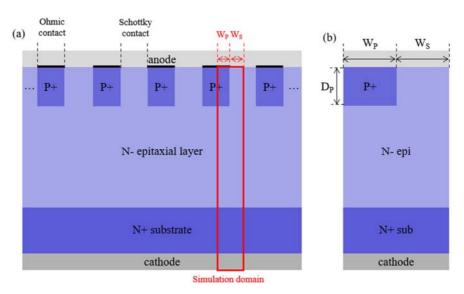

본 연구에서는 TCAD simulation을 활용하여 기존의 SiC SBD에 P<sup>+</sup> 영역을 추가해 단극/양극 동작이 가능한 SiC MPS diode를 설계했으며, MPS diode P<sup>+</sup> 영역의 너비와 깊이 변화에 따른 snapback 현상과 전기적 특성 연구를 하고자 한다. 그림 1(a)는 SiC MPS diode의 구조를 보여주며, (b)는 실제 연구에서 다룬 시뮬레이션 영역을 보여준다. 그림 1(a)를 보면, P<sup>+</sup> 영역의 추가로 MPS diode는 Ohmic contact을 형성하는 p-i-n 영역과 Schottky contact을 형성하는 Schottky 영역으로 구성된다. 그림 1(b) simulation domain에서 소자의 anode와 Ohmic contact을 이루는 P<sup>+</sup> 영역의 너비를 W<sub>P</sub>, 높이를 D<sub>P</sub>라고

지칭했다. MPS diode에서 PN 접합 영역과 Schottky 영역의 비율에 따른 전기적 특성과 snapback 현상의 변화를 확인하기 위해  $W_P$ 를  $1.0\sim3.0~\mu m$ ,  $D_P$ 를  $0.5\sim1.0~\mu m$ 으로 시뮬레이션을 진행했다. 설계된 MPS diode의 성능 및 안정성을 평가하기 위해서  $W_P$ 와  $D_P$ 에 따른  $R_{on.sp}$ , breakdown voltage (BV), Baliga's figure of merits (BFOM)과 snap-back 현상이 발생했을 때의 최대 전압 값( $V_{snap}$ )을 비교 분석했다.

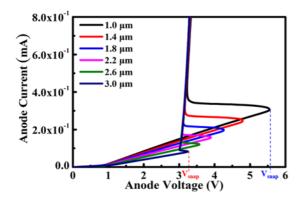

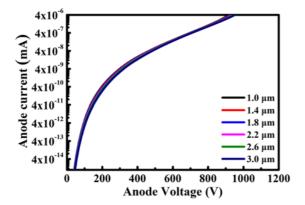

그림 2와 3은 MPS diode의 Wp를 1.0 µm부터 3.0 µm 까지 0.4 μm씩 증가시키고, Dp는 0.5 μm로 고정했을 때, 소자의 순방향과 역방향 바이어스에서의 I-V curve를 나 타낸다. MPS diode의 Wp가 증가할수록 Vsnap이 감소했으 며,  $W_P$ 가 3.0  $\mu m$  가장 길 때,  $V_{snap}$ 은 약 3.27 V로 가장 작 았다. 이는  $W_P$ 가 증가할수록 PiN 영역이 증가함에 따라  $P^+$ 영역 아래로 흐르게 되는 Schottky contact에서의 전류 의 양이 줄어들면서 나타나는 결과이다. Schottky contact을 통해 흐르는 전류가 p-i-n 영역을 덜 침범하게 되면서 양극 모드로 동작 시, hole injection에 미치는 영 향이 감소한다 [8]. 따라서 p-i-n 영역과 Schottky 영역의 경계 부근에서 비교적 낮았던 hole의 농도가 증가하게 되 고, 최종적으로 경계 부근의 불균일한 전도성 변화가 완화 되어 voltage drop이 감소하게 되면서 snapback 현상이 완화된다. 또한 그림 3의 역 바이어스 I-V curve의 전류 1.0 × 10<sup>-6</sup> A에서 확인한 BV의 값은 약 1,000 V로, 소자 의 W<sub>P</sub>의 변화에 따라 크게 변화하지 않았다. 이를 통해 MPS diode의  $W_P$ 가 BV에 큰 영향을 미치지 않음을 알 수 있다.

Fig. 1. (a) Full structure of MPS diode and (b) structure of simulation domain.

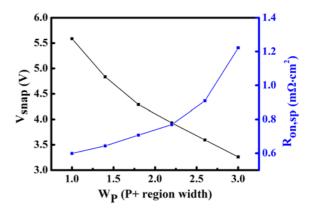

다음으로  $W_P$ 의 변화에 따른 MPS diode의  $V_{snap}$ 과  $R_{on,sp}$ 에 대한 영향을 그림 4에 나타냈다.  $W_P$ 가 증가할수록  $R_{on,sp}$ 는 증가했으며,  $W_P$ 가 3.0  $\mu$ m 가장 길 때,  $R_{on,sp}$ 는  $6^{-1}$   $10.01 \times 10^{-1}$   $10.01 \times 10^{-1}$

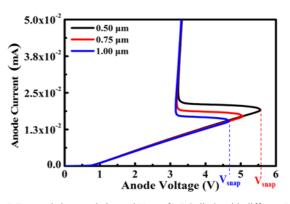

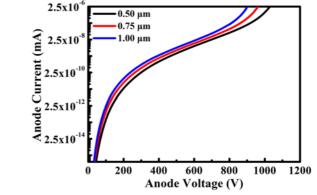

그림 5와 6은 MPS diode의  $D_p$ 를  $0.5 \mu m$ 부터  $1.0 \mu m$  까지  $0.25 \mu m$ 씩 증가시키고,  $W_P$ 는  $1.0 \mu m$ 로 고정했을 때, 소자의 순방향과 역방향 바이어스에서의 I-V curve를 나타낸다. MPS diode의  $D_P$ 가 증가할수록  $V_{snap}$ 이 감소했으며,  $D_P$ 가  $1.0 \mu m$ 로 가장 길 때,  $V_{snap}$ 은 약 4.65 V로 가장 작았다. 이는 그림 2를 통해서 확인한  $D_P$ 의 증가에 따른

$V_{snap}$ 의 감소와 같은 이유로 설명할 수 있다.  $D_P$ 의 증가로  $P^+$  영역이 N-epi층 쪽으로 깊이가 증가하면서 Schottky 영역과 PiN 영역의 경계 부근에서 Schottky contact을 통해 흐르는 전류가  $P^+$ 층 아래로 덜 침범하게 된다. 따라서

Fig. 4. Trade off relation between V<sub>snap</sub> and R<sub>on,sp</sub> with different W<sub>p</sub>.

Fig. 2. Forward characteristics and  $V_{\text{snap}}$  of MPS diode with different  $W_{\text{p}}.$

Fig. 5. Forward characteristics and  $V_{\text{snap}}$  of MPS diode with different  $D_p$ .

$\textbf{Fig. 3.} \ Reverse \ characteristics \ of \ MPS \ diode \ with \ different \ W_{p.}$

Fig. 6. Reverse characteristics of MPS diode with different D<sub>P</sub>.

경계 부근의 hole 농도가 증가하게 되고, 불균일한 전도성 변화가 완화되면서  $V_{snap}$ 이 감소하게 된다. 하지만  $D_P$ 의 변화는 simulation domain에서 Schottky 영역의 비율에는 영향을 미치지 않는다. 따라서 그림 4를 통해 알 수 있듯이, MPS diode의  $D_P$ 의 증가는  $R_{on,sp}$ 에 큰 영향을 미치지 않는다.

다음으로 그림 6에서 MPS diode의  $D_P$ 가 증가할수록 소자의 BV가 감소함을 알 수 있다. 이는  $D_P$  증가에 따라 PiN 영역에서 N-epi 영역의 넓이가 감소하기 때문이다.  $D_P$ 가 증가하면서 N-epi 영역에 형성되는 depletion 영역의 넓이가 감소하게 되고, 이에 따라 소자의 전계가 감소하면서 최종적으로 BV가 감소하게 된다 [11,12]. 그림 6에서 확인할 수 있듯이, 소자의  $D_P$ 가  $0.5~\mu$ m에서  $1.0~\mu$ m로 증가함에 따라 BV는 점점 감소했으며,  $D_P$ 가  $1.0~\mu$ m로 가장 길 때 전류  $1.0\times10^{-6}~A$ 에서 계산한 BV는 약 1,060~V로 가장 작았다.

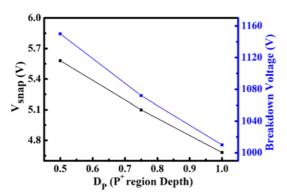

이러한  $D_P$ 의 변화에 따른 MPS diode의  $V_{snap}$ 과 BV에 대한 영향을 그림 7에 나타냈다. 이를 통해  $D_P$ 가 증가할수

Fig. 7. Trade off relation between V<sub>snap</sub> and BV with different D<sub>p</sub>.

Fig. 8. Relation between 1/BFOM and  $V_{snap}$  with different  $W_P$  and  $D_P$ .

록  $V_{snap}$ 이 감소하고, BV도 감소하여,  $V_{snap}$ 과 BV 사이의 trade-off 관계가 존재함을 확인했다.

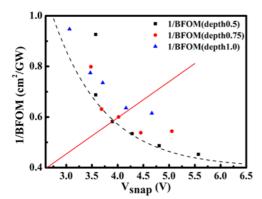

그림 4와 7을 통해 MPS diode의 W<sub>P</sub>와 D<sub>P</sub>에 따른 R<sub>on,sp</sub>, BV, V<sub>snap</sub>의 변화와 각 변수들 사이의 trade-off 관계를 파 악했다. 그림 8은 Dp가 0.5, 0.75, 1.0 μm 일 때, 각 Dp에 대한 Wp를 1.0, 1.4, 1.8, 2.2, 2.6, 3.0 µm으로 설정하여 시뮬레이션하고, 이때의 각 W▷와 D▷에 따른 1/BFOM (BFOM의 역수)와 V<sub>snap</sub>을 나타낸다. 그림 8에 설정된 1/BFOM과 V<sub>snap</sub>의 범위 내에서 D<sub>P</sub>가 0.5 µm인 소자의 값 6개, D<sub>P</sub>가 0.75, 1.0 μm인 소자의 값을 각각 5개씩 나타냈 다. MPS diode의 W<sub>P</sub>와 D<sub>P</sub>에 따른 BFOM과 V<sub>snap</sub>은 trade-off 관계에 따라서 소자의 성능 및 안정성을 개선하 기 위해 1/BFOM과 V<sub>snap</sub>를 감소시켜야 한다. 따라서 그림 8의 그래프에서 좌측 하단, 즉 원점에 가까운 값일수록 BFOM 값이 높고, snapback voltage가 작은 이상적인 diode를 의미하기 때문에 그래프의 원점에서 linear 하게 빨간색 실선을 그렸다. 결론적으로 Wp와 Dp에 따른 MPS diode의 1/BFOM과 V<sub>snap</sub>의 분포를 나타내는 검은색 점선 과 빨간색 실선이 맞닿는 가장 좌측 하단의 값이 최적의 값 으로, W<sub>P</sub>가 2.2 μm, D<sub>P</sub>가 0.5 μm일 때, 1/BFOM이 약 0.53 cm<sup>2</sup>/GW, V<sub>snap</sub>이 4.28 V로 비교적 낮은 V<sub>snap</sub>을 가 지며, 높은 성능을 가진다.

최종적으로 최적화된 MPS diode의 spec은 표 1을 통해 확인할 수 있다. 본 연구는 MPS diode의  $P^+$  영역 변화에 따른 BFOM과  $V_{snap}$ 을 비교 분석함으로써 소자의  $W_p$ 와  $D_p$ 에 대해 최적화했다. 시뮬레이션을 통해  $W_p$ 와  $D_p$  변화에 따른 순방향 및 역방향 전압-전류 특성을 확인함으로써 각 파라미터에 대한 BFOM과  $V_{snap}$ 을 도출했다. 결론적으로 BFOM과  $V_{snap}$ 사이의 trade-off 관계를 파악하고, 소자의 성능 및 안정성을 개선할 수 있도록 trade-off 관계를 완화하는 조건을 찾아  $W_p$ 와  $D_p$  값을 선정했다.  $W_p$ 와  $D_p$

Table 1. Spec of optimized MPS diode.

| MPS diode                                        |                    |   |

|--------------------------------------------------|--------------------|---|

| P <sup>+</sup> width (μm)                        | 2.2                |   |

| P <sup>+</sup> depth (μm)                        | 0.5                |   |

| Epi layer doping concentration (N <sub>P</sub> ) | $1 \times 10^{16}$ |   |

| Epi layer thickness (μm)                         | 0.7                |   |

| Sub layer thickness (μm)                         | 0.7                |   |

| V <sub>snap</sub> (V)                            | 3.89               |   |

| $R_{\text{on,sp}}(m\Omega\cdot cm^2)$            | 0.77               |   |

| Breakdown voltage (V)                            | 1,150              |   |

| BFOM (GW/cm <sup>2</sup> )                       | 1.72               | • |

가 최적화된 MPS diode는  $1.72~\mathrm{GW/cm^2}$ 의 BFOM을 가지는 고성능 소자로, 약  $3.89~\mathrm{V의}$  낮은  $\mathrm{V_{snap}}$ 을 가진다. 본연구에서 개발된 MPS diode는 성능 및 안정성이 개선된 전력 반도체 기술로서 중요한 역할을 할 것으로 기대되며, 차세대 고성능 전력 변환 장치로서의 가능성을 입증했다.

#### **ORCID**

Sang-Mo Koo

https://orcid.org/0000-0002-9827-9219

## 감사의 글

This work was supported by the Korea Institute for Advancement of Technology (KIAT) (P0012451), the Korea Evaluation Institute of Industrial Technology (KEIT) (RS-2024-00401983) grant funded by the MOTIE of Korea, and the Research Grant of Kwangwoon University in 2024.

#### **REFERENCES**

- [1] S. Li, S. Lu, and C. C. Mi, *Proc. IEEE*, **109**, 985 (2021). doi: https://doi.org/10.1109/JPROC.2021.3071977

- [2] A. S. Abdelrahman, Z. Erdem, Y. Attia, and M. Z. Youssef, *Can. J. Electr. Comput. Eng.*, 41, 45 (2018). doi: https://doi.org/10.1109/CJECE.2018.2807780

- [3] X. She, A. Q. Huang, Ó. Lucía, and B. Ozpineci, *IEEE Trans. Ind. Electron.*, 64, 8193 (2017).

doi: https://doi.org/10.1109/TIE.2017.2652401

- Z. Liu, B. Li, F. C. Lee, and Q. Li, *IEEE Trans. Ind. Electron.*, 64, 9114 (2017).

doi: https://doi.org/10.1109/TIE.2017.2716873

- [5] S. Zhao, A. Kempitiya, W. T. Chou, V. Palijia, and C. Bonfiglio, IEEE Trans. Ind. Appl., 58, 2965 (2022). doi: https://doi.org/10.1109/TIA.2022.3151867

- [6] A. Wang, Y. Bai, Y. Tang, C. Li, Z. Han, J. Lu, H. Chen, X. Tian, C. Yang, J. Hao, and X. Liu, *IEEE Trans. Electron Devices*, 68, 6330 (2021). doi: https://doi.org/10.1109/TED.2021.3122403

- [7] Q. Du and X. Tao, *IEEE Trans. Electron Devices*, **67**, 4033 (2020).

- doi: https://doi.org/10.1109/TED.2020.2982684

[8] H. Niwa, J. Suda, and T. Kimoto, *IEEE Trans. Electron Devices*,

- doi: https://doi.org/10.1109/TED.2016.2636573

64, 874 (2017).

- [9] X. D. Zhang, Y. Wang, M. T. Bao, X. J. Li, J. Q. Yang, and F. Cao, *IEEE Trans. Electron Devices*, 68, 5062 (2021). doi: https://doi.org/10.1109/TED.2021.3106620

- [10] H. J. Lee, Y. H. Kang, S. W. Jung, G. H. Lee, D. W. Byun, M. C. Shin, C. H. Yang, and S. M. Koo, *J. Korean Inst. Electr. Electron. Mater. Eng.*, 35, 241 (2022). doi: https://doi.org/10.4313/JKEM.2022.35.3.5

- [11] A. Haggag and K. Hess, *IEEE Trans. Electron Devices*, 47, 1624 (2000). doi: https://doi.org/10.1109/16.853040

- [12] N. Serra, G. Giacomini, A. Piazza, C. Piemonte, A. Tarolli, and N. Zorzi, *IEEE Trans. Nucl. Sci.*, **58**, 1233 (2011). doi: https://doi.org/10.1109/TNS.2011.2123919