# 온칩 마이크로컨트롤러를 사용하는 낸드 플래시 메모리의 제조 후 어레이 동작 수정

## Post-manufacturing Array Operation Repair for NAND Flash Memories with On-Chip Microcontrollers

김 건 우\*, 조 용 호\*\*

Geonu Kim\*, Yong-Ho Cho\*\*

#### **Abstract**

This paper proposes a scheme for NAND flash memories equipped with on-chip microcontrollers and instruction ROM, that enables patching of erroneous cell array operation instructions after manufacturing. The scheme incorporates a small patch instruction RAM, where the patching instructions are fetched using a configurable Program Counter (PC) substitution mechanism. Both the patching instructions and PC substitution data are stored in a designated NAND cell area and loaded at power-up along with the electrical fuse data. As the scheme is designed to handle only a small number instruction patches, the area overhead remains minimal.

#### 요 약

본 논문에서는 온칩 마이크로컨트롤러(MCU)와 명령어(instruction) ROM을 사용하는 NAND 플래시 메모리에서 제조 이후 잘 못된 셀(cell) 어레이 구동 명령어들을 수정하는 방법을 제안한다. 이 방법은 작은 패치(patch) 명령어 RAM을 사용하며, MCU는 재구성 가능한 프로그램 카운터(PC) 대체 메커니즘을 통해 패치 명령어들을 가져와 수행한다. 패치 명령어들과 PC 대체를 위한 데 이터는 특정 낸드 셀 영역에 저장되고, 전원이 켜질 때 전기적 퓨즈(fuse) 정보와 함께 로드된다. 제안하는 방법은 소수의 명령어 패치만 지원하기 때문에 면적 증가는 무시할 수 있을 만큼 매우 작다.

Key words: NAND Flash, Microcontroller, ROM, Array Operation, Algorithm Patch

## 1. 서론

낸드 플래시 메모리는 순차적인 읽기와 쓰기 패턴을 보이는 대용량 데이터 저장 장치로, 일반적으로 랜덤 (random)한 읽기와 쓰기 동작에 대해 저지연 성능이 중 요한 다른 반도체 메모리들과 달리 처리량(throughput)

이 가장 중요한 성능 지표로 간주된다. 낸드 플래시 메모 리는 기본적으로 페이지(page)나 블록(block 단위로 다 수의 셀(cell)을 병렬 처리하여 높은 처리량을 달성하며, 그 결과 긴 셀 어레이 동작 시간을 허용하게 된다. 긴 셀 어레이 동작 시간은 고집적 저신뢰도 특성을 갖는 낸드 플래시 셀 어레이의 정교하고 동적인 제어를 가능케 한

E-mail: yonghocho@mnu.ac.kr, Tel: 061-450-2742

Manuscript received Sep. 12, 2024; revised Sep. 24, 2024; accepted Sep. 24, 2024.

This is an Open-Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License(http://creativecommons.org/licenses/by-nc/3.0) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

<sup>\*</sup> Professor, Dept. of Information and Communications Engineering, Mokpo National University

<sup>★</sup> Corresponding author

Acknowledgment

다. 낸드 플래시 메모리는 높은 집적도를 유지하기 위해 플레인(plane)이라고 불리는 대단위의 셀 어레이 몇 개 로 구성되는데, 이에 따라 비트라인(bitline)과 워드라인 (wordline) RC 부하가 매우 커 셀 어레이의 제어 신호 들은 낮은 시간 해상도를 갖는다. 이러한 특성은 셀 어레 이 제어기의 설계에 있어 유한상태기계(FSM) 대신 마이 크로컨트롤러(MCU)를 사용하는 것을 가능하게 한다 [1]-[3]. 한편, 낸드 플래시의 집적도가 지속해서 증가함 에 따라 셀의 신뢰성이 점점 저하되고, 그에 따라 셀 어 레이 제어 알고리즘이 점점 복잡해지고 있다[4]-[5]. 이 는 설계 과정에서 미묘한 오류가 발생할 확률을 높이며, 결과적으로 이러한 오류를 갖는 어레이 제어 알고리즘이 적용된 낸드 플래시 메모리가 대량 제조될 우려가 있다. 특히 MCU 명령어(instruction)들은 쓰기 가능한 RAM (Random-Access Memory) 대신, 면적 효율이 훨씬 높은 ROM(Read-Only Memory)에 저장되기 때문에, 일단 오류가 포함된 메모리가 생산되면 이를 수정할 방 법이 없다. 본 논문에서는 이와 같은 제조 후의 상황에서 알고리즘을 부분 수정하여 패치(patch)할 수 있는 MCU 아키텍처를 제안한다.

## Ⅱ. 본론

#### 1. 아키텍처 및 동작

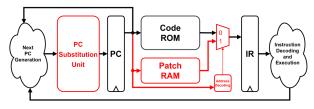

Fig. 1. Proposed MCU architecture. 그림 1. 제안하는 MCU 아키텍처

본 논문에서 제안하는 MCU 아키텍처를 그림 1에 나타내었으며, 새로 추가되는 구성 요소들은 빨간색으로 표시되어 있다. 기반이 되는 MCU는 간단한 2-단계 파이프라인(pipeline) 구조를 갖는 것으로 가정하였다. 첫번째 단계는 명령어 인출(fetch) 단계로, PC(Program Counter)의 주소 값에 따라 ROM에서 명령어를 가져와 IR(Instruction Register)에 저장한다. 두 번째 단계에서는 명령어 인출 이후 명령어 복호화, 연산 실행, 데이터 메모리 접근, 레지스터 쓰기 등의 나머지 모든 동작이수행된다.

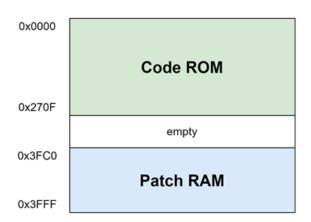

Fig. 2. MCU address map including the Patch RAM region.

그림 2. 패치 RAM을 포함한 MCU의 주소 맵

패치될 명령어들이 탑재되는 패치 RAM은 별도의 주소 공간을 형성하지 않고, 그림 2에서와 같이 기존 MCU 주소 공간에 할당된다. 일반적으로 셀 어레이 제어 알고리즘의 명령어 개수가 2<sup>n</sup>이 아닐 것이기 때문에 남는 주소 공간의 일부를 패치 RAM에 할당할 수 있다. 그림 2에서는 셀 어레이 제어 알고리즘이 10,000개의 명령어로 구성 되어있는 상황에서 패치 명령어 64개를 탑재하는 패치 RAM을 주소 공간의 끝부분에 할당하는 것을 가정하였다. 패치 명령어들은 전기적 퓨즈(fuse) 정보와 함께특정 셀 영역 저장되어 있다가 전원이 켜질 때 초기화과정에서 패치 RAM에 탑재된다. 패치 명령어들은 근본적으로 ROM이 아닌 낸드 셀에 저장되기 때문에 제조이후에도 얼마든지 프로그램 가능하다.

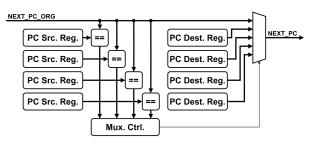

Fig. 3. PSU (PC Substitution Unit) block diagram. 그림 3. PSU(PC Substitution Unit) 블록 다이어그램

그림 1에서 기존의 다음 PC 값은 곧바로 PC 레지스 터에 입력되지 않고 새로 추가된 PSU(PC Substitution Unit)를 거친다. 그림 3에 PSU의 세부 구조를 나타내었 다. 4개의 패치까지 지원하는 것으로 가정하여 이를 위 한 레지스터 4쌍이 갖춰져 있다. 모든 PSU 레지스터의 값은 패치 RAM과 마찬가지로 특정 셀 영역에 저장되어 있다가 전원이 켜질 때 초기화 과정에서 PSU 레지스터 들에 탑재된다. 이후 어레이 제어 알고리즘이 MCU에서 실행될 때, 연산된 다음 PC 값이 특정 주소 값과 일치하 면, 멀티플렉서 제어를 통하여 미리 정해진 패치 RAM의 주소 값으로 대체된다. 이처럼 기존 MCU 주소 공간에 패 치 RAM을 할당함으로써 단순히 PC 값을 대체하는 방식 으로 명령어 실행 흐름을 패치 RAM으로 전환할 수 있다. PSU의 동작은 기본적으로 CAM(Contents Addressable Memory)과 동일하다.

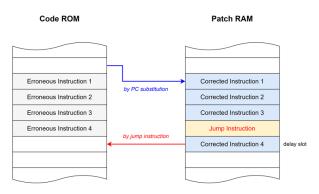

Fig. 4. Patched instruction snippet execution flow. 그림 4. 패치된 명령어들의 실행 흐름

그림 4는 패치된 명령어들의 실행 흐름을 보여준다. ROM에 저장된 명령어들이 실행되다가 오류 영역의 첫 주소 값이 다음 PC 값으로 설정되면, PSU에서 이를 감 지하여 RAM에 있는 패치 명령어 영역의 첫 주소로 대체 한다. 이후의 명령어 인출과 다음 PC 값 계산을 포함한 명령어 수행이 자연스럽게 연결된다. MCU 입장에서 패 치 명령어는 일반 ROM 영역의 명령어와 다를 것이 없 으므로 패치 명령어의 종류에는 특별한 제한이 없다. 패 치 명령어들의 실행이 끝나면 점프(jump) 명령어를 통해 ROM 내의 오류 영역 바로 다음 명령어로 실행 흐름이 전환된다. 점프 명령어 자체를 패치 명령어로 포함하여 프로그램할 수 있으므로 실행 흐름을 다시 ROM으로 전 환하기 위해서 별도의 PSU를 갖출 필요가 없는 것이다. 그림 4에서는 2-단계 파이프라인 구조를 가지는 MCU가 명령어 지연 슬롯(delay slot) 하나를 지원하는 것을 가 정하였다.

## Ⅲ. 결론

본 논문에서는 온칩 MCU를 사용하는 낸드 플래시 메 모리에서 셀 어레이 동작의 설계 오류를 제조 이후에도 수정할 수 있는 방법과 이를 위한 MCU 아키텍처를 제

안하였다. 제안된 아키텍처에서는 기존의 MCU 아키텍 처에 패치 명령어들을 저장하는 패치 RAM과 명령어 실 행 흐름을 ROM에서 패치 RAM으로 전환하는 PSU를 간단히 추가하였다. 패치 명령어들과 PSU 레지스터 값 들은 낸드 플래시 셀의 특정 영역에 전기적 퓨즈 데이터 와 같이 제조 이후에 프로그램되며 낸드 플래시 초기화 과정에서 패치 RAM과 PSU에 탑재된다. 본 논문에서 제 안한 기법을 통해 지속적으로 고도화되는 낸드 플래시 메모리에서의 설계 오류로 인한 리스크에 효과적으로 대 응할 수 있을 것으로 기대된다.

## References

[1] R. Micheloni, Luca Crippa, and Alessia Marelli, Inside NAND Flash Memories, Springer, 2010.

[2] G. Kim, "Leveraging the page buffer data cache for enhanced programmability in NAND flash memories with on-chip microcontrollers," Electronic Letters, vol.60, no.3, pp.e13111, 2024. DOI: 10.1049/ell2.13111

[3] G. G. Marotta et al., "A 3bit/cell 32gb nand flash memory at 34nm with 6mb/s program throughput and with dynamic 2b/cell blocks configuration mode for a program throughput increase up to 13mb/s," in 2010 IEEE International Solid-State Circuits Conference (ISSCC), 2010, pp.444-445. DOI: 10.1109/ISSCC.2010.5433949 [4] B. Kim et al., "A high-performance 1tb 3b/cell 3d-nand flash with a 194mb/s write throughput on over 300 layers," in 2023 IEEE International Solid-State Circuits Conference (ISSCC), 2023, pp.27-29. DOI: 10.1109/ISSCC42615.2023.10067666 [5] A. Khakifirooz et al., "A 1.67tb, 5b/cell flash memory fabricated in 192-layer floating gate 3d-nand technology and featuring a 23.3gb/mm2 bit density," in 2023 IEEE International Solid-State Circuits Conference (ISSCC), 2023, pp.27-29. DOI: 10.1109/LSSC.2023.3285508

## **BIOGRAPHY**

## Geonu Kim (Member)

2004 : BS degree in Electrical Engineering, KAIST.

2007 : MS degree in Electrical

Engineering, KAIST.

2017 : PhD degree in Electrical Engineering, Seoul National

University.

2007~2020: Senior Engineer, SK Hynix. 2020~: Assistant Professor, Mokpo National University.

## Yong-Ho Cho (Member)

2004: BS degree in Electrical

Engineering, KAIST.

2006: MS degree in Electrical

Engineering, KAIST.

2013: PhD degree in Electrical

Engineering, KAIST

2013~2016: Senior Researcher, Samsung Electronics. 2016~2021: Assistant Professor, Hoseo University. 2021~: Associate Professor, Mokpo National University.