# 2.4GHz 대역폭을 갖는 온도 보상 기능 탑재 고전력부가효율의 2 단 차동 캐스코드 전력증폭기 설계

Design of a Two-stage Differential cascode Power Amplifier with a Temperature Compensation function of High PAE with 2.4 GHz

박준형  $^1$ , 장지성  $^{1,2}$ , 김호원  $^{1,2}$ , 이강윤  $^{1,2,+}$  (Joon Hyung Park  $^1$ , Jisung Jang  $^1$ , Howon Kim  $^1$ , and Kang-Yoon Lee  $^{2+}$ )

### 요 약

본 논문에서는 130nm CMOS 공정을 이용하여 제작된 2.4GHz 차동 캐스코드 전력 증폭기에 대한 연구를 제시하고 있다. 이 전력증폭기는 무선 전력 전송 응용을 위해 설계되었으며, 단일 종단 출력을 위한 발룬 트랜스포머 설계로 구성된 두 개의 차동스테이지를 갖추고 있다. 출력 단 뿐만 아닌 각 단 사이의 전력 매칭을 위해 발룬 트랜스포머를 활용하고 있으며, 온도 보상이 가능한 바이어스 회로를 추가하여 2.4GHz 주파수 대역에서 안정적인 바이어스 전압을 유지한다. 이를 통해 TT/40℃에서 출력 전력은 21.75 dBm 이고 전력부가효율은 40.9%를 달성한다.

#### **ABSTRACT**

This paper presents a study on a 2.4GHz differential cascode power amplifier(PA) fabricated using a 130nm CMOS process. This PA is designed for wireless power transmission applications and consists of two differential stages with custom-designed balun transformers for single-ended output. Balun transformers are utilized not only for the output stage but also for power match-ing between each stage. Additionally, a bias circuit with temperature compensation capability is added to maintain stable bias voltage in the 2.4GHz frequency band. As a result, it achieves an output power of 21.75 dBm with a power-added efficiency(PAE) of 40.9% at  $TT/40\,^{\circ}\text{C}$ .

### **KEY WORDS**

balun transformer; temperature compensation;

## I. 서 론

수단으로 자리매김하고 있다. 휴대폰, 무선 인터넷, 센서 네트워크 및 사물 인터넷 (IoT)과 같은 다양한 응용 분야에서 무선 통신 기술의 중요성은 더욱 커지고 있다. 이에 따라 무선 통신 시스템의 성능 향상과 효율적인 운영은 더욱 중요해지고 있다.

특히 송신부에 활용되는 전력 증폭기의 고출력 전력과 높은 효율이 요구되고 있다. 전력증폭기는 온도 변화에 민감하여 출력 전력과 효율에 변화를 보일 수 있다. 이러한 온도 변화는 전력증폭기의 내부 저항과 손실도(Loss)를 변경시키며, 따라서 효율(Efficiency)에 영향을 미친다. 안정적인 따라서 효율성을 유지하기 위해서는 온도변화에 대한 보상이 필수적인 것을 알 수 있다[1,6]. 해당 논문에서는 전력증폭기의 동작 안정성을 확보하기 위해 Proportional To Absolute Temperature 발생기와 (PTAT) 기준 전압 발생기가 전압 조정 바이어스 발생기 온도 포함된 추가로 반영하여 온도 보상 보상 블록을 바이어스 회로를 전력증폭기에 도입하였다. 이를 통해 동작 온도 범위인 -40℃ ~ 125℃ 일정한 바이어스 전압을 내에서 유지함으로써 전력증폭기의 성능을 일관되게 유지할 수 있다. 이러한 보상 메커니즘은 전력증폭기가 고온 환경에서도 성능과 출력 전력을 유지할 수 있도록 한다.

<sup>&</sup>lt;sup>1</sup> Department of Electrical and Computer Engineering, Sungkyunkwan University

<sup>&</sup>lt;sup>†</sup>Corresponding author: Kangyoon Lee, <u>klee@skku.edu</u> <sup>2</sup> SKAlChips

<sup>(</sup>Received May. 1, 2024, Revised Jul. 22, 2024, Accepted Jul. 26, 2024)

해당 설계에서는 전력증폭기에 도입한 온도 바이어스 회로에 인해 -40℃ ~ 125℃의 넓은 범위의 온도 변동에서 20dBm 이상의 출력 전력을 유지하였으며 TT/40℃에서 40.9%의 높은 전력부가효율 (PAE)을 달성할 수 있었다.

본 논문은 본론에서 설계에서 사용된 전력증폭기 및 발룬 트랜스포머, 온도 보상회로에 대한 부가 설명, 그리고 시뮬레이션 결과를 다룰 예정이다.

## II. 본 론

## 1. 전력증폭기 설계

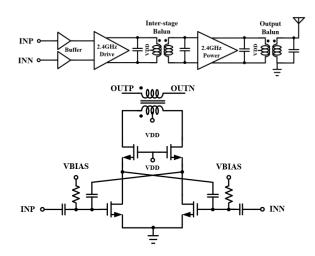

그림 1. 2.4GHz Drive Amp 및 Power Amp

전력증폭기 설계에 있어서 효율과 전력 부가효율은 전력증폭기의 우수성을 나타내는 대표적인 지표이다. 효율은 출력 전력과 입력 전력 간의 관계로 정의된다.

$$Efficiency(\%) = \frac{RF P_{out}}{DC P_{in}} \times 100$$

(1)

$$PAE(\%) = \frac{RF P_{out} - RF P_{in}}{DC \ power} \times 100 \tag{2}$$

식 (1)을 통해 출력 전력이 증가할수록, 효율이 높게 나오는 것을 확인할 수 있다. 전력 증폭기가 입력으로 받은 전력에 비해 출력으로 제공하는 전력의 비율을 나타낸 것이 식 (2)이며, 이를 전력부가효율이라고 정의할 수 있다 [2].

### (1) 2단 차동 캐스코드 전력증폭기 설계

높은 효율 및 전력부가효율을 달성하기 위해 출력전력이 필요하다[2]. 따라서 20dBm 이상의 높은 출력 전력을 달성하기 위해 그림 1 처럼 Drive Amp 및 Power Amp로 2단으로 구성하며, 출력신호를 강하게 증폭하는 동시에 공통모드 신호를 억제하여 전력 손실을 최소화하기 위해 차동 캐스코드 구조의 전력증폭기를 사용하였다 [4]. 입력 신호가 왜곡되어 신호이 품질을 저하시키지 않고 정확하게 증폭 및 증폭하는 과정에서 효율적으로 전력을 증폭하고 소비되는 전력을 최소화로 전력부가효율을 증가시키기 위해 Drive Amp 및 Power Amp를 선형성을 가진 클래스 AB 전력증폭기로 설계를 하였다.

#### 2. 트랜스포머

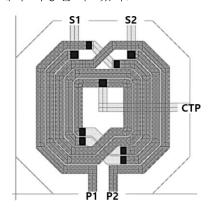

증폭기 간 손실이 최소화된 신호 전달을 위해 그림 2처럼 Interstage Balun Transformer와 차동 신호에서 종단 안테나에 단일 신호로 전달하기 위해 Output Balun Transformer를 구성하였다. Inter stage, Output 모두 나선형 구조를 사용하였다. 이러한 나선 구조의 Balun Transformer는 두 개의 나선 형태로 감겨진 전도체 선으로 구성되어 있다.

#### (1) 나선형 발룬 트랜스포머

나선형 발룬 트랜스포머는 고주파 신호의 전송에 적합하며, 넓은 주파수 대역에서 작동할 수 있다.

그림 2. Inter-Stage, Output Balun

이는 더 넓은 주파수 대역에서 데이터를 전송하고 통신의 품질을 향상시킬 수 있다. 이러한 나선형 구조는 전기적인 임피던스를 매우 효율적으로 변환할 수 있어 신호의 손실을 최소화 하고 신호의 정확성을 유지할 수 있다. 또한 소형화 및 통합성이 뛰어나며, 회로 및 시스템의 설계 및 구현을 용이하며 전력증폭기에 공통모드 잡음을 효과적으로 잡아주므로 차동 캐스코드 구조를 사용한 위 전력증폭기에 적합하다[3]. 나선형 구조는 회전 수, 폭, 직경 등을 조절하여 원하는 주파수 범위나 전력수준에 맞출 수 있다는 장점이 있다. 본 논문에서 각 발륜의 센터 탭은 Drive Amp와 Power Amp에 3.3V의 전압을 제공한다. Interstage 센터 탭에는 온도 보상 바이어스 회로로 인해 조절된 전력증폭기의 바이어스 전압을 공급하는 경로로 사용된다.

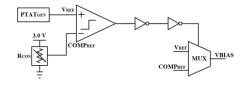

#### 3. 온도 보상 바이어스 회로

그림 3은 바이어스 전압 생성기는 출력 발문의 보조 센터 탭 및 전력증폭기의 차동 입력에 적용되는 바이어스 전압을 생성하기 위해 설계된 아키텍처를 보여준다. 이러한 바이어스 전압은 전력증폭기의 출력 전력 및 효율을 조절하는 데 중요한 역할을 한다 [6,7]. 그 중에서도 PTAT 발생기는 온도에 따라 선형적으로 변화하는 전압을 생성하는 역할을 담당하고 있다.

그림 3. 온도 보상 바이어스 아키텍처

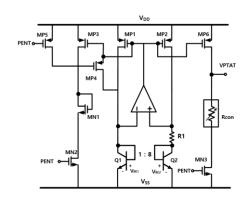

## (1) PTAT 발생기

PTAT 발생기는 그림 4에 나타낸 것처럼 주로 밴드갭 레퍼런스(BGR) 회로를 활용하여 구현된다. BGR 회로는 Process, Voltage, Temperature (PVT) 변동에 무관한 안정된 전압을 생성하는데 사용된다. 이를 통해 PTAT 발생기는 온도에 따라변하는 전압을 안정적으로 생성할 수 있다[5]. PTAT 발생기에서 발생하는 PTAT 전압은 식(3),(4)와 같다.

$$\Delta V_{BE} = V_{BE1} - V_{BE2} = V_T ln \frac{nI_0}{I_{S1}} - V_T ln \frac{I_0}{I_{S2}}$$

$$= V_T ln n$$

(3)

$$V_{REF} = V_{BE} + V_T \ln n \tag{4}$$

PTAT 발생기에서 생성된 선형 증가 전압과 참조 전압 발생기에서 생성된 직선 레벨 전압은 그림 3에 표기된 비교기를 통해 MUX로 전달된다. MUX는 입력된 두 전압 중에서 더 큰 값을 선택하여 최종 바이어스 전압을 생성한다. 이를 통해 온도에 따라 선형 또는 증가하는 전압 수준을 유지하면서 전력증폭기의 출력 전력을 안정적으로 유지할 수 있다.

이러한 PTAT 발생기를 통해 전력 증폭기의 민감도를 해결할 수 있고, 온도가 상승함에 따라 바이어스 전압을 보충하여 온도에 민감한 전력증폭기의 출력 전력을 20dBm 이상으로 유지할 수 있다.

## III. 시뮬레이션 결과

본 논문에서 소개된 전력증폭기는 3.3V의 공급전압에서 동작하며 설계와 검증은 130nm CMOS 공정을 사용하였다.

그림 4. PTAT 발생기

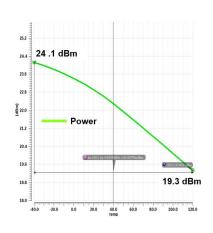

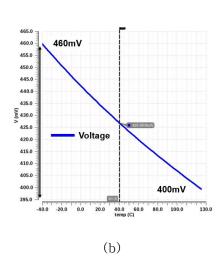

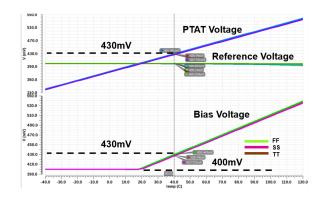

그림 5 에서는 설계된 전력증폭기를 온도에 따른 출력 전력과 바이어스 전압을 구한 것이다. 그림 5(a)를 통해 -40℃ ~ 125℃ 까지 출력 전력 변화량이 4.8dBm 임을알 수 있고, 그림 5(b)를 통해 바이어스 전압변화량이 60mV 임을 확인할수 있다. 그림6은 온도 보상 바이어스 회로에서 각코너별로 -40℃ ~ 125℃에서 PTAT 전압및 바이어스 전압을 나타내고 있다. 기준전압보다 PTAT 전압이 낮을 때는 400mV를바이어스 전압으로 보내주고 40℃일 때, PTAT 발생기에서 생성된 430mV 가바이어스 전압으로 출력되는 것을 확인할수있다. 따라서 기존 전압보다 PTAT 전압이

높아질 시 PTAT 전압을 바이어스 전압으로 보내주는 것을 알 수 있다.

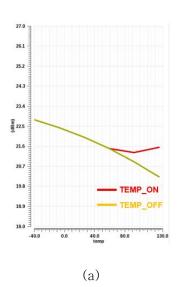

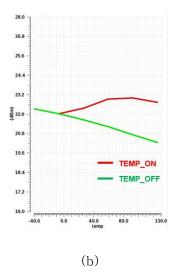

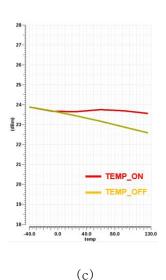

그림 7 은 온도 보상이 온/오프 된 SS/TT/FF 각 코너별로 공정에 대한 온도 범위가 -40° C 에서 125° C 까지의 전력 증폭기의 출력 전력을 보여주고 있다. 온도 보상 모드가 활성화된 경우, 고온에서 감소하던 출력 전력이 증가하는 것을 관찰할 수 있다. 가장 높은 온도인 125°C 에서 SS/TT/FF 공정에 대해 출력 전력이 각각 약 1.31dBm, 2.48dBm 및 0.96dBm 증가함을 확인할 수 있다. 이처럼 전력증폭기에 연결된 온도 보상 바이어스 블록을 통해 보상 모드를 켰을 때, 온도가 변하더라도 바이어스가 떨어지지 않고 증가하도록 하여, 출력전력이 온도에 따라 저하되는 현상을 방지하며 충분한 출력전력을 유지하게 끔 하는 것이 가능하다는 것을 확인할 수 있다.

(a)

그림 5. 온도 변화에 따른 (a) 출력 전력 (b) 바이어스 전압

그림 6. 바이어스 전압 발생기로부터의 바이어스 전압

그림 7. 온도 보상이 온/오프 된 코너 별 전력증폭기 출력 전력 (a) SS (b) TT (c) FF

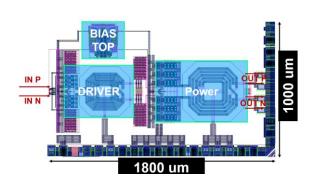

그림 8 은 설계되어진 전력증폭기의 전체적인 레이아웃을 보여주고 있다. 본문에 설명한 대로, 바이어스 전압 발생기에서 공급되는 바이어스 전압이 단계 간 발룬의센터 탭에 적용되는 것을 관찰할 수 있다. 이 전력증폭기의 레이아웃은 전력증폭기 코어와 패드 라우팅을 포함하여  $1000 \, \mu \, \mathrm{m} \times 1800 \, \mu \, \mathrm{m}$ 의 칩 영역 내에 구현되었다.

그림 8. 설계된 전력증폭기 레이아웃

표 1 를 통해 -40° ~ 125° 의 넓은 범위의 온도 변동에서 최소 20dBm 이상의 출력전력을 확보하고 최소 29% 이상의 PAE가 나오는 것을 확인할 수 있다.

표 2 를 통해 위 논문에서 설계된 전력증폭기가 온도범위가 더 넓고, 더 높은 전력부가효율을 가지는 것을 확인할 수 있다.

표 1. 제안된 전력증폭기 출력 비교표

|                          | Temperature Compensation ON |        |         |

|--------------------------|-----------------------------|--------|---------|

|                          | FF/−40℃                     | TT/40℃ | SS/125℃ |

| Power<br>[dBm]           | 23.84                       | 21.75  | 21.55   |

| Current Consumption [mA] | 140                         | 113    | 147.1   |

| Power Gain<br>[dBm]      | 18.84                       | 16.75  | 147.1   |

| P1dB<br>[dBm]            | 21.9                        | 19.46  | 13.11   |

| PAE<br>[%]               | 52.53                       | 40.9   | 29.23   |

표2. 전력증폭기 참고문헌 비교표

|                                | This Work     | [6]           | [7]                   |

|--------------------------------|---------------|---------------|-----------------------|

| Process                        | CMOS<br>130nm | CMOS<br>180nm | GaAs<br>MESFET<br>N/A |

| Туре                           | Class-AB      | Class-E       | Class-AB              |

| VDD<br>[V]                     | 3.3           | 3.3           | 7                     |

| Frequency<br>[GHz]             | 2.4           | 0.34-0.53     | 6.5-10.5              |

| Power<br>[dBm]                 | 21.75         | -3            | 23.5                  |

| Tempera-<br>ture Range<br>[°C] | -40/125       | -40/85        | -10/80                |

| PAE<br>[%]                     | 40.9          | 24            | 37                    |

### IV. 결론

본 논문에서는 2.4GHz 타켓 높은 효율의 전력증폭기를 제안하였다. 제안된 전력증폭기 구조는 Interstage Balun 과 Output Balun을 적용하여 파워 매칭을 달성하고, 최적화된 파라미터를 통해 TT/40℃ 조건에서

10

21.75dBm 의 출력전력을 얻었다. 또한, 온도 보상 바이어스 블록을 도입하여 온도 변동에 기능을 갖추었다. 시뮬레이션 대하 보상 결과로부터 40.9%의 전력부가 효율을 달성하여 입력전력을 효율적으로 증폭된 출력전력으로 변환할 수 있음을 입증하였다. 보상 바이어스 블록은 또하. 온도 PTAT 발생기를 활용하여 동작 온도 범위 내에서 일정한 바이어스 전압을 유지하므로 전력증폭기의 일관된 성능과 출력 전력을 보장할 수 있다는 것을 확인하였다. 이러한 온도 보상 바이어스 블록의 성능을 개선하고 더 넓은 온도 범위에 대한 보상을 제공하기 위해 또 다른 구조나 보상 메커니즘을 고려하는 연구를 통해 더욱 효율적이고 안정적인 고성능 전력 증폭기의 개발과 무선 통신 시스템의 성능 향상에 기여할 수 있을 것으로 기대된다.

### 감사의 글

이 논문은 2024 년도 정부(산업통상 자원부)의 재원으로 한국산업기술진흥원의 지원을 받아 수행된 연구임 (P0012451, 2024년 산업혁신인재성장지원 사업)

## 참고 문헌

- [1] D. Kang, B. Park, D. Kim, J. Kim, Y. Cho, and B. Kim, "Envelope-tracking CMOS power amplifier module for LTE applications," IEEE Transactions on Microwave Theory and Techniques, vol. 61, no. 10, pp. 3763-3773, Oct. 2013.

- [2] B. Razavi, "RF Microelectronics," 2nd ed. Prentice Hall, 2012, ch. 12, sec. 2, pp. 826–848.

- [3] I. Aoki, S. D. Kee, D B. Rutledge, and A. Hajimiri, "Fully integrated CMOS power amplifier design using the distributed active-transformer architecture," IEEE Journal of Solid-State Circuits, vol. 37, no. 3, pp. 371-383, Mar. 2002

- [4] D. Chowdhury, C. D. Hull, O. B. Degani, Y. Wang, and A. M. Niknejad, "A fully integrated dual-mode highly linear 2.4 GHz CMOS power amplifier for 4G WiMAX applications," IEEE Journal of Solid-State Circuits, vol. 44, no. 12, pp. 3393-3402, Dec. 2009.

- [5] Y. Ji, B. Kim, H. -J. Park and J. -Y. Sim, "A Study on Bandgap Reference Circuit With Leakage-Based PTAT Generation," in IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 26, no. 11, pp. 2310-2321, Nov. 2018, doi:10.1109/TVLSI. 2018.285280.

- [6] C.Liu, C.J.Richard Shi, "Design of the Class-E Power Amplifier Considering the Temperature Effect of the Transistor On-Resistance for Sensor Applications",

IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 68, no. 5, pp. 1705-1709, Mar. 2021.

[7] K. Yamauchi, Y. Iyama, M. Yamaguchi, Y. Ikeda, S. Urasaki and T. Takagi, "X-band MMIC power amplifier with an on-chip temperature-compensation circuit", IEEE Trans. Microw. Theory Techn., vol. 49, no. 12, pp. 2501-2506, Dec. 2001.

박준형 (Joon Hyung Park), 정회원

2023년 2월 : 충남대학교 전파정보통신공학과 졸 업

2023년 3월~현재 : 성균 관대학교 전자전기컴퓨 터공학과 석사과정

<관심분야> CMOS RF 송수신기 설계

장지성 (Jisung Jang), 정회원

2021년 2월 : 한국항공대 학교 전기전자공학과 졸업

2024년 2월 : 성균관대학 교 전자전기컴퓨터공학 과 석사

2024년 3월~현재 : 성균 관대학교 전자전기컴퓨 터공학과 박사과정

<관심분야> CMOS RF 송수신기 설계, 아날로 그 회로

김호원 (Howon Kim), 정회원

2021년 2월 : 국립강릉원 주대학교 전자공학과 졸업

2023년 2월 : 성균관대학 교 전자전기컴퓨터공학 과 석사

2023년 3월~현재 : 성균 관대학교 전자전기컴퓨 터공학과 박사과정

<관심분야> CMOS RF 송수신기 설계, 위상 고정 루프 설계

## 이강윤 (Kang-Yoon Lee), 정회원

1996년 2월 : 서울대학교 전기정보공학부 졸업 1998년 2월 : 서울대학교 전기정보공학부 석사 2003년 2월 : 서울대학교 전기전자공학부 박사 2003년 3월 ~ 2005년 :

GCT Semiconductor Inc. 근무

2005년~2011년 : 건국대학교 전자공학과

조교수 근무

2012년~현재 : 성균관대학교 정보통신공학

부 교수 재직 중

2019년~현재 : 스카이칩스 CEO(Chief

Executive Officer) 재직 중

<관심분야> 전력 통합 회로, CMOS RF 송수 신기, 아날로그 통합 회로, 아날로그/디지 털 혼합 모드 VLSI 시스템 설계 등