# 저온 중수소 어닐링을 활용한 Enclosed-Layout Transistors (ELTs) 소자의 제작 및 전기적 특성분석

왕동현1, 김동호1, 길태현1, 연지영2, 김용식3, 박준영100

<sup>1</sup> 충북대학교 전자공학부 <sup>2</sup> 키파운드리 <sup>3</sup> 대림대학교 반도체학과

Fabrication of Enclosed-Layout Transistors (ELTs) Through Low-Temperature

Deuterium Annealing and Their Electrical Characterizations

Dong-Hyun Wang  $^{\rm l}$  , Dong-Ho Kim  $^{\rm l}$  , Tae-Hyun Kil  $^{\rm l}$  , Ji-Yeong Yeon  $^{\rm 2}$  , Yong-Sik Kim  $^{\rm 3}$  , and Jun-Young Park  $^{\rm l}$

<sup>1</sup> School of Electronics Engineering, Chungbuk National University, Cheongju 28644, Korea

<sup>2</sup> Key Foundry Co., Ltd., Cheongju 28429, Korea

(Received October 16, 2023; Revised November 4, 2023; Accepted November 8, 2023)

**Abstract:** The size of semiconductor devices has been scaled down to improve packing density and output performance. However, there is uncontrollable spreading of the dopants that comprise the well, punch-stop, and channel-stop when using high-temperature annealing processes, such as rapid thermal annealing (RTA). In this context, low-temperature deuterium annealing (LTDA) performed at a low temperature of  $300^{\circ}$ C is proposed to reduce the thermal budget during CMOS fabrication. The LTDA effectively eliminates the interface trap in the gate dielectric layer, thereby improving the electrical characteristics of devices, such as threshold voltage ( $V_{TH}$ ), subthreshold swing (SS), on-state current ( $I_{ON}$ ), and off-state current ( $I_{OFF}$ ). Moreover, the LTDA is perfectly compatible with CMOS processes.

Keywords: Enclosed-layout transistor, Low-temperature deuterium annealing, MOSFET, Silicon, Thermal budget

#### 1. 서 론

반도체 소자의 크기는 칩의 집적도 향상과 출력 속도의 개선, 그리고 저전력 구동을 위하여, 수십 년간 소형화되

☑ Jun-Young Park; junyoung@cbnu.ac.kr

Copyright ©2024 KIEEME. All rights reserved.

This is an Open-Access article distributed under the terms of the

This is an Open-Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License (http://creativecommons.org/licenses/by-nc/3.0) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

고 있다 [1]. 하지만 반도체 소자의 지속적인 소형화는 단채널 효과(short-channel effects, SCEs) 유발로 인한 소자 개발의 어려움을 초래하며, 이에 대한 해결책 모색이 꾸준히 이루어지고 있다 [2]. 단채널 효과란, metal-oxide-semiconductor field-effect-transistor (MOSFET) 소자의 채널의 길이(channel length)가 소형화되면서, 게이트 전압(gate voltage,  $V_G$ )에 의한 트랜지스터의 ON/OFF 제어가 아닌 드레인 전압(drain voltage,  $V_D$ ) 이 소자 구동을 통제하는 현상이다. 이러한 단채널 효과는 MOSFET

<sup>&</sup>lt;sup>3</sup> Department of Semiconductor Engineering, Daelim University College, Anyang 13916, Korea

의 threshold voltage  $(V_{TH})$  mismatch 및 칩의 오작동을 유발할 뿐만 아니라, 칩의 대기전력과 관련된 소자의 subthreshold swing (SS) 및 off-state current  $(I_{OFF})$ 의 증가를 초래한다 [3].

하지만 이러한 단채널 효과는 게이트 전압에 의한 드레인 전류(drain current,  $I_D$ )의 제어 능력인 게이트 통제력 (gate controllability)의 개선을 통하여, 크게 억제될 수있다. 이를 위하여, 소자의 구조적 측면에서는, FinFET 또는 gate-all-around (GAA) FET와 같은 3차원 반도체 소자 구조가 양산에 적용되고 있다 [2,4]. 뿐만 아니라, 소자의 소재적 측면에서는, 기존의  $SiO_2$  게이트 절연막 (dielectric)에  $HfO_2$ 와 같은 high-k 소재를 추가 적용하여, 게이트 커패시턴스(gate capacitance)를 증가시키고 있다 [5].

이 외에, 소자의 제조공정 측면에서는, 저온 기반(low-temperature)의 열 공정(thermal annealing) 기술 개발의 필요성이 대두되고 있다. 기존의 고온 기반의 CMOS 열공정은, shallow junction을 만들기에 불리할 뿐만 아니라, well, punch-stop, channel-stop, halo 등에 포함된 dopant의 불가피한 확산 및 deactivation을 초래한다. 이러한 맥락에서, 열 비용(thermal budget)을 줄이기 위한 대체 기술로써, microwave annealing (MWA)과 같은 기술이 2014년에 소개된 바 있다 [6]. 이러한 MWA은 낮은열 비용 하에서, dopant activation은 극대화하는 반면, dopant의 확산은 최소화하는 것이 특징이다. 하지만 MWA은 microwave의 흡수를 용이하게 하기 위한 별도의 탄소 기반의 흡수재를 웨이퍼에 도포하고, 이후 별도 제거하는 과정을 필요로 하는 등 아직 실리콘 기반의 CMOS 공정에 적용되기에는 난제가 존재하고 있다.

이에, 이 연구에서는 기존에 활용되어 온 고온 기반의 열 공정을 일부 대체 가능 하도록 새로운 열 공정을 제안한다. 구체적으로, 기존 1,000~1,100℃의 온도 범위에서 이루어진 rapid thermal annealing (RTA)을 대신하여, 300℃의 낮은 온도 범위에서 이루어지는 열 공정을 소개한다. 이를 좀 더 용이하게 하기 위하여, 챔버 내부에 고압의 중수소 가스를 주입하며, 주입된 중수소는 소자 특성의 개선을 극대화한다. 중수소 가스의 유효성을 검증하기 위하여, 질소 가스 환경에서 대조군 실험 및 실험군과의 비교 분석이 이루어진다. 질소 가스 환경에서 시행되는 열 공정과는 달리, 중수소 가스 환경에서는 소자의 SiO₂ 게이트 절연막과 Si 채널 사이에 존재하는 interface trap의 passivation 이 가능하다. 제안하는 열 공정의 온도는 기존의 열 공정에 비해 현저히 낮을 뿐만 아니라, CMOS 공정에 완벽히 호환가능한 특징을 지니고 있다.

#### 2. 실험 방법

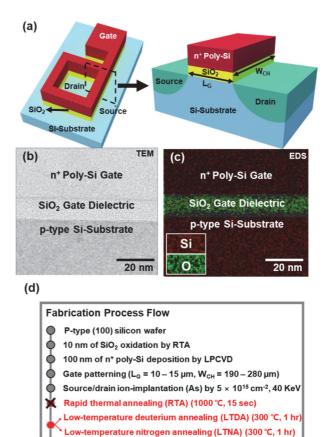

저온 기반의 열 공정을 시행하기 전에. 공정의 유효성을 검증하기 위하여, 실리콘 기판에서 test vehicles (TVs) 반도체 소자를 그림 1과 같이 제작하였다 [7]. 그림 1(a)와 같은 enclosed-layout transistor (ELT) 소자는 게이트 전 극이 소스/드레인 영역을 전체적으로 감싸고 있는 형태를 지니고 있으며, 제조과정이 용이하기에, 공정 검증을 위한 TVs로 활용되기에 적합하다. 소자의 제작은 4인치 p-type 실리콘 웨이퍼(Si-substrate) 상에서 이루어졌으며, 클리닝 이후, 산화 공정(thermal oxidation)을 활용하여 10 nm 두께의  $10 \text{ sio}_2$  게이트 절연막(gate dielectric)을 형성하였다. 이후, low-pressure chemical vapor deposition (LPCVD) 공정 및 포토공정을 진행하여 100 nm 두께의 10 mm 두메의 10 mm  $10 \text{ mm$

**Fig. 1.** (a) Schematic of an enclosed-layout transistor fabricated for test vehicles (TVs), (b) a cross-sectional transmission-electron microscopy (TEM) image, (c) an energy-dispersive x-ray spectroscopy (EDS) image of a device, and (d) summary of the fabrication process flow of the TVs.

입(ion implantation) 공정을 통하여 Arsenic (5×10<sup>15</sup> cm<sup>-2</sup>, 40 keV)을 self-align으로 주입하였다. 이온 주입이후, 통상적으로 1,000~1,100℃의 고온에서 이루어지는 RTA 공정이 dopant activation을 위하여 필요하다. 하지만 이번 연구에서는 이러한 고온의 열 공정을 300℃에서 이루어지는 low-temperature deuterium annealing (LTDA)으로 대체하였다 [8-10]. 제작 완료된 실리콘 TV 소자의 transmission-electron microscopy (TEM) 사진 및 상세한 제조공정은 그림 1(b)~(d)에 요약되어 있다.

제작된 TVs 소자의 크기는 gate length (L<sub>G</sub>) 기준으로 10~15 µm 범위, 그리고 channel width (W<sub>CH</sub>) 기준으로 190~280 µm 범위에서 분포하였다. 소자 제작 이후, LTDA 공정을 수행하기 이전에, B1500A 반도체 분석기 (parameter analyzer)를 활용하여, 총 354개 소자의 I<sub>D</sub>-V<sub>G</sub> 및 I<sub>D</sub>-V<sub>D</sub> 특성을 측정하였다. 이후, 175개의 비교군 소자를 대상으로, 질소(N<sub>2</sub>)와 중수소(D<sub>2</sub>)가 96:4의 비율로 혼합된 가스를 챔버에 주입하여, 10 bar의 압력 및 300°C 환경으로 만들었으며, 이 상태에서, 1시간 동안 유지하여 LTDA 공정을 수행하였다. 저온 중수소 공정(LTDA)의 유효성을 객관적으로 비교 검증 하기 위하여, 나머지 179개의 대조군 소자를 대상으로는, low-temperature nitrogen annealing (LTNA), 즉 100% 농도의 질소를 주입하여, 동일한 온도와 압력에서 열 공정을 진행하였다.

## 3. 결과 및 고찰

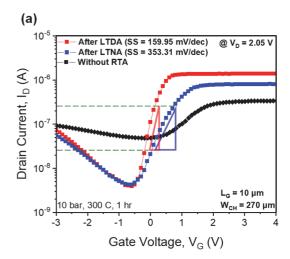

그림 2(a)는 제작된 반도체 소자의 열 공정 적용 유무에 대한 측정된  $I_{D}$ - $V_{G}$  그래프를 보여준다. 모든 소자는 dopant activation을 위한 별도의 고온 RTA를 생략하였으며, 이를 대신하여, LTDA 또는 LTNA를 시행하였다. LTDA 또는 LTNA 공정 전/후 소자의 비교는 웨이퍼 내에서 동일한 소자를 대상으로 진행하였다. 소자의  $V_{TH}$ 는 constant current (CC) method를 기반으로 추출하였다. 일반적인 CC method는  $W_{CH}/L_{G}$  ratio에 일정 크기의  $I_{D}$ 를 곱하여,  $V_{TH}$ 를 추출하는 것이 특징이다 [11]. 하지만 RTA를 생략한 공정의 특성상, 소자의 series resistance 가 높은 관계로 인하여, 이 연구에서는  $I_{D}$ = $2.5\times10^{-7}$  A에서 일괄적으로  $V_{TH}$ 를 추출하였다. SS는  $V_{TH}$ 로부터 10배 낮은 전류 구간의 기울기를 통하여 추출하였으며,  $I_{ON}$ 은  $V_{G}$ = $V_{TH}$ +2 V에서 일괄적으로 추출하였다.

RTA를 전혀 시행하지 않은 초기 소자와 비교할 때, LTNA 공정을 시행한 소자의 경우, SS 및 on-state current  $(I_{ON})$  특성의 개선이 확인되었다. 오직 질소만이

Fig. 2. Measured (a) the  $I_D$ - $V_G$  and (b) transconductance  $(g_m)$  of a device without RTA, after LTNA, and after LTDA.

주입된 환경에서, 소자의 특성이 개선되는 것은 소자의  $n^+$  poly 게이트 전극 내에 포함되어 있던 미량의 수소 (hydrogen)의 확산으로부터 기인하였을 것으로 추정된다 [12]. 하지만 중수소 환경에서 시행되는 LTDA에서는 LTNA에 견주어, 2.21배 더 개선된 SS 특성과 1.7배 더 개선된  $I_{ON}$ 을 보여주었다. 즉 질소 환경에서 시행되는 LTNA는 본디 존재하는 수소의 공급량이 충분하지 못하여, 게이트 절연막과 채널 사이에 존재하는 interface trap을 효과적으로 passivation 하지 못하는 반면, LTDA 공정에서는 외부로부터 충분한 중수소가 공급되어, interface trap를 효과적으로 제거 가능함을 알 수 있다 [13,14]. 그리고 이러한 interface trap의 개선은 carrier mobility의 개선을 가능하게 하여,  $I_{ON}$ 의 향상에 기여하는 것으로 여겨진다. 그림  $I_{ON}$ 의 출력 특성인 transconductance ( $I_{OM}$ )를 보여주고 있다. LTNA의 경우는 RTA를 전혀 시행하지

않은 초기 소자에 비하여,  $g_m$ 이 3.43배 개선되었으나, 중 수소를 활용한 LTDA의 경우는 LTNA의 경우보다 약 2.89배 더 개선됨을 확인할 수 있다. 이러한 소자의 전기적인특성의 개선이 LTNA에 비하여, LTDA에서 더 뚜렷하다는점에 착안할 때, 온도나 압력 조건에 의한 소자의 개선이 아닌, 중수소 가스의 영향으로 인한 소자의 개선임이 명백하다.

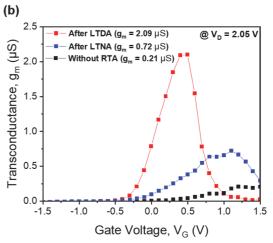

그림 3은 실험의 재현성 확인을 하기 위하여, 총 354개의 소자를 대상으로 대량 측정된  $I_D$ - $V_G$  데이터를 보여준다. 354개의 TV 소자 중, RTA 공정을 대신하여, LTNA를 시행한 소자들은 총 179개이며, LTDA를 진행한 소자들은 총 175개이다. 결과적으로, 중수소 환경에서 열처리 공정을 시행한 경우가 질소 대조군에 비하여,  $I_{ON}$  및 SS 특성의 개선이 일관적으로 더 효과적임을 확인할 수 있다.

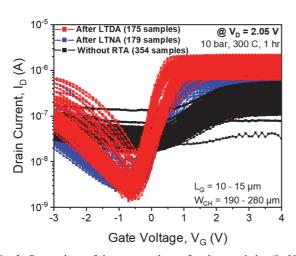

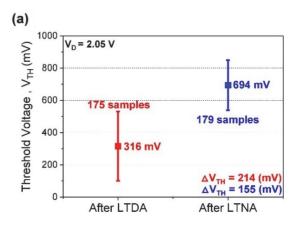

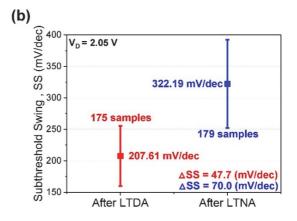

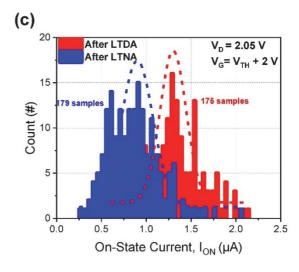

그림 4는 LTDA와 LTNA 열 공정 적용에 대한 TV 소자의  $V_{TH}$ , SS, 그리고  $I_{ON}$ 의 평균값 및 표준편차를 보여준다. 그림 4(a)에 따르면  $V_{TH}$ 의 평균값은 LTDA 및 LTNA가 각각 316 mV, 694 mV이며, LTDA의 경우, 이상적인 소자의  $V_{TH}$ 의 범위인  $200\sim300$  mV 구간에 위치함을 알수 있다. 그리고 LTDA의 SS 평균값은 207.61 mV/dec인 반면, LTNA의 평균값은 322.19 mV/dec로 약 114.58 mV/dec차이를 보여주었다 [그림 4(b)]. 그림 4(c)는 열 공정에 대한 추출된  $I_{ON}$  누적 분포 결과를 보여준다. LTDA를 진행한 대부분의 소자들이 LTNA에 비해  $I_{ON}$ 의 산포가 21% 더 개선되었고, 중간값은 1.5배 더 개선되었음을 확인할수 있다 [9,15].

$\label{eq:Fig. 3. Comparison of the measured transfer characteristics ($I_D$-$V_G$) plot without RTA, after LTNA, and after LTDA for 354 samples.}$

**Fig. 4.** Comparison of the mean and standard deviation of (a)  $V_{TH}$  extracted at  $I_D$ =2.5×10<sup>-7</sup> and (b) extracted SS, and (c) cumulative distribution of  $I_{ON}$  extracted at  $V_D$ =2.05 V.

### 4. 결 론

이 연구에서는 실리콘 CMOS 소자 제작을 위하여 기존 활용되어 온, 고온 기반의 rapid thermal annealing (RTA) 공정을 일부 대체하여, 300℃의 낮은 온도에서 열 공정을 진행하였다. 먼저, 제안하는 저온 열 공정의 유효 성을 검증하기 위하여, 실리콘 기판에서 enclosedlayout transistors (ELTs) 소자를 제작하였다. ELT 소자 는 제조과정이 용이하여, 공정을 시험하기 위한 소자로 적 절하다. 소자 제작 이후, 300℃의 온도 및 10 bar의 압력 하에, 질소 가스(low-temperature nitrogen annealing, LTNA)와 중수소 가스(low-temperature deuterium annealing, LTDA)를 각각 주입하여, 소자의 특성 변화를 관찰하였다. LTNA 또는 LTDA를 시행한 샘플의 경우, RTA를 전혀 시행하지 않은 초기 소자에 비하여, 성능 개선 이 확인되었다. 특히, 질소 가스가 주입된 LTNA의 경우, 소자의 n<sup>+</sup> poly 게이트 전극에 존재하던 미량의 수소의 확 산이 소자 개선을 일부 가능하게 한 것으로 추정된다. 반 면, 중수소 가스가 주입된, LTDA 비교군의 경우 LTNA 공 정을 진행한 대조군에 견주어 V<sub>TH</sub>, I<sub>ON</sub>/I<sub>OFF</sub> ratio, SS, and g... 특성이 더욱 뚜렷하게 개선되었다. 이는 LTNA 공정과 는 다르게 LTDA 공정에 주입되는 중수소가 게이트 산화 막과 표면을 passivation 하여 interface trap를 효과적 으로 제거하였기 때문이다. 결론적으로, 이와 같은 저온 공 정은 실리콘 소자를 제작함에 있어 낮은 열 비용을 추구할 수 있게 된다는 점에서 고무적이라 할 수 있다.

#### **ORCID**

Jun-Young Park

https://orcid.org/0000-0003-4830-9739

#### 감사의 글

This research was supported by Chungbuk National University Korea National University Development Project (2023).

#### **REFERENCES**

[1] M. Badaroglu, Proc. 2021 IEEE International Roadmap for Devices and Systems Outbriefs (IEEE, Santa Clara, USA, 2022) p. 1.

doi: https://doi.org/10.1109/IRDS54852.2021.00010

- [2] J. Y. Yeon, K. S. Lee, S. S. Yoon, J. W. Yeon, H. Bae, and J. Y. Park, J. Korean Inst. Electr. Electron. Mater. Eng., 35, 576 (2020).

- doi: https://doi.org/10.4313/JKEM.2022.35.6.6

- [3] D. J. Frank, R. H. Dennard, E. Nowak, P. M. Solomon, Y. Taur, and H.S.P. Wong, *Proc. IEEE*, 89, 259 (2001). doi: https://doi.org/10.1109/5.915374

- [4] D. H. Wang and J. Y. Park, J. Korean Inst. Electr. Electron. Mater. Eng., 36, 50 (2022). doi: https://doi.org/10.4313/JKEM.2022.35.1.8

- [5] C. P. Lin, B. Y. Tsui, M. J. Yang, R. H. Huang, and C. H. Chien, IEEE Electron Device Lett., 27, 360 (2006). doi: https://doi.org/10.1109/LED.2006.872832

- [6] Y. R. Jhan, Y. C. Wu, Y. L. Wang, Y. J. Lee, M. F. Hung, H. Y. Lin, Y. H. Chen, and M. S. Yeh, *IEEE Electron Device Lett.*, 36, 105 (2014). doi: https://doi.org/10.1109/LED.2014.2386213

- [7] D. H. Jung, J. Y. Ku, D. H. Wang, Y. S. Son, and J. Y. Park, J. Korean Inst. Electr. Electron. Mater. Eng., 35, 264 (2022). doi: https://doi.org/10.4313/JKEM.2022.35.3.8

- [8] J. M. Yu, D. H. Wang, J. Y. Ku, J. K. Han, D. H. Jung, J. Y. Park, and Y. K. Choi, *Solid-State Electron.*, 197, 108421 (2022). doi: https://doi.org/10.1016/j.sse.2022.108421

- [9] D. H. Wang, S. S. Yoon, J. Y. Ku, D. H. Jung, K. S. Lee, D. Kim, and J. Y. Park, *IEEE Trans. Device Mater. Reliab.*, 23, 297 (2023). doi: https://doi.org/10.1109/TDMR.2023.3275947

- [10] J. Y. Ku, J. M. Yu, D. H. Wang, D. H. Jung, J. K. Han, Y. K. Choi, and J. Y. Park, *IEEE Trans. Electron Devices*, 70, 3958 (2023).

- doi: https://doi.org/10.1109/TED.2023.3278626

- [11] H. G. Lee, S. H. Oh, and G. Fuller, *IEEE Trans. Electron Devices*, 29, 326 (1982). doi: https://doi.org/10.1109/T-ED.1982.20707

- [12] J. Y. Park, D. I. Moon, G. B. Lee, and Y. K. Choi, *IEEE Trans. Electron Devices*, **67**, 777 (2020). doi: https://doi.org/10.1109/TED.2020.2964846

- [13] J. Y. Ku, K. S. Lee, D. H. Jung, D. H. Wang, S. Oh, K. Lee, B. Cho, H. Bae, and J. Y. Park, *IEEE Trans. Device Mater. Reliab.*, 23, 276 (2023). doi: https://doi.org/10.1109/TDMR.2023.3270920

- [14] D. H. Kim, S. K. Lim, H. Bae, C. K. Kim, S. W. Lee, M. Seo, S. Y. Kim, K. M. Hwang, G. B. Lee, B. H. Lee, and Y. K. Choi, IEEE Trans. Electron Devices, 65, 1640 (2018). doi: https://doi.org/10.1109/TED.2018.2805316

- [15] J. M. Yu, J. Y. Park, T. J. Yoo, J. K. Han, D. H. Yun, G. B. Lee, J. Hur, B. H. Lee, S. Y. Kim, B. H. Lee, and Y. K. Choi, *IEEE Trans. Electron Devices*, 67, 3903 (2020). doi: https://doi.org/10.1109/TED.2020.3008882