ISSN: 1226-7244 (Print) ISSN: 2288-243X (Online)

논문번호 23-02-08

54

# 빠른 회로 시뮬레이션을 위한 멤리스터의 전류-전압 및 과도 동작 콤팩트 Verilog-A 모델

Compact Verilog-A Model of Current-Voltage and Transient Behaviors of Memristors for Fast Circuit Simulation

조 승 명, 오 석 진, 윤 리 나, 민 경 식\*\*

Seung-Myeong Cho, Seokjin Oh, Rina Yoon, Kyeong-Sik Min\*\*

## Abstract'

This paper proposes and describes a compact model for the butterfly current-voltage characteristics and time-varying transient characteristics of memristors, which are attracting attention as a next-generation nonvolatile memory technology due to their advantages of low power, high integration, and fast switching speed. Specifically, we want to evaluate the accuracy of the model by comparing it to measurements of memristor devices and see if the simulation time is reduced by applying the model to circuit simulations. The error between the memristor measurements and the model in this paper is calculated to be less than 2%, showing that the model can predict the current-voltage characteristics of the memristor with high accuracy. It can be observed that utilizing the model in this paper to perform circuit simulation can cut simulation time by around 27% when compared to the prior model by comparing the simulation times of the memristor model and the previous model. The memristor compact model proposed in this paper is expected to contribute to reducing the total system design time by reducing simulation time, especially in the design of edge intelligence hardware.

#### 요 약

본 논문은 저전력, 높은 집적도, 빠른 스위칭 속도 등의 이점으로 차세대 비휘발성 메모리 기술로 주목받고 있는 멤리스터의 butterfly 전류-전압 특성과 시간의 변화에 따른 transient 특성에 대한 콤팩트한 모델을 제안하고 이를 설명한다. 구체적으로 멤리스터 소자의 측정과 비교하여 모델의 정확도를 평가하여 회로 시뮬레이션에 본 모델을 적용하여 시뮬레이션 시간이 단축되는 것을 확인하려 한다. 멤리스터 측정과 본 논문의 모델의 오차는 2% 이하로 계산이 되어서 본 모델이 멤리스터의 전류-전압 특성을 높은 정확도로 예측할 수 있음을 보여준다. 이전 모델과 본 논문의 멤리스터 모델의 시뮬레이션 시간을 비교한 결과 본 논문의 모델을 이용해서 회로 시뮬레이션을 수행하면 이전의 모델에 비해 시뮬레이션 시간이 27% 정도 단축이 될 수 있음을 확인할 수 있다. 본 논문에서 제안한 멤리스터 콤팩트 모델은 특히 엣지 인텔리젼스 하드웨어의 설계 등에서 시뮬레이션 시간을 단축하여 시스템 총 설계 시간을 줄이는 데 기여할 수 있을 것으로 기대된다.

Key words: Characterization, ReRAM, Non Volatile Memory, Rram modeling, Verilog-A

E-mail: mks@kookmin.ac.kr, Tel: +82-2-910-4634

Acknowledgment

The work was financially supported by NRF-2022R1A5A7000765, NRF-2021R1A2C1011631, NRF-2021M3F3A2A01037972, The CAD tools were supported by IC Design Education Center (IDEC), Daejeon, Korea.

Manuscript received May. 22, 2023; revised Jun. 13, 2023; accepted Jun. 26, 2023,

This is an Open-Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License(http://creativecommons.org/licenses/by-nc/3.0) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

<sup>\*</sup> Dept. of Electronics Engineering, Kookmin University

<sup>★</sup> Corresponding author

#### 1. 서론

멤리스터(memristor)는 1971년에 Leon Chua 교수가 이론상으로 제안하였으며, 2008년 HP 연구진의 실험을 통해 발견된 이후 Processing In Memory, 뉴로모픽 등에 응용하기 위한 연구가 활발히 진행되고 있다[1]. 멤리스터는 높은 직접도, 낮은 전력 소모, 빠른 switching속도 등의 이점으로 인해 기존의 메모리 기술에 비해 내장용 메모리로 사용될 수 있고 또한 메모리와 연산 기능의 통합 소자로써 매우 유망한 대안으로 부상하고 있다[2]. 또한 멤리스터 제작은 기존 CMOS 소자 위에서 수직 적층으로 가능하기 때문에 CMOS 회로와 혼합하여사용하는 것도 가능하다[3], [4].

기존의 DRAM과 FLASH 등의 외장용 메모리에 대한 대안으로 부상하고 있는 내장형 메모리인 멤리스터의 동 작 특성을 예측하고 회로를 보다 정확하고 효율적으로 설계하여 분석하기 위해서는 멤리스터 소자를 정확하게 모델링하는 것이 중요하다. 또한 많은 개 수의 멤리스터 셀을 어레이로 만들 경우에 어레이 회로의 시뮬레이션 시간을 줄이기 위해서 가급적 멤리스터 소자의 동작을 콤팩트하게 모델링을 하는 것이 필요하다[5]-[7]. 콤팩트 한 모델링은 회로 설계와 시뮬레이션 시간을 단축할 수 있으므로 보다 효율적인 시스템 설계를 가능하게 한다. 물 론 멤리스터를 단순한 저항으로 모델링하여 시뮬레이션 시간을 매우 짧게 할 수도 있지만 멤리스터의 dynamics 를 고려하지 않는다면 프로그래밍 펄스의 인가에 의한 멤리스터 특성의 시간적인 변화를 관찰할 수 없으므로 멤리스터의 read와 write 동작의 정확한 분석이 불가능 하게 된다. 따라서 멤리스터의 DC 전류-전압 특성과 transient dynamics의 정확하면서 콤팩트한 모델링은 멤리스터 기반 메모리 회로의 최적 설계에 필수적이다.

기존의 멤리스터 모델을 검토해보면, 물리적인 특성을 구체적으로 모델링을 하는 물성 기반 모델링을 먼저 찾아볼 수 있는데, 이 경우에는 일반적으로 수식이 매우 복잡하기 때문에 한 개의 소자의 시뮬레이션을 할 때에서는 큰 문제가 없지만 여러 개의 소자로 이루어진 어레이회로를 시뮬레이션할 때에는 시뮬레이션 시간이 매우 길어지게 되므로 멤리스터 신경망과 같이 복잡한 멤리스터-CMOS 혼합회로의 시뮬레이션에는 적당하지 않다[6], [8], [9].

위에서 설명한 이유 때문에 본 논문에서는 물성 기반 멤리스터 모델보다는 멤리스터의 전류-전압의 butterfly 특성과 transient dynamics를 간단한 수식으로 나타낼 수 있도록 개발된 멤리스터 behavioral model을 기반으로 시뮬레이션 시간 단축을 할 수 있는 모델을 개발하려고 한다[10]-[12]. 기존에 개발된 멤리스터 behavioral model은 오늘날까지 매우 광범위하게 여러 분야에서 사용되고 있고, 특히 Verilog-A로 구현하기가 용이하기 때문에 회로 시뮬3레이션에서 많이 사용되고 있다[12]. 기존의 behavioral model에서 transient dynamics를 많이 단순화한 모델도 연구되었으나, 멤리스터의 상태변수를 포함한 dynamic equation을 지나치게 단순화하여 멤리스터 소자의 종류에 따라서 모델링의 정확도가많이 저하될 수 있기 때문에 본 논문에서는 그 모델을 고려하지는 않기로 하였다[13].

본 논문에서는 멤리스터-CMOS 혼합회로 시뮬레이션 시간을 단축하면서도 모델의 정확도를 유지할 수 있는, 멤리스터의 DC 전류-전압 특성과 transient dynamics를 포함하는 정확하면서 동시에 콤팩트한 모델을 제안하고자 한다. 또한 모델의 실용성을 제고하기 위해서 본 논문의 모델에서 사용된 파라미터 추출의 과정을 순서도로 구성하여 자동화할 수 있게 하려고 한다. 또한 제안한 모델을 회로 시뮬레이션 소프트웨어에 구현하기 위해서 Verilog-A를 이용해 프로그램하고 이를 상용 회로 시뮬레이터를 이용하여 시뮬레이션을 수행하여 제안된 모델의 유용성을 검증한다. 본 논문에서 제안하는 멤리스터의 실용적인 모델의 우수성을 나타내기 위해서, 기존의 멤리스터 소자 모델과 시뮬레이션 시간을 비교하여 본논문에서 제안하는 멤리스터 모델이 시뮬레이션 시간을 단축할 수 있음을 보이려고 한다.

#### Ⅱ. 본론

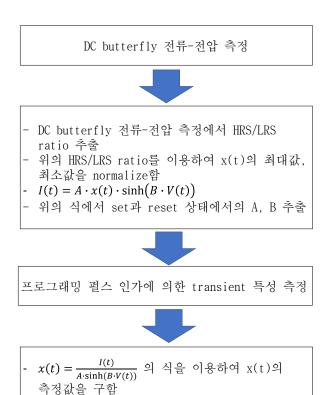

그림 1은 멤리스터 모델링을 위한 순서도이다.

$$I(t) = A \cdot x(t) \cdot \sinh(B \cdot V(t)), V(t) > 0 \quad (1)$$

식(1)은 멤리스터 모델링을 위한 1번 식으로 x(t)는 멤리스터의 상태변수이며 DC 측정에서는 x(t)=1로 한다. I(t)와 V(t)는 각각 멤리스터에 흐르는 전류와 이때 인가한 전압을 나타내며 A, B는 피팅 파라미터를 나타낸다.

$$\frac{dx(t)}{dt} = g(V(t)) \tag{2}$$

$$g(V(t)) = C \cdot \exp(V(t)) \cdot \exp(-D \cdot x(t))$$

(3)

식(2)는 멤리스터의 transient 변화를 나타낸 식으로 식(3)에 정의되어 있다. 식(3)은 시간 변화에 따른 멤리

Fig. 1. Flowchart for compact memristor model. 그림 1. 콤팩트한 멤리스터의 모델링을 위한 순서도.

$-g(V(t)) = C \cdot \exp(V(t)) \cdot \exp(-D \cdot x(t))$

- 위의 식을 이용하여 dx(t)/dt versus x(t)

아래의 식으로 근사함

plot으로 부터 C와 D를 구함

위의 x(t) versus # of pulses의 plot 으로 부터  $\frac{dx(t)}{t^2}$  를 구하고 이를 x(t)에 대해서 plot

위의 그래프로부터 dx(t)/dt와 x(t)의 관계를

스터의 transient 특성 변화로 이때 V(t)는 읽기 전압이다. C는 dx(t)/dt의 크기를 나타내는 파라미터이며, D는 시간이 지날수록 멤리스터의 transient 변화가 줄어드는 과정을 나타내기 위한 파라미터이다.

멤리스터 모델링을 위한 첫 번째 순서는 멤리스터의 DC 버터플라이(butterfly) 특성을 측정한 뒤 HRS와 LRS의 비를 계산하고, 이로부터 x(t)의 최대, 최솟값을 정규화한다. 그런 다음 측정된 버터플라이 커브를 낮은 오차로 가장 유사하게 나타내는 파라미터 A, B를 식 (1)을 이용하여 추출한다[11]. 위 과정에서 A, B는 버터플라이 커브의 모양을 나타내는 피팅 파라미터이다. 여기에서 V(t)는 멤리스터에 인가한 전압이다.

다음 transient 특성을 측정한 뒤 DC 측정에서 구한 A, B와 식(1)을 이용해 측정 x(t)를 구한다. 위 식에서 의 V(t)는 읽기 전압이다. 측정 x(t)로부터 dx(t)/dt를 구하고 이를 x(t)에 대해 그린다. 다음 위 그래프로부터

dx(t)/dt와 x(t)의 관계를 식(3)으로 근사하고, dx(t)/dt와 x(t)의 그래프로부터 C와 D를 구한다. 멤리스터의 transient 특성상 지수적으로 증가하며 증가량은 점차 줄어들면서 saturation 된다. 따라서 exponential 함수로 멤리스터의 모델링이 가능하다.

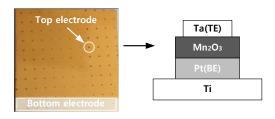

그림 2는 실제 실험에 사용된 멤리스터 소자를 나타낸다. 왼쪽 그림에서 어두운 점 부분이 멤리스터의 상부 전국(top electrode)이며 흰색 부분은 하부 전국(bottom electrode)이다. 멤리스터 소자는 100개의 서로 다른 소자가 하부 전극을 공유한다. 두 개의 전극 사이의 절연체물질은  $Mn_2O_3$ 를 사용했으며 박막 두께는 80nm, 상부전극은 Ta를 사용했으며 박막 두께는 100nm이다. 셀의지름은 500m이며 그림 2의 오른쪽 그림은 제작된 멤리스터 소자의 단면을 보인다[8].

Fig. 2.  $Ta/Mn_2O_3/Pt/Ti$  stacked memristor devices. Ta thickness is 100nm,  $Mn_2O_3$  thickness is 80nm, cell's diameter is 500 $\mu$ m [14].

그림 2.  $Ta/Mn_2O_3/Pt/Ti$  적층된 멤리스터 소자. Ta 두께는 100nm,  $Mn_2O_3$ 두께는 80nm, 셀의 지름은  $500\mu$ m[14]

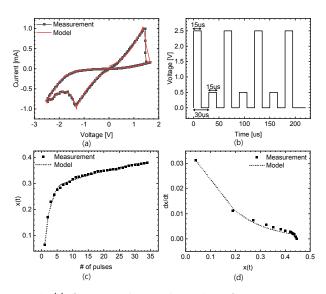

그림 3. (a)는 멤리스터의 DC 전류-전압 특성을 나타 내는 버터플라이 커브를 보여주는 그래프이다. 이 그래 프를 통해 식(1)의 모델링 함수에서 A와 B값을 추출한 다. 그림 3. (b)는 멤리스터의 transient 특성을 확인하 기 위해 멤리스터에 인가한 전압 펄스이다. 쓰기 전압은 2.5V이며 읽기 전압은 0.5V이다. 멤리스터에 인가한 전 압 펄스는 square-waveform voltage 펄스로 이를 사 용한 이유는 간단하고 명확한 형태를 가지고 있어 다루 기 쉽고 분석하기 용이하다. 또한, 프로그래밍하는 동안 고/저 전압 레벨을 유지하는 시간을 제한적으로 사용하 므로 전력 소비가 상대적으로 낮기 때문에 에너지 효율 적인 멤리스터 프로그래밍을 가능하게 한다[15]. 그림 3. (c)는 측정 x(t)와 모델 x(t)를 나타낸다. 측정 x(t)는 DC 측정에서 식(1)로 A, B를 구한 다음 transient 측정을 한 뒤 식(1)을 x(t)에 대해 정리한 다음 계산한 결과이다. 모델 x(t)는 식(2)를 통해 구한다. 그림 3. (d)는 측정 dx(t)/dt와 모델의 dx(t)/dt를 나타내며 모델의 dx(t)/dt 는 식(3)을 통해 구한다. 측정 dx(t)/dt는 측정 x(t)의 미 분 결과이다.

Fig. 3. (a) Current-Voltage relationship of memristor A. (b) Programming and read pulses [11], [15]. (c) Measured and modeled x(t) with increasing # of pulses. (d) Measured and modeled dx/x(t) with increasing x(t).

그림 3. (a) 멤리스터 소자 A의 전류-전압 특성. (b) 프로그래밍과 읽기 펄스 [11], [15]. (c) 전압 펄스 개 수의 증가에 따른 측정된 x(t)와 모델 x(t). (d) x(t)의 증가에 따른 측정된 dx(t)/dt 와 모델 dx(t)/dt

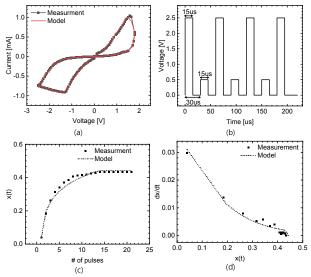

그림 4의 측정에 사용된 소자는 그림 3의 측정에 사용된 소자는 서로 다른 소자이다. 그림 4. (a)는 DC 버터플라이 특성과 피팅 결과를 나타낸 것이며 이 그래프로부터 식(1)의 파라미터 A, B를 추출한다. 그림 4 (b)는소자의 transient 특성을 확인하기 위해 소자에 인가한전압 펄스이며 쓰기 전압은 2.5V, 읽기 전압은 0.5V이다. 그림 4. (c)는 측정 x(t)와 모델 x(t)를 나타내며 측정x(t)는 DC 측정과 transient 측정을 한 뒤 식(1)을 통해구하며모델 x(t)는 식(2)를 통해구한다. 그림 4. (d)는 측정 dx(t)/dt와모델의 dx(t)/dt를 나타낸다. 그림을 보면 측정을 모델이 잘 따라가는 것을 확인할 수 있다.

Xiaoping Wang et al. 에서 멤리스터의 모델을 보면,  $\frac{dx}{dt} = M_p e^{a1\,Vpulse}$ 로 정의한다. 하지만 멤리스터의 transient 특성상 시간이 지나면서 컨덕턴스 변화량이줄어드는 즉 컨덕턴스의 크기가 점차 saturation 되는 dynamic 특성을 포함해야 한다. 따라서 본 논문에서는 transient 특성의 saturation 동작을 더 정확하게 반영하는 모델을 제안한다[13].

Fig. 4. (a) Current-Voltage relationship of memristor B. (b) Programming and read pulses [11], [15]. (c) Measured and modeled x(t) with increasing # of pulses. (d) Measured and modeled dx/x(t) with increasing x(t).

그림 4. (a) 멤리스터 소자 B의 전류-전압 특성. (b) 프로그래밍 과 read 펄스 [11], [15]. (c) Pulse 개 수의 증가에 따른 측정된 x(t)와 모델 x(t). (d) x(t)의 증가에 따른 측정된 dx(t)/dt 와 모델 dx(t)/dt

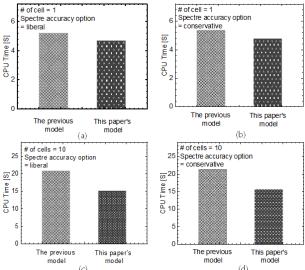

그림 5는 이전 모델과 본 연구에서 제안한 모델을 시뮬 레이션 결과이다[11]. 시뮬레이션은 CADENCE SPECTRE Verilog-A 환경에서 진행했다. 그림 5. (a)는 셀 한 개 에 대해 펄스 500개를 인가하고 이전 모델과 본 논문의 모델을 liberal 환경에서 시뮬레이션하여 비교한 결과로 이전 모델 5.22초, 본 논문의 모델 4.7초로 본 논문의 모델이 더 빠른 것을 확인할 수 있다. 그림 5. (b)는 셀 한 개에 대해 conservative 환경에서 시뮬레이션 시간 을 측정한 결과로 이전 모델은 5.36초가 걸리는 반면 본 논문의 모델은 4.8초로 나타났다. 그림 5. (c)와 (d)에서 는 셀 10개에 대해 liberal 환경과 conservative 환경에 서 실행 시간을 측정한 결과로 이전 모델 20.88, 21.5초 이며 본 논문의 모델 15.2, 16.4초로 차이가 크게 나는 것을 확인할 수 있다. 셀의 수가 증가할수록 시뮬레이션 시간 차이가 더 커지는 것을 확인했으며 본 논문의 모델 을 어레이로 구성하고 시뮬레이션할 때 시뮬레이션 시간 을 대폭 줄일 수 있을 것으로 예상된다.

표 1은 이전 모델과 본 논문의 모델의 정확도와 시뮬레이션 시간을 비교한 것이다. 표를 보면 이전 모델 95.2%며 본 논문의 모델은 96.7%로 비슷한 정확도를보이지만 시뮬레이션 시간은 더 빠른 것을 확인할 수 있다. 이는 본 논문의 제안한 모델이 모델의 정확도를 손상

하지 않으면서 수식을 단순화함으로써 모델의 계산 시간을 줄일 수 있기 때문이다. 따라서 표 1로부터 본 논문의모델이 정확도 측면에서도 이전 모델에 비해 높으며 시뮬레이션 속도 또한 더 빨라 실용적인 모델로 활용될 수있을 것으로 예상된다. 표 1에서 비교한 이전의 멤리스터소자의 모델은 멤리스터 소자의 모델로 제일 많이 사용되는 behavioral model을 사용했다[10]. 이 behavioral model을 이용하여 그 후에 많은 파생 모델이 개발되어왔으나 본 연구에서는 비교하려고 하는 시뮬레이션 시간이 단축되는 효과는 거의 없기 때문에 본 연구에서의 비교 상대로는 후속 파생 모델을 사용하지 않고 원래의 모델을 사용하여 시뮬레이션 시간을 비교하였다[11].

Fig. 5. (a) Comparison of simulation time of the previous model and this paper's model (# of cells=1 and Spectre accuracy option=liberal). (b) Comparison of simulation time of the previous model and this paper's model (# of cells=1 and Spectre accuracy option=conservative). (c) Comparison of simulation time of the previous model and this paper's model (# of cells=10 and Spectre accuracy option=liberal). (d) Comparison of simulation time of the previous model and this paper's model (# of cells=10 and Spectre accuracy option=conservative).

그림 5. (a) 이전 모델과 본 논문의 모델의 시뮬레이션 시간 비교 (# of cells=1 and Spectre accuracy option=liberal).

(b) 이전 모델과 본 논문의 모델의 시뮬레이션 시간 비교 (# of cells=1 and Spectre accuracy option=conservative). (c) 이전 모델과 본 논문의 모델의 시뮬레이션 시간 비교 (# of cells=10 and Spectre accuracy option=liberal). (d) 이전 모델과 본 논문의 모델의 시뮬레이션 시간 비교 (# of cells=10 and Spectre accuracy option=conservative)

Table 1. Comparison of simulation time and accuracy between the previous model and this paper's model.

표 1. 이전 모델과 본 논문의 모델의 시뮬레이션 시간과 정확도 비교.

|          | Previous model | This paper's model |

|----------|----------------|--------------------|

| Accuracy | 95.2%          | 96.7%              |

| Speed    | 21.5s          | 16.4s              |

## Ⅲ. 결론

멤리스터 소자의 콤팩트한 모델링은 회로 설계와 시뮬레이션 시간을 단축할 수 있으므로 시스템 설계를 효율적으로 수행할 수 있게 한다. 물론 멤리스터를 단순한 저항으로 모델링하여 시뮬레이션 시간을 매우 짧게 할 수도 있지만 멤리스터의 dynamics를 고려하지 않는다면 프로그래밍 전압 펄스의 인가에 의한 멤리스터 특성의시간적인 변화를 관찰할 수 없으므로 멤리스터의 읽기와쓰기 동작의 정확한 분석이 불가능하게 된다. 따라서 멤리스터의 DC 전류-전압 특성과 transient dynamics의 정확하면서 콤팩트한 모델링은 멤리스터 기반 메모리 회로 설계의 최적화에 필수적이다.

본 논문에서는 위에서 언급한 필요성을 반영하여 멤리스터의 DC 전류-전압 특성과 transient dynamics를 포함하는 정확하면서 동시에 콤팩트한 모델을 제안하고 모델에서 사용된 파라미터 추출의 과정을 설명하였다. 또한 제안한 모델을 회로 시뮬레이션 소프트웨어에 구현하기 위해서 Verilog-A를 이용해 프로그램하였고 이를 상용 회로 시뮬레이터를 이용하여 시뮬레이션 하여 제안된 모델의 유용성을 검증하였다. 또한 기존 멤리스터 모델과 본 논문의 모델의 시뮬레이션 시간을 비교했을 때본 논문의 모델의 시뮬레이션 시간을 비교했을 때본 논문의 모델의 이용해서 회로 시뮬레이션을 수행하면이전의 모델에 비해 시뮬레이션 시간이 27% 정도 단축이 될 수 있음을 확인하였다. 본 논문에서 제안한 멤리스터 콤팩트 모델은 특히 엣지 인텔리젼스 하드웨어의 설계 등에서 시뮬레이션 시간을 단축하여 시스템 설계 시간을 줄이는 데 기여할 수 있을 것으로 기대된다.

## References

[1] D. B. Strukov *et al*, "The missing memristor found," *Nature*, Vol.453, No. *7191*, pp.80-83, 2008. [2] K. Moon *et al*, "RRAM-based synapse devices

for neuromorphic systems," *Faraday Discuss.*, Vol. 213, pp.421-451, 2019.

[3] J. Hazra *et al*, "Improving the memory window/resistance variability trade-off for 65nm CMOS integrated HfO 2 based nanoscale RRAM devices," in *2019 IEEE International Integrated Reliability Workshop (IIRW)*, 2019.

DOI: 10.1109/IIRW47491.2019.8989872

[4] V. Saxena, "Mixed-signal neuromorphic computing circuits using hybrid CMOS-RRAM integration," *IEEE Transactions on Circuits and Systems II: Express Briefs*, Vol.68, No.2, pp.581-586, 2020.

DOI: 10.1109/TCSII.2020.3048034

[5] P. Chen and S. Yu, "Compact modeling of RRAM devices and its applications in 1T1R and 1S1R array design," *IEEE Trans. Electron Devices*, Vol.62, No.12, pp.4022-4028, 2015.

DOI: 10.1109/TED.2015.2492421

[6] P. Huang *et al*, "A physics-based compact model of metal-oxide-based RRAM DC and AC operations," *IEEE Trans. Electron Devices*, Vol.60, No.12, pp.4090-4097, 2013.

DOI: 10.1109/TED.2013.2287755

[7] Z. Jiang *et al*, "Verilog-A compact model for oxide-based resistive random access memory (RRAM)," in *2014 International Conference on Simulation of Semiconductor Processes and Devices (SISPAD)*, 2014.

DOI: 10.1109/SISPAD.2014.6931558

[8] A. Lekshmi Jagath *et al*, "Insight into physicsbased RRAM models-review," *The Journal of Engineering*, Vol.2019, No.7, pp.4644-4652, 2019. DOI: 10.1049/joe.2018.5234

[9] Y. Zhao *et al*, "A compact model for drift and diffusion memristor applied in neuron circuits design," *IEEE Trans. Electron Devices*, Vol.65, No.10, pp.4290-4296, 2018.

DOI: 10.1109/TED.2018.2865225

[10] C. Yakopcic *et al*, "A memristor device model," *IEEE Electron Device Lett.*, Vol.32, No.10, pp.1436-1438, 2011. DOI: 10.1109/LED.2011.2163292

[11] S. N. Truong *et al*, "New pulse amplitude modulation for fine tuning of memristor synapses,"

Microelectron. J., Vol.55, pp.162-168, 2016.

DOI: 10.1016/j.mejo.2016.07.010

[12] F. O. Rziga *et al*, "An efficient Verilog-A memristor model implementation: simulation and application," *Journal of Computational Electronics*, Vol. 18, pp. 1055-1064, 2019.

DOI: 10.1007/s10825-019-01357-9

[13] X. Wang, B. Xu and L. Chen, "Efficient memristor model implementation for simulation and application," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, Vol.36, No.7, pp.1226-1230, 2017.

DOI: 10.1109/TCAD.2017.2648844

[14] M. K. Yang and G. H. Kim, "Post-Annealing Effect on Resistive Switching Performance of a Ta/Mn2O3/Pt/Ti Stacked Device," *Physica Status Solidi (RRL)-Rapid Research Letters,* Vol.12, No.6, pp.1800031, 2018. DOI: 10.1002/pssr.201800031 [15] K. V. Pham *et al,* "Asymmetrical training scheme of binary-memristor-crossbar-based neural networks for energy-efficient edge-computing nanoscale systems," *Micromachines,* Vol.10, No.2, p.141, 2019. DOI: 10.3390/mi10020141

#### **BIOGRAPHY**

## Seung-Myeong Cho (Member)

2023: BS degree in Electrical Engineering, Kookmin University. 2023~current: MS degree in Electrial Engineering, Kookmin University.

#### Seokjin Oh (Member)

2021: BS degree in Electrical Engineering, Kookmin University. 2021~current: MS degree in electrical Engineering, Kookmin University.

## Rina Yoon (Member)

2023: BS degree in Electrical Engineering, Kookmin University. 2023~current: MS degree in electrical Engineering, Kookmin University.

## Kyeong-Sik Min (Member)

1991 : BS degree in Electrical Engineering, Korea University. 1993 : MS degree in Electrical

Engineering, KAIST.

1997: PhD degree in Electircal

Engineering, KAIST.

1997~2001: Research Engineer, Hynix Semiconductor

Inc.

2001~2002: Research Engineer, University of Tokyo.

2002~2022: Professor, Kookmin University.