103

ISSN: 1226-7244 (Print) ISSN: 2288-243X (Online) 논문번호 23-01-15

# 1200V급 SiC 기반 트렌치 게이트 MOSFET의 전기적 특성에 관한 연구

# The Electrical Characteristics of 1200V Trench Gate MOSFET Based on SiC

김 유 림<sup>\*</sup>, 이 동 현<sup>\*</sup>, 김 민 서<sup>\*</sup>, 최 진 우<sup>\*</sup>, 강 이 구<sup>\*\*</sup>

Yu Rim Kim<sup>\*</sup>, Dong Hyeon Lee<sup>\*</sup>, Min Seo Kim<sup>\*</sup>, Jin Woo Choi<sup>\*</sup>, Ey Goo Kang<sup>\*</sup>

#### **Abstract**

This research was carried out experiments with changing processes and design parameters to optimally design a SiC-based 1200V power MOSFET, and then, essential electrical characteristics were derived. In order to secure the excellence of the trench gate type SiC power MOSFET device to be designed, electrical characteristics were derived by designing it under conditions such as planner gate SiC power MOSFET, and it was compared with the trench gate type SiC power MOSFET device. As a result of the comparative analysis, the on-resistance while maintaining the yield voltage was 1,840m2, for planner gate power MOSFET and to 40m2 for trench gate power MOSFET, respectively, indicating characteristics more than 40 times better. It was judged that excellent results were derived because the temperature resistance directly affects energy efficiency. It is predicted that the devices optimized through this experiment can sufficiently replace the IGBT devices generally used in 1200V class, and that since the SiC devices are wide band gap devices, they will be widely used to apply semiconductors for vehicles using devices with excellent thermal characteristics.

#### **Ω** Ω

본 연구에서는 SiC 기반의 1200V급 전력 MOSFET을 최적 설계하기 위하여 공정 및 설계 파라미터를 변화시키면서 실험을 수행한 후, 필수적인 전기적 특성을 도출하였다. 그리고 최종적으로 설계하고자 하는 트렌치 게이트형 SiC 전력 MOSFET 소자의 우수성을 확보하기 위하여 플래너 게이트 SiC 전력 MOSFET을 같은 조건하에 설계하여 전기적인 특성을 도출하여 트렌치 게이트형 SiC 전력 MOSFET 소자와 비교 분석을 하였다. 비교 분석한 결과, 항복전압을 그대로 유지한 상태에서 온 저항은 각각 플래너게이트 전력 MOSFET은 1,840m 2, 트렌치 게이트 전력 MOSFET는 40m 2으로 약 40배 이상 우수한 특성을 도출하였다. 온 저항은에너지 효율에 직접적인 영향을 끼치는 바에너지 효율에 있어 우수한 결과를 도출한 것으로 판단되었다. 본 실험을 통해 최적화된소자는 1200V급에 일반적으로 사용되었던 IGBT소자를 충분히 대체 가능한 것으로 판단되었다.

Key words: SiC Materials, Wide Band Gap, Power MOSFET, On Resistance, Power Devices and ICs

E-mail: keg@kdu.ac.kr, Tel: +82-43-879-3648

\* Acknowledgment

This work was supported by the Industrial Technology Evaluation and Planning Institute's Material Parts Project (20022501) and the Industrial Technology Promotion Agency's Industrial Innovation Talent Fostering Project (P0017308)

Manuscript received Feb. 22, 2023; revised Mar. 12, 2023; accepted Mar. 20, 2023.

This is an Open-Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License(http://creativecommons.org/licenses/by-nc/3.0) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

<sup>\*</sup> Master's degree, Dept. of Energy IT, Far East University

<sup>★</sup> Corresponding author

#### 1. 서론

현재까지 실리콘 기반 소자의 물성적 한계로 인해 발전속도가 떨어지고 있는 추세이다. 이러한 실리콘 전력반도체가 가진 한계상황을 대체하기 위해 만든 차세대 전력반도체인 탄화규소(SiC) 소재기반 전력반도체이다. SiC 기반의 전력반도체 소자는 실리콘 전력반도체에 비해 3배정도의 넒은 밴드 갭과 2배 정도의 우수한 열전도성, 10배의 높은 파괴전계강도, 2배의 높은 전자 포화속도를지나고 있다[1-2].

1200V급 플래너 게이트 SiC Power MOSFET은 JFET 의 영향으로 인해 온 저항이 높다는 단점과 소형화 및 경량화에 불리한 면이 있다. 이러한 단점을 보완하기 위해본 논문에서는 1200V급 SiC 기반의 트렌치 게이트 전력 MOSFET을 제안하였으며, 실험을 통해 소자 및 공정파라미터를 최적화하였다. 전기적인 특성을 분석한 결과 소자가 정상적으로 동작을 하고 있음을 확인하였다.

#### Ⅱ. 본론

## 1. 플래너 게이트 SiC MOSFET 및 트렌치 게이트 SiC 전력 MOSFET의 구조 및 동작원리

기존 실리콘 기반의 플래너 게이트 MOSFET에서는 발전된 형태는 JFET영역이 제거된 구조인 트렌치 게이트 전력 MOSFET이다. 본 구조로 발전된 이유는 온 저항에 깊게 영향을 미치는 JFET 영역이 트렌이 영역으로 대체되는데, 이때 항복전압은 유지하면서 온 저항을 효율적으로 감소시키기 때문이다. 최근에 가장 많이 활용이 되는 용량은 600V급이다. 현재 자동차 및 공장용으로 활용되는 전력반도체 소자는 1200V급인데, 이때 주로 활용되는 소자는 실리콘 기반 소자인 전력 IGBT 소자이다. 이 소자를 단순한 SiC 기반의 전력 MOSFET 소자로 대체하기 위해서는 기존 SiC 웨이퍼의 에피층의 깊이보다 2배이상 필요하다. 따라서 에피 성장기술이 필수적으로 필요하며, 깊이가 깊을수록 온 저항이 커지므로 온 저항을 줄이기 위해서는 트렌치 게이트를 형성하는 것도 효율적이라 할 수 있다.

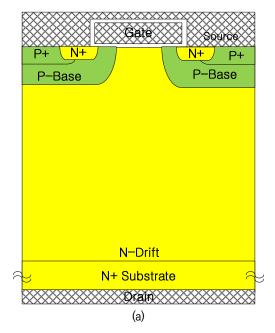

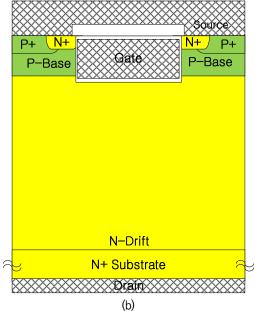

그림 1은 1200V급 플래너 게이트 및 트렌치 게이트 SiC 전력 MOSFET의 단면도를 나타내고 있다.

SiC 전력 MOSFET의 동작은 게이트의 형태와 상관없이 공통된 동작을 하게 되는데, 게이트 단자에 문턱전압이상을 인가하면 채널이 형성되고, Vds 전압을 인가하게되면, 그 채널을 통해 전류가 흐르기 시작한다. 이때 흐

르는 전류상에 형성되는 저항이 온 저항이다. 알려진 바와 같이 온 저항은 소자의 에너지 효율을 결정하는 중요한 전기적인 특성 중 하나이다.

항복전압은 게이트전압에 0V를 인가하고, 소오스 전압을 접지상태로 두고 드레인 전압을 상승시켜 측정하는 전기적인 특성이다. 1200V급 플래너 게이트 및 트렌치

Fig. 1. The structures of 1200V class planar gate Power MOSFET and proposed Trench gate Power MOSFET (a) Planar gate Power MOSFET (b) Trench gate Power MOSFET.

그림 1. 1200V급 SiC 플래너 게이트 전력 MOSFET와 트렌치 게이트 전력 MOSFET (a) 플래너 게이트 전력 MOSFET (b)트렌치 게이트 전력 MOSFET 게이트 SiC 전력 MOSFET 두 소자 모두 항복전압을 유지한 후 온 저항 등의 특성을 향상시키는 방향으로 설계하고 있다.

그림 1에서 보는 것처럼, 트렌치 게이트 전력 MOSFET은 온 저항에 큰 부분을 차지하는 JFET 영역이 사라지기 때문에 플래너 게이트 전력 MOSFET보다 온 저항을 크게 줄일 수 있는 장점을 가지고 있다. 본 논문에서는 이러한 방향으로 설계 및 공정파라미터를 설정하여 실험을 진행하였다.

#### 2. 실험을 위한 설계 및 공정파라미터의 설정

실험을 수행하기 위한 1200V급 플래너 게이트 및 트 렌치 게이트 SiC 전력 MOSFE 기반의 실험을 수행하기 위한 기본적인 공정 및 설계 파라미터를 표 1에 제시하고 있다.

Table 1. Process and design parameters of 1200V class SiC Power MOSFETs.

표 1. 기반 실험을 위한 SiC 전력 MOSFET의 공정 및 설계 파라미터

| Process and design parameters            | value                             |

|------------------------------------------|-----------------------------------|

| Cell Pitch                               | 8μm                               |

| Depth of Drift Layer                     | 13μm                              |

| Doping Concentration of substrate        | $1 \times 10^{19} \text{cm}^{-3}$ |

| Doping Concentration of Epi layer        | $4 \times 10^{15} \text{cm}^{-3}$ |

| Doping Concentration of P-base           | $5 \times 10^{16} \text{cm}^{-3}$ |

| Doping Concentration of P+ Drain Region  | $1 \times 10^{19} \text{cm}^{-3}$ |

| Doping Concentration of N+ Source Region | $1 \times 10^{18} \text{cm}^{-3}$ |

| Gate width                               | 2μm                               |

표 1에 있는 공정 및 설계 파라미터를 바탕으로 항복 전압과 온 저항에 영향을 끼치는 에피층의 깊이 및 농도를 변화시키면서 항복전압과 온 저항의 전기적인 특성에 관련된 실험을 수행하였다. 또한 문턱전압에 영향을 끼 치는 P-base영역의 농도도 변화를 시키면서 실험을 수 행하였다. 기타 소자의 전기적인 특성에 영향을 끼칠 수 있는 변수에 대한 부분도 고려하여, 실험을 진행하였고 SiC 전력 소자의 문제점으로 지적되고 있는 누설전류 특 성을 개선하기 위한 게이트 산화막 두께는 1000Å으로 설정하였다. 전기적인 특성을 수행하기 전에 구조를 설 정하기 위한 공정시뮬레이션을 통해서 산화막 공정을 최 적화하고자 하였다.

#### 3. 1200V급 SiC 전력 MOSFET 전기적 특성 실험 결과

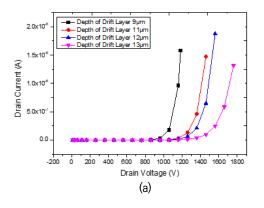

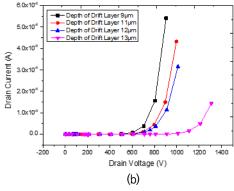

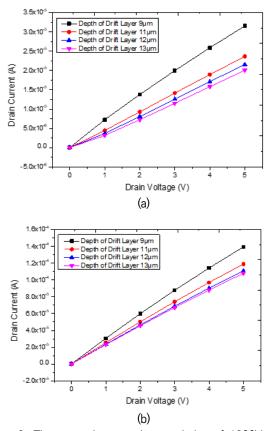

본 절에서는 파라미터를 설정하고 공정 및 설계 시뮬레이션을 통해서 얻은 전기적인 특성에 대해서 고찰하고자 하였다. 우선 그림 2에서는 플래너 및 트렌치 게이트 SiC 전력 MOSFET소자의 항복전압 특성을 보여주고 있다. 그림에서 나타낸 바와 같이 드리프트 층의 깊이에 따른 항복전압 특성을 보여주고 있는데, 예상한 바와 같이 깊이가 깊어질수록 항복전압은 증가하고 있는 것을 볼수 있다. 두소자 모두 13㎞ 였을 때 1200V를 나타내고 있는데, 실제 공정을 진행 할때는 10㎞ 내외에서 설계하면 될 수 있을 것으로 판단된다.

그 다음으로 그림 3에서는 드리프트 층의 깊이에 따른 온저항 특성을 보여주고 있다. 그림에서 나타낸 바와 같 이 깊이가 깊을수록 온 저항은 커지는 것을 볼 수 있고, 작을수록 온 저항은 작아지는 것을 알 수 있다.

Fig. 2. The breakdown voltage characteristics of 1200V class SiC Power MOSFETs (a)Planar gate Power MOSFET (b)Trench gate Power MOSFET.

그림 2. 1200V SiC Power MOSFET의 항복전압 특성 (a) 플래너 게이트 전력 MOSFET (b) 트렌치 게이트 전력 MOSFET

그림 2와 3을 보면 알 수 있듯이 항복전압과 온 저항 특성은 트레이드 오프 특성을 갖는다는 것을 알 수 있으 며, 이후 드리프트 층의 농도에 따른 특성도 같은 경향을 보이는 것을 알 수 있다. 다만, 우선적으로 결정해야 되는 것은 항복전압으로 항복전압을 세팅한 후 적절한 온 저항 특성을 결정해야 할 것으로 생각한다.

Fig. 3. The on resistance characteristics of 1200V class SiC Power MOSFETs (a)Planar gate Power MOSFET (b)Trench gate Power MOSFET.

그림 3. 1200V SiC 전력 MOSFET의 온 저항 특성 (a) 플래너 게이트 전력 MOSFET (b) 트렌치 게이트 전력 MOSFET

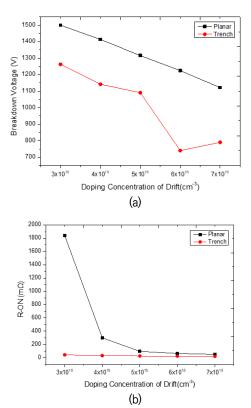

그림 4는 드리프트층의 농도에 따른 두 소자의 전기적인 특성을 비교 분석하여 보여주고 있다. 그림에서 나타낸바와 같이  $3\times10^{15}/\mathrm{cm}^3$ 의 농도에서 SiC 기반의 플래너및 트렌치 게이트 전력 MOSFET의 항복전압 1200V를 유지하고 있다는 것을 알 수 있으며, 특히, 온 저항 특성에 있어서는 해당 농도에서 트렌치게이트 전력 MOSFET소자가 우수한 특성을 갖고 있음을 알수 있다. 이때, 트렌치 게이트 전력 MOSFET소자의 온 저항은  $40\mathrm{m}\,\Omega$ 으로 극히 낮은 저항을 얻어 에너지 효율면에서 매우 적절한 값을 가짐을 알 수 있다. 플래너의 경우  $7\times10^{15}/\mathrm{cm}3$ 일때  $50\mathrm{m}\,\Omega$ 을 얻을 수 있지만, 트레이드 오프 관계인 항복전압을 고려해야하기 때문에 트렌치 구조로 제작하는 것이 바람직하다고 생각할 수 있다.

Fig. 4. the comparison of electrical properties of two devices (a) breakdown voltage characteristics (b) On resistance characteristics.

그림 4. 1200V 플래너 및 트렌치 게이트 SiC 전력 MOSFET의 전기적인 특성 비교 (a) 항복전압 특성 (b) 온 저항 특성

소자의 문턱전압을 15V로 유지하기 위해서 P-base 농도는  $5\sim6\times10^{16}/\text{cm}^3$ 로 적절히 유지하면 될 것으로 판단되었다.

#### Ⅲ. 결론

본 연구에서는 SiC 기반의 1200V급 전력 MOSFET을 최적설계하기 위하여 공정 및 설계 파라미터를 변화시키면서 실험을 수행한 후, 필수적인 전기적 특성을 도출하였다. 그리고 최종적으로 설계하고자 하는 트렌치 게이트형 SiC 전력 MOSFET 소자의 우수성을 확보하기 위하여 플래너 게이트 SiC 전력 MOSFET 같은 조건하에설계하여 전기적인 특성을 도출하여 트렌치 게이트형 SiC 전력 MOSFET 소자와 비교 분석을 하였다. 비교 분석한 결과, 항복전압을 그대로 유지한 상태에서 온 저항은 각각 플래너게이트 전력 MOSFET은 1,840mû, 트렌치 게이트 전력 MOSFET는 40mû으로 약 40배이상우수한 특성을 도출하였다. 온 저항은 에너지 효율에 직접적인 영향을 끼치는 바 우수한 결과를 도출한 것으로

판단되었다. 본 실험을 통해 최적화 된 소자는 1200V급에 일반적으로 사용되었던 IGBT소자를 충분히 대체가능한 것으로 판단되며, SiC 소자는 와이드밴드갭 소자이기때문에 열특성이 우수한 소자가 쓰이는 자동차용 반도체적용에 크게 활용될 것으로 전망한다.

#### References

[1] Mulpuri V. Rao, J. Tucker, O. W. Holland, N. Papanicolaou, P. H. Chi, J. W. Kretchmer and M. Ghezzo, "Donor Ion-Implantation Doping into SiC," *Journal of Electronic Materials*, Vol.28, No.3, pp.334-340, 1999.

DOI: 10.1007/s11664-999-0036-8

[2] G. J. Phelps, "Dopant ion implantationsimulations in 4H-Silicon Carbide," *Modelling and Simulation In Materials Science And Engineering*, Vol.12, pp.1139-1146, 2004.

DOI: 10.1088/0965-0393/12/6/008

[3] Atul Mahajan, and B. J Skromme, "Designand optimization of junction termination extension (JTE) for 4H-SiC high voltage Schottky diodes," *Solid State Electronics*, Vol.49, pp.945-955, 2005. DOI: 10.1016/j.sse.2005.03.020

[4] David C. Sheridan, Guofu Niu, and John D. Cressler, "Design of single and multiple zonejunction termination extension structures for SiCpower devices," *Solid State Electronics*, Vol.45, pp.1659-1664, 2001. DOI: 10.1016/S0038-1101(01)00052-1 [5] Reza Ghandi, Benedetto Buono, Martin-Domeij, Gunnar Malm, Carl-Mikael Zetterling, and Mikael Östling, "High-Voltage 4H-SiC PiN Diodes With Etched Junction TerminationExtension," *IEEE Electron Device Letters*, Vol.30, No.11, pp.1170-1172, 2009.

DOI: 10.1109/LED.2009.2030374

[6] D. H. Kim and S. M. Koo, "Effect of P-Emitter length and structure on Asymmetric SiC MOSFET performance," *J. Korean Inst. Electr. Electron. Mater. Eng.*, Vol.33, No.2, pp.83-87, 2020.

DOI: 10.4313/JKEM.2020.33.2.83

[7] J. J. Ahn, K. S. Moon and S. M. Koo, "Optimization of 4H-SiC Vertical MOSFET by current spreading

layer and doping level of epilayer," *J. Korean Inst. Electr. Electron. Mater. Eng.*, Vol.23, No.10, pp.767-770, 2010.

DOI: 10.4313/JKEM.2010.23.10.767

#### BIOGRAPHY

#### Yu Rim Kim (Member)

2022: BS degree in Dept. Energy IT, Far East University.

2022~present: MS degree in Dept. Energy IT, Far East University.

2022~present: Research Student, Dept. Energy IT, Far East University

#### Dong Hyeon Lee (Member)

2018~present: BS degree in Dept. Energy IT, Far East University. 2022~present: Research Student, Dept. Energy IT, Far East University

#### Min Seo Kim (Member)

2019~present: BS degree in Dept. Energy IT, Far East University. 2023~present: Research Student, Dept. Energy IT, Far East University

#### Jin Woo Choi (Member)

2018~present: BS degree in Dept. Energy IT, Far East University. 2023~present: Research Student, Dept. Energy IT, Far East University

### Ey Goo Kang (Member)

1993: BS degree in Electrical Engineering, Korea University.

1995: MS degree in Electrical Engineering, Korea University.

2002: Ph.D degree in Electrical Engineering, Korea University.

2003~present: Professor, Dept. Energy IT, Far East University