J. Korean Inst. Electr. Electron. Mater. Eng.

Vol. 36, No. 1, pp. 23-28 January 2023

DOI: https://doi.org/10.4313/JKEM.2023.36.1.4

ISSN 1226-7945(Print), 2288-3258(Online)

# Through-Silicon Via를 활용한 3D NAND Flash Memory의 전열 어닐링 발열 균일성 개선

손영서, 이광선, 김유진, 박준영⑩

충북대학교 전자공학부

Electro-Thermal Annealing of 3D NAND Flash Memory Using Through-Silicon Via for Improved Heat Distribution

Young-Seo Son, Khwang-Sun Lee, Yu-Jin Kim, and Jun-Young Park School of Electronics Engineering, Chungbuk National University, Cheongju 28644, Korea

(Received September 20, 2022; Revised October 5, 2022; Accepted October 6, 2022)

**Abstract:** This paper demonstrates a novel NAND flash memory structure and annealing configuration including through-silicon via (TSV) inside the silicon substrate to improve annealing efficiency using an electro-thermal annealing (ETA) technique. Compared with the conventional ETA which utilizes WL-to-WL current flow, the proposed annealing method has a higher annealing temperature as well as more uniform heat distribution, because of thermal isolation on the silicon substrate. In addition, it was found that the annealing temperature is related to the electrical and thermal conductivity of the TSV materials. As a result, it is possible to improve the reliability of NAND flash memory. All the results are discussed based on 3-dimensional (3-D) simulations with the aid of the COMSOL simulator.

Keywords: Electro-thermal annealing, Reliability, Simulation, Through-silicon via, 3D NAND flash memory

### 1. 서 론

반도체소자는 크게, 메모리 반도체소자와 시스템반도체소자로 분류된다. 그리고 메모리 반도체소자 중, 데이터를 반 영구적으로 저장할 수 있는 비 휘발성(non-volatile memory, NVM) 소자로는 ONO ( $SiO_2/Si_3N_4/Al_2O_3$ ) gate dielectric을 기반으로 하는 플래시메모리 소자가 대표적이다. 비록, resistive random access memory (RRAM),

☑ Jun-Young Park; junyoung@cbnu.ac.kr Young-Seo Son and Khwang-Sun Lee equally contributed to this

Copyright ©2023 KIEEME. All rights reserved.

work.

This is an Open-Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License (http://creativecommons.org/licenses/by-nc/3.0) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

phase change random access memory (PRAM) 등이 차세대 NVM 소자로써, 꾸준히 제안되고 있으나, 셀 집적도 및 셀 당 비용(bit-cost)을 모두 고려하였을 때, 아직까지는 ONO 기반의 소자가 가장 적합하다고 여겨지고 있다 [1-3].

ONO gate dielectric 기반의 플래시메모리 소자에 데이터를 program하기 위해서는 gate electrode (wordline, WL)에 양의 전압을 인가하여 Si₃N₄ charge trap layer에 전자를 주입시키며, erase를 수행하기 위해서는, 실리콘 기판에 양의 전압을 인가하거나 [4], gate-induced drain leakage (GIDL) 현상을 유발하도록 drain electrode에 높은 전압을 인가한다 [5]. 하지만, 높은 집적도 구현을 위하여, 플래시메모리 소자의 크기가 작아지고셀의 밀도가 높아짐에 따라, short-channel effects (SCEs)로 인한 소자 off-state current (IOFF) 증가 및 셀

신뢰성(retention 및 endurance) 저하라는 부작용이 발생하기 시작하였다.

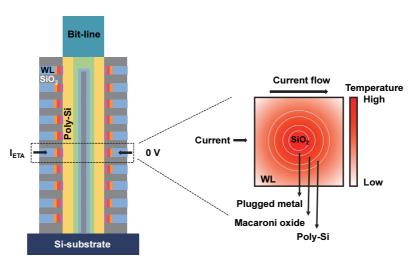

이에, 2007년 Toshiba에서, 3D NAND 플래시메모리 소자가 새로이 제안되었다 [6,7]. 하지만, 3D NAND 플래 시메모리 소자는 효과적으로 SCEs를 억제하였지만, 얇아 진 gate dielectric으로 인한, tunneling oxide 손상 및 신 뢰성 저하를 피할 수 없다. 이러한 신뢰성 저하를 개선하기 위해서는 tunneling oxide와 channel 간 존재하는 interface trap을 줄이는 것이 중요하며, 대표적인 기술로 는 forming gas annealing (FGA) 이 있다 [8]. 하지만, 이 러한 FGA는 금속이나 소자의 도핑 분포의 손상을 초래할 수 있기에, 3D NAND 플래시메모리 만을 위한 새로운 어 닐링 방법을 필요로 하게 되었다. 이에 대한 개선 방법으 로, 전열 어닐링(electro-thermal annealing, ETA) 기술 이 새로이 제안되었는데, 이는 그림 1과 같이, WL-to-WL 에 높은 전류를 인가하여, 메모리 셀 내에서 국부적인 열을 발생시키고, 이러한 열을 통해 단위 소자를 어닐링하는 방 식이다 [9-11]. 비록 이러한 ETA 기술이, 소자의 retention 및 endurance 등 신뢰성 개선에 효과적이나, 전류를 흘려준 layer와 나머지 layer 간의 온도의 불 균일 성으로 인한 기계적 스트레스에 대한 우려가 존재한다 [7,12].

이에, 이 연구에서는 3D NAND 플래시메모리 소자의 ETA 과정 중 발생할 수 있는, 온도의 불 균일성을 개선하기 위하여, 실리콘 기판 내부를 관통하는 through-silicon via (TSV) 전극 삽입을 최초로 제안한다. 기판을 관통하는 TSV를 3D NAND 내에 삽입되어 있는 plugged metal에 연결하여, ETA를 위한 전극으로 활용한다면, 셀

전체에 균일한 온도 분포를 만들어 낼 수 있다. 그리고 TSV를 통해 소자에서 발생하는 열이, 실리콘 기판을 통해 방출되지 못하도록 기판 위에 추가적인 절연층을 증착하여, ETA 효율을 극대화시킨다. 제안 방법을 통하여, 기존의 3D NAND 플래시메모리 소자에서 이루어진 ETA 방법에 견주어, 열이 더 고르게 분포될 수 있으며, 이에 발생할 수 있는 잠재적인 기계적인 손상을 최소화할 수 있다.

### 2. 실험 방법

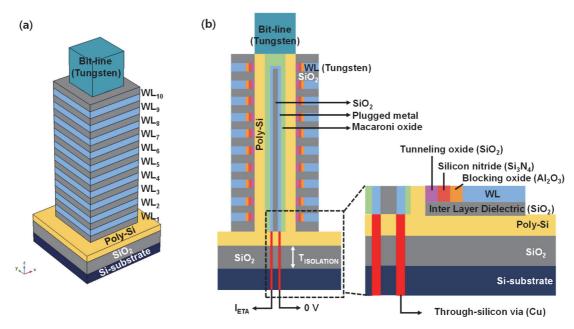

실험을 위하여 COMSOL Multiphysics 활용하였으며, 구체적으로는 solid mechanics, heat transfer in solids, 그리고 electrical currents 모듈을 사용하였다. 시뮬레이션 과정에서 대류에 의한 heat flux (h)는 10 W/mK으로, 그리고 실리콘 기판의 하단부는 상온이라 가정하였다. 그리고 각각의 WL 내에서 최대값을 기준으로 온도를 추출하고 비교하였다. 실험에서 사용된 3D NAND 플래시메모리어레이의 상세 구조는 아래의 그림 2와 같다. 3D NAND 플래시메모리어레이의 기본구조는 metal로 이루어진 plugged pillar을 내부에 포함하도록 하였다 [13,14].

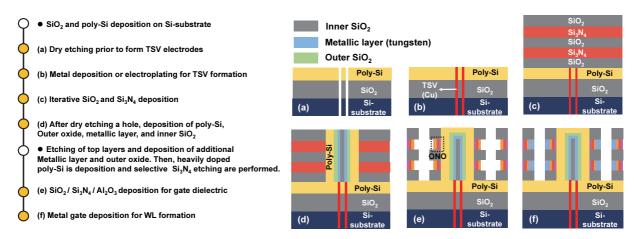

그리고 이와 같은 구조의 제조과정은, 그림 3의 방법으로 제작한다고 가정하였다. 먼저, n형 실리콘 기판상에  $SiO_2$  절연층과 poly-Si을 순차적으로 증착한다. 그리고 이후 dry etching 과 증착을 통하여 TSV을 형성한다 (그림 2(a)). 이후, 기존에 잘 알려진 3D NAND 공정을 활용하게된다 [14]. 구체적으로,  $SiO_2$ 와  $Si_3N_4$ 로 구성된 여러 개의 층들을 반복적으로 기판층에 증착한다. 그리고, dry

**Fig. 1.** Operating principle of a conventional electro-thermal annealing (ETA) configuration in 3D NAND flash memory. WL-to-WL current flow is utilized for Joule heat generation [9-11].

Fig. 2. (a) Schematic of the proposed NAND flash memory structure with TSV electrodes and (b) cross-sectional image of Fig. 2(a). The TSV electrodes are included inside of the silicon substrate.

**Fig. 3.** (a)-(f) Fabrication process flow of the proposed 3D NAND flash memory structure containing TSV electrodes. It is assumed that the TSV electrodes are composed of copper.

etching을 통하여 hole을 형성하고, atomic layer deposition (ALD)를 활용하여 poly-Si channel, outer SiO<sub>2</sub>, plugged metal, inner SiO<sub>2</sub> 순으로 증착한다 (그림 2(d)). 이후, 앞에서 증착된 Si<sub>3</sub>N<sub>4</sub> 층을 selective etching 하고, SiO<sub>2</sub> (O), Si<sub>3</sub>N<sub>4</sub> (N), Al<sub>2</sub>O<sub>3</sub> (O)를 순차적으로 증착하고, 마지막으로 metal word-line (WL)을 증착한다 (그림 2(e)-(f)). 이때 WL과 bit-line (BL), 그리고 plugged metal에 포함된 metal은 모두, 전기전도율 ( $\sigma$ )는  $2 \times 10^7$  S/m 및 열전도율 ( $\kappa$ ) 40 W/m • K 인 tungsten으로 설정하였다. 이외에, SiO<sub>2</sub>의  $\sigma$ 및  $\kappa$ 는 각각,  $1 \times 10^{-12}$  S/m 및

$1.4 \text{ W/m} \cdot \text{K}$ , 그리고 실리콘 기판의  $\sigma$  및  $\kappa$ 는 각각,  $1 \times 10^{-12} \text{ S/m}$  및  $130 \text{ W/m} \cdot \text{K}$ , 그리고 poly-Si의  $\sigma$  및  $\kappa$ 는 각각,  $3 \times 10^3 \text{ S/m}$  및  $9.4 \text{ W/m} \cdot \text{K}$ 이라고 가정하였다.

## 3. 결과 및 고찰

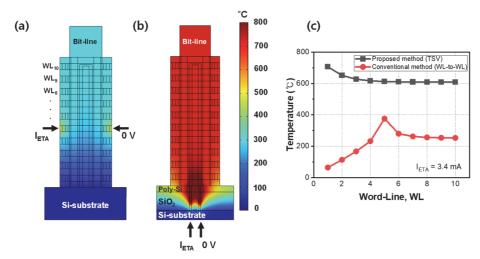

그림 4(a)는 plugged pillar가 삽입되어 있는 3D NAND 플래시메모리 어레이에서, 기존의 ETA 방식인 WL-to-WL 방식을 활용할 경우, 온도 시뮬레이션 결과를 보여준

Fig. 4. Comparison of heat distribution profiles between the (a) conventional ETA using WL-to-WL current, (b) the proposed annealing method using TSV electrodes, and (c) extracted temperature along the bit-line direction.

다. 이때, 전열 어닐링을 위하여, 5층에 위치하고 있는 WL 의 전극 끝에 전류 I<sub>ETA</sub> 전류 3.4 mA를 흘려주었으며, 이 전류 값은 전열 어닐링에 의해 소자 신뢰성 저하가 발생하 지 않는 범위이다 [7]. 이때, 셀의 최고온도는 375℃이며, 최저온도는 64℃임을 확인하였다. 그림 4(b)는 본 연구에 서 제안한 대로, TSV를 실리콘 기판에 먼저 삽입한 뒤, 기 판 아래에 형성된 TSV 패드를 통하여 동일한 전류를 인가 하였을 경우, 발생하는 온도의 분포를 보여준다. 그림 4(c) 는 그림 4(a)와 그림 4(b)의 결과에서 추출된 셀 간의 온도 분포를 비교하여 보여준다. 기존의 3D NAND 플래시메모 리 어레이의 경우, 전열 어닐링을 하는 셀 자체의 온도는 높지만, 주변 셀의 온도는 낮음과 동시에, 셀간 온도의 불 균일성이 존재한다. 이러한 온도의 불 균일 특성은, 셀마 다 각각 상이한 온도의 어닐링 조건을 초래하므로, 결국 셀 의 산포저하 및 기계적인 신뢰성 저하를 초래한다. 하지만, TSV 가 실리콘 기판에 삽입되었을 시, 최고온도 706℃, 최 저온도 609℃이며, 그림 4(c)와 같이 대체로 균일함을 알 수 있다. 이로 인하여, TSV를 활용한 경우, 모든 셀을 균 일한 온도로 동시에 전열 어닐링할 수 있으며, 이로 인하여 셀의 산포저하를 최소화하면서, 어닐링의 효과는 극대화 할 수 있다. 뿐만 아니라, 온도의 크기 측면에서 볼 때, TSV 를 적용한 경우가, 기존의 WL-to-WL 방법에 견주어, 더 높은 온도를 보여준다. 그 이유는 TSV를 통해 발생한 열 이, 기판 상에 존재하는 SiO<sub>2</sub> 절연층으로 인하여, 기판 아 래로 원활하게 방출되기 어렵기 때문이다. 반면, 기존의 WL-to-WL 방법의 경우, 5층의 셀에서 발생한 열이 기판 을 통해 방출되므로, 아래층으로 갈수록 온도의 크기가 확 연히 낮아지게 된다. 본문에는 포함되어 있지 않지만, 기

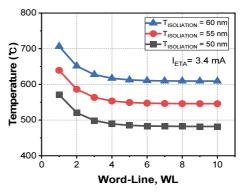

**Fig. 5.** Extracted temperatures with various isolation thicknesses (Tisolation) deposited on a Si-substrate.

존의 구조인 그림 4(a)의 구조에, 그림 4(b)와 동일한 60 nm 두께의 SiO₂를 기판상에 형성하였을 경우, 최대 온도의 크기는 375°C에서 526°C로 증가하였다. 하지만, 셀간온도의 불 균일성은 여전히 개선되지 않음을 별도 확인하였다.

그림 5는 TSV를 실리콘 기판에 삽입한 경우, 기판상에 증착한  $SiO_2$ 의 두께( $T_{ISOLATION}$ )에 대한 전열 어닐링 온도의 분포를 보여준다. 앞서 언급한 것과 마찬가지로,  $SiO_2$  절 연층의 두께가 두꺼워질수록, 전열 어닐링 과정 중 발생하는 열이 기판으로의 방출이 억제된다. 왜냐하면,  $SiO_2$ 의 thermal conductivity ( $\kappa$ )는 1 W/mK 으로써, 실리콘 기판에 견주어 100배 이상 낮기 때문이다. 따라서,  $SiO_2$  절 연층의 두께를 조절하여, 동일한  $I_{ETA}$  전류 하에서, 전열 어닐링 온도를 더 높이거나 낮추는 것이 가능하다.

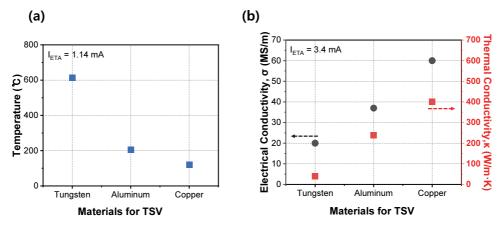

그림 6(a)는 TSV 로 삽입되는 전극을 copper가 아닌 다

Fig. 6. (a) Extracted temperature with various alternative metals for TSV and (b) material properties such as electrical conductivity and thermal conductivity with various alternative metals for TSV.

른 금속으로 대체하였을 때, 발생하는 최고온도를 보여준다. 텅스텐(tungsten)을 활용하였을 때에 비하여, 알루미늄(aluminum)이나 구리(copper)를 TSV 소재로 사용할때, 최고 온도가 각각  $200^{\circ}$ C 및  $100^{\circ}$ C 근처로 낮아짐을 확인하였다. 이러한 온도저하의 원인을 그림 6(b)와 같이 분석해보니, 금속의 electrical conductivity ( $\sigma$ ) 및 thermal conductivity ( $\kappa$ )와 연관 있음을 확인하였다.  $\sigma$ 가 높은 금속을 활용할 경우, 금속 전극의 저항이 감소하여, 발생하는 온도의 크기가 낮다 [15]. 하지만, Wiedemann-Franz Law에 의하면,  $\sigma$ 이 큰 금속이  $\kappa$  값 또한 큰 값을 가지는 경향이 있다. 이에,  $\sigma$ 이 큰 금속이 방출하는 낮은 온도의 열이, 높은  $\kappa$ 를 지니는 금속으로 원활히 방출되기에, 셀의 온도는 낮게 형성된다. 따라서, 동일한  $I_{\text{ETA}}$  인가전류 하에, 에너지 효율을 높이기 위해서는 낮은  $\sigma$  및  $\kappa$  성질을 지니는 금속소재를 활용하는 것이 바람직하다.

### 4. 결 론

본 연구에서는 through-silicon via (TSV)를 활용한 전열 어닐링(electro-thermal annealing, ETA) 기법을 최초로 제안한다. 실리콘 기판을 관통하는 TSV와 3D NAND플래시메모리 어레이에 존재하는 plugged metal을 활용한다. 기존에 제안된 WL-to-WL 전류를 활용한 플래시메모리의 전열 어닐링의 경우, 실리콘 기판이라는 heat sink로 인하여, 전열 어닐링 온도가 낮으며, 셀과 셀간의 온도분포가 불균일하다는 단점이 존재하였다. 하지만 제안하는 바와 같이, TSV로 형성된 두개의 전극으로 전열 어닐링이 이루어질 경우, 발생한 열이 어레이 내에 존재하는 모든 셀에 균일하게 퍼지며, 이에 불가피한 소자간 산포 증가

및 기계적인 응력을 피할 수 있다. 또한 실리콘 기판 상에 증착되는 SiO<sub>2</sub> 절연층의 두께가 두꺼울수록, 동일한 입력 전류 하에서, 전열 어닐링의 온도가 높아지는 것을 확인하 였다. 절연층의 두께(T<sub>ISOLATION</sub>)가 10 nm 증가할 때, 소자 내부 온도는 약 20% 상승하였으며, 이는 어닐링의 열 효율 (속도 및 전력소모) 특성을 개선할 수 있다는 것을 의미한 다. 여기에서 더 나아가, TSV에 활용가능한 다양한 소재 를 대상으로 하여, 어닐링 온도의 크기와 열전도율 및 전기 전도율의 상관관계에 대하여 알아보았다. 특히, 열전도율 과 전기전도율이 낮은 소재를 TSV에 활용할 때, 동일한 입 력 하에서 에너지 효율이 더 높다는 것을 확인하였다. 결론 적으로 이와 같은 3D NAND 플래시메모리의 전열 어닐링 효율 개선에 대한 연구는, 메모리 신뢰성 향상에 기여할 수 있을 것으로 기대된다. 하지만, 제안하는 구조는 inner SiO<sub>2</sub>, plugged metal, 그리고 outer SiO<sub>2</sub> 등을 형성하기 위한 공정난이도가 매우 어려울 것으로 여겨진다. 그리고, 삽입된 plugged metal의 일 함수(work function)에 의한 채널의 문턱 전압 변화 등의 우려에 대해서도, 별도로 다루 어질 필요성이 있다.

#### **ORCID**

Jun-Young Park

https://orcid.org/0000-0003-4830-9739

### 감사의 글

This work was partially supported by the National Research Foundation of Korea (NRF) grant funded by the Korea government (MIST) (No. 2021R1F1A 1049456).

### **REFERENCES**

- [1] C. M. Compagnoni, A. Goda, A. S. Spinelli, P. Feeley, A. L. Lacaita, and A. Visconti, *Proc. IEEE*, 105, 1609 (2017). [DOI: https://doi.org/10.1109/JPROC.2017.2665781]

- [2] S. Y. Lee, J.-S. Oh, S.-D. Yang, K.-S. Jeong, H.-J. Yun, Y.-M. Kim, H.-D. Lee, and G.-W. Lee, *J. Korean Inst. Electr. Electron. Mater. Eng.*, 25, 85 (2012). [DOI: https://doi.org/10.4313/JKEM.2012.25.2.85]

- [3] S.-H. Baek, K.-H. Song, and H.-Y. Lee, J. Korean Inst. Electr. Electron. Mater. Eng., 23, 261 (2010). [DOI: https://doi.org/10. 4313/JKEM.2010.23.4.261]

- [4] J.-H. Jang, H.-S Kim, W.-S Cho, H.-S Cho, J.-H Kim, S.-I Shim, Younggoan, J.-H. Jeong, B.-K Son, D.-W Kim, Kihyun, J.-J. Shim, J.-S. Lim, K.-H. Kim, S.- Y. Yi, J.-Y. Lim, D.-W Chung, H.-C. Moon, S.-M Hwang, J.-W Lee, Y.-H. Son, U.-I.Chung and W.-S. Lee, *Proc. 2007 IEEE Symp. VLSI Technol.* pp.192-193

- [5] N. Righetti and G. Puzzilli, Proc 2017 IEEE Int. Integ. Rel. Wrksp. (IIRW) pp. 1-6. [DOI: https://doi.org/10.1109/IIRW. 2017.8361235]

- [6] H. Tanaka, M. Kido, K. Yahashi, M. Oomura, R. Katsumata, M. Kito, Y. Fukuzumi, M. Sato, Y. Nagata, Y. Matsuoka, Y. Iwata, H. Aochi, and A. Nitayama, *Proc. 2007 IEEE Symp. VLSI Technol.* (Kyoto, Japan, 2007) pp. 14-15. [DOI: https://doi.org/10.1109/VLSIT.2007.4339708]

- [7] Y.-J. Kim and J.-Y. Park, J. Korean Inst. Electr. Electron. Mater. Eng., 35, 246 (2022). [DOI: https://doi.org/10.4313/JKEM.2022. 35.3.6]

- [8] K. Onishi, C.-S. Kang, R. Choi, H.-J. Cho, S. Gopalan, R.E. Nieh, S.A. Krishnan, and J.C. Lee, *Proc. IEEE T. Electron Dev.*, 50, 384 (2003). [DOI: https://doi.org/10.1109/TED.2002.807 447]

- [9] H.-T. Lue, P.-Y. Du, C.-P. Chen, W.-C. Chen, C.-C. Hsieh, Y.-H. Hsiao, Y.-H. Shih, and C.-Y. Lu, *Proc. 2012 International Electron Devices Meeting* (IEEE, San Francisco, USA, 2012) pp. 9.1.1-9.1.4. [DOI: https://doi.org/10.1109/IEDM.2012.6479008]

- [10] T.-H. Hsu, H.-T. Lue, P.-Y. Du, W.-C. Chen, T.-H. Yeh. R. Lo, H.-S. Chang, K.-C. Wang, and C.-Y. Lu, *Proc. 2019 IEEE 11th International Memory Workshop* (IMW), (Monterey, CA, USA, 2019) pp. 1-4. [DOI: https://doi.org/10.1109/IMW.2019.8739 692]

- [11] D.-I. Moon, J.-Y. Park, J.-W. Han, G.-J. Jeon, J.-Y. Kim, J. Moon, M.-L. Seol, C. Ki Kim, H.-C. Lee, M. Meyyappan, and Y.-K. Choi, *Proc.* 2016 IEEE Int. El. Devices Meet. (IEDM), pp. 31.8.1-31.8.4. [DOI: https://doi.org/10.1109/IEDM.2016.7838 524]

- [12] D.-H. Wang and J.-Y. Park, J. Korean Inst. Electr. Electron. Mater. Eng., 35, 50 (2022). [DOI: https://doi.org/10.4313/ JKEM.2022.35.1.8]

- [13] J.-Y. Park, D.-H. Yun, S.-Y. Kim, and Y.-K. Choi, *IEEE Electr. Device L.*, 40, 212 (2019). [DOI: https://doi.org/10.1109/LED. 2018.2889037]

- [14] D.-H. Jung, K.-S. Lee, and J.-Y. Park, J. Semicond. Technol. Sci., 21, 334 (2021). [DOI: https://doi.org/10.5573/JSTS.2021. 21.5.334]

- [15] J.-Y. Park, D.-I. Moon, M.-L. Seol, C.-K. Kim, C.-H. Jeon, H. Bae, T. Bang, and Y.-K. Choi, *IEEE T. Electron Dev.*, 63, 910 (2016). [DOI: https://doi.org/10.1109/TED.2015.251 3744]