Journal of the Korea Institute of Information and Communication Engineering

한국정보통신학회논문지 Vol. 26, No. 3: 412~421, Mar. 2022

# 5G NR 셀 탐색과 동기화를 위한 교차상관관계 기반 PSS 검출기 구조

이 짓\*

# Hardware Structure of Cross Correlation based PSS Detector for Cell Search and Synchronization of 5G NR Systems

#### Jin Lee

\*Assistant Professor, Department of Communication and Information, Pyeongtaek University, Pyeongtaek, 17869 Korea

#### 요 약

5G NR 모든 기기는 기지국과 통신을 위해 가장 먼저 셀 탐색 및 동기화 과정을 진행해야 한다. 이 과정에서 PSS 검출이 제일 먼저 성공적으로 수행되어야 하므로, PSS 검출은 5G NR 통신에서 가장 중요하고 어려운 문제 중 하나이다. 다양한 PSS 검출 방법 중 본 논문에서는 교차상관관계 기반의 검출 방법에 대해 소개하고 복잡도와 검출 속도를 고려한 하드웨어 구조에 대해서 설명한다. 또한, PSS 검출기를 포함하는 시스템 구성을 위해 필요한 인터페이스와 효율적이고 유연한 동작을 위한 구동 소프트웨어 동작도 제안하고, 이를 구현하였을 때 Xilinx사의 UltraScale+FPGA의 자원 사용량을 다양한 구조에 따라 비교 분석한다.

# **ABSTRACT**

All 5G NR devices must first perform the cell search and synchronization process to communicate with the base station. In this process, PSS detection is one of the most important and difficult problems in 5G NR communication because PSS detection must first be successful in order to extract essential information from the following signals. Among the various PSS detection methods, this paper describes a cross-correlation-based detection method, and the implementation methods of the tap delay line hardware with parallelization are introduced and compared in terms of complexity and detection speed. In addition, the interface required for system configuration including the PSS detector and control software for efficient and flexible operation are also explained. In this paper, the resource usages of Xilinx's UltraScale+ FPGA are compared for various PSS detector structures and analyzed according to various parallelization levels.

**키워드**: 5G NR, 동기화, 셀 탐색, PSS 검출, 하드웨어

Keywords: 5G NR, Synchronization, Cell search, PSS detection, Hardware

Received 20 January 2022, Revised 2 February 2022, Accepted 19 February 2022

\* Corresponding Author Jin Lee(E-mail:mygenie79@ptu.ac.kr, Tel:+82-31-659-8288)

Assistant Professor, Department of Communication and Information, Pyeongtaek University, Pyeongtaek, 17869 Korea

Open Access http://doi.org/10.6109/jkiice.2022.26.3.412

print ISSN: 2234-4772 online ISSN: 2288-4165

©This is an Open Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License(http://creativecommons.org/licenses/by-nc/3.0/) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

Copyright © The Korea Institute of Information and Communication Engineering.

### Ⅰ. 서 론

5세대 (5G) NR (new radio)는 3GPP (3rd generation partnership project)에서 LTE (long therm evolution) 네 트워크의 후속 버전으로 개발한 새로운 무선 이동통신 기술로 다양한 요구 성능과 적용 범위를 지원할 수 있도록 설계 되었다[1]. 5G NR의 적용 범위는 기존 보다 발전된광대역 이동 통신 (enhanced mobile broadband, MBB), 긴급 장비용 통신 (critical machine type communication, cMTC), 필요한 대량 기기용 통신 (massive machine type communication, mMTC) 등이 대표적이다. 특히 mMTC에 적용하기 위해서는 저가의 기기가 낮은 에너지 소비를 사용해서 5G NR 통신을 할 수 있도록 무선 통신 하드웨어가 설계되어야 한다.

기기가 5G NR 네트워크를 통해 통신을 하기 위해서는 제일 먼저 셀 탐색을 수행하여 주변에 존재하는 셀을 식별하고 물리적/논리적으로 동기를 맞추어야 한다. 셀 탐색은 기지국 (BS)에서 전송하는 동기화 신호 블록 (synchronization signal block, SSB)을 수신하고 해석하는 것이다.

SSB는 primary synchronization signal (PSS)와 secondary synchronization signal (SSS) 그리고 physical broadcast channel (PBCH)로 구성되어 있다. 물리적인 동기를 맞 추는 것은 시간과 주파수 영역에서 신호의 시작점과 중 심주파수의 오차를 조정하는 과정을 의미하고, 이 동작 은 PSS를 해석하는 과정을 통해 이루어진다. 논리적인 동기를 맞추는 것은 각 BS에 할당된 물리계층 셀 ID (Physical Cell ID, PCI)와 네트워크에서 통신하기 위한 필수 정보의 모음인 master information block (MIB)을 찾아내는 것이다. PCI는 PSS와 SSS를 해석해서 얻어내 는 것이고, MIB는 PBCH를 해석해서 구해내는 정보이 다 [2][3]. 5세대 (5G) NR (New Radio) 표준은 LTE에 비 교해서 다양한 대역폭 지원과 향상된 안정성을 위해 동 기화 신호를 개선하였고, 이 때문에 하향링크 동기화 절 차가 복잡해지게 되었다 [3]. LTE와 5G NR의 동기화 신호의 가장 큰 차이점은 사용되는 시퀀스가 다르다는 것이다. LTE에서는 Zadoff-Chu (ZC) 시퀀스를 사용하 였는데, 5G NR에서는 시간/주파수 오차를 파악하는데 더 좋은 성능을 보이는 m-sequence를 사용하는 것으로 변경되었다. m-sequence는 ZC 만큼 훌륭한 상관관계 특성을 갖기 때문에 LTE에서 사용되었던 동기화 알고

리즘을 활용할 수가 있다.

OFDMA (orthogonal frequency division multiple access) 기반의 통신 기술인 LTE와 5G NR 시스템은 송신부와 수신부 사이의 주파수 및 타이밍 오류에 민감하다. 주파수 오차는 서브캐리어 간의 직교성을 손상시켜 반송파간 간섭(ICI)을 유발할 수 있기 때문에 성능 손실을 피하기 위해 정확한 PSS 해석을 통한 동기화가 필수적이다 [4][5].

5G NR에서는 PSS에 3종류의 m-sequence를 사용하는데 BS와 동기화를 위해 가장 먼저 수행해야 하는 것이 바로 수신 신호에서 PSS가 존재 하는 지, 3개 중 어떤 시퀀스를 사용하는지 파악하는 PSS 검출과정이다. PSS 검출은 모든 통신 과정 중에 제일 먼저 수행되어지는 중요하고 어려운 문제이다.

PSS 검출을 위한 방법은 다양하게 존재하는 데, 크게 구분하면 시간 영역 처리 방법과 주파수 영역 처리 방법으로 구분할 수가 있다. 일반적으로 시간 영역 처리 방법이 불확실성이 적고, 복잡도가 낮다고 알려져 있으므로 [3][6]-[8] 본 논문에서는 시간영역 처리 방법에 대해서만 다룬다. 시간 영역에서 PSS 시퀀스를 검출하는 방식은 자기상관관계 (auto-correlation) 방식과 교차상관관계 (cross-correlation) 방식으로 구분할 수 있다. 일반적으로 자기상관관계 방식은 불확실성이 높고, 낮은 SNR (signal to noise ratio)에서 성능이 더 열악해진다고 알려져 있으므로 정확도를 향상시키기 위해서는 자기상관 기반 방식이 아닌 교차상관 기반 방식을 적용할 것을 권고한다[3]. 따라서 본 논문에서는 교차상관관계 기반의 PSS 검출기만을 다룬다.

십년 이상 다양한 연구를 통해서 OFDMA 기반의 셀탐색 및 동기화 방법에 대한 연구가 진행되어 왔지만, 자세한 구현 방법 및 시스템 구성 방법에 대해서는 관련 논문이나 기술 문서를 찾기가 어렵다. 따라서 본 논문에서는 5G NR용 PSS 검출기를 교차상관관계 기반으로 복잡도를 고려하면서 구현하는 방법 및 시스템 구성 방법에 대해 설명하고 구현 결과를 분석한다.

II 장에서는 5G NR 표준의 셀 탐색 및 동기화 과정에 대해서 설명하고, III 장에서는 PSS 신호의 구성 및 교차 상관관계를 통한 검출 방법에 대해서 설명한다. IV장에서는 PSS 검출기 구현 방법과 구현 결과에 대해서 논하고, 마지막으로 V장에서 결론을 맺는다.

# Ⅱ. 5G NR의 셀 탐색 및 동기화 과정

이번 장에서는 5G NR 시스템에서의 셀 탐색 및 동기 화 과정을 5G 프레임 구조 (frame structure)와 같이 요약 하여 설명한다.

#### 2.1. 5G NR 프레임 구조

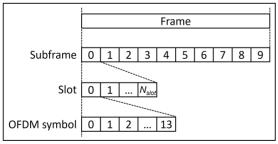

5G NR 표준안[1]에서는 5G 통신에서의 프레임 구조를 정의하고 있다. 5G 프레임의 길이는 10ms고 고정되어 있고, 하나의 프레임(frame)은 10개의 서브프레임으로 구성되어 있다. 즉 서브프레임(subframe)의 길이는 1ms이고, 서브 프레임은 정해진 수의 슬롯(slot)으로 구성된다. 하나의 서브프레임을 구성하는 슬롯의 수는 사용하는 서브캐리어 간격 (sub-carrier spacing)에 따라 달라진다. 5G에서는 서브캐리어 간격으로 15, 30, 60, 120, 240kHz를 지원한다. 서브프레임을 구성하는 슬롯의 수는 변할 수 있지만, 하나의 슬롯은 5G 통신 물리계층의가장 기본 단위인 OFDM 심볼 14개로 구성된다. 프레임과 서브프레임 길이는 각각 10ms와 1ms로 고정되어 있지만, 슬롯의 길이와 OFDM 심볼의 길이는 서브캐리어 간격에 따라 달라진다.

Table. 1 Parameters for components consisting a frame

| Subcarrier spacing (kHz)                              | 15 | 30 | 60 | 120 | 240 |

|-------------------------------------------------------|----|----|----|-----|-----|

| Number of subframes (N <sub>subframe</sub> )          | 10 | 10 | 10 | 10  | 10  |

| Number of slots for one subframe $(N_{slot})$         | 1  | 2  | 4  | 8   | 16  |

| Number of symbols for one slot (N <sub>symbol</sub> ) | 14 | 14 | 14 | 14  | 14  |

Fig. 1 5G NR frame structure

5G의 프레임 구조는 그림 1과 같이 표현될 수 있다. 프레임을 구성하는 서브프레임, 슬롯, OFDM 심볼에 관 련된 파라미터들의 수치는 표 1에 정리하였다.

5G에서는 두 가지 타입의 CP (Cyclic Prefix)가 정의되어 있다. 표 1의 슬롯 당 심볼 수 ( $N_{symbol}$ )은 normal CP를 기준으로 하였다. extended CP인 경우 슬롯 당 OFDM 심볼 수는 12개가 된다.

#### 2.2. Synchronization Signal Block (SSB)

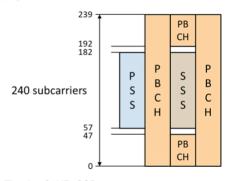

5G 기지국은 단말기의 셀 탐색과 동기화가 가능하도록 주기적으로 동기화 신호를 전송하게 된다. 이 동기화 신호는 PSS와 SSS 2가지 종류가 있다. PSS와 SSS는 기지국과 통신하기 위한 기본 정보들을 포함하는 PBCH와 함께 SSB로 묶여서 전송된다. SSB는 4개의 OFDM 심볼로 이루어져 있으며, SSB의 각 심볼에 전송되는 신호는 그림 2에 나타내었다. SSB가 전송되는 시점 및 전송 패턴은 다양한 경우로 정리되어 있지만, SSB를 구성하는 신호의 구성 및 물리적인 파라미터들은 변하지 않는다. 또한, 2개의 프레임 당 (즉, 20ms) 한 번은 반드시 전송된다.

Fig. 2 5G NR SSB structure

SSB는 주파수 영역에서는 240개의 서브캐리어로 전송된다. PSS는 SSB의 첫 번째 OFDM 심볼로 전송되고 57~182까지 SSB의 중심 127개의 서브캐리어를 사용해서 전송한다. SSS는 세 번째 OFDM 심볼에서 PSS와같은 서브캐리어로 전송된다. PBCH는 2~4 OFDM 심볼에 걸쳐져서 전송이 되는데, 두 번째와 네 번째 OFDM 심볼에서는 240개 전체 서브캐리어를 사용하고,세 번째 심볼 구간에서는 SSS가 사용하지 않는 서브캐리어를 사용하게 된다. PBCH의 서브캐리어 중간 중간에는 PBCH를 복호할 때 사용할 채널의 정보를 파악하

기 위한 PBCH demodulation reference signal (DMRS) 이 삽입되어 있지만, 본 논문의 주제와 관련이 없기 때문에 이에 대한 자세한 설명은 생략하기로 한다.

5G에서는 LTE와 다르게 시간 영역과 주파수 영역에서 SSB의 전송이 고정되어 있지 않다. LTE에서는 SSB의 중심 주파수는 캐리어 중심과 일치하였지만, 5G에서는 사용하는 주파수 대역 내에서 SSB가 전송되는 위치가 달라질 수 있고, SSB가 전송되는 시점도 고정되어 있지 않고, 상황에 따라 여러 가지 case로 정의되어 있다.이에 대한 내용도 본 논문의 주제와 관련이 없기 때문에자세한 설명은 생략하기로 한다.

#### 2.3. 셀 탐색 및 동기화 과정

5G에서 셀 탐색 과정을 통해 얻어야 하는 결과는 다음과 같다.

- 물리계층 셀 ID (PCI)

- Frame 시작점

- PBCH로 전달되는 MIB

PSS와 SSS는 각각 3개와 336가지 유형이 있으며, 물리계층 셀 ID는 식(1)과 같이 PSS와 SSS에 사용된 패턴의 번호를 조합이기 때문에 PSS와 SSS를 복호하여 총1008개 중 하나의 PCI를 검색하여야 한다.

$$N_{DD}^{cell} = 3N_{DD}^{(1)} + N_{DD}^{(2)} \tag{1}$$

여기서,  $N_{ID}^{(1)}$ 는 SSS에 사용된 패턴 번호로  $0\sim355$  사이의 정수이고,  $N_{ID}^{(2)}$ 는 PSS에 사용된 패턴의 번호로 0, 1,2 중에 하나가 된다.

PSS를 검출하면서 PSS가 전송되는 OFDM 심볼의 시작점도 파악하게 되는데 이 지점이 SSB의 시작점이 된다. SSB가 전송되는 시점은 여러 가지 경우가 있기 때문에 바로 frame 시작점을 찾을 수는 없지만, PBCH DMRS에 사용된 패턴 번호를 파악하여 SSB가 전송되는 시점이 결정되면 PSS의 시작점으로부터 frame 시작점을 구할 수가 있게 된다. PBCH DMRS는 총 8가지 패턴 중에 하나를 사용하는 데 사용된 패턴 번호에 따라서 SSB의 송신 시점을 파악할 수가 있다.

PBCH에는 여러 가지 5G 네트워크 통신에 필요한 정보가 들어있지만, 본 논문의 주제와 관련이 없기 때문에

자세한 설명은 생략하기로 한다.

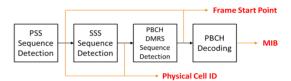

지금까지 설명한 셀 탐색 및 동기화 과정을 도식화 하면 그림 3와 같이 나타낼 수가 있다. 본 논문에서는 이중 제일 첫 단계인 PSS 시퀀스 검출 과정을 위한 하드웨어 구조를 다룰 것이다.

Fig. 3 Cell search and synchronization procedure

# Ⅲ, PSS 검출 방법

이번 장에서는 PSS 시퀀스를 생성하는 방법과 특징, 수신된 신호에서 PSS 시퀀스를 검출하는 방법에 대해 설명하고, 5G 테스트 장비를 통해 수집한 실제 5G 무선 신호를 갖고 링크레벨 시뮬레이션으로 검출한 결과를 소개한다.

#### 3.1. PSS 시퀀스 생성

5G NR에서 PSS는 길이 127인 m-sequence 세 개 중에 하나를 선택하여 SSB의 첫 번째 OFDM 심볼로 전송한다. m-sequence는 특수한 형태의 LFSR(Linear Feedback Shift Register)로 반복하지 않는 가능한 가장 긴 시퀀스를 생성하기 때문에 MLS (Maximul Length Sequence)라고 한다. 또한, 서로 다른 시퀀스에 대해서 월등하게 구별되는 상호상관관계를 보이기 때문에 PSS, SSS와 같은 시퀀스 생성에 많이 사용되다.

PSS 시퀀스인  $D_{nss}(n)$ 는 다음과 같이 생성된다.

$$D_{pss}(n) = 1 - 2x(m), (0 \le n \le 127)$$

(2)

여기서 x(m) 이 m-sequence로 식 (2)는 0과 1로 표시되는 시퀀스를 1과 -1로 변환하는 과정으로 이해하면된다. PSS에서 사용되는 m-sequence의 LFSR은 다음 식으로 표현된다.

$$x(i+7) = (x(i+4) + x(i)) \mod 2$$

(3)

초기 값은  $[1\ 1\ 1\ 0\ 1\ 1\ 0]$ 으로 설정하고, 식 (2)에서의 m과 n의 관계는 다음과 같다.  $N_D^{(2)}$ 는 0,1,2 중에 하나

가 된다.

$$m = (n + 43N_{ID}^{(2)}) \mod 127$$

(4)

이렇게 생성된  $D_{pss}(n)$ 를 정해진 서브캐리어 127개에 맵핑하여 OFDM 심볼을 만들면 PSS OFDM 신호가 완성된다. PSS 검출은 PSS에서 사용 가능한 모든 m-sequence의 OFDM 심볼과 수신된 신호의 상호상관 관계를 계산해서 가장 전송 확률이 높은 m-sequence에 사용된  $N_n^{(2)}$ 를 찾아내는 과정이다.

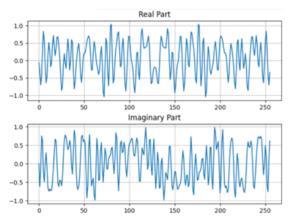

Fig. 4 PSS OFDM symbol waveform ( $N_{ID}^{(2)}$  = 1)

m-sequence를 사용하여 생성한 PSS OFDM 심볼 신호의 특성은 그림 4와 같이 중앙을 중심으로 실수부는 좌우 대칭, 허수부는 좌우상하 대칭이 됨을 알 수가 있다. 이 현상은 다른  $N_D^{(2)}$ 에서도 동일하게 나타난다. 이 특성을 활용해서 하드웨어 설계 시 저장 공간을 효율적으로 사용할 수 있게 된다.

PSS를 포함한 SSB의 OFDM 심볼은 주파수 영역에서 240개의 서브캐리어만 사용하기 때문에, 그림 4에서와 같이 256 서브캐리어로 해석하는 것이 효율적이다.

#### 3.2. PSS 검출 과정

이 장에서는 5G 테스트 장비를 통해 수집한 5G 무선 신호로부터 PSS를 검출하는 과정을 링크레벨 시뮬레이 션 결과를 갖고 설명한다.

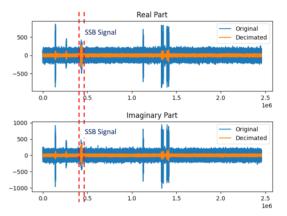

Anritsu 5G 테스트 장비를 통해 캡처한 KT 5G의 베이스밴드 수신 신호는 그림 5와 같다. 20ms에 한 번은 SSB가 수신되기 때문에 20ms 분량의 신호를 나타낸 것

이다. 이 신호는 SSB의 중심 주파수를 기준으로 하여 수 신한 것이다.

KT는 100MHz 대역폭을 사용하고, 30kHz의 서브캐리어 간격을 사용하기 때문에 122.88MHz의 샘플링 속도와 4096 point FFT 기반의 OFDM 심볼을 사용한다.하지만, SSB는 256 point FFT 기반으로 해석하는 것이효율적이기 때문에 decimation 필터를 사용해서 다운샘플링한 후에 PSS를 검출한다. 그림 5는 ADC 출력인 original 신호와 decimation 필터를 거쳐서 1/16 다운샘플링된 신호를 같이 표현하고 있다. 여기서 decimation 필터를 통과한 신호가 급격하게 줄지 않는 약 4ms ~4.5ms 사이 부분에 SSB 신호가 있음을 알 수가 있다.

Fig. 5 5G received signal waveform (time domain)

PSS 검출은 수신 신호 256개의 샘플들과 3.1장의 그림 4와 같이 전송 가능한 PSS 시퀀스 OFDM 심볼의 샘플 256개의 교차상관관계 (Cross-correlation)를 식(5)과 같이 계산하고 이 값의 크기를 최대로 만드는 전송 가능한 PSS 시퀀스와 시점을 찾는 과정이다.

$$C_{PSS}(u,t,n) = \sum_{i=0}^{255} [y(n+i) \cdot d_{u,t}^{*}(i)]$$

(5)

여기서,  $(\circ)^*$ 는 켤레복소수 (complex conjugate)를 나타낸다. y(n)은 안테나를 거쳐 ADC를 통해 입력된 베이스밴드 신호를 decimation 필터를 통과시켜 다운 샘플링한 신호이다.  $d_{u,t}^*(i)$ 는  $N_{LD}^{(2)}=u$ 일 때  $D_{pss}(n)$ 을 integer CFO (Carrier Frequency Offset)가 t 인 상황을 고려하여 OFDM 심볼로 만든 정해져 있는 PSS OFDM 심볼 패턴이다.

식 (5)와 같이 계산된  $C_{PSS}(u,t,n)$ 의 크기를 최대로 만드는  $\hat{u}$ 와  $\hat{t}$ 를  $N_{ID}^{(2)}$ 와 integer CFO로 판단하고,  $\hat{n}$ 을 PSS의 시작점으로 판단하는 것이 PSS 검출의 최종 목표이다.

$$(\hat{u}, \hat{t}, \hat{n}) = \underset{u,t,n}{\operatorname{arg} max} |C_{pss}(u, t, n)|^{2}$$

(6)

앞에서 설명한 것과 같이 일반적으로 PSS 검출 과정 중에 CFO 성분 중 서브캐리어 간격의 정수 배 오차에 대해서 측정하는 것을 동시에 진행한다. 이를 위해서는 PSS OFDM 심볼에 정수배 CFO가 추가된  $d_{u,t}^*(i)$  패턴을 구해야 한다. 예를 들어 integer CFO가 1인 (즉,  $30\mathrm{kHz}$  CFO인 경우)  $d_{u,1}^*(i)$ 는 PSS 시퀀스  $D_{pss}(n)$ 를 OFDM 심볼을 만들 때 서브 캐리어를 하나씩 어긋나게 배정해서 FFT 연산을 하는 것으로 구할 수 있다.

결과적으로 PSS 검출은 판단하고자하는 integer CFO 의 수와  $N_{ID}^{(2)}$ 의 수 (= 3)의 곱만큼 식 (5)(6)의 교차상관 관계 연산과 최대값 검색 과정을 하는 것으로 이해할 수 있다. 예를 들어, 30kHz의 서브캐리어 간격을 사용하는 5G 통신에서  $\pm 50k$ Hz 수준의 CFO까지 보상할 수 있으려면 integer CFO를  $\{-1,0,1\}$ 의 3개의 경우를 고려해야하므로 총 9개의  $d_{u,t}^*(i)$ 에 대해서 교차상관관계 연산을하고 이들의 최대값을 비교하고 결과를 판단해야 하는 것이다.

CFO 성분 중에서 integer CFO외에 남는 성분을 fractional CFO라고 하고 이 또한 여러 가지 방식으로 측정하여 오차를 보정해야 하지만, 본 논문의 주제와 관련이 없기 때문에 자세한 설명은 생략하기로 한다.

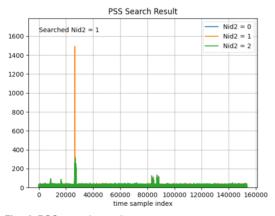

Fig. 6 PSS search result

그림 6는 실제 5G의 베이스밴스 신호를 다운샘플링하여 3가지  $N_D^{(2)}$ 에 대해서 교차상관관계의 크기를 그래프로 나타낸 것이다. (integer CFO는 0으로 설정하였다.) 이 그림에서  $N_D^{(2)}=1$ 인 경우, 다운 샘플링된 신호의 26,571번째 샘플에서 교차상관관계의 크기가 제일크다는 것을 확인할 수 있고, 이 위치는 그림 5의 SSB위치의 시작점을 나타낸다.

# Ⅳ. PSS 검출기 하드웨어 구조

3.2장의 식 (5)의 교차상관관계 계산은 256개의 입력 샘플 당 1개의 교차상관관계 결과가 나오게 된다. 즉, 수 신된 입력 샘플의 수가 M인 경우, 연산되는 교차상관관계의 수는

$$N_{corr} = \{ (M - 256) + 1 \} \tag{7}$$

이 되고, 계산된  $N_{corr}$ 개의 교차상관관계 값의 크기의 최대값을 추적하는 것이 PSS 검출기 하드웨어에서 하는 일이 된다.

이번 장에서는 교차상관관계를 활용한 PSS 검출기를 하드웨어로 구현하는 방법에 대해서 설명한다. 4.1에서는 교차상관관계를 구현하는 하드웨어 구조에 대해설명하고, 4.2장에서는 교차상관관계 연산기를 포함하는 PSS 검출기 전체를 구현하는 방법에 대해 설명하고 실제 구현 결과를 비교해 본다.

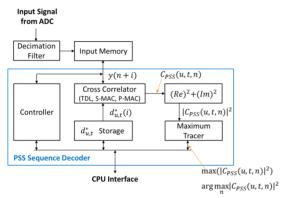

### 4.1. 교차상관관계 연산기 구조

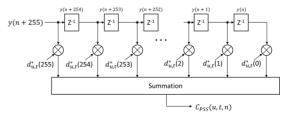

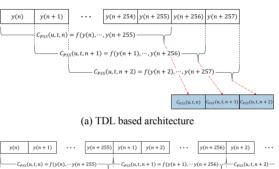

교차상관관계나 FIR 필터를 구현할 때 가장 직관적 이면서 일반적으로 사용되는 구조는 tapped delay line (TDL) 구조이다. 그림 7은 TDL로 식 (5)를 구현한 블록 도를 나타낸다.

Fig. 7 TDL based cross correlation

이 구조로 식 (5)를 구현하려면 256개의 복소수 곱셈 기와 곱셈 결과를 모두 더하기 위한 255개의 복소수 덧 셈기 뭉치가 필요하다.

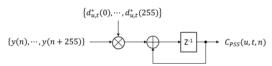

TDL 기반의 PSS 검출기의 하드웨어 복잡도를 효과적으로 줄일 수 있는 방법으로는 단일 곱셈 누산기 (Multiply-Accumulate, MAC) 구조를 사용하는 것이다. 일반적인 MAC 동작은 다음 식과 같다.

$$a \leftarrow a + (b \times c)$$

(8)

이 동작을 256회 반복하면 결과적으로 식 (5)의 교차 상관관계를 구할 수가 있게 되는 것이다. 즉, 그림 8과 같이 복소 곱셈기와 덧셈기를 각 1개씩만 사용해서 교 차상관관계를 구할 수 있게 된다.

Fig. 8 MAC based cross correlation

TDL 구조는 수신 신호 y(n)이 순차적으로 입력될때, 256개의 샘플이 입력되면 이 후 매 사이클 교차상관관계 결과가 출력되기 때문에 M개의 입력 샘플에 대한  $N_{corr}$ 개의 교차상관관계 출력을 전부 계산하는 데 필요한 시간은 다음과 같이 계산할 수 있다. (단위는 클록 사이클이다.)

$$T_{TDL} = N_{corr} + 256 = M + 1$$

(9)

단일 MAC (Single MAC, SMAC) 방식은 y(n)부터 y(n+255)까지 256개의 입력에 대한 교차상관관계 연산을 완료한 후 다시 y(n+1)부터 y(n+256)까지의 입력으로 다음 교차상관관계를 계산할 수 있기 때문에, M개의 입력 샘플에 대한 연산 시간은 다음과 같다. (반복 제어를 위해 필요한 지연 요소는 무시되었다.)

$$T_{SMAC} = 256 \cdot N_{corr} = 256 \cdot \{(M-256)+1\} (10)$$

이에 대한 개념은 그림 9의 (a)와 (b)에 나타내었다. 간략한 표현을 위해 그림 9에서 연산과 제어에 필요한 세부 지연 요소는 무시하였다.

병렬 MAC (Parallel MAC, PMAC) 구조는 SMAC 구조를 P개 병렬 연결하여 연산 복잡도가 P배 늘어나지만, 연산 시간을 1/P배로 줄일 수 있는 구조이다.

SMAC 구조는 P=1인 PMAC 구조로 해석하면 된다.

P가 2인 경우 (즉, 그림 8의 SMAC 구조 교차상관관계 연산기 2개로 이루어진 경우) y(n)의 입력 패턴과 교차상관관계 연산 결과 출력을 그림 9 (c)에 나타내었다. 첫 번째 SMAC 연산기는 y(n)부터 y(n+255)까지 입력되는 동안  $C_{PSS}(u,t,n)$ 를 연산하게 되고, 두 번째 SMAC 연산기는 y(n+1)부터 y(n+256)까지 입력되는 동안  $C_{PSS}(u,t,n+1)$ 을 연산하게 되어 두 개의 교차상관관계 결과는 바로 구해질 수 있게 된다. 즉, PMAC 구조는 y(n)부터 y(n+255+(P-1))까지 신호를 입력 받아 P개의 교차상관관계 연산을 병렬로 진행하는 것이다.

Fig. 9 Cross correlation operation timing diagram

PMAC 구조는 (255+P) 개의 입력 샘플을 입력 받아 P개의 교차상관관계를 평가 하는 것이므로, M개의 입력 샘플에 대해  $\lceil N_{corr}/P \rceil$  회 반복 동작을 해야 한다. 이를 정리하면 PMAC의 연산 시간은 다음과 같다. (반복 제어를 위해 필요한 지연 요소는 무시되었다.)

$$\begin{split} T_{PMAC} &= (255 + P) \bullet \lceil N_{corr}/P \rceil \\ &= (255 + P) \bullet \lceil \{(M - 256) + 1\}/P \rceil \end{split} \tag{11}$$

SMAC과 PMAC 구조는 실시간으로 입력되는 y(n)

에 대해서 on-the-fly로 교차상관관계 연산을 진행할 수 없기 때문에, 일정양의 y(n)을 메모리에 저장한 후에 저장된 y(n)을 순서에 맞게 읽어오면서 연산을 수행할 수 있도록 y(n)과  $d_{u,t}^*(i)$ 의 순서를 맞춰주는 제어 회로가 같이 설계되어야 한다.

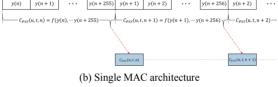

#### 4.2. PSS 검출기 구조

그림 10은 본 논문을 위해 구현된 PSS 검출기블록도 및 시스템 구성을 위한 인터페이스를 나타낸다.

Fig. 10 Block diagram of PSS sequence decoder

ADC를 통해 입력되고 decimation 필터를 통과하여 다운 샘플링된 수신신호는 우선 입력 메모리 (input memory)에 저장된다. 5G에서는 SSB가 20ms 당 한 번은 반드시 전송되기 때문에, 정확하게 PSS를 감지하기 위해서는 20ms 분량을 저장하는 것이 필요하다. 메모리 사용량에 대해 부담이 있는 경우 적은 양을 저장하고 여러 번 나누어 PSS를 감지하는 제어가 필요하다.

PSS 검출기 하드웨어의 역할을 간단하게 정리하면, 입력 메모리에 저장된 M개의 입력 샘플에 대해서  $N_{corr}$ 개의 교차상관관계의 최대값을 추적하는 것이 된다. 이를 위해 입력 메모리 (input memory)에 저장되어 있는 샘플들은 구조의 특성에 맞는 입력 패턴이 인가될 수 있도록 PSS 검출기에서 제어 되어야 한다. 검출기의 출력은 정해진  $N_{ID}^{(2)}$ 와 integer CFO 조합에 대한  $d_{u,t}^*(i)$ 와 입력 y(n) 사이의 교차상관관계 크기가 최대가 되는 n과 최대값이다.

모든  $N_{ID}^{(2)}$ 와 integer CFO 조합 중에서 교차상관관계의 크기가 최대인 조합을 찾기 위해 PSS 검출기를 병렬

로 구성하여 동시에 연산을 진행할 수도 있지만, 본 논문에서는 하드웨어 복잡도를 줄이기 위해서 하나의 검출기로  $d_{u,t}^*(i)$ 를 바꾸어가면서 반복 연산하는 구조에 대해서만 설명하도록 한다.

그림 10의 구조에서는  $N_{ID}^{(2)}$ 와 integer CFO 조합에 따라  $d_{u,t}^*(i)$ 를 바꿀 수 있도록  $d_{u,t}^*$ 저장소가 포함되어 있다. 기지국에서 전송하는 PSS OFDM 심볼의 패턴은 3.1 장의 그림 4를 통해 알아본 바와 같이 실수부는 좌우 대 칭이고 허수부는 좌우상하대칭인 특징이 있다. 이를 이용하면 256개의 샘플을 전부 저장하지 않고 첫 129개만 저장해서 전체 패턴을 표현할 수가 있기 때문에  $d_{u,t}^*(i)$ 의 저장 공간을 효율적으로 사용할 수가 있다.

PSS 검출기를 구현하기 위해서는 교차상관관계 계산기 외에 식 (6)을 구현하기 위한 복소수 크기 계산 및 최대값 추적기가 필요하다. PSS 검출을 위해서는 정확한 교차상관관계의 크기를 구하는 것이 목적이 아니라 상대적인 크기 비교가 목적이다. 따라서 교차상관관계의 실수부의 제곱과 허수부의 제곱을 계산하기 보다는 L1 norm 방식을 사용하여 실수부와 허수부의 절대값의합으로 근사하여 계산해도 크기 비교에 무리가 없다.

앞에서 설명한  $N_{ID}^{(2)}$ 와 integer CFO의 조합에 따라 유연한 반복 동작을 하기 위해서는 그림 10과 같이 PSS 검출기는 CPU와 연결되어 소프트웨어와 같이 co-work 할수 있는 구조가 효율적이다. 또한, PMAC 구조의 경우입력 메모리에 저장되어 있는 샘플들을 여러 번 나누어연산을 하고 각각의 연산 결과를 종합하여 전체 입력에 대한 결과를 도출하여야 하므로 효율적이고 유연한 동작을 위해서 소프트웨어의 제어가 필요하다. 본 논문에서 설명하는 PSS 검출기의 구동 소프트웨어 동작 순서는 다음과 같이 요약할 수 있다.

- a. 입력 메모리에 다운샘플링된 신호 저장 대기

- b.  $d_{u,t}^*$ 저장소에  $d_{u,t}^*(i)$  저장

- c. 교차상관관계 연산 및 최대값 추적 (하드웨어)

- d. (c) 완료까지 대기 후 결과 수집

- e. (b) ~ (d) 반복

- f. 수집된 결과로부터  $N_m^{(2)}$ 와 integer CFO,

SSB 시작점 결정

(e)의 반복 횟수는  $N_D^{(2)}$ 의 경우의 수 3개와 검토하고 자 하는 integer CFO의 개수의 곱으로 결정된다.

PMAC 구조는 (255+P) 개의 입력 샘플이 인가되어 P개의 교차상관관계에 대한 평가를 하는 것이기 때문에 (c)의 과정 내부에서  $\lceil N_{orr}/P \rceil$  회 반복 동작을 해야 하고, 이 반복 동작 사이에도 소프트웨어가 부분 결과를 획득하고 다음 부분 연산 시작을 위한 작업을 처리해야 한다.

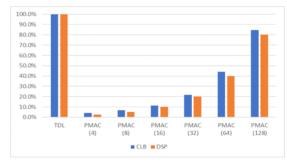

본 논문에서는 앞에서 설명한 PSS 검출기를 TDL구조와 PMAC 구조 기반으로 설계하고 Xilinx사의 Zynq UltraScale+ RFSoC ZU48DR FPGA칩을 타겟하여 구현하였다. 앞에서 설명한 효율적인 하드웨어 구현을 위해서  $d_{u,t}^*(i)$  패턴은 129개만 저장하도록 하였으며, 복소수크기도 L1 norm으로 근사하여 비교하였다.

**Table. 2** Resource usage of PSS sequence decoder in Xilinx UltraScal+ RFSoC (ZU48DR)

|         | CLB     | CL             |              |          |       |

|---------|---------|----------------|--------------|----------|-------|

| Arch.   |         | LUT<br>(logic) | LUT<br>(mem) | FF       | DSP   |

| TDL     | 4,350   | 17,077         | 32           | 27,934   | 960   |

|         | (3,624) | (15,491)       | (32)         | (15,523) | (960) |

| PMAC    | 188     | 858            | 160          | 488      | 24    |

| (P=4)   | (94)    | (412)          | (0)          | (176)    | (24)  |

| PMAC    | 298     | 1,330          | 160          | 796      | 48    |

| (P=8)   | (193)   | (824)          | (0)          | (352)    | (48)  |

| PMAC    | 499     | 2,262          | 160          | 1,412    | 96    |

| (P=16)  | (364)   | (1,648)        | (0)          | (704)    | (96)  |

| PMAC    | 942     | 4,015          | 160          | 2,647    | 192   |

| (P=32)  | (731)   | (3,296)        | (0)          | (1,408)  | (192) |

| PMAC    | 1919    | 7,601          | 160          | 5,118    | 384   |

| (P=64)  | (1528)  | (6,592)        | (0)          | (2,816)  | (384) |

| PMAC    | 3675    | 14,790         | 160          | 10,061   | 768   |

| (P=128) | (3041)  | (13,184)       | (0)          | (5,632)  | (768) |

표 2는 구조에 따른 FPGA 구성요소의 사용량을 정리하였다. (() 안의 숫자는 교차상관관계 회로에 사용된 자원의 사용량을 나타낸다.) CLB는 Configurable Logic Block의 약자로 Xilinx FPGA를 구성하는 핵심 범용 조합/순차 회로 자원이다 [9]. CLB는 8개의 LUT (Look-Up Table)과 16개의 플립플롭(FF)을 포함하고 있다. (단, 설계에 사용된 CLB가 포함하는 LUT와 FF가모두 사용되는 것은 아니다.) LUT는 조합회로를 구성하는데 사용되지만, 상황에 따라 메모리나 shift-register로

활용될 수도 있다. 표 2에서 조합회로로 사용된 것은 LUT(logic)으로, 메모리로 활용된 것은 LUT(mem)으로 구분하여 표시하였다.

구조의 특성 상  $d_{u,t}^*(i)$  저장 공간이 TDL의 경우 전부 FF으로 구성되었고, PMAC의 경우 160개의 LUT를 메모리로 활용하여 구성되었다. TDL 구조는 모든  $d_{u,t}^*(i)$  값이 연산에 필요하기 때문에 FF으로 구현될 수밖에 없고, PMAC은  $d_{u,t}^*(i)$  값이 순차적으로 필요하기 때문에 메모리로 구현가능 한 것으로 이해할 수가 있다.

표 2 에서 DSP는 Xilinx UltraScale 구조 FPGA에서 사용되는 디지털 신호 처리 유닛을 나타낸다. DSP는 27 비트 덧셈기와 27x18 곱셈기 등을 포함하여 다양한 연산에 활용된다 [10]. 교차상관관계 연산을 위한 복소 곱셈기와 덧셈기는 DSP를 이용하여 구현된다고 이해할수 있다.

ZU48DR은 총 53,160개의 CLB와 4,272개의 DSP를 포함하고 있는 대용량 FPGA이다. 표 2의 구현 결과를 보면 TDL 기반의 PSS 검출기는 ZU48DR CLB의 약 8.2%, DSP의 약 22.5%를 차지하는 것을 알 수 있다. 이는 다른 기능을 포함하여 5G 시스템을 구성하는 경우부담되는 크기이기 때문에, 복잡도를 줄일 수 있는 구조가 요구 될 것이다. 이 때 고려될 수 있는 구조가 PMAC 기반의 구조이다.

Fig. 11 Complexity comparison

그림 11은 CLB와 DSP의 사용량을 TDL 구조를 기준으로 하여 그래프로 나타낸 것이다. P=128인 경우 TDL 복잡도의 80% 이상이지만, 연산 시간이 소프트웨어 지연 포함 2배 이상 길어지기 때문에 매력적인 옵션은 아니다. 하지만, P=64 이하의 PMAC은 TDL 기준으로 약  $4\% \sim 45\%$  복잡도로 구현 가능하기 때문에, 연산속도와 tradeoff를 고려해 볼 수 있을 것이다.

### Ⅴ. 결 론

PSS 검출은 5G NR 통신에서 가장 중요하고 어려운 문제 중 하나이고, 이를 구현할 수 있는 여러 가지 PSS 검출 방식이 연구되어 왔다. 이 중 본 논문에서는 교차 상관관계 기반의 방식에 대해서 기본 검출 원리를 설명하고 PSS 검출기의 하드웨어 설계 방법에 대해서 구체적으로 기술하였다. 또한, 하드웨어 복잡도와 검출 속도를 동시에 고려한 설계에 활용할 수 있도록 구조에 따른하드웨어 구성 방법과 검출 속도를 판단할 수 있는 기준을 제시하였다. TDL 기반의 교차상관관계 구조를 사용하면 검출 속도에서 가장 빠른 성능을 보이지만, 하드웨어 복잡도가 높다. 병렬 MAC 구조를 활용한 교차상관관계 구조는 상대적으로 낮은 복잡도로 구현이 가능하지만, 검출 속도가 늦어지게 된다.

본 논문에서는 PSS 검출기 하드웨어를 다양한 구조로 구현하여 Xilinx사 UltraScale+ RFSoC FPGA의 자원 사용량을 기준으로 하드웨어 복잡도를 분석하였고, PSS 검출기를 포함하는 시스템 구성을 위해 필요한 인터페이스와 효율적이고 유연한 동작을 위한 구동 소프트웨어 동작도 설명하였다.

# **ACKNOWLEDGEMENT**

Following are results of a study on the "Leaders in INdustry-university Cooperation +" Project, supported by the Ministry of Education and National Research Foundation of Korea

Communications, vol. 14, no. 18, pp. 3175-3183, Nov. 2020.

- [5] A. Chakrapani, "On the design details of SS/PBCH, signal generation and PRACH in 5G-NR," *IEEE Access*, vol. 8, pp. 136617-136637, Jul. 2020.

- [6] M. Morelli and M. Moretti, "A Robust Maximum Likelihood Scheme for PSS Detection and Integer Frequency Offset Recovery in LTE Systems," *IEEE Transactions on Wireless Communications*, vol. 15, no. 2, pp. 1353-1363, Oct. 2016.

- [7] A. Golnari, M. Shabany, A. Nezamalhosseini, and G. Gulak, "Design and Implementation of Time and Frequency Synchronization in LTE," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 23, no. 12, pp. 2970-2982, Jan. 2015.

- [8] K. Chang and S. Lee, "Robust OFDM-Based Synchronization Against Very High Fractional CFO and Time-Varying Fading," *IEEE Systems Journal*, vol. 14, no. 3, Jan. 2020.

- [ 9 ] UG574 UltraScale Architecture Configurable Logic Block User Guide [Online]. Available: https://www.xilinx.com/ content/dam/xilinx/support/documentation/user\_guides/ug5 74-ultrascale-clb.pdf

- [10] UG579 UltraScale Architecture DSP Slice User Guide [Online]. Avaliable: https://www.xilinx.com/content/dam/xilinx/support/documentation/user\_guides/ug579-ultrascale-dsp.pdf

# References

- [1] NR; Physical Channels and Modulation (Release 16), document TS38.211, V.16.3.0, 3GPP, Sep. 2020.

- [2] S. Won and S. W. Choi, "A Tutorial on 3GPP Initial Cell Search: Exploring a Potential for Intelligence Based Cell Search," *IEEE Access*, vol. 9, pp. 100223-100263, Jul. 2021.

- [3] D. Wang, Z. Mei, H. Zhang, and H. Li, "A Novel PSS Timing Synchronization Algorithm for Cell Search in 5G NR System," *IEEE Access*, vol. 9, pp. 5870-5880, Jan. 2021.

- [4] V. Vahidi and E. Saberinia, "Downlink Data Transmission for High-Speed Trains in 5G Communication Systems," *IET*

이 진(Jin Lee)

한국과학기술원 (KAIST) 전기 및 전자공학 박사 삼성전자 책임/수석 연구원 현재 평택대학교 조교수 ※관심분야: 무선 통신 반도체,

임베디드 시스템, System on Chip