# ♣차세대 뉴로모픽 • 소재 및 소자

글\_김상범교수 | 서울대학교 재료공학부

# 1. 서론

최근 인공지능 기술은 여러 기술적인 돌파 구 마련을 통해 자율주행차, 로보틱스, 국방 기술과 같이 경제와 사회에 파급력이 큰 분야 에 적용될 가능성이 커지면서 기업 수준을 넘 어서서 국가 전략으로서도 큰 관심을 받고 있 다. 인공지능 기술의 빠른 발전 속도로 인해 인공지능 연산량은 3.5개월마다 2배씩 폭발적 으로 늘어나는 경향을 보이고 있다 [1]. 이는 그동안 무어의 법칙에 따라 증가해온 컴퓨터 연산 능력의 발전 속도를 크게 뛰어 넘는다. 그러므로 인공지능 연산에 있어서 하드웨어 연산 속도를 발전시킬 수 있는 새로운 방안이 필요하다. 이 같은 배경에서 기존의 연산 장치 의 동작원리로 대표되는 폰 노이만 아키텍처 에서 벗어난 새로운 연산 장치 패러다임의 필 요성이 대두되고 있고 뉴로모픽 컴퓨팅은 그 중 하나이다. 뉴로모픽 소자와 재료는 뉴로모 픽 컴퓨팅을 구현하는 핵심적인 기술이다. 본 고에서는 대표적인 뉴로모픽 소자인 시냅스 소자에 요구되는 특성이 무엇이며 해당 요구 사항을 만족시키기 위해 최근 연구 동향이 어 떻게 진행되었는지를 살펴보고자 한다.

# 2. 차세대 소재 및 소자에 기반한 뉴로모픽 컴퓨팅

## 2.1 시냅스 소자를 이용한 뉴로모픽 컴퓨팅의 장점

뉴로모픽 컴퓨팅 개발은 크게 2가지 방향으로 이루어지고 있다. 첫째, 두뇌 동작원리를 모사하는 방법을 통해 기존의 인공지능을 뛰 어넘는 새로운 알고리즘을 개발한다. 알고리 증에 중심을 둔 연구에서는 새로운 뉴로모픽 소자를 반드시 필요로 하지는 않는다. 예를 들어 인텔 연구소(Intel Labs)는 2017년에 Loihi라고 이름 붙인 뉴로모픽 프로세서 테스트 칩을 신소자 적용 없이 14 nm Si CMOS 공정으로 제작하여 발표하였다 [2]. Loihi는 차세대인공신경망으로 불리는 스파이킹 뉴럴 네트워크의 여러 특성을 충실히 구현한 프로세서로서 현존하는 소자 기술을 바탕으로 차세대인공지능 알고리즘 개발을 목표로 한다.

뉴로모픽 컴퓨팅 개발의 두 번째 방향은 인 공지능 연산을 더 빠르고 효율적으로 수행하는 뉴로모픽 신소자 개발을 목표로 한다. 이를 위해 다양한 뉴로모픽 소자들이 연구되고 있으며, 가장 대표적인 것이 인공신경망에서 시냅스의 역할을 대신할 수 있는 시냅스 소자이다. 시냅스 소자가 인공지능 연산을 더 빠르고 효율적으로 수행할 수 있을 것으로 기대되는 이유는 복합적인데 가장 중요한 이유는 크게 두 가지이다. 첫째, 시냅스 소 자가 시냅스 가중치를 저장하는 메모리의 역할과 행렬과 벡터의 곱과 같은 연산을 수행하는 역할을 동시에 수행할 수 있기 때문이다. 이를 통해 반도체칩이 차지하는 면적을 줄임과 동시에 기존의 폰 노이만 아키텍처에서 메모리에 저장되어 있던 시냅스 가중치를 실제 연산을 수행할 연산기로 가지고 오는데 걸리는 시간과 에너지를 절약할 수 있다.

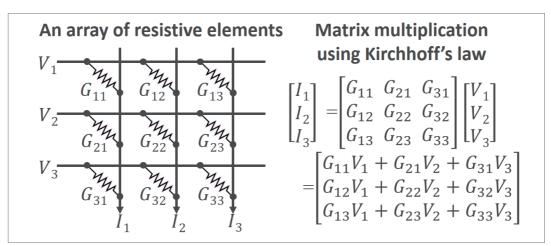

시냅스 소자가 인공지능 연산을 더 빠르고 효율적으로 수행할 수 있을 것으로 기대되는 두번째 이유는 행렬과 벡터의 곱과 같은 연산을 수행함에 있어서 기존 컴퓨터 아키텍처에서는 불가능했던 최고수준의 병렬처리를 가능케 해 처리속도가 빨라진다는 점이다. 시냅스소자의 중요한 특성 중에 하나가 가변저항과같이 옴의 법칙을 따르며 저항값 변화가 가능한 소자라는 점이다. 시냅스의 가변저항과 같은 성질을 이용하면 그림 1에서 볼 수 있듯이벡터와 행렬의 곱 연산을 가변저항 어레이를통해 아날로그 방식으로 수행할 수 있다. 어레

고림 1 ▶ 가변저항 어레이를 이용하여 벡터와 행렬 곱 연산이 수행하는 원리에 대한 설명. 각각의 가변저항 소자는 시냅스 소자 하나에 해당된다. 실제 시냅스 소자는 2개 이상의 단자를 가질 수 있지만, 본 그림에서는 가변저항적인 성질을 갖는 단자 2개 외에는 그림에서 생략하였다.

이에 있는 시냅스로 구현된 가변저항 소자들의 컨덕턴스(conductance) 값으로 행렬을 나타내고, 벡터값으로 전압을 수평 방향의 도선들에 입력한 뒤에, 그라운드에 연결된 수직 방향의 도선들로부터 전류 값들을 읽어내면 해당 전류들은 행렬와 전압 벡터의 곱을 벡터 형태로 나타내게 된다. 그림 1에서는 3×3의 크기를 갖는 작은 시냅스 어레이를 예로 들었으나, 같은 원리를 이용하여 임의의 크기에 해당하는 행렬과 벡터의 곱셈도 실행이 가능하다. 예를 들어 10°×10°의 크기를 시냅스 어레이를 이용한다면 10°번의 곱셈과~10°번의 덧셈을 단 한번의 동작으로 실행하는 셈이 된다.

위에서 기술한 2가지 장점(메모리와 연산을 단일 소자에서 수행, 최고 수준의 병렬 연산) 외에도 시냅스 소자 활용 시 기대되는 추가적 인 장점으로는 하나의 시냅스 소자에 아날로 그 방식으로 수 bit 해상도 수준의 값을 저장 함으로써 필요한 메모리 소자의 개수를 줄이 는 효과, 비휘발성으로 인한 전력 소모 절감 효과, 단순한 소자 구조로 인한 면적 감소 효 과 등이 있다. 이와 같은 시냅스 소자에 기반 한 뉴로모픽 프로세서의 다양한 장점을 실제 로 구현하는 데 성공했을 때 얻을 수 있는 기대 효과를 예측한 연구에 따르면 딥러닝에 가장 최적화되어 있는 GPU (graphical processing unit)와 비교했을 때 전력 효율과 가속 성능이 천 배에서 만 배에 이를 것으로 예측되고 있다 [3].

### 2.2 시냅스 소자에 요구되는 특성

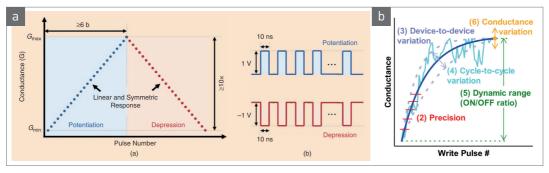

이와 같은 다양한 시냅스 소자의 장점이 충실히 발현되기 위해서는 시냅스 소자의 성능 이 우수해야 한다. 시냅스 소자의 성능을 평가할 수 있는 기준은 여러 논문에서 다양하게 제 시되었는데 [3,4], 일반적인 메모리 소자에 요 구되는 retention, cycling endurance, 에너지 소모량과 같은 조건 외에도 시냅스 기능 구현 에 추가로 요구되는 조건이 상당이 많으며 이 러한 추가적인 조건들은 기존 메모리 소자들 로는 쉽게 달성하기 어려운 특성들이다. 그림 2는 이러한 조건들 중에 대표적인 6가지를 요 약해서 일목요연하게 보여주고 있다. 여러 요 구 조건 중에 가장 대표적인 것은 가중치 갱신 과 관련된 선형성과 대칭성이다. 선형성과 대 칭성이 확보되지 않으면 시냅스 소자 어레이

그림 2 ▶ 시냅스에 요구되는 특성. (a) 시냅스 가중치 갱신의 선형성과 대칭성. 오른쪽의 펄스 모양은 동일한 종류의 펄스를 반복적으로 사용했을 때 선형성과 대칭성 달성이 가능해야 함을 나타낸다 [6]. (b) 선형성과 대칭성 외에 요구되는 특성 [4].

내의 시냅스 소자들을 병렬적으로 동작시키는 것이 불가능해지기 때문에, 위에서 소개한 시냅스 소자 어레이의 장점이 더 이상 발휘될 수 없다. 또한, 선형성과 대칭성 외에 variation과 관련된 조건이 3가지나 포함되어 있는데 이는 시냅스 소자가 연산을 아날로그 방식으로 수행하기 때문에 variation이 연산 정확도를 직접적으로 저하시키기 때문이다 [5].

#### 2.3 저항변화 소재에 기반한 시냅스 소자

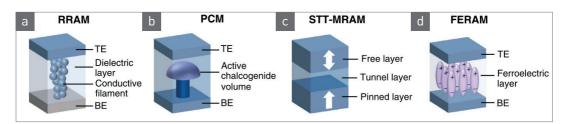

시냅스 소자 연구의 초창기에는 그림 3에 표시된 가변저항의 특성을 가지는 여러 소재에 기반한 소자 연구가 대부분이었다. 특히 RRAM (resistive random-access memory)과 PRAM (phase-change random access memory)은 이미 차세대 메모리 소자로서 오랜 기간 연구가 축적되었고 최대/최소 저항비가 우수하며 소자 미세화 가능성도 어느 정도 검증되었으며 우수한 연구 인프라가 갖추어져 있었기때문이다. 그러나 RRAM과 PRAM 기반으로는 충분한 수준의 선형성과 대칭성을 가지는 시냅스 소자를 아직 구현하지 못하고 있다. 이는 PRAM과 대부분의 RRAM 소자의 동작원리상선형성과 대칭성 확보가 쉽지 않은 이유들이존재하기때문이다.

PRAM의 경우 저항값을 선형적으로 감소시

키기 위해 상변화 물질의 결정화 위치와 속도 를 정밀하게 조절해야 한다. 하지만 PRAM의 경우 결정화를 위해 전기적 펄스를 가했을 때 소자 내부의 온도 분포가 균일하지 않으며, 같 은 전기적 펄스를 가하더라도 여러 소자 간의 미세한 크기 차이 등으로 인해 온도 차이가 발 생하는데, 상변화 물질의 결정화 속도가 온도 에 의해 크게 좌우되기 때문에 [7] 결정화 정 도를 정밀하게 제어하는 것이 상당히 어렵다. 또한, PRAM의 저항값을 점차적으로 증가시 키는 과정 역시 상변화 물질의 온도가 녹는점 이상으로 올라가는 영역이 펄스의 회수에 관 계없이 거의 일정하기 때문에 저항값을 점차 적으로 증가시키기 어렵다. 이러한 문제점들 을 해결하기 위하여 confined 구조 [8], 벽 형태 의 bottom electrode [9], sub-nanosecond 펄스 [10] 등을 이용하여 선형성과 대칭성을 향상시 키는 연구 결과가 최근에도 꾸준히 발표되고 있다.

대부분의 RRAM은 금속 이온 또는 산소 결핍을 이동시켜 전도성 필라멘트를 형성하거나 파괴함으로서 저항을 변화시키는 동작 원리를 가지고 있다. 따라서, 저항을 점진적으로 중가 또는 감소시키기 위해서는 필라멘트의 길이 또는 굵기를 정밀하게 조절할 수 있어야 하지만 필라멘트의 형성과 파괴 속도가 빠르고

그림 3 ▶ 두 개의 단자를 가지는 다양한 시냅스 소자. 모든 시냅스 소자들이 저항변화 소재와 원리에 기반을 두고 있다 [12].

확률적 거동을 보이며 전기장의 크기 등에 매우 민감하기 때문에 필라멘트의 위치, 모양, 형성/파괴 속도 조절이 쉽지 않다. 이를 극복하기 위해 단결정 SiGe를 이용하여 필라멘트의 위치를 고정시키거나 [11] 필라멘트 형성하지 않고 계면 특성을 변화시킴으로써 저항을 변화시키는 방법 등이 연구되고 있다.

#### 2.4 전하저장형 시냅스 소자

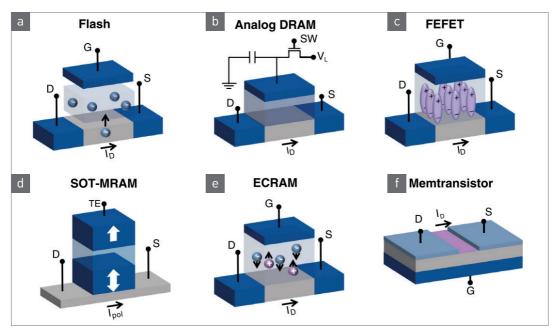

시냅스에 요구되는 특성을 충족시킬 수 있는 동작원리를 지니는 새로운 시냅스 소자를 개발하는 노력도 계속되고 있다. 가장 대표적으로는 커패시터 등을 이용하여 전하를 저장하여 시냅스가중치를 구현하는 연구이다. 그림 4(b)와 같이 커패시터와 트랜지스터를 이용하여 구현된 아날로그 DRAM 시냅스의 동작

워리는 다음과 같다. 커패시터에 저장된 전하 량에 의해 결정된 트랜지스터의 gate 전압이 source와 drain 사이의 저항값을 결정하며 해 당 저항값의 역수가 시냅스 가중치를 나타내 게 된다. SW에 들어가는 펄스 신호의 전압과 펄스 폭을 조절하면 커패시터에 원하는 양만 큼 전하를 추가하거나 제거하는 것이 가능하 다. 이와 같은 원리를 따르면 시냅스 가중치 갱 신의 선형성과 대칭성을 대폭 향상시킬 수가 있음이 이미 실험적으로 제시되었다 [13]. 이 러한 커패시터 기반 시냅스 소자의 가장 큰 단 점은 PRAM과 RRAM 대비 상대적으로 소자의 면적이 크고 트랜지스터와 커패시터의 누설 전류로 인해 retention 시간이 짧다는 점이다. 짧은 retention 시간으로 인해 학습 정확도가 저하되는 문제점은 on-chip 훈련을 고속으로

고림 4 ► 세 개의 단자를 가지는 시냅스 소자들 [12]. 두 단자 사이의 저항값을 세 번째 단자에 전압 또는 전류 등의 신호를 가하여 변화시키는 원리에 기반을 두고 있다. (a), (b), (e)의 경우 세번째 단자를 통해 전자나 이온 등의 전하를 이동을 정밀하게 제어함으로써소자 내에 저장된 전하의 양과 채널의 저항값을 조절하는 전하저장형 시냅스 소자이다.

수행하여 어느 정도 극복 가능하다는 것이 알려져 있으며 [14] 누설전류를 최소화하여 retention 시간을 늘리기 위한 연구도 진행 중 이다 [15].

이 외에도 다양한 소재들을 이용한 시냅스 소자가 연구되고 있다. 예를 들어 HfO<sub>2</sub>와 같 이 기존 반도체 공정과 호환성이 확보되어 있 고 소자 미세화에 적합한 강유전체 물질 [16], 2차원 물질 [17]과 같이 다양한 응용이 가능한 소재에 기반을 둔 시냅스 소자와 배터리에 사 용되던 소재를 이용하여 저장된 이온의 양으 로 시냅스 가중치를 나타내는 새로운 원리에 기반한 시냅스 소자들도 활발히 연구되고 있 으며 연구 초기에 있음에도 시냅스 소자 성능 을 빠른 속도로 개선해 나가고 있어서 향후 연 구 결과에 따라 기존에 연구되던 시냅스 소자 들보다 더 나은 특성을 보일 가능성이 있을 것 으로 기대된다. 갖추어야 하므로, 기존 메모리 소자들이 갖추어야 할 특성 외에 가중치 갱신의 선형성과 대칭성 등 추가적인 특성을 가져야 한다. 현재 이상적인 시냅스 소자의 특성을 모두 갖춘소자는 없으며 차세대 메모리 소자인 PRAM, RRAM 외에 커패시터 기반의 전하저장형 시냅스 소자 등도 활발히 연구되고 있다. 시냅스소자의 동작원리를 바탕으로 했을 때 전하저장형 시냅스 소자는 선형성과 대칭성 확보에 유리하나 retention 문제와 상대적으로 큰소자 크기가 단점이다. 향후 다양한 소재와 동작원리를 갖는 소자 연구를 통해 이상적인 시냅스소자가 개발되어 인공지능 연산 속도에 획기적인 발전이 이루어지길 기대해 본다. ♣️

# 3. 맺음말

인공지능 기술의 발전을 지속하기 위해서는 인공지능 연산을 저전력 고성능으로 실행할수 있는 컴퓨터의 개발이 필수적이다. 아날로 그 방식으로 시냅스 가중치를 저장할 수 있는 시냅스 소자는 인공지능 연산 효율을 수만배정도까지도 중대시킬 수 있을 것으로 기대된다. 그러나 시냅스 소자는 단순히 가중치를 저장하는 것에 그치지 않고 저장된 가중치를 피연산자로 이용하여 연산을 수행하는 기능을

39

## 참/고/문/헌

- [1] X. Xu et al., Nat. Electron., 1, 216 (2018). [doi: 10.1038/s41928-018-0059-3]

- [2] M. Davies et al., IEEE Micro, 38, 82 (2018). [doi: 10.1109/MM.2018.112130359]

- [3] T. Gokmen and Y. Vlasov, Front, Neurosci., 10, 1

- [4] R. Islam et al., J. Phys. D. Appl. Phys., 52, 113001 (2019).[doi: 10,1088/1361-6463/aaf784]

- [5] W. Haensch, T. Gokmen, and R. Puri, Proc. IEEE, 107, 108, (2019). [doi: 10.1109/JPROC.2018.2871057]

- [6] J. Woo and S. Yu, IEEE Nanotechnol, Mag., 12, 36 (2018).[doi: 10.1109/MNANO.2018.2844902]

- [7] G. W. Burr et al., J. Appl. Phys., 111, 104308 (2012)[doi: 10.1063/1.4718574]

- [8] W. Kim et al., 2019 Symposium on VLSI Technology (2019) p. 66. [doi: 10.23919/VLSIT.2019.8776551]

- [9] S. La Barbera et al., Adv. Electron, Mater., 4, 1 (2018)[doi: 10.1002/aelm.201800223]

- [10] K. Stern et al., IEEE Electron Device Lett., 3106, 1 (2021)

- [doi: 10.1109/led.2021.3094765]

- [11] S. Choi et al., Nat. Mater., 17, 335 (2018). [doi: 10.1038/s41563-017-0001-5]

- [12] D. Ielmini and G. Pedretti, Adv. Intell. Syst., 2, 2000040, (2020). [doi: 10.1002/aisy.202000040]

- [13] S. Kim, T. Gokmen, H. M. Lee, and W. Haensch, IEEE 60th International Midwest Symposium on Circuits and Systems (MWSCAS), (2017) p. 422. [doi: 10.1109/MWSCAS.2017.8052950]

- [14] Y. Li et al., 2018 IEEE Symposium on VLSI Technology (2018) p. 25. [doi: 10.1109/VLSIT.2018.8510648]

- [15] D. Saito et al., IEEE Trans. Electron Devices, 67, 4616 (2020). [doi: 10.1109/TED.2020.3025986]

- [16] M. Jerry et al., Tech. Dig. Int. Electron Devices Meet, (2017), p. 6.2.1. [doi: 10.1109/IEDM.2017.8268338]

- [17] R. Xu et al., Nano Lett., 19, 2411 (2019). [doi: 10.1021/acs.nanolett.8b05140]

성명 김상범 학력 2001년 서울대학교 전기공학부 공학학사 2005년 스탠포드 대학교 Electrical Engineering 공학석사 2010년 스탠포드 대학교 Electrcial Engineering 공학박사 경력 2010년 - 2012년 IBM Research 박사후연구원

2012년 ~ 2018년 IBM Research Research Staff Member 2018년 ~ 현재 서울대학교 재료공학부 조교수