ISSN: 1226-7244 (Print) ISSN: 2288-243X (Online)

논문번호 21-02-22

148

하이브리드 게이트 드라이버를 위한 회로 디자인 방법과 성능 평가에 관한 연구 A Study on the Circuit Design Methodology and Performance Evaluation for Hybrid Gate Driver

조 근 호\*★

Geunho Cho\*\*

#### Abstract

As Head-Mounted Displays(HMDs), which are mainly used to maximize realism in games and videos, have experienced increased demand and expanded scope of use in education and training, there is growing interest in methods to enhance the performance of conventional HMDs. In this study, a methodology to utilize Carbon NanoTubes(CNTs) to improve the performance of gate drivers that send control signals to each pixel circuit of the HMD is discussed. This paper proposes a new circuit design method that replaces the transistors constituting the buffer part of the conventional gate driver with transistors incorporating CNTs and compare the performance of the suggested gate drive with that of a gate driver comprising only conventional transistors via simulations. According to the simulation results, by including CNTs in the gate driver, the output voltage can be increased by approximately 0.3V compared to the conventional gate driver high voltage(1.1V) at a speed of 12.5 GHz and the gate width also can be reduced by up to 20 times.

## 요 약

과거 주로 게임과 동영상 재생에 있어 리얼함을 극대화하기 위해 사용되었던 HMD(Head Mount Display)의 수요가 증가하고, 그 활용 범위가 교육과 훈련 등으로 확대되면서, 기존 HMD의 성능을 향상시킬 수 있는 방안에 대한 관심이 높아지고 있다. 본 논문에서는 HMD의 각 화소 회로에 제어 신호를 보내는 gate driver의 성능을 향상시키기 위해 CNT를 포함한 트랜지스터를 활용하는 방법에 대해 논하고자 한다. 기존 gate driver의 버퍼부를 구성하는 트랜지스터를 CNT를 포함한 트랜지스터로 교체하는 회로 설계 방법을 제안하고, 그 성능을 회로 시뮬레이션을 통해 기존 트랜지스터로만 구성된 gate driver의 성능과 비교해 보고자 한다. 시뮬레이션 결과, gate driver에 CNT를 포함할 경우 12.5 GHz의 속도로 기존 gate driver 대비약 0.3V 증가된 출력 전압(1.1V)을 얻을 수 있었으며, 최대 20배의 gate width를 줄일 수 있었다.

Key words: Gate Driver, CNTFET, CNT, CNT Density, Digital Circuit

E-mail: choroot@skuniv.ac.kr, Tel: +82-2-940-7730

Acknowledgment

This work was supported by the National Research Foundation of Korea(NRF) grant funded by the Korea government (MSIT) (No.2018R1C1B5086081) \* MSIT: Ministry of Science and ICT

The EDA tool was supported by the IC Design Education Center(IDEC), Korea

Manuscript received Jun. 4, 2021; revised Jun. 17, 2021; accepted Jun. 24, 2021.

This is an Open-Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License (http://creativecommons.org/licenses/by-nc/3.0) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

<sup>\*</sup> Assistant Professor, Dept. of Electronics Engineering, Seokyeong University

<sup>★</sup> Corresponding author

# I . 서론

최근 각광을 받고 있는 AR(Augmented Reality, 증강현실), VR(Virtual Reality, 가상현실), 그리고 MR(Mixed Reality, 혼합현실) 기술은, 기존에 널리 알려진 게임에서의 활용을 넘어서 다양한 교육과 훈련 등 폭넓은 분야로 활용 범위를 넓히고 있다. 이러한 상황에서 AR, VR, 그리고 MR 기술을 실감 나게 구동할 수 있는 HMD에 대한 관심 역시 높아 져 HMD를 통해 실감나는 영상을 재생할 수 있는 노력이 지속적으로 이어지고 있다. HMD는 일반적 으로 사용자의 눈에 가깝게 고정한 상태에서 빠른 화면 전환을 매우 넓은 시야로 제공해야 하기 때문 에, TV 또는 스마트폰용 디스플레이에 비해 훨씬 더 높은 해상도와 재생 속도(60HZ 이상)로 구동 되 어야 한다. 따라서, HMD용 디스플레이의 각 픽셀 회로에 구동 신호를 보내는 gate driver는 TV 또는 스마트폰용 디스플레이에서 사용되는 gate driver 보다 많은 픽셀 회로에 빠른 속도로 좁은 배선을 따라 제어 신호를 보낼 수 있어야 한다. 더욱이, HMD는 일반적으로 사람 머리 장착이 용이해야 하기 때문에, 위에서 언급한 gate driver를 포함한 HMD 용 디스플레이는 그 형태를 자유롭게 변형할 수 있는 플렉서블 디스플레이를 선호한다. 변형이 자유로운 플렉서블 디스플레이를 구현하기 위해서, gate driver 를 구성하는 트랜지스터는 유연한 반도체 재료로 제작되어야 하므로, 높은 기계적 유연성을 가지고 있는 organic semiconductor, TMD(Transition Metal Dichalcogenide), 그리고 CNT(Carbon NanoTube) 등이 플렉서블 디스플레이를 제작하기 위한 후보 물질로서 높은 관심을 받고 있다[1]-[5].

CNT는 약 lum의 자유이동경로(mean free path)를 갖고 있어 낮은 바이어스 전압으로 전자의 ballistic 혹은 near-ballistic 이동을 가능하게 만든다. 차세대 반도체로 각광받고 있는 CNTFET(Carbon NanoTube Field Effect Transistor)은 이러한 CNT를 소스 (source)와 드레인(drain) 사이의 전류 통로로 활용하여, 반도체 소자의 성능을 CV/I 측면에서 약 13배의 성능향상을 구현할 수 있다고 알려져 있다. 이러한 CNTFET의 장점을 활용하여 최근 CNTFET 으로 구성된 Intel 4004 마이크로프로세서를 구현하는데 성공하였으나, 현재 공정 개발 단계에서 CNT의 밀도, 즉, CNTFET 안에 충분히 좁은 간격으로

많은 수의 CNT를 나란히 배치하는 공정이나 누설 전류를 제어하는 능력이 부족하여, 칩 전체의 성능을 높이는데 어려움을 겪고 있다. 이러한 어려움을 극복하기 위한 다양한 연구가 최근까지 이어지고 있어, CNT의 밀도를 100~200 CNT/um까지 올릴 수 있는 기술, 기존 CNTFET의 구조를 변형하여 전력 손실을 줄이기 위한 기술, 그리고 기존 반도체 소자와 CNTFET을 결합한 하이브리드 CNTFET 기술 등 다양한 방안이 제시되고 있다[6]-[13].

디스플레이의 gate driver는 일반적으로 제어부 (control part)와 버퍼부(buffer part)로 나누어져 있으며, 버퍼부는 디스플레이 전체를 가로지르는 배선에 높은 전압과 전류를 빠른 속도로 공급하는 역할을 하고 있어, 버퍼부를 구성하는 반도체는 그 크기가 매우 크고, 큰 스트레스 아래 구동되도록 되어 있어, 전체 gate driver의 성능과 신뢰성을 높 이는데 걸림돌로 작용하는 것으로 알려져 있다. 이 러한 상황에서, 기존 반도체 소자보다 높은 성능을 보여주는 CNTFET은 기존 gate driver 성능을 높 일 수 있는 소중한 대안으로 관심 받고 있다. 특히, CNT를 이용한 반도체 소자는 유연기판 위에서도 구현할 수 있어 앞서 언급한 HMD용 디스플레이의 형태를 자유롭게 변형하는데 큰 도움을 줄 수 있을 것으로 기대된다. 이에 더해, gate driver의 버퍼부 는 회로적으로 그리고 layout 측면에서 그 구조가 매우 단순하고, 패널 전체에 반복되는 특성을 가지 고 있어, 앞서 언급한 CNT 배치 밀도 문제로부터 보다 자유로워질 수 있을 것으로 기대된다. 무엇보 다, 앞서 언급한 바와 같이 CNT를 활용한 반도체 소자는 기존 반도체 소자와 함께 사용할 수 있는 가능성을 가지고 있어, gate driver의 버퍼부는 CNT를 활용한 반도체 소자로 제어부는 기존 반도 체 소자로 구성할 수 있다면, CNT를 활용한 트랜 지스터의 높지만 불안한 성능을 기존 트랜지스터 로 정교하게 컨트롤할 수 있는 gate driver를 구성 할 수 있을 것으로 기대된다[3][5][10].

따라서, 본 논문에서는 높은 성능에도 불구하고 불안한 공정으로 주목 받지 못했던 CNTFET을 높 은 전압/전류 성능을 요구하는 HMD용 gate dri -ver의 버퍼부에 도입하는 회로 디자인 방법을 소 개하고 그 성능 향상 정도를 논의해 보고자 한다. 보다 현실 적인 시뮬레이션 비교를 위해, 본 연구 에서는 최근 [3]에서 제안된 AR/VR Display용 gate driver를 활용하여, 전체 gate driver를 기존 트랜지스터로 구성한 경우와 버퍼부를 CNT가 포함된 트랜지스터로 대체한 경우를 비교하여 어느 정도 성능 향상이 있는 그 차이를 시뮬레이션을 통해 검증해 보고자 한다. 이러한 시뮬레이션 검토에 있어, 기존 반도체 소자와 CNT가 포함된 반도체 소자의성능을 객관적으로 비교하기 위해 본 논문에서는 오랫동안 MOSFET과 CNTFET 회로의 성능 비교에 사용되었던 32nm PTM MOSFET 라이브러리파일과 Stanford 대학교에서 개발한 32nm CNFET라이브러리파일과 Stanford 대학교에서 개발한 32nm CNFET라이브러리파일을 사용하고자 한다[14][15]. 본 논문에서는 편의상 기존 반도체 소자는 MOSFET 그리고 CNT를 활용한 반도체 소자는 CNTFET라부르고자 한다[16]-[18].

# II. 하이브리드 게이트 드라이버

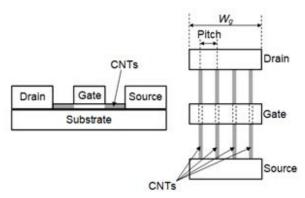

Fig. 1. CNTFET. 그림 1. CNTFET

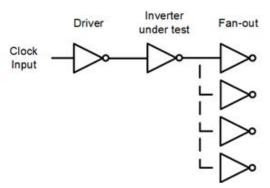

Fig. 2. Inverter Chain. 그림 2. 인버터 체인

차세대 반도체로 각광받고 있는 CNTFET은 그림 1과 같이 CNT를 소스(Source)와 드레인(Drain) 사이에 배치 시켜 낮은 바이어스 전압으로 높은 전 류를 흐를 수 있는 구조를 가지고 있어, 일반적으로 CNTFET 안의 CNT 수가 늘어날수록 동일한 gate 전압에 대해 더 많은 전류를 흘릴 수 있지만, CNT의 수가 증가함에 따라, gate capacitance가늘어나고, CNT 사이의 거리가 가까워지면, 스크리닝 효과(screening effect)에 의해 각 CNT에 흐르는 전류의 양이 줄어들어, CNTFET의 성능을 저하시킬 수 있다[6][7].

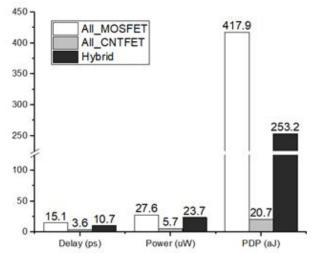

Fig. 3. Delay, Power, and PDP of Inverter Chain. 그림 3. 인버터 체인의 Delay. Power. 그리고 PDP

기존 MOSFET에서 gate width가 늘어날수록 gate를 통해 흐르는 전류의 양이 증가하여 반도체 소자의 성능을 향상시키는 역할을 하지만, 동시에 gate capacitance도 늘어나 반도체 소자의 성능을 감소시키는 역할을 하기 때문에, 반도체 소자의 성능을 측정하고자 할 때는 전통적으로 그림 2와 같인 FO4(Fan Out of 4) 인버터 체인을 활용하여 최적의 반도체 소자 크기를 정해 왔다. 본 논문에서는 MOSFET, CNTFET, 그리고 MOSFET과 CNTFET을 함께 사용하는 Hybrid 회로의 성능을 측정하기위해 그림 2와 같이 전통적인 FO4 인버터 체인을 사용하여 반도체 소자의 성능(Delay, Power, 그리고 PDP)을 시뮬레이션 하였으며, 그 결과를 그림 3에 표시하였다[19].

그림 2의 FO4 인버터 체인에서 모든 반도체 소자를 MOSFET에서 CNTFET으로 변경할 경우, 그림 3과 같이 Delay, Power, 그리고 PDP에 있어서 각각 약 4.2배, 4.8배, 그리고 20.2배의 개선 효과가 있음을 알 수 있다. 여기서, Hybrid 회로의 성능을 측정하기 위해 그림 2의 'Inverter under test'에 해당하는 인버터를 CNTFET으로 교체하여 CNTFET inverter를 MOSFET 인버터 다음에 연결하는 상황을 만들면, 모든 인버터를 MOSFET으로 구현했을 때 보다, Delay, Power, 그리고 PDP에 있어 각각 약 29.3%, 14.3%, 그리고 39.4%의 개선이 이루어짐을 알 수 있다.

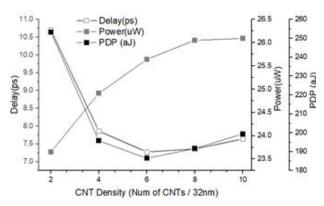

Fig. 4. Delay, Power, and PDP when CNT density of inverter chain is increased.

그림 4. 인버터 체인에서 CNT 밀도가 증가할 때의 Delay, Power, 그리고 PDP

그림 3과 같은 시뮬레이션 결과를 도출할 때, 각 CNTFET의 CNT의 수는 32nm gate width 당 2개 로, CNT 사이에 거리(pitch)를 충분히 확보하였다. 이러한 상황에서 주어진 32nm gate width에 보다 많은 CNT를 배치할 경우, 그 성능 향상 정도를 파 악하기 위해, gate width 그리고 CNT 지름으로부터 CNT 사이의 간격을 MATLAB으로 계산한 후, 그 값을 HSPICE 시뮬레이션에 반영하는 방법으로 CNT Density, 즉, Number of CNTs/32nm를 2CNTs/ 32nm로부터 10CNTs/32nm까지 증가시켰다. CNT Denstiy를 6CNTs/32nm까지 증가시킨 경우, 그림 4와 같이 FO4 inverter chain의 Delay가 줄어듬을 확인할 수 있으나, CNT Density가 6CNTs /32nm 를 넘어서는 경우, 앞서 언급한 스크리닝 효과에 의해 각 CNT에 흐르는 전류의 양이 줄어들면서 Delay가 다시 증가함을 보여주고 있다. 이는 CNT 의 수가 늘어나도 각 CNT에 흐르는 전류의 양이 감소함에 따라 전체 전류의 증가가 CNT 수에 비 례하여 증가하지 못하는 반면, CNTFET의 gate capacitance는 CNT 수에 비례하여 지속적으로 증 가하기 때문으로 판단된다. 이러한 현상은 그림 4

와 같이 CNT의 수가 늘어나도, 더 이상 전체 Power 가 늘어나지 않고, PDP가 증가하는 상황을 통해다시 한 번 확인할 수 있다. 본 논문에서는 MOSFET 회로의 일부분을 CNTFET으로 변경하여 Hybrid 회로를 구성할 경우 얻을 수 있는 성능 향상을 정도를 살펴보는 것이 목표이므로, 그림 4에서 회로의속도를 가장 높게 향상시킬 수 있는 CNT Density (6CNTs/32nm)를 선택하여 AR /VR용 gate driver를 Hybrid 회로로 디자인 하고자 한다[20].

Fig. 5. Proposed Hybrid Gate Driver for AR/VR Display based on [3].

그림 5. [3]을 기반으로 제안하는 AV/VR 디스플레이를 위한 하이브리드 게이트 드라이버

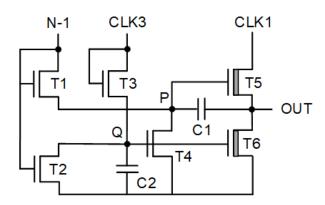

지금까지 진행한 Hybrid 회로 설계 방법을 앞서 언급한 AR/VR용 gate driver에 적용하기 위해 해당 driver의 회로 구성을 살펴보면 그림 5와 같다. 본 논문의 목표가 gate driver의 버퍼부를 CNT-FET으로 바꾸었을 때 얻을 수 있는 성능이기 때문에, 그림 5에서 버퍼부에 해당하는 T5와 T6를 CNTFET으로 변경한 경우와 그렇지 않은 경우를 비교하여 시뮬레이션을 진행하고자 한다. 그림 5에서 T5와 T6가 CNTFET으로 변경된 상황을 표현하기 위해, 해당 트랜지스터의 일부를 회색으로 표시하였으며, 그림 5의 T5와 T6가 MOSFET으로만 구성된 경우, 해당 gate driver를 MOSFET gate driver, 그리고 T5와 T6가 CNTFET로 구성된 경우, 해당 gate driver를 명명하고자 한다.

### Ⅲ. 시뮬레이션

앞서 언급한 두 종류의 gate driver를 구동하기

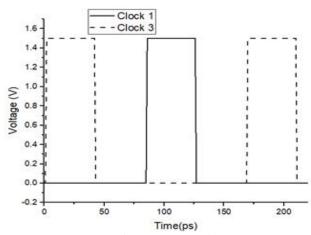

Fig. 6. Control Signal (CLK1 and CLK3) of Hybrid Gate Driver in Figure 5.

그림 6. 그림 5의 하이브리드 게이트 드라이버의 제어 신호 (CLK1과 CLK3)

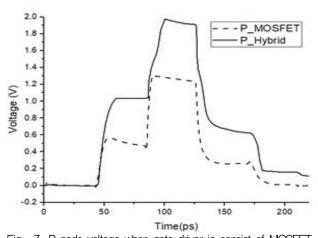

Fig. 7. P node voltage when gate driver is consist of MOSFET devices and Hybrid devices respectively in Figure 5. 그림 7. 그림 5의 게이트 드라이버가 각각 MOSFET 디바이스와 하이브리드 디바이스로 이루어졌을 때의 P노드 전압

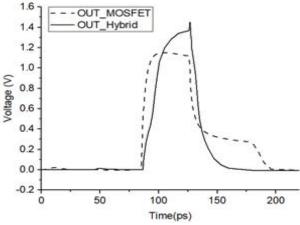

Fig. 8. OUT node voltage when gate driver is consist of MOSFET and Hybrid devices respectively at Figure 5. 그림 8. 그림 5의 게이트 드라이버가 각각 MOSFET 디바이스와 하이브리드 디바이스로 이루어졌을 때의 OUT 노드 전압

위해, 그림 6과 같은 구동 신호(Clock 1과 Clock 3)를 1.5V의 12.5GHz의 속도로 MOSFET gate driver와 Hybrid gate driver에 동일하게 인가하였으며, 그 결과 얻어진 두 회로의 P node 전압과 OUT node 전압을 그림 7과 그림 8과 같이 각각 도시하였다. P node 전압은 그림 5에서 T5와 T6의 gate 전압으 로서, T1과 OUT node로부터 공급되는 전류와 전 압으로 부스터 되어 T5와 T6의 전류를 더욱 증가 시키는 역할을 한다. 앞서 언급한 MOSFET 대비 CNTFET의 높은 성능으로 그림 7과 같이 Hybrid gate driver의 P node 전압이 MOSFET gate driver 의 P node 전압보다 약 0.8V 더 높게 boost 될 수 있 음을 알 수 있으며, 그 결과, 그림 8과 같이 Hybrid gate driver의 OUT node 전압이 MOSFET gate driver의 OUT node 전압 보다 약 0.3V 높은 전압을 생성할 수 있음을 알 수 있다. 일반적으로 32nm MOSFET만으로 회로를 구성할 때, 구동전압을 0.9V 를 사용하는 점을 상기하면, MOSFET만으로 gate driver를 구성하였을 때, 32nm MOSFET 만으로 구성된 화소 회로를 구동시킬 수 있는 전압을 출력 할 수 있지만, gate driver의 버퍼부를 CNTFET으 로 구성할 경우, 0.3V 더 높은 전압을 얻을 수 있 어, 디스플레이의 휘도를 높이거나 더 높은 속도로 구동시킬 수 있는 구동 마진을 획득할 수 있을 것 으로 기대된다.

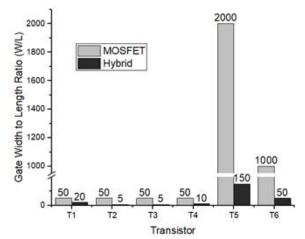

Fig. 9. Gate Width to Length ratio (W/L) for MOSFET gate driver and Hybrid gate driver respectively.

그림 9. MOSFET 게이트 드라이버와 Hybrid 게이트 드라 이버를 위한 게이트 넓이 대 길이 비율(W/L)

CNTFET은 앞서 언급한 바와 같이 gate 전체가 아닌 CNT를 통해 전류가 흐르기 때문에 기존 MOSFET

보다 작은 gate 면적으로 회로를 구성할 수 있고, 낮은 gate 전압에서 높은 전류를 흘릴 수 있으므로, CNTFET은 MOSFET보다 짧은 gate width로 제작할 수 있으며, 이는 동시에, CNTFET을 컨트롤 하는 MOSFET도 함께 gate width를 줄일 수 있음을 알 수 있다. 따라서, gate driver의 버퍼부를 CNTFET으로 구성한 경우, 그림 9과 같이, gate driver를 구성하는 모든 트랜지스터의 gate width를 줄일 수 있음을 알 수 있다. 앞서 언급한 두 종류의 gate driver의 gate width를 비교하면, 그림 9와 같이, T5의 gate width는 약 13.3배 그리고 T6의 gate width는 20배를 줄일 수 있음을 알 수 있어, gate driver에서 2개의 트랜지스터로 교체하는 것만으로도 커다란 면적 이득을 볼 수 있음을 알수 있다.

# Ⅳ. 결론

기존 반도체 소자에 CNT를 포함할 경우 그 성능 을 크게 향상시킬 수 있음에도 불구하고, 오랜 시 간 상업용 제품의 회로 부분에서 활용될 수 없었던 주요 이유 중 하나는 CNT를 일정하게 배치시킬 수 있는 공정 기술의 부족이었다. Gate driver의 버 퍼부는 일반적으로 디지털 회로 중 가장 간단한 구 조로 알려진 인버터로 구성되어 있고, 디스플레이 전체에 걸쳐 일정한 패턴으로 위치하기 때문에, 버 퍼부에 CNT를 적용하는 방법은 현재 CNT를 기존 회로에 활용할 수 있는 가장 현실적이고 효과적인 방법이라고 볼 수 있다. 총 6개의 트랜지스터 중, 2 개의 트랜지스터에 CNT를 포함시킴으로써, 동일 한 구동 신호에 대해 0.3V 더 높은 출력 전압을 얻 을 수 있고, 최대 20배로 gate width를 줄일 수 있 어, 더 좁은 디스플레이 영역에 성능 높은 gate driver를 구현할 수 있다. 더욱이, 디스플레이에 있 어서 이러한 기술은 플랙서블 디스플레이에 활용 할 수 있는 가능성이 있어. 가까운 미래에 사람 얼 굴에 보다 밀착시킬 수 있는 성능 높은 HMD 구현 에 기여할 수 있을 것으로 기대된다.

### References

[1] G. Nageswara Rao, K. Aruna Kumari, D. Ravi Shankar, and K. G. Kharade, "A comparative study of augmented reality-based head-worn display devices," *Mater. Today Proc.*, 2021

[2] H. G. Kenngott *et al.*, "IMHOTEP: cross-rofessional evaluation of a three dimensional virtual reality system for interactive surgical operation planning, tumor board discussion and immersive training for complex liver surgery in a head-ounted display," *Surg. Endosc.*, 2021.

DOI: 10.1007/s00464-020-08246-4

[3] Y. Chen *et al.*, "An 18.6-µm-Pitch Gate Driver Using a-IGZO TFTs for Ultrahigh-Definition AR/VR Displays," in *IEEE Transactions on Electron Devices*, vol.67, no.11, pp.4929-4933, 2020.

DOI: 10.1109/TED.2020.3023069

[4] J. Kim and T. Park, "The Onset Threshold of Cybersickness in Constant and Accelerating Optical Flow," *Applied Sciences*, vol.10, no.21. 2020.

DOI: 10.3390/app10217808.

[5] D. Ji *et al.*, "Recent progress in the development of backplane thin film transistors for information displays," *J. Inf. Disp.*, vol.22, no.1, pp.1–11, 2021. DOI: 10.1080/15980316.2020.1818641.

[6] J. Deng and H.-.P. Wong, "A Compact SPICE Model for Carbon-Nanotube Field-Effect Transistors Including Nonidealities and Its Application-Part I: Model of the Intrinsic Channel Region," in *IEEE Transactions on Electron Devices*, vol. 54, no.12, pp.3186–3194, 2007.

DOI: 10.1109/TED.2007.909030

[7] J. Deng and H.-.P. Wong, "A Compact SPICE Model for Carbon-Nanotube Field-Effect Transistors Including Nonidealities and Its Application-Part II: Full Device Model and Circuit Performance Benchmarking," in *IEEE Transactions on Electron Devices*, vol.54, no.12, pp.3195–3205, 2007.

DOI: 10.1109/TED.2007.909043

[8] G. Hills *et al.*, "Modern microprocessor built from complementary carbon nanotube transistors," *Nature*, vol.572, no.7771, pp.595–602, 2019.

DOI: 10.1038/s41586-019-1493-8.

[9] D. Ji *et al.*, "Recent progress in the development of backplane thin film transistors for information displays," *J. Inf. Disp.*, vol.22, no.1, pp.1–11, 2021.

DOI: 10.1080/15980316.2020.1818641

[10] C. Zhao *et al.*, "Strengthened Comple-mentary Metal-Oxide-Semiconductor Logic for Small-Band-Gap Semiconductor-Based High-Performance and Low-Power Appli-cation," *ACS Nano*, vol.14, no.11, pp.15267–15275, 2020.

[11] Y. Wang *et al.*, "Applying Viscous Shear Stress to Align Single-Walled Carbon Nanotubes," in *2020 4th IEEE Electron Devices Technology & Manufacturing Conference (EDTM)*, pp.1–4, 2020. DOI: 10.1109/EDTM47692.2020.9117997

[12] L. Liu *et al.*, "Aligned, high-density semi-conducting carbon nanotube arrays for high-performance electronics," *Science*, vol.368, no.6493, pp.850-856, 2020. DOI: 10.1126/science.aba5980

[13] Y. Lee *et al.*, "Hybrid integration of carbon nanotube and amorphous IGZO thin-film transistors," *AIP Adv.*, vol.10, no.2, pp.25131, 2020.

[14] PTM Models, http://ptm.asu.edu/ CNFET Models. http://nano.stanford.edu/ models.php

[15] A. S. Vidhyadharan and S. Vidhyadharan, "An ultra-low-power CNFET based dual VDD ternary dynamic Half Adder," *Microelectronics J.*, vol.107, pp.104961, 2021.

[16] I. Mamatov, Y. Özçelep, and F. Kaçar, "Voltage differencing buffered amplifier based low power, high frequency and universal filters using 32 nm CNTFET technology," *Microelectronics J.*, vol.107, pp.104948, 2021. DOI: 10.1016/j.mejo.2020.104948

[16] Z. Zareei, M. Bagherizadeh, M. Shafiabadi, and Y. Safaei Mehrabani, "Design of efficient approximate 1-bit Full Adder cells using CNFET technology applicable in motion detector systems," *Microelectronics J.*, vol.108, p.104962, 2021.

DOI: 10.1016/j.mejo.2020.104962

[17] J. M. Rabaey et al., "Digital Integrated Circuits: A Design Perspective., 2nd ed," *Englewood Cliffs*, NJ, USA: Prentice-Hall, 2007.

[18] G. Cho and F. Lombardi, "Circuit-Level Simulation of a CNTFET With Unevenly Positioned CNTs by Linear Programming," in *IEEE Transactions on Device and Materials Reliability*, vol.14, no.1, pp.234–244, 2014. DOI: 10.1109/TDMR.2013.2279154

# **BIOGRAPHY**

#### Geunho Cho (Member)

2004: BS degree in Electronic Engineering, Sogang University.

2006: MS degree in Electronic Engineering, Sogang University.

2012: PhD degree in Electrical Engineering, Northeatern University.

2012~2017: Senior Engineer, Samsung Display.

2017~present: Assistant Professor, Seokyeong University.