# Multi-Valued Logic Device Technology; Overview, Status, and Its Future for Peta-Scale Information Density

# Kyung Rok Kim<sup>1,2</sup>, Jae Won Jeong<sup>1</sup>, Young-Eun Choi<sup>1</sup>, Woo-Seok Kim<sup>1</sup> and Jiwon Chang<sup>1</sup>

<sup>1</sup> Department of Electrical Engineering, UNIST, Ulsan, Korea

Corresponding Author: Kyung Rok Kim (email: krkim@unist.ac.kr)

**Funding Information**: This work was supported by the Samsung Research Funding & Incubation Center of Samsung Electronics under project number SRFC-TA1703-07 and by the U-K Brand Research Fund (1.200033.01) of UNIST (Ulsan National Institute of Science & Technology). The authors are grateful to foundry support for 130-nm, 90-nm, and 28-nm CMOS technology processes

# **ABSTRACT**

Complementary metal-oxide-semiconductor (CMOS) technology is now facing a power scaling limit to increase integration density. Since 1970s, multi-valued logic (MVL) has been considered as promising alternative to resolve power scaling challenge for increasing information density up to peta-scale level by reducing the system complexity. Over the past several decades, however, a power-scalable and mass-producible MVL technology has been absent so that MVL circuit and system implementation have been delayed. Recently, compact MVL device researches incorporating multiple-switching characteristics in a single device such as 2D heterojunction-based negative-differential resistance (NDR)/transconductance (NDT) devices and quantum-dot/superlattices-based constant intermediate current have been actively performed. Meanwhile, wafer-scale, energy-efficient and variation-tolerant ternary-CMOS (*T*-CMOS) technology has been demonstrated through commercial foundry. In this review paper, an overview for MVL development history including recent studies will be presented. Then, the status and its future research direction of MVL technology will be discussed focusing on the *T*-CMOS technology for peta-scale information processing in semiconductor chip.

### **KEY WORDS**

Multi-valued logic (MVL), peta-scale, power-scaling limit, ternary-CMOS (*T*-CMOS) technology.

### 1. INTRODUCTION

Complementary metal-oxide-semiconductor (CMOS) technology has provided the unique economic efficiency to the semiconductor industry by its own geometrical scalability [1]. To achieve the peta-scale information densities (~10<sup>14</sup>/cm²), however, the binary Boltzmann switch of CMOS that controls current with potential barrier, face power density limits to giga-scale level (~10<sup>9</sup>/cm²) [2]. This needs for new technology that can overcome the power

density limits is "cycle" of paradigm change since we already experienced these changes from vacuum tubes to the first solid-state bipolar junction transistors (BJTs) in the 1950s, and BJTs to MOS field-effect transistors (MOSFETs) in the 1970s.

Multi-valued logic (MVL) has been considered as one of the promising alternatives since, in principle, the radix (R) increase of {0,1,2,...} from binary value {0,1} enables the significant increases in information density ( $N=R^d$ ) for the same digit (d) and/or reduction of the number of digit ( $d=log_RN$ ) for the same N.

<sup>&</sup>lt;sup>2</sup> Ternell Corporation, Ulsan, Korea

Especially, the most efficient way to overcome these power scaling challenges, is to move from a binary to a ternary system, where the system complexity is reduced to  $C = \log_3 N/\log_2 N \approx 63.1\%$  [3][4].

The human brain is an example of an energy-efficient system that uses ternary synaptic weights [5], consuming only ~20 W with peta-scale connection densities [6]. The evidences of these brain-inspired systems have been demonstrated by wafer-scale deeplearning (DL) engine with peta-scale memory and fabric bandwidth [7] and ternary-based neural network accelerator with many-core processing-in-memory (PIM) architecture [8] based on binary CMOS technology. Therefore, it can be expected that energy-efficient ternary logic scheme and its stable integration technology enable compact chip-scale DL engines with peta-scale processing capacity.

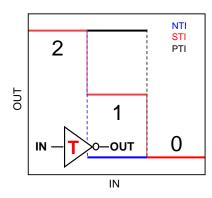

In practical aspects to integrate ternary system on semiconductor chip, however, there has been no power-scalable and mass-producible basic building block technology for the standard ternary inverter (STI) operation, while positive ternary inverter (PTI) or negative ternary inverter (NTI) can be easily implemented by shifting the transition region of binary CMOS inverter close to  $V_{DD}$  or 0 (GND), respectively. As shown in Figure 1, even though its circuit symbol looks simple and conceptually similar with binary CMOS case, the various ternary device and circuit approaches have been studied over the past few decades. In this review paper, an overview of MVL technologies is presented with a systematic benchmarking of various studies. Then, we present the status and contributions of ternary-CMOS (*T*-CMOS) technology. Finally, the future research direction of MVL technology will be discussed.

# 2. OVERVIEW OF MVL TECHNOLOGIES

In the early stage of MVL technology, ternary logic research to realize STI function has been performed

Figure 1. Standard ternary inverter (STI) IN-OUT voltage transfer characteristics with negative (NTI) and positive ternary inverter (PTI). Inset show the circuit symbol of STI building block.

based on CMOS technology owing to its convenience of implementation, but these circuit-level approaches needed additional voltage sources for three voltage states such as  $+V_{\rm DD}/-V_{\rm DD}$  and additional circuit elements for the intermediate states by voltage dividing of  $V_{\rm DD}$  such as two more resistors [9],  $V_{\rm DD}/2$  source with a resistor [10], and with an active load of the depletion/enhancement CMOS in output node [11].

Evidently, those additional circuit components lead to an increase in the number of devices (4~6) more than the ternary states (*R*= 3) even in a basic building block of STI configuration. For the area efficiency, carbon nanotube (CNT) FETs [12], [13] and single-electron transistors (SETs) [14] tried to replace CMOS components in those circuit-level approaches. Thus, it is the key challenge that the controllability of 1D CNT diameters and 0D quantum-dot size variations should be guaranteed in very-large-scale integration (VLSI). Recent advancement of a large-scale CNTFET integration [15] opens a new chance for the realization of CNT-based MVL technology. Furthermore, the stacked interfacial devices that can be processed by low thermal processes such as a graphene barrister

| Scheme                        | e Multi-threshold                 |                               |                           |                                 |                                |                                  |                                                               |                        |                                         | Single-<br>threshold       |

|-------------------------------|-----------------------------------|-------------------------------|---------------------------|---------------------------------|--------------------------------|----------------------------------|---------------------------------------------------------------|------------------------|-----------------------------------------|----------------------------|

| Device<br>Char.<br>Reference  | Step I-V (constant on-current)    |                               | NDR                       | NDT (multiple on-off switching) |                                |                                  |                                                               |                        |                                         | Step I-V w.<br>off-current |

|                               | [17]                              | [18]                          | [19]                      | [20]                            | [21]                           | [22]                             | [23]                                                          | [24]                   | [25]                                    | [26]                       |

| Physical principle            | Coulomb<br>blockade               | Quantized<br>mobility<br>edge | BTBT*<br>(broken-<br>gap) | multi-Dirac<br>voltage          | Non-<br>uniform<br>bandgap     | Reverse<br>saturated<br>junction | Anti-ambipolar transistor<br>(inverted ambipolar<br>transfer) |                        | G-<br>potential<br>control              | BTBT*<br>(Zener<br>diode)  |

| Device                        | QDG<br>FET                        | ZnO<br>composite<br>nanolayer | Hetero-<br>junction       | Graphene<br>(G)FET              | Hetero-<br>junction<br>(HJ)FET | UTB**<br>p-i-n<br>FET            | Organic HJFETs                                                |                        | HJFET                                   | MOSFET                     |

| Material                      | Silicon<br>QD in SiO <sub>2</sub> | ZnO<br>/Organic               | BP<br>/ReS <sub>2</sub>   | G/Pt (n)<br>G/Al (p)            | BP<br>/MoS <sub>2</sub>        | Silicon                          | α-6T<br>/PTCDI-C8                                             | DNTT<br>/PTCDI-<br>C13 | WS <sub>2</sub> /G<br>/WSe <sub>2</sub> | Silicon                    |

| Load                          | p-QDG<br>FET                      | Resistor                      | BP p-<br>channel<br>TFT   | p-GFET                          | BP FET                         | Resistor                         | PTCDI-C8<br>n-transistor                                      | PTCDI-<br>C13          | p-FET<br>(model)                        | CMOS                       |

| $V_{\mathrm{DD}}(\mathrm{V})$ | 0.6<br>(Sim.)                     | 5                             | 2                         | 2                               | 2                              | Pulse<br>0.5 -<br>0.625          | 10                                                            | 50                     | 2.1<br>(Sim.)                           | 0.5/0.7/1                  |

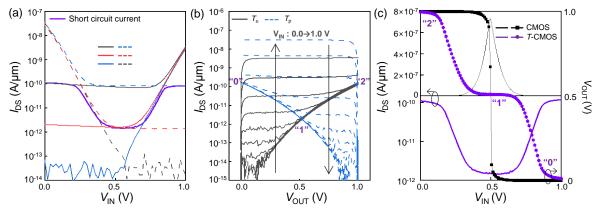

Figure 2. The off-state working T-CMOS characteristics: (a) transfer  $I_{DS}$ - $V_{IN}$  for  $|V_{DS}|$ = 0.1, 0.5, 1.0 V and (b) output  $I_{DS}$ - $V_{OUT}$  for varying  $V_{IN}$  from 0 V to 1 V (step: 0.1 V) with high "2", intermediate "1", and low-state "0" (c) The voltage transfer curves (VTC) and the respective short-circuit currents of T-CMOS inverter in comparison with CMOS at  $V_{DD}$ =1V. The short-circuit currents are on linear scale for CMOS inverter and on log scale for T-CMOS inverter in off-state regime.

(GB) with multi-thresholds also can provide a route to the area-efficient back-end-of-line (BEOL) MVL integration for ternary full-adder circuit [16].

Since the mid of 2010s, device-level approaches have been intensively taken to achieve the compact STI design with number of components less than three (the number of logical states; trit). These MVL device technologies are summarized in Table I with each material/device type and operation mechanism [17]-[26]. Basically, multiple low and high threshold voltage  $(V_T)$  are implemented in one single device for ternary operation. Then, this multiple switching device connected with one more component of complementary active or passive load in the series connection between  $V_{\rm DD}$  and ground (GND) leads to the number of components (2) less than 3 (ternary states  $\{0, 1, 2\}$ ), which can accelerate the reduction of system complexity and number of interconnects as the information processing density increases.

Characteristics of MVL devices can be classified into step I-V with constant current and multiple on-off switching with negative-differential resistance (NDR)/ transconductance (NDT). To realize stable intermediate states for circuit-design available noise margin, multiple-step I-V scheme with constant intermediate current is one of the promising device characteristics. For example, quantum-dot gate (QDG) FETs provided step-like transfer I-V characteristics using Coulombblockade effect in QDG insulator as a pioneering work of ternary device research by Intel [17]. Recently, a new channel material of ZnO composite nanolayer has been demonstrated for MVL transistors with well-defined intermediate state by mobility edge quantization effect [18]. The number of steps in transfer I-V curves can be controlled by stacking multiple ZnO layers.

The MVL devices based on the multiple on-off switching-oriented NDR/NDT characteristics have also been actively studied to resolve the inherent unstable intermediate state issue. Various NDR [19] and NDT devices pursuing high peak-to-valley current ratio (PVCR) demonstrated ternary logic functions based on complementary graphene FET [20], 2D van-der-Waals heterojunction FET [21], ultra-thin body (UTB) MOSFETs [22], and organic heterojunction-based antiambipolar transistors [23], [24]. Recently, a quaternary (*R*= 4) inverter function is demonstrated using double NDT characteristics by parallel configuration of WS<sub>2</sub>-graphene-WSe<sub>2</sub> heterojunctions with a p-channel transistor active load [25], which shows the possibility of compact thin-film stacking technology for the extension of multi-valued logic states as in [18].

# 3. STATUS AND FUTURE OF MVL DEVICE TECHNOLOGY

In contrast to all the previous MVL devices based on multi- $V_{\rm T}$  scheme [17]-[25], T-CMOS with single  $V_{\rm T}$  is an ultimately energy-efficient MVL device based on off-state working principle [26]. Specifically, ternary state operates in subthreshold region at  $V_{\rm DD} < V_{\rm T}$  and then, the complementary single-step I-V can be implemented with  $V_{\rm IN}$ -independent constant band-to-band tunneling current ( $I_{\rm Sub}$ ). Therefore, it can be demonstrated by the same layout design with conventional binary CMOS using the commercial foundry-processed 8-inch-wafers [26].

Figure 2(a) shows the measured transfer  $I_{DS}$ - $V_{IN}$  characteristics of T-CMOS where constant  $I_{BTBT}$  is clearly shown and exponentially varied by  $|V_{DS}|$  in off-current regime prior to the  $|V_{DS}|$ -independent  $I_{sub}$ . As in case of CMOS configuration,  $V_{DS}$  of T-nMOS  $(T_n)$  is  $V_{OUT}$ , and  $V_{DS}$  of T-pMOS  $(T_p)$  is  $V_{OUT}$ - $V_{DD}$ . Thus, when  $V_{OUT}$  increases,  $I_{BTBT}$  of  $T_n$   $(T_p)$  increases (decreases) in complementary way and then, by Kirchhoff's law,  $V_{OUT}$  is determined at the same  $I_{DS}$  of  $T_n$  and  $T_p$ . For example, in lower  $V_{IN}$  (~0 V),  $I_{BTBT}$  of  $T_n$  and  $I_{sub}$  of  $T_p$  (black lines

in Figure 2(a)) generate high "2" state around 100 pA level short-circuit current. For  $V_{\rm IN}=V_{\rm DD}/2$ ,  $I_{\rm BTBT}$  of  $T_{\rm n}$  and  $T_{\rm p}$  generate the intermediate "1" state (red lines) near 1 pA. In larger  $V_{\rm IN}$  (~1V),  $I_{\rm sub}$  of  $T_{\rm n}$  and  $I_{\rm BTBT}$  of  $T_{\rm p}$  generate low "0" state (blue lines).

Figure 2(b) shows the measured output  $I_{DS}$ - $V_{OUT}$ curves, which clearly indicate that the complementary current component varies from  $I_{BTBT}$  ( $I_{sub}$ ) to  $I_{sub}$  ( $I_{BTBT}$ ) of  $T_n$  ( $T_p$ ) when  $V_{IN}$  increases from 0 to 1 V. It should be noted that the tunneling current,  $I_{BTBT}$  with exponential dependence on  $V_{\text{OUT}}$  determines each tritstate {0, 1, 2}. Finally, as shown in Figure 2(c), the VTC and short circuit current of T-CMOS inverter are measured, which are distinguished from binary CMOS one having the same layout design. Conventional CMOS inverter achieves maximum current when both pull-up and pull-down are in on-state mode while the T-CMOS short-circuit current ranges in tunneling-based off-leakage regime. The exponential dependence of significantly reduces the  $I_{\mathrm{BTBT}}$ static consumption  $P_S$  (~  $I_{OFF}V_{DD}$ ) comparing with binary CMOS and previous MVL devices. Therefore, it allows the dynamic power ( $P_D$ )-dominant T-CMOS operation, which opens new circuit design field based on T-CMOS basic building block. Furthermore, single-V<sub>T</sub> scheme has advantages to scale down  $V_{\rm DD}$  than previous multi- $V_{\rm T}$  schemes and  $P_{\rm D}$  (~  $V_{\rm DD}^2$ ) could be further reduced by the half logic swing of  $V_{\rm DD}/2$  in ternary operation.

The constant  $I_{BTBT}$  based on quantum-mechanical tunneling, which is the key mechanism of T-CMOS, has been observed in highly doped tunnel junction between the body and drain by halo and retrograde-well doping. Retrograde (low-to-high from surface to body) doping profile can be formed between source and drain with relatively high channel ion-implantation energy and dose. Then, the subthreshold diffusion current  $(I_{sub})$ becomes the exponential current component. As the first study, we proposed compact design of the STI operation based on the binary CMOS inverter having these two off-currents [27], [28]. By comparing with both numerical TCAD device simulation and analytical model equations, the feasibility of the T-CMOS operation has been verified in terms of the noise margin, off-leakage variation, and  $V_{\rm DD}$  scaling.

In addition, we proposed T-CMOS device and circuit design platform based on compact model and verified the physical model parameters from the measured data [29]. The model parameters determine the VTC of STI with four noise margin voltages  $V_{\rm IL}$ ,  $V_{\rm IML}$ ,  $V_{\rm IMH}$  and  $V_{\rm IH}$ . The static noise margin (SNM) of STI is enhanced with T-CMOS design framework and power-delay product (PDP) analysis for high performance and low power ternary logic gates (STI, NMIN, NMAX) is provided.

Based on these prior works, we realized *T*-CMOS on large-scale 8-inch wafers using commercial CMOS foundries [26] which can significantly reduce power consumption as 1/1000 compared to binary CMOS.

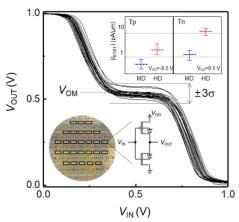

Figure 3. VTCs with die-to-die variations caused by  $\Delta I_{\rm BTBT}$  and  $\Delta V_{\rm T}$  from the 27 T-CMOS inverters at  $V_{\rm DD}$ = 1.0V. Inset shows photograph of 130-nm foundry processed 8-inch wafer with T-CMOS inverter schematic in 27 dies and the die-to-die variations of  $I_{\rm BTBT}$  for 27  $T_{\rm n}$  (MD) and  $T_{\rm p}$  (HD) samples. MD/HD, medium/high dose.

From the foundry wafer-scale results, we verified that  $P_{\rm S}$  and  $P_{\rm D}$  are scaled down by reducing  $I_{\rm OFF}$  to subpicoampere level and scaling  $V_{\rm DD}$  down to 0.5 V in the subthreshold regime. Furthermore, the intermediate state voltage of T-CMOS is more variation tolerant than binary CMOS subthreshold logic since it is reduced by log-scale of the constant tunneling current variations. We firstly demonstrated a *trit* state on an integrated circuit of the quantizer in ternary analogue-to-digital converter (T-ADC) and latch-cell operation in ternary static-random-access-memory (T-SRAM) on a silicon wafer to build ternary logic and memory systems. Thus, it could lead to ultra-low power ternary-binary hybrid circuit and system designs in semiconductors, which possibly inspire the software and algorithm engineers.

Now we discuss about the mass production results of T-CMOS technology by analyzing the variations of  $I_{\rm BTBT}$ ,  $V_{\rm T}$ , and VTC on wafer-scale measured data through the 130-nm and 90-nm CMOS processes. Figure 3 shows the measured VTCs of the T-CMOS inverters from 27 dies on an 8-inch wafer (inset). The third voltage state, output mid-state voltage  $(V_{OM})$ , is formed at a half of  $V_{\rm DD}$  by using voltage dividing between  $T_n$  and  $T_p$  with constant  $I_{BTBT}$ . Thus, the variation of the output mid-state voltage ( $\Delta V_{\rm OM}$ ) is determined by the variation of  $I_{BTBT}$  ( $\Delta I_{BTBT}$ ). At this point, we should recall the unique exponential output characteristics of T-CMOS (Figure 2(b)), which lead to the logarithmic dependence of  $V_{\rm OM}$  on  $I_{\rm BTBT}$  by the simplified expression of  $V_{\rm OM} \sim [1/\ln(1/I_{\rm BTBT})]^2$ . From this relationship, the robust ternary inverter operation was experimentally demonstrated by the small standard deviation of  $V_{\rm OM}$  ( $\sigma V_{\rm OM}$ = 16 mV) at average  $V_{\rm OM} = 0.52 \rm V.$

Despite its inherent robustness and tolerance to the variations, it is indispensable for suppressing  $\Delta I_{\rm BTBT}$  as much as possible (i.e. within one-decade) to realize T-CMOS technology-based integrated circuits. From

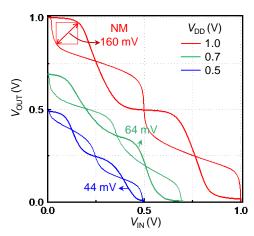

Figure 4. Butterfly curves from the symmetric  $V_{\rm IN}$ – $V_{\rm OUT}$  transfer characteristics at  $V_{\rm DD}$  =1.0, 0.7 and 0.5 V. The noise margin is the diagonal distance of the maximum possible square in symmetric VTC as noted in case of  $V_{\rm DD}$ = 1.0 V.

the measured dataset of the T-CMOS devices on an 8-inch wafers, the observed values of  $\Delta I_{\rm BTBT}$  were within one order of magnitude from MD to HD conditions (insets of Figure 3). This small  $\Delta I_{\rm BTBT}$  can be explained by the relation to the junction effective doping concentration ( $N_{\rm eff}$ ),  $\Delta I_{\rm BTBT} \propto \exp(N_{\rm eff}^{1/2}/N_{\rm eff})$ . Thus,  $\Delta I_{\rm BTBT}$  of T-CMOS will have much lower value with more increased  $N_{\rm eff}$  by decreasing  $N_{\rm eff}^{1/2}/N_{\rm eff}$  term [30]. Further reduction of the  $\Delta I_{\rm BTBT}$  can be obtained by exploiting an epitaxial doping which makes a more

Figure 5. 3D cross-section view of *T*-n/pFinFET at the middle of fin with BTBT layer (a) just below source and drain locally and (b) at sub-fin region across the substrate. These examples can also be applied to 3D stacked nanowire and nanosheet structures for future sub-3nm technology node.

steeper doping gradient at tunnel junction. We also experimentally demonstrated the small variation of  $V_{\rm T}$  ( $\Delta V_{\rm T}$ ) by lowering the surface doping concentration [26]. The retrograde profile by a well-controlled epitaxial doping technique could also be a promising option for further suppression of the  $\Delta V_{\rm T}$  and  $\Delta I_{\rm BTBT}$ .

Figure 4 presents butterfly curves from the symmetric in-out VTCs with SNM evaluation for each  $V_{\rm DD}$ = 1.0, 0.7 and 0.5 V. Compared with the butterfly curves in previous work [26], SNMs for  $V_{DD}$ =0.7 and 0.5V have been improved by reducing GND noise with high-resolution source measure units (SMU). For the largest noise margin in the T-CMOS inverter, the ratio of input gate voltage  $(V_{IN})$  region for each  $T_n$  and  $T_{\rm p}$  should have the optimal ratio of 3:1 for  $I_{\rm BTBT}$  and  $I_{\text{sub}}$ , respectively. From this optimal T-CMOS design, the symmetric in-out VTC characteristics are obtained with a considerable SNM which is 25-45% of the ideal one ( $\sqrt{2V_{DD}}/4$ ) at  $V_{DD} = 1.0$ , 0.7 and 0.5 V. Furthermore, the  $V_{\rm DD}$  scalability for energy-efficient T-CMOS technology is proved by demonstrating symmetrically measured VTCs even at a scaled  $V_{DD}$ = 0.5 V.

Further enhancement of SNM can be achieved by reducing the subthreshold swing (SSW). Improving the gate controllability with tri-gate or gate-all-around (GAA) structure and negative capacitance (NC) effect of ferroelectric materials as gate dielectrics are promising schemes to enhance SNMs of T-CMOS inverters operating at a further scaled  $V_{\rm DD}$ . Through a combination of the enhanced SSW and advanced doping technique, the ultimately scaled  $V_{\rm DD}$ = 0.3 V operation can be expected in T-CMOS inverters with a considerable SNM.

For sub-10 nm T-CMOS technology, we propose advanced T-CMOS technology based on 3D FinFET structure in Figure 5, which show the 3D cross-section view of T-n/pFinFET at the middle of fin. In 3D structures such as FinFETs, highly doped BTBT layer can be formed locally just below source and drain by ion-implantation or epitaxial growth right before the regrowth of source and drain (Figure 5(a)) as well as by ground-plane (GP) ion-implantation, dopantdiffusion from Borophosphosilicate glass (BPSG), or a well-controlled epitaxial doping technique for subfin region across the substrate (Figure 5(b)), which offer a considerable design room for the tunnel junction area. Thus, in more advanced technology node, T-CMOS technology based on 3D FinFET and/or stacked nanowire (SNW) and nanosheet (NS) structure can also be implemented in the wafer-level integration using the already commercialized fabrication process techniques. Additionally, more robust power-scalable T-CMOS architecture can be realized with the reduction of  $\Delta V_{\rm T}$  by lowering the influence of BTBT layer to surface channel region owing to the enhanced degree of freedom in the design of BTBT junction area.

The goal of the MVL technologies is to break through the power density limits while processing larger amounts of data than binary system. Thus, the MVL device research will be conducted in the direction of power-scalability and 3D integrated technologies along with the wafer-level integration. In T-CMOS technology, robust power-scalable ternary system can be realized through a combination of low thermal budget epitaxial doping technology with abrupt graded junction and steep-slope transistors such as tunnel FETs (TFETs) and NCFETs with 3D-stacked architecture, which lead to the reduced SSW, increased design margin of junction area for  $I_{\rm BTBT}$  and enhanced independent controllability of  $V_{\rm T}$  and  $I_{\rm BTBT}$ .

The multiple ZnO nano-layer or multi-threshold GB device based on 2D-layer stacking structure is an example of 3D-stacked device architecture that can be applied in low-thermal budget BEOL process. For NDT devices, lots of heterojunction devices composed of stacked 2D materials or organic semiconductor layers are developed and these kinds of thin-film process technologies will accelerate the power scalability of the MVL technologies for petascale information density era.

# 4. CONCLUSION

Multi-valued logic (MVL) exploiting more than three logical bases, is a one of promising technology to breakthrough the binary Boltzmann switching CMOS facing power density limits by a reduced system complexity. Among various MVL technologies, the ultimately energy-efficient "sleeping-mode" working T-CMOS technology, which shows a commercial wafer-level integration feasibility with robust variation tolerance and power scalability, has been intensively investigated. For processing peta-scale information density by overcoming power scaling limits, the future direction of MVL technologies should be capable of providing 3Dstacked integration for area-efficiency as well as energy-efficiency by having supply voltage scalability. Based on the power-scalable and mass-producible MVL device platform technology, the collaboration with circuit and system level exploiting massively parallel processing architecture would open new research field for peta-scale ternary-binary hybrid system integration on semiconductors.

# **REFERENCES**

- [1] D. J. Frank. (2002, Mar.). Power-constrained CMOS scaling limits. IBM J. Res. Develop. [Online]. vol. 46, pp. 235–244. Available: https://doi.org/10.1147/rd.462.0235

- [2] V. V. Zhirnov. (2003, Nov.). Limits to binary logic switch scaling - a gedanken model. Proc. IEEE. [Online]. vol. 91, pp. 1934-1939. Available: https://doi.org/10.1109/JPROC.2003.818324

- [3] Smith, K. C. (1981, Sept.). The prospects for multivalued logic: A technology and applications view. IEEE Transactions on Computers. [Online]. C-30(9), pp. 619-634. Available: https://doi.org/10.1109/TC.1981.1675860

- [4] Hurst, S. L. (1984, Dec.). Multiple-valued logic-Its status and its future. IEEE transactions on Computers. [Online]. 33(12), pp.

- 1160-1179. Available: https://doi.org/10.1109/TC.1984.1676392

- [5] Esser, S. K. (2016, Sep.). Convolutional networks for fast, energy-efficient neuromorphic computing. [Online]. Proc. Natl Acad. Sci. USA. 113(41), pp. 11441–11446 Available: https://doi.org/10.1073/pnas.1604850113

- [6] Lennie, P. (2003, Mar.). The cost of cortical computation. [Online]. Curr. Biol. 13(6), pp. 493-497. Available: https://doi.org/10.1016/S0960-9822(03)00135-0

- [7] S. Okumura et. (2019, June.). A Ternary Based Bit Scalable, 8.80 TOPS/W CNN accelerator with Many-core Processing-inmemory Architecture with 896K synapses/mm2. VLSI Circuits. [Online]. Available: https://doi.org/10.23919/VLSIC.2019.8778187

- [8] C.systems. (2019, May.). Wafer-scale Deep Learning. HotChips. [Online]. 31 Available:https://www.hotchips.org/hc31/HC31\_1.13\_Cerebr as.SeanLie.v02.pdf

- [9] H. T. (1977, Mar.). Design of ternary COS/MOS memory and sequential circuits. IEEE Trans. Comput. [Online]. C-26(3), pp.281–288. Available: https://doi.org/10.1109/TC.1977.1674821

- [10] Mouftah, H. T. (1982, Dec.). Injected voltage low-power CMOS for 3-valued logic. IEE Proceedings G-Electronic Circuits and Systems. [Online]. 129(6). pp. 270-272. IET. Available: https://doi.org/10.1049/ip-g-1.1982.0047

- [11] A. Heung. (1985, Apr.). Depletion/enhancement CMOS for a lower power family of three-valued logic circuits. IEEE JSSC. Online]. sc-20(2). Available: https://doi.org/10.1109/JSSC.1985.1052354

- [12] A. Raychowdhury. (2005, Mar.). Carbon-nanotube-based voltage-mode multiple-valued logic design. IEEE Tran. Nanotech. [Online]. 4(2). Available: https://doi.org/10.1109/TNANO.2004.842068

- [13] S. Lin. (2011, Mar.). CNTFET-based design of ternary logic gates and arithmetic circuits. IEEE Trans. Nanotechnol. [Online]. 10(2), pp. 217–225. Available: https://doi.org/10.1109/TNANO.2009.2036845

- [14] W. Gang. (2009, Feb.). Ternary logic circuit design based on single electron transistors. J. Semiconductor. [Online]. 30(2). Available: <a href="https://iopscience.iop.org/article/10.1088/1674-4926/30/2/025011">https://iopscience.iop.org/article/10.1088/1674-4926/30/2/025011</a>

- [15] Gage Hills. (2019, Aug.). Modern microprocessor built from complementary carbon nanotube transistors. Nature. [Online]. 572(7771) Pages 595-602. Available: <a href="https://doi.org/10.1038/s41586">https://doi.org/10.1038/s41586</a>-019-1493-8

- [16] Heo, Sunwoo. (2018, Dec.). Ternary full adder using multithreshold voltage graphene barristors. IEEE Electron Device Letters. [Online]. 39(12), pp. 1948-1951. Available: https://doi.org/10.1109/LED.2018.2874055

- [17] Karmakar. (2017, June.). Ternary logic gates using quantum dot gate FETs (QDGFETs). Silicon. [Online]. 6(3), pp. 169-178. Available: https://doi.org/10.1007/s12633-013-9175-x

- [18] Lee, Lynn. (2019, April.). ZnO composite nanolayer with mobility edge quantization for multi-value logic transistors. Nature communications. [Online]. 10(1), pp. 1-9. Available: https://doi.org/10.1038/s41467-019-09998-x

- [19] J. Shim et al. (2019, Nov.). Phosphorene/rhenium disulfide heterojunction-based negative differential resistance device for multi-valued logic. Nature Communications. [Online]. 7. Available:

- https://www.nature.com/articles/ncomms13413

- [20] Kim. Y. J. (2016, Dec.). Demonstration of complementary ternary graphene field-effect transistors. Scientific reports. [Online]. 6, 39353. Available: https://www.nature.com/articles/srep39353

- [21] Huang, Mingqiang. (2017, Oct.). Multifunctional high-performance van der Waals heterostructures. Nature nanotechnology. [Online]. 12(12), 1148. Available: https://doi.org/10.1038/nnano.2017.208

- [22] Lee, Sejoon. (2017, Sep.). Extraordinary Transport Characteristics and Multivalue Logic Functions in a Silicon-Based Negative-Differential Transconductance

- Device. Scientific reports. [Online]. 7(1), pp. 1-9. Available: https://doi.org/10.1038/s41598-017-11393-9

- [23] Kobashi, Kazuyoshi. (2018, July.). Multi-Valued Logic Circuits Based on Organic Anti-ambipolar Transistors. Nano letters. [Online]. 18(7), pp. 4355-4359. Available: https://doi.org/10.1021/acs.nanolett.8b01357

- [24] Yoo, Hocheon. (2019, May.). Negative Transconductance Heterojunction Organic Transistors and their Application to Full-Swing Ternary Circuits. Advanced Materials. [Online]. 31(29), 1808265. Available: https://doi.org/10.1002/adma.201808265

- [25] Lim, Ji-Hye. (2019, Sep.). Double Negative Differential Transconductance Characteristic: From Device to Circuit Application toward Quaternary Inverter. Advanced Functional Materials. [Online]. 29(48), 1905540. Available: https://doi.org/10.1002/adfm.201905540

- [26] Jeong, Jae Won. (2019, July.). Tunnelling-based ternary metal-oxide-semiconductor technology. Nature Electronics. [Online]. 2(7), pp. 307-312. Available: https://doi.org/10.1038/s41928-019-0272-8

- [27] Shin, Sunhae. (2015, July.). Compact design of low power standard ternary inverter based on OFF-state current mechanism using nano-CMOS technology. *IEEE Transactions* on Electron Devices. [Online]. 62(8), pp. 2396-2403. Available: https://doi.org/10.1109/TED.2015.2445823

- [28] Ternary digit logic circuit, by Kim, Kyung Rok. (2018, Nov 20). U.S. Patent No. 10,133,550. 20 [Online]. Available: https://patents.google.com/patent/US10133550B2/en

- [29] Shin, Sunhae. (2017, May.). CMOS-compatible ternary device platform for physical synthesis of multi-valued logic circuits. *IEEE 47th International Symposium on Multiple-Valued Logic* (*ISMVL*). [Online]. pp. 284-289. Available: https://doi.org/10.1109/ISMVL.2017.48

- [30] Park, B.-G, "Quantum Well Devices" in Nanoelectronic Devices, 1st ed. Singapore, 2012, pp. 222–223.

### **AUTHOR BIOGRAPHIES**

**Kyung Rok Kim** received the B.S., M.S., and Ph.D. degrees in electrical engineering from Seoul National University, Seoul, South Korea, in 1999, 2001, and 2004, respectively. He has been a Professor with the Department of Electrical and Computer Engineering, Ulsan

National Institute of Science and Technology, Ulsan, South Korea. From 2004 to 2006, he was with the Stanford Technology Computer-Aided Design (TCAD) Group, Center for Integrated Systems, Stanford University, Stanford, CA, USA, where he developed a TCAD-based quantum tunneling model as a Postdoctoral Research Associate. From 2006 to 2010, he was with Samsung Electronics Corporation, Ltd., Suwon, South Korea, where he developed unified process-device-circuit analysis tools for memory and logic devices as a Senior Engineer. His current research interests include nanoelectronic emerging devices and circuits, future CMOS and memory devices, low-power ICs, Si quantum-effect neuromorphic devices and circuits, terahertz plasmawave devices, and its physical modeling based on the TCAD platform.

Jae Won Jeong received the B.S. degree in electrical and computer engineering from the Ulsan National Institute of Science and Technology, Ulsan, Korea, in 2015, where he is currently pursuing the Ph.D. degree. His current research interests include

nanoelectronic emerging devices and circuits, low-power nanoscale ICs, neuromorphic device, ternary logic devices, future CMOS and memory devices with its physical modeling based on the TCAD platform and digital circuit design.

Young-Eun Choi received the B.S. degree in electrical and computer engineering from the Ulsan National Institute of Science and Technology, Ulsan, Korea, in 2018, where she is currently pursuing the Ph.D degree. Her current research interests include

nanoelectronic emerging devices and circuits, lowpower nanoscale ICs, neuromorphic device, ternary logic devices, future CMOS and memory devices with its device modeling and digital circuit design.

Woo-Seok Kim received the B.S. degree in electrical and computer engineering from the Ulsan National Institute of Science and Technology, Ulsan, Korea, in 2019, where he is currently pursuing the Ph.D degree. His current research interests include

nanoelectronic emerging devices and circuits, low-power nanoscale ICs, neuromorphic device, ternary logic devices, future CMOS, and memory devices with its physical and device modeling based on the TCAD platform.

**Jiwon Chang** received the B.S. degree in electrical engineering from Seoul National University, Seoul, Korea, in 2007, and the M.S.E. and Ph.D. degrees in electrical and computer engineering in 2009 and

2013, respectively, from the University of Texas at Austin, Austin, TX, USA. From 2013 to 2015, he was a postdoctoral researcher in SEMATECH, Albany, NY, USA., where he developed quantum transport simulator for 2-dimensional devices. From 2015 and 2017, he was a senior engineer in Intel, Hillsboro, OR, USA, where he was involved in the technology development for 7, 5 nm and beyond. From 2017, he has been a Professor with the Department of Electrical and Computer Engineering, Ulsan National Institute of Science and Technology, Ulsan, South Korea. His current research interests are in the physics, technology, and modeling of nanoscale device.