ISSN: 1226-7244 (Print) ISSN: 2288-243X (Online) 논문번호 20-04-16

108

# 동일대역 간섭저감기의 설계 및 구현

# Design and Implementation of In-band Interference Reduction Module

강 상 기\*<sup>★</sup>, 홍 헌 진\*\*, 정 영 준\*\*

Sanggee Kang\*\*, Heonjin Hong\*\*, Youngjun Chong\*\*

#### **Abstract**

The existing in-band interference reduction method recommends the physical separation distance between wireless devices and interference signals, and the interference can be suppressed through the separation distance. If the in-band interference signals can be reduced in a wireless device, a margin can be given to the physical separation distance. Since there is an effect of extending the receiver dynamic range of receivers, it is highly useful for interference reduction and improvement method.

In this paper, the structure of an in-band analog IRM(Interference Reduction Module) is proposed and the design and implementation of the proposed analog IRM are described. To design an analog IRM, the interference reduction performance according to the delay mismatch, phase error and the number of delay lines that affect the performance of the analog IRM was simulated. The proposed analog IRM composed of 16 delay lines was implemented and the implemented IRM has the interference reduction performance of about 10dB for a 5G(NR-FR1-TM-1.1) signal having a 40MHz bandwidth at a center frequency of 3.32GHz. The analog IRM proposed in this paper can be used as an in-band interference canceller.

## 요 약

기존의 동일대역 간섭저감 방법은 무선기기 사이에 물리적인 이격거리를 지정하는 것으로 이격거리를 통해서 간섭을 억제한다. 만약 무선기기에서 동일대역 간섭을 저감할 수 있다면 물리적인 이격거리에 마진을 줄 수 있고, 수신기의 동작영역을 확장시키는 효과가 있으므로 간섭 대응 및 개선에 활용도가 크다.

본 논문에서는 동일대역 아날로그 간섭저감기의 구조를 제안하였고, 제안한 아날로그 간섭저감기의 설계와 구현에 대해서 기술하였다. 아날로그 간섭저감기를 설계하기 위해서 아날로그 간섭저감기의 성능에 영향을 미치는 지연(delay) 불일치, 위상오차 그리고 지연선로의 수에 따른 간섭저감 성능을 시뮬레이션 하였다. 16개의 지연선로로 구성된 아날로그 간섭저감기를 제작하였으며, 구현한 간섭저감기는 3.320k의 중심주파수에서 40kk 대역폭을 갖는 5G(NR-FR1-TM-1.1) 신호에 대해서약 10dB의 간섭저감 성능을 갖는다. 본 논문에서 제안한 아날로그 간섭저감기는 동일대역 간섭저감기로 활용가능하다.

Key words: in-band interference, interference cancellation, cancellation performance, delay mismatch, phase error

E-mail: skkang@kunsan.ac.kr, Tel: +82-63-469-4858

This work was supported by the Institute for Information & Communications Technology Planning & Evaluation(IITP) grant funded by the korea government(MSIT)(No. 2020-0-00879, Development of clean zone protection technology to secure  $5G^+$  frequency).

Manuscript received Nov. 19, 2020; revised Dec. 23, 2020; accepted Dec. 28, 2020.

This is an Open-Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License (http://creativecommons.org/licenses/by-nc/3.0) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

<sup>\*</sup> School of Computer Information and Communication Engineering, Kunsan National University

<sup>★</sup> Corresponding author

<sup>\*\*</sup> Electronics and Telecommunications Research Institute

Acknowledgment

## I . 서론

기존의 동일대역 간섭저감 방법은 무선기기 사이에 물리적인 이격거리를 지정하는 것으로 이격거리를 통해서 간섭을 억제한다. 만약 무선기기에서 동일대역 간섭을 저감할 수 있다면 물리적인 이격거리에 마진을 줄 수 있고, 수신기의 동작영역을 확장시키는 효과가 있으므로 간섭 대응 및 개선에 적극적으로 활용될 수 있다.

최근에 많은 연구가 진행되고 있는 전이중(fullduplex) 통신의 자기간섭신호 제거기술은 무선기 기의 송신신호의 일부가 누설되어 자체 무선기기 내부로 유입되거나 외부 환경의 영향에 의해서 반 사되어 자기 자신의 수신경로 유입되는 신호에 의 한 간섭을 저감하는 기술이다. 전이중 통신용 간섭 신호 저감기술은 간섭신호가 저감되는 위치에 따라 서 아날로그 간섭저감(analog interference reduction) 기술과 디지털 간섭저감(digital interference reduction) 기술로 구분되며, 수신경로로 유입되는 간섭신호를 인위적으로 생성한 모사간섭신호(replication interference signal)를 이용해서 수신경로에서 간섭신호를 저감 하는 기술이다[1, 2, 3]. 동일대역 간섭신호를 저감 하기 위한 간섭저감기로는 구현 복잡도, 간섭저감 성능 그리고 동작속도 등을 고려하면 아날로그 간 섭저감기술을 적용한 간섭저감기가 적합하다. 본 논문에서는 5G 신호가 위성신호에 미치는 간섭을 줄이기 위한 아날로그 간섭저감기에 대해서 기술 하며, 5G 신호를 간섭신호로 취급하므로 동작 대역 폭이 넓은 전이중 통신용 자기간섭 저감기술을 응 용한다. 본 논문에서는 지연 불일치, 위상오차 그리 고 다중지연선로의 수가 아날로그 간섭저감기의 성능에 미치는 영향을 분석하고, 그 결과를 이용한 아날로그 간섭저감기의 설계 및 구현에 대해서 기 술한다.

## Ⅱ. 아날로그 간섭저감기의 설계

## 1. 아날로그 간섭저감기 구조

본 논문에서 제안하는 아날로그 간섭저감기의 기본 원리는 위성안테나에는 간섭신호인 5G 신호와 원신호(Wanted Signal)인 위성신호가 동시에 유입되지만 이동통신 안테나에는 5G 신호만 유입되는 점을 이용하는 것이다. 5G 안테나로 유입되는 신호를

기준신호로 이용하면 위성안테나로 유입되는 5G 신호를 억압할 수 있다.

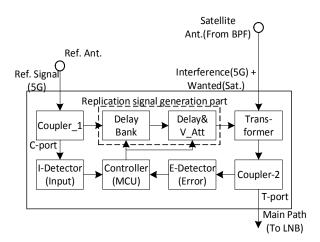

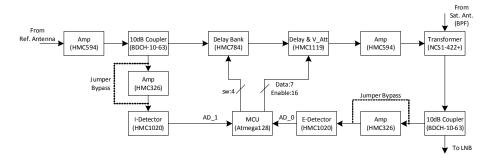

본 논문에서 제안하는 아날로그 간섭저감모듈 (IRM: Interference Reduction Module)의 기본 구 성은 그림 1과 같다. 그림 1에서 위성안테나로 수 신되는 간섭신호(5G 신호)를 저감하기 위해서 아 날로그 IRM은 모바일 안테나로부터 기준신호(5G 신호)를 수신하고, 수신된 기준신호는 전력결합기 -1을 통해서 모사신호성형부로 인가된다. 모사신호 성형부는 지연(delay) 뱅크와 다중지연경로(Delay & V\_Att)로 구성되며, 모사신호성형부의 출력은 트랜스포머(transformer)에 인가된다. 트랜스포머 에서는 모사신호성형부의 출력과 간섭신호와 원신 호가 동시에 수신되는 경로가 전력결합 된다. 트랜 스포머의 출력은 전력결합기-2로 인가되며, 전력결 합기-2의 일부신호가 커플링 단자를 통해서 E-전 력검출기로 인가된다. 제어기는 E-전력검출기의 출력 신호를 이용해서 지연 뱅크의 RF 스위치와 모사신호성형부의 가변감쇠기(V\_Att)를 제어한다. 전력결합기-1의 커플링 단자를 통해서 수신되는 기준신호의 일부신호는 I-전력검출기에 인가되고, I-전력검출기의 출력신호도 모사신호성형부의 가 변감쇠기와 RF 스위치 제어에 이용된다. 그림 1의 구성 요소들의 기능은 다음과 같다.

- 전력결합기-1(Coupler\_1): 기준신호의 일부를 표본하는 기능 제공

- 모사신호성형부(지연 뱅크와 다중지연선로(Delay & V\_Att)): 지연 뱅크는 기준신호와 간섭신호 사이의 시간지연을 보상하며, 다중지연경로 (Delay & V\_Att)는 기준신호를 간섭신호와 동일한 신호로 생성하는 기능을 제공

- 트랜스포머(Transformer): 빼기회로의 기능을 제공

- 전력결합기-2(Coupler\_2): 수신경로의 신호를 표본하는 기능 제공

- I-전력검출기(Input-Detector): 기준신호의 수 신 정도를 확인하기 위한 수단 제공

- E-전력검출기(Error-Detector): 간섭신호 제거 정도를 확인하기 위한 수단 제공

- 제어기(Controller): 적응형 알고리즘을 이용해 서 모사신호성형부의 가변감쇠기와 지연 뱅크 의 RF 스위치를 제어하는 기능 제공

Fig. 1. The structure of the proposed analog IRM. 그림 1. 제안하는 아날로그 간섭저감모듈(IRM)의 구조

#### 2. 아날로그 간섭저감기의 성능 시뮬레이션

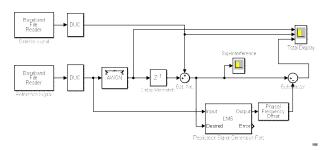

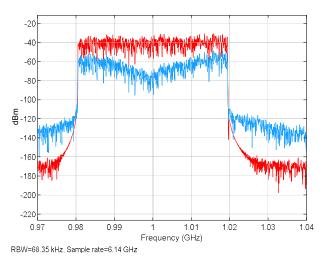

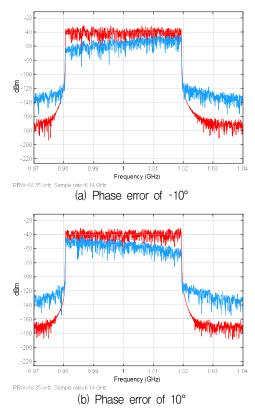

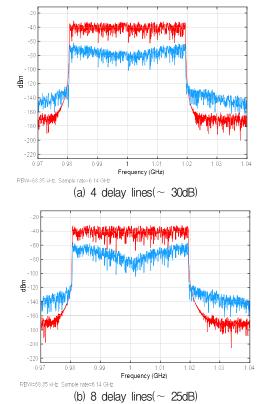

그림 1의 아날로그 IRM의 성능은 기준신호 경로 와 간섭신호 유입 경로 사이의 시간지연, 빼기회로 의 위상오차 그리고 다중지연경로의 수에 의해서 영향을 받는다. 그림 1의 아날로그 IRM을 실제 구 현하기 위해서 시간지연, 위상오차 그리고 지연경 로의 수가 성능에 미치는 영향을 확인할 필요가 있 으며, MATLAB을 이용해서 이들 파라미터가 간섭 저감에 미치는 영향을 시뮬레이션 하였다. 그림 2 는 성능 시뮬레이션 구성도이며, 시뮬레이션의 편 의를 위해서 RF 신호는 10kk 대역으로 설정하였고. 40Mb 대역폭을 갖는 5G(NR-FR1-TM1.1) 신호를 생성해서 시뮬레이션 하였다. 그림 3~그림 5는 간 섭저감기의 성능을 시뮬레이션한 결과이며, 제어알 고리즘은 LMS(Least Mean Squares) 알고리즘을 사용하였다[4]. 그림 3은 16개의 지연경로로 구성된 간섭저감기의 성능을 시뮬레이션한 결과이며, 약 20dB의 간섭저감 성능을 갖는다. 그림 4는 위상오 차가 -10°인 경우와 10°인 경우에 대한 시뮬레이션 한 결과로 음의 위상오차를 갖는 경우 지연선로가 짧아지는 효과 때문에 아날로그 간섭저감기의 동 작주파수의 중심은 왼쪽으로 이동되며, 양의 위상 오차를 갖는 경우에는 지연선로가 길어지는 효과 로 인해서 중심주파수는 오른쪽으로 이동됨을 보 여준다. 그림 5는 지연선로의 수에 따른 간섭저감 기의 성능을 시뮬레이션한 결과이다. 그림 5의 시 뮬레이션에서는 step-size 파라미터 μ를 동일한 값 으로 설정했기 때문에 지연선로의 수가 많게 되면 지연선로의 가중값을 미세하게 제어하지 못하는 결과를 초래하게 되므로 지연선로의 수가 작은 경우 간섭저감기의 성능이 좋은 것으로 시뮬레이션 되었다. 지연선로의 수가 많은 경우에는  $\mu$ 를 더 작은 값으로 설정하면 간섭저감기의 성능이 향상된다. 하지만 이 경우 수렴속도가 느려지는 단점이 있다. 그리고 지연선로의 수가 작으면 지연 불일치에 의한 영향을 줄일 수 있는 허용범위가 줄어들기때문에 지연선로의 수는 이들 사이에 절충이 필요하다.

광대역의 간섭저감 성능을 갖기 위해서는 지연 불일치가 작아야 하며, 표 1에는 지연 불일치에 의해서 발생되는 위상오차를 간략하게 나타내었다. 20dB 정도의 간섭저감 성능을 갖기 위해서 크기는 약 0.8dB 이내 위상은 약 8°이내에서 유지되어야한다. 때문에 100㎞ 대역폭을 갖는 간섭신호를 20dB 저감하기 위해서 크기 불일치를 0.8dB 이내로 유지하는 경우, 지연 불일치는 0.5ns 이내로 유지해야한다[5].

Fig. 2. Simulation configuration of the analog IRM. 그림 2. 간섭저감기 모의 시뮬레이션 구성도

Fig. 3. Interference reduction performance(16 delay lines). 그림 3. 간섭저감성능(16개의 지연경로)

Fig. 4. Interference reduction performance according to phase error.

#### 그림 4. 위상오차에 따른 간섭저감성능

Fig. 5. Interference reduction performance according to the number of the delay lines.

그림 5. 지연경로의 수에 따른 간섭저감성능

Table 1. Phase error due to delay mismatch.

표 1. 지연 불일치에 의한 위상오차

| Delay mismatch | Phase error(40Mz BW) | Phase error(0.10Hz BW) |

|----------------|----------------------|------------------------|

| 1ns            | ±7.2°                | ±18.0°                 |

| 2ns            | ±14.4°               | ±36.0°                 |

| 5ns            | ±36.0°               | ±90.0°                 |

## Ⅲ. 아날로그 간섭저감기의 구현

설계한 아날로그 IRM의 상세 구성도는 그림 6과 같다. 그림 6에서 Ref. 안테나로 수신되는 기준신호 는 증폭기(HMC594)를 통해서 증폭되고 10dB 커플 러(BDCH-10-63)를 통과한 다음, 지연 뱅크(BPF (Band Pass Filter))와 RF 스위치(HMC784)로 구성 됨)와 모사신호성형부(지연선로, V\_Att(HMC1119) 와 전력분배기로 구성됨)를 거치면서 위성안테나 로 수신되는 간섭신호와 같은 모양의 신호가 생성 된다. 지연 뱅크를 마이크로스트립 선로로 구현하 는 경우 크기가 증가하므로 대역통과필터(BPF)를 사용해서 시간지연을 구현하는 것으로 설계하였고, 모사신호성형부의 지연은 마이크로스트립 선로로 설계하였다. 모사신호성형부의 출력은 증폭기(HMC 594)를 거친 후, 빼기회로의 기능을 제공하는 트랜 스포머(NCS1-422+)에 인가된다. 트랜스포머의 출 력은 10dB 커플러에 인가되며, 10dB 커플러의 커 플링 단자를 이용해서 수신신호의 일부를 샘플링 한다. 샘플링된 신호는 증폭기(HMC326)를 통해서 증폭된 다음, E-전력검출기(HMC1020)에 인가된 다. E-전력검출기의 출력은 MCU의 ADC(AD\_0) 를 이용해서 모니터링하며, 이 ADC 값을 이용해서 모사신호성형부의 가변감쇠기의 감쇠량과 지연 뱅크 의 RF 스위치를 제어하며, 제어 알고리즘은 LMS 를 사용하였다. Ref. 안테나와 증폭기 다음에 위치 하는 10dB 커플러의 커플링 단자를 통해서 인가받 은 기준신호는 증폭기(HMC326)로 증폭한 다음에 I-전력검출기로 인가된다. I-전력검출기의 검출전 압은 MCU의 ADC(AD 1)를 이용해서 모니터링하 며, 모사신호성형부의 가변감쇠기의 감쇠량 제어와 지연 뱅크의 RF 스위치 제어에 사용한다. 기준신 호의 전력 레벨이 낮은 경우에 신호 증폭을 목적으 로 적용된 증폭기(HMC326)는 bypass 할 수 있도 록 구성하였다.

Fig. 6. Block diagram of the implemented analog IRM. 그림 6. 구현한 아날로그 IRM의 상세 구성도

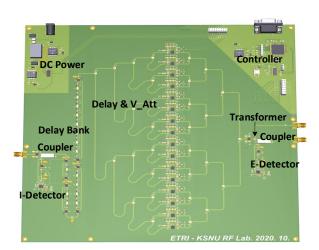

16개의 다중지연선로(Delay & V\_Att)의 구성은 그림 7의 설계된 아날로그 간섭저감기의 형상에서 확인할 수 있다. 16개의 지연선로의 길이는 임의의 특정한 길이를 갖는 t(임의의 길이로 아날로그 IRM 내에서는 모두 동일함)와 n△t를 갖도록 구성하였다(n=1, 2, 4, 8). △t를 갖는 지연선로의 길이는 유전율 4.6, H=0.6mm 그리고 W=1.1mm인 경우 20mm로 설계하였다. 그림 7에서 확인할 수 있듯이 2개의지연선로를 기본 블록으로 16개의 다중지연선로 블록을 구성하였고, 16개의 다중지연선로 블록은 8개의 2-경로블록으로 구성된다. 구현한 아날로그IRM에서는 4-경로블록의 2△t는 40mm, 8-경로블록의 4△t는 80mm 그리고 16-경로블록의 8△t는 160 mm로 구현하였으며, 이들 경로의 길이를 고려해서 임의의 길이 t를 선택하였다.

Fig. 7. The photograph of the implemented analog IRM. 그림 7. 구현된 아날로그 간섭저감기의 형상

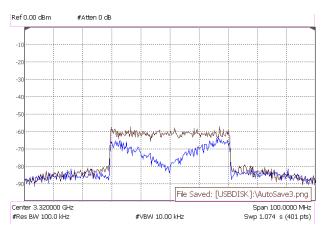

중심주파수 3.320k에서 40kk 대역폭을 갖는 5G (NR-FR1-TM-1.1) 신호를 생성해서 제작한 아날로그 간섭저감기의 간섭저감 성능을 확인하였고,

그림 8과 같이 약 10dB의 간섭저감 성능을 갖는 것으로 측정되었다. 그림 8은 제안한 아날로그 간섭저감기가 적절하게 동작함을 보여준다. 제작한 간섭저감기의 간섭저감 성능이 시뮬레이션 결과에미치지 못하는 이유는 FR4 기판으로 아날로그IRM을 제작하였는데 3대 대역에서 지연선로의 손실이 커서 원하는 모사간섭신호를 적절하게 생성하지 못했기 때문이다. 향후 기판의 재질을 변경하면 원하는 성능을 얻을 수 있다고 판단된다.

Fig. 8. Interference reduction performance of the implemented analog IRM.

그림 8. 구현한 아날로그 간섭저감기의 성능

## Ⅳ. 결론

본 논문에서는 동일대역 아날로그 간섭저감기의설계와 구현에 대해서 기술하였다. 아날로그 간섭저감기를 설계하기 위해서 아날로그 간섭저감기의성능에 영향을 미치는 지연 불일치, 위상오차 그리고 지연선로의 수에 따른 간섭저감 성능을 시뮬레이션 하였다. 16개의 지연선로로 구성된 아날로그 IRM을 구현하였으며, 제작한 아날로그 IRM은 3.32

대의 중심주파수에서 40mb 대역폭을 갖는 5G(NR-FR1-TM-1.1) 신호에 대해서 약 10dB의 간섭저감성능을 갖는다. 간섭저감기의 제작에는 FR4를 사용하였는데 3GHz 대역에서 지연선로의 삽입손실이 커서 성능에 열화가 있는 것으로 판단되며, 향후 손실이 작은 RF 기판을 사용해서 간섭저감기를 제작하면 원하는 성능을 가질 것으로 판단된다. 본논문의 결과는 동일대역 간섭저감기로 활용가능하다.

## References

[1] Tho Le-Ngoc and Ahmed Masmoudi, Full-Duplex Wireless Communications Systems: Self-Interference Cancellation, Springer, 2017.

[2] Dinesh Bharadia, Emily Mcmilin and Sachin Katti, "Full Duplex Radios," *ACM SIGCOMM*, vol.43, no.4, pp.375–386, 2013.

DOI: 10.1145/2534169.2486033

[3] M. Jain, J. I. Choi, T. Kim, D. Bharadia, S. Seth, K. Srinivasan, P. Levis, S. Katti, and P. Sinha, "Practical, Real-time, Full Duplex Wireless," *ACM MobiCom 2011*, pp.301–312, 2011.

DOI: 10.1145/2030613.2030647

[4] Monson H. Hayes, Statistical Digital Signal Processing and Modeling, Wiley & Sons, 1996.

[5] Sanggee Kang and Ilkyoo Lee, "Cancellation performance of a linearisation loop of a feedforward amplifier," Electronics Letters, Vol.33, pp.444–446, 1997. DOI: 10.1049/el:19970317

#### **BIOGRAPHY**

### Sanggee Kang (Member)

2004: PhD degree in Radio Engineering, Chungnam National University.

1989: Research Engineer, Samsung

Electronics

$1994 \sim 2005$ : Senior Research

Engineer, ETRI

2005~present: Professor, Telecommunication Engineering, Kunsan National University.

#### **Heonjin Hong** (Member)

1990: MS degree in Electronic Engineering, Chungnam National University.

1990~present: Principal Research

Engineer, ETRI

#### Youngjun Chong (Member)

2005: PhD degree in Electronic Engineering, Chungnam National University.

2006∼2008 : RF Module Design Team, Team Leader, ETRI

2012~2014, 2016 : Spectrum Engineering Lab., R&D Manager, ETRI

1994~present: Principal Research Engineer, Project Leader, ETRI