JPE 19-6-15

https://doi.org/10.6113/JPE.2019.19.6.1496 ISSN(Print): 1598-2092 / ISSN(Online): 2093-4718

# Scheme for Reducing Harmonics in Output Voltage of Modular Multilevel Converters with Offset Voltage Injection

Devnath Anupom\*, Dong-Cheol Shin\*, and Dong-Myung Lee<sup>†</sup>

†,\*School of Electronic and Electrical Engineering, Hongik University, Seoul, Korea

#### **Abstract**

This paper proposes a new THD reduction algorithm for modular multilevel converters (MMCs) with offset voltage injection operated in nearest level modulation (NLM). High voltage direct current (HVDC) is actively introduced to the grid connection of offshore wind powers, and this paper deals with a voltage generation technique with an MMC for wind power generation. In the proposed method, third harmonic voltage is added for reducing the THD. The third harmonic voltage is adjusted so that each of the pole voltage magnitudes maintains a constant value with a maximum number of (N+1) levels, where N is the number of sub-modules per arm. By using the proposed method, the THD of the output voltage is mitigated without increasing the switching frequency. In addition, the proposed method has advantageous characteristics such as simple implementation. As a part of this study, this paper compares the THD results of the conventional method and the proposed method with offset voltage injection to reduce the THD. In this paper, simulations have been carried out to verify the effectiveness of the proposed scheme, and the proposed method is implemented by a HILS (Hardware in the Loop Simulation) system. The obtained results show agreement with the simulation results. It is confirmed that the new scheme achieved the maximum level output voltage and improved the THD quality.

**Key words:** High voltage direct current (HVDC) transmission, HILS (Hardware in the Loop Simulation), Modulation index (MI), Modular multilevel converter (MMC), Nearest level modulation (NLM), Sub-module (SM), Third harmonics, Total harmonic distortion (THD)

#### I. Introduction

The modular multilevel converter (MMC) was first introduced in 2001 as a new type of voltage source converter (VSC) [1]. After its introduction, many researchers have been focused on the technical challenges corresponding with the design, operation and control of the MMC to develop its performance for numerous applications: VSC based transmission [2]. Due to its good modularity, efficiency, flexible scalability, better harmonic performance and excellent quality waveforms, the MMC has received a great deal of attention in the function of HVDC transmission, reactive power compensation, motor drives, electric railways, etc. Now, it is hot topic in HVDC research and construction.

Manuscript received Jun. 1, 2019; accepted Aug. 26, 2019 Recommended for publication by Associate Editor Younghoon Cho. Recently, the introduction of large capacity offshore wind power has been expanding due to developments in new and renewable energy. HVDCs are being introduced for linking systems. The MMC is well known as the most applicable and proficient type of converter For the HVDC systems associating with offshore wind farms and MVDC systems [3].

In the grid connection of offshore wind power generation systems, two MMCs use the back to back structure. This study is concerned with sharing the generator voltage of an offshore wind turbine among two MMC's. In this study, a THD reduction technique is proposed for the generated output voltage of the MMC that works as the source voltage of a wind turbine.

Meanwhile, voltage generation through an MMC can be broadly divided into pulse width modulation (PWM) and staircase modulation. When the SM number is relatively small, PWM is usually used since it can make the output voltage of an MMC achieve an excellent quality [4]. However, the disadvantage is a high power loss. On the other hand, since

<sup>†</sup>Corresponding Author: dmlee@hongik.ac.kr

Tel: +82-2-320-3047, Hongik University, Seoul, Korea

<sup>\*</sup>School of Electronic and Electrical Eng., Hongik University, Korea

NLM is simpler and the switching frequency is lower, it is recommended for a large number of SMs so that the output quality is good enough [5].

Hybrid topology of an MMC can be for enlarging the output voltage level [6]. However, it makes the highest THD which is a serious threat to the reliable operations of MMC systems and creates a more complication of MMC topology. That is why NLM is the best solution for overcoming the above mentioned problem.

When the operational level is low, the THD of the output voltage is rather high. Meanwhile the operational level should be controlled by changing the modulation index (MI). Moreover, an MMC in an MVDC is more formed because of the small number of SMs [7].

Methods for reducing the THD have been proposed by several researchers [8]-[10]. In [8], Li et al, proposed a method combining PWM and NLM for improving the output voltage and reducing the THD. However, this method substantially increases the switching frequency of IGBTs. The method proposed in [9] can increase the output voltage level without increasing the THD. However, it leads to a change of the average voltage of the sub-module capacitor. Therefore, it results in an amplitude change of the output voltage. Some harmonic elimination methods were presented in [10], [11]. However, they require more calculations, which results in lower modularity of MMCs. The authors of [12], [13] presented a strategy to determine the switching angles that minimizes the THD with analytically proof. However, the MI is restricted in the zone close to its upper bound, making it inappropriate for applications with various voltage level requirements or unstable load conditions. Moreover, the calculation complexity of these techniques is high and they are troublesome to implement in real time simulations. More importantly, the reducing THD becomes a common concern for sensitive industries and HVDC applications.

The proposed method has a simple and effective way to overcome these problems. The MMC is operated in NLM to reduce the total harmonic distortion (THD) of the pole voltage and to generate the maximum level of pole voltage by adding the third harmonic voltage. Moreover, this paper compares the performances of several methods that aim to reduce THD by adding offset voltage.

This paper is organized as follows. In Section II, the operational characteristics of an MMC are introduced. A comparison of different modulation methods that uses offset voltage injection is analyzed in Section III. Simulation and experimental results are presented in Section IV and section V, respectively. Finally, some conclusions are presented in Section VI.

## II. OPERATIONAL CHARACTERISTICS OF AN MMC

# A. Output Voltage Forming

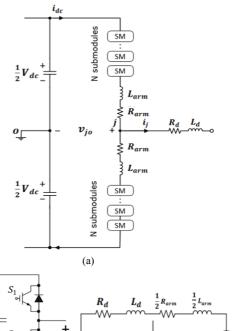

Fig. 1(a) shows the configuration of a single phase MMC,

Fig. 1. Diagrams. (a) Topology of a single phase MMC. (b) Submodule structure. (c) Equivalent circuit of an MMC.

which consists of two arms. Each arm includes a total of  $\,^{n}_{SM}$  sub-modules and two arm reactors. Two arms in the same phase form a phase unit.

Fig. 1(b) shows an SM structure. For commercial HVDC systems, a SM configured with a half bridge is very popular. Each SM is a simple chopper cell composed of two insulated-gate bipolar transistor (IGBT) switches, two antiparallel diodes and a capacitor.

The SM output voltage  $V_{SM}$  only has two values:  $V_{SM} = V_{C}$  when the upper IGBT is switched on and the lower one is switched off; or  $V_{SM} = 0$  when the lower IGBT is switched on and the upper one is switched off. This means that each SM only has two conditions in normal operation: switched on or off.

Upper arm and lower arm voltage equations in single phase are shown as follows.

$$u = -u_n + 2L\frac{di_n}{dt} - \frac{V_{dc}}{2} \tag{1}$$

$$u = -u_p + 2L\frac{di_p}{dt} + \frac{V_{dc}}{2}$$

(2)

where, u is voltage of a single phase. In addition,  $u_p$  and  $u_n$  are the voltages of the upper arm and the lower arm, respectively. The current in a single phase is:

$$i = i_n - i_p \tag{3}$$

where, i,  $i_p$  and  $i_n$  are the phase current, upper arm and lower arm current, respectively.

The upper arm current is the total of half the phase current  $i_a$ , one third of the DC current  $i_{dc}$  and the circulating current in the phase  $i_{icc}$ .

$$i_{p} = \frac{a}{2} + \frac{i_{dc}}{3} + i_{jcc} \tag{4}$$

$$i_{n} = -\frac{i}{2} + \frac{i_{dc}}{3} + i_{jcc} \tag{5}$$

The common circulating current  $i_{jcc}$  can be represented by equation (6).

$$i_{jcc} = \frac{i_{p} + i_{n}}{2} - \frac{i_{dc}}{3} \tag{6}$$

The circulating current does not influence the DC and AC part of the circuit. However, it does cause an increase in the arm current and the voltage ripple of the capacitors. The terminal voltage  $v_{jo}$  can be expressed by equations (7) and (8).

$$v_{jo} = \frac{V_{dc}}{2} - v_{jU} - R_{arm} \frac{i}{p} - L_{arm} \frac{di}{dt}$$

(7)

$$v_{jo} = -\frac{V_{dc}}{2} - v_{jL} - R_{arm} \frac{i}{n} - L_{arm} \frac{di}{dt}$$

(8)

Equation (9) is obtained by adding equations (7) and (8).

$$v_{jo} = \frac{u_n - u_p}{2} - \frac{1}{2} (R_{arm} + L_{arm} \frac{d}{dt}) i_j$$

(9)

Based on equation (9), the arm reactor plays an important role for the voltage drop.

$v_e$  is the electromotive force (EMF) and is expressed as following equation (10).

$$v_e = \frac{u_n - u_p}{2} \tag{10}$$

In general, the ac EMF reference value is simplified as equation (11).

$$v_e^{ref} = \frac{MI * V_{dc}}{2} \cos(\omega t) \tag{11}$$

where MI is the modulation index, and  $\omega$  is the angular frequency.

An equivalent circuit of the MMC is shown in Fig. 1(c). From (1), (2) and (3), the output voltage can be written as

$$v = \frac{1}{2}(u_n - u_p) + \frac{L}{2}\frac{di}{dt}$$

(12)

With the traditional NLM method, N sub-modules are inserted into the circuit. Therefore, the equation (13) is supported the dc side.

$$V_{dc} = u_p + u_n \tag{13}$$

# B. Modulation Analysis

Generally, pulse width modulation (PWM) and staircase

Fig. 2. Overall diagram of the NLM method.

modulation are two common modulation techniques. Using various modulation methods, PWM is based on regulating all the sub-module capacitor voltages. Staircase modulation is based on a sorting technique to control voltages. Staircase modulation has a lower switching frequency, and the developed output voltage changes less suddenly. PWM is usually used when the number of SMs in the MMC is relatively small since this can make the output voltage of the MMC having an excellent quality. However, it suffers due to a great loss of power. On the other hand, the staircase modulation SM is easy to calculate and has a lower power loss. However, the quality of voltage is not good when the number of SMs in the MMC is comparatively small. The equal area method (EAM) [14], selective harmonic reduction method (SHRM)[15], and nearest level modulation (NLM) method are common staircase modulation schemes. The EAM and SHRM schemes develop comparatively low level harmonics. However, they need more calculations. That is why NLM is one of the most commonly used staircase modulation schemes.

NLM works by using a rounding function to select the level changing point, and it avoids the use of triangular waves in the output voltage. Thus, it possesses uncomplicated calculations and easy implementation.

When an MMC operates in the NLM,  $E_a$  is the peak value of the inner alternating voltage, and MI is calculated by the relation of the AC voltage and the DC voltage.

$$MI = \frac{E}{V}$$

$$\frac{dc}{2}$$

(14)

The upper and lower arms reference voltages can be expressed by using the trigonometric function along with modulation index as shown in equations (15) and (16).

$$u_p^{ref} = \frac{V_{dc}}{2} [1 - MI \cos \omega t]$$

(15)

$$u_n^{ref} = \frac{V_{dc}}{2} [1 + MI \cos \omega t]$$

(16)

Fig. 2 shows an overall diagram of the NLM method using the rounding function and the reduced switching frequency voltage balancing algorithm. The number of sub-modules is determined by loading the command of the upper and lower arm reference voltage.

The voltage level plays an important role in NLM because it impacts on the average switching time and the output voltage THD. The THD of the output voltage is designated by equation (17).

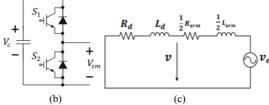

Fig. 3. THD with respect to the MI according to the number of SMs.

$$THD = \frac{\sqrt{\sum_{n=2}^{\infty} V_{n\_rms}^2}}{V_{find\_rms}}$$

(17)

where,  $V_{n\_rms}$  and  $V_{fund\_rms}$  are the RMS voltage of the nth harmonic and the fundamental harmonics, respectively.

When the voltage level and modulation index increase, the THD can be minimized. However, it reduces nonlinearly in a definite range, which is due to the level of the voltage casually changing because of the MI. Fig. 3 shows THD results when the maximum voltage level is designated to  $10{\sim}50$ , and the scale of the MI is set at  $0.6 \le MI \le 1$ . If the voltage level is more than 50, the output voltage THD stays as small as less than 2%. By using sine PWM with equations (15) and (16), the THD with respect to the MI corresponding to different level numbers of MMCs is shown in Fig. 3.

# III. PROPOSED METHOD FOR REDUCING THE THD IN THE OUTPUT VOLTAGE

This paper proposes a new scheme that compensates the decrease of the output voltage level due to a low MI. The proposed method decreases the total harmonic distortion (THD) of the pole voltage corresponding with the magnitude of the MI.

In this method, the third harmonic voltage plays an important role to control the phase voltage to obtain the maximum pole voltage. The maximum level pole voltage shows the lowest THD. Moreover, a triangular waveform by the Fourier series consists of a number of harmonics whereas a sinusoidal waveform only consists of one frequency component. Due to the sinusoidal waveform of the third harmonic, it also helps reduce the THD of the output voltage.

The proposed method operated with the third harmonic voltage having a sinusoidal waveform, which is explained by equation (18).

$$v_{no} = \alpha * v_{3rd} \tag{18}$$

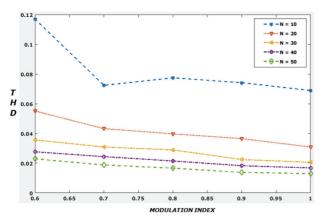

Fig. 4. Pole, phase and third harmonic voltages.

$$v_{abco}^* = v_{abcn}^* + v_{no} \tag{19}$$

Where  $\alpha$  is a variable with respect to a variable modulation index. It can be conceived by using the maximum value equation of the pole voltage. The value of  $\alpha$  has been evaluated in the zone of  $0 \le MI \le 1$ , where the pole voltage, due to the third harmonic voltage injection, is greater than the phase voltage.

By using equations (15) and (16), the reference voltage is determined according to the value of the MI, and if NLM is applied as shown in Fig. 2, the number of pole voltage levels can be calculated. Therefore, the offset voltage in equation (18) is applied and follows equation (19). Therefore, the pole voltage command value becomes  $\frac{V_{dc}}{2}$  and the maximum number of voltage levels is generated. As a result, the THD is reduced.

Fig. 4 shows the pole voltage, phase voltage and harmonic. The pole voltage always stands at the maximal value in the phase angle of  $\theta = \frac{\Pi}{2}$ . It can be initiated by applying the pole voltage's maximum value equation.

Equations (20)-(22) express the phase voltage with the MI and the DC voltage.

$$v_{an} = MI * \frac{V_{dc}}{2} \sin \omega t \tag{20}$$

$$v_{bn} = MI * \frac{V_{dc}}{2} (\sin \omega t - \frac{2}{3} \Pi)$$

(21)

$$v_{cn} = MI * \frac{V_{dc}}{2} (\sin \omega t + \frac{2}{3} \Pi)$$

(22)

Third harmonic equation with the MI and the DC voltage.

$$v_{an\_3rd}^* = \alpha * MI * \frac{V_{dc}}{2} \sin \omega t$$

(23)

$v_{bn\_3rd}^*$  and  $v_{cn\_3rd}^*$  support equation (23) and the difference is just the phase shift.

The following formula defines the greatest value of the pole voltage.  $\alpha$  can be calculated by equation (24).

$$\frac{V}{\frac{dc}{2}} * MI * \sin \omega t + \alpha * \frac{V}{\frac{dc}{2}} * MI * \sin 3\omega t = \frac{V}{\frac{dc}{2}}$$

$$\alpha = -6(\frac{1}{MI} - 1) : (0 < MI \le 1)$$

(24)

Fig. 5. Flowchart of the proposed method.

Fig. 5 shows the proposed algorithm for offset voltage control including the NLM. The phase voltage reference is set through sensing the voltage.  $\alpha$  is determined in accordance with the value of the MI and follows equation (24). The offset voltage and pole voltage references are expressed by equations (18) and (19), respectively. The pole voltage reference is passed through the NLM algorithm to achieve the switching pulses. For real-time operation, a digital signal processor (DSP) board can freely implement the proposed algorithm on since it does not demand a huge running period.

# IV. COMPARISON OF MODULATION SCHEMES THAT UTILIZE OFFSET VOLTAGE INJECTION

In terms of THD reduction through setting the maximum voltage level by injecting offset voltage [16], there are a number of modulation schemes available. Some of them are listed below and their results are compared with the THD results of the proposed method.

# A. Modulation Analysis

#### 1) Modulations with Offset Voltage Injection

The pole voltage  $v_{abco}$  is a summation of the phase voltage  $v_{abcn}$  and the offset voltage  $v_{no}$ .

$$v_{abco} = v_{abcn} + v_{no} \tag{25}$$

For applying the offset voltage control modulation, the relationship between the prime values of the maximum and the minimum pole voltages can be made equivalent by equation (26) and offset voltage is identified by equation (27). Where,  $V_{no}$  has a well-known triangular shape.

$$v_{\text{max}}^* + v_{no} = -(v_{\text{min}}^* + v_{no})$$

(26)

$$v_{no} = -\frac{v_{max}^* + v_{min}^*}{2} \tag{27}$$

TABLE I

CIRCUIT PARAMETERS FOR SIMULATION STUDY

| Parameters       | Values  |

|------------------|---------|

| DC bus Voltage   | 690 V   |

| Arm Inductor     | 3.00 mH |

| SM Capacitor     | 7.5 mF  |

| Frequency        | 60 Hz   |

| Line Inductance  | 1.00 mH |

| Modulation Index | 0.9     |

| Number of SM     | 30      |

In this modulation, the MMC output voltage level decreases, and the output voltage level is dependent on the phase voltage magnitude (i.e. MI).

# 2) Offset Voltage Control Modulation

There is another method for obtaining the maximum output voltage level. This method uses equation (28) for controlling the offset voltage. In this method, the shape of  $v_{no}$  is a scaled triangular waveform.

$$v_{no} = -\alpha * \frac{v_{\text{max}}^* + v_{\text{min}}^*}{2}$$

(28)

where,  $\alpha$  is variable that is controlled by changing the modulation index.

## 3) Third Harmonic Voltage Control Method

By using the third harmonic method, the pole voltage is the summation of the phase voltage and the third harmonic voltage  $v_{3rd}$ . Equation (29) can be simplified by the third harmonic voltage control method.

$$v_{abco} = v_{abco} + v_{3rd} \tag{29}$$

Moreover, equation (30) can simplify the relationship between the third harmonic and the phase voltage.

$$v_{3rd} = \frac{1}{6} * v_{abcn} \tag{30}$$

In this modulation, the output voltage level depends on the phase voltage magnitude, and the THD result is not better in the expected modulation index range.

## V. SIMULATION RESULTS

To verify the performance of the proposed modulation method, a detailed model is developed and simulations are carried out with MATLAB/Simulink. The circuit parameters for the simulation model are presented in Table I.

Table II summarizes comparison results for four different modulation schemes. The proposed method maintains a constant maximum pole voltage level. This grants the lowest THD of the pole voltage and ripple reduction of the SM capacitor voltage.

Fig. 6 presents a comparison between the third harmonic method and the proposed method. What is interesting is that

| Items                    | Only offset                                               | $\alpha$ offset method                                             | Using third harmonic            | Proposed method                          |

|--------------------------|-----------------------------------------------------------|--------------------------------------------------------------------|---------------------------------|------------------------------------------|

| Main Function            | $v_{no} = -\frac{v_{\text{max}}^* + v_{\text{min}}^*}{2}$ | $v_{no} = -\alpha * \frac{v_{\text{max}}^* + v_{\text{min}}^*}{2}$ | $v_{no} = v_{an} + v_{an\_3rd}$ | $v_{no} = v_{an} + \alpha * v_{an\_3rd}$ |

| Maximum Phase<br>Voltage | $MI * \frac{V}{dc}$                                       | $MI * \frac{V}{\sqrt{3}}$                                          | $MI * \frac{V}{dc}$             | $MI * \frac{V}{dc} \frac{dc}{\sqrt{3}}$  |

| Maximum Pole<br>Voltage  | $MI * \frac{V}{dc}$                                       | $\frac{V}{\underline{dc}}$                                         | $MI * \frac{V}{dc}$             | $\frac{V}{dc}$                           |

| THD                      | Greatest                                                  | Lower                                                              | Greater                         | Lowest                                   |

TABLE II

COMPARISON OF DIFFERENT MODULATION SCHEMES

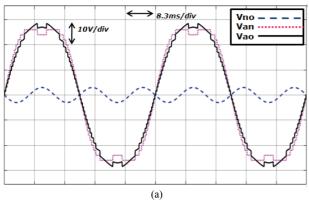

Fig. 6. Performance analysis of two schemes. (a) Third harmonic injection method. (b) Proposed method.

the pole voltage is higher in the proposed method than in the third harmonic injection method in Fig. 6(a).

Moreover, in third harmonic injection method, the peak value of the phase voltage is not constant which is responsible for reducing the voltage level. On the other hand, Fig. 6(b) shows that the proposed scheme generates the pole voltage at its greatest value, which is half of the DC voltage. Therefore, the output voltage is generated with (N+1) levels.

In order to increment the pole voltage magnitude so that is larger than the phase voltage, the third harmonic voltage is added. These waveforms ensure that the pole has a constant maximum level. Because there are more levels in the pole voltage of the proposed method, the THD result shows more improvement than the third harmonic method.

# A. THD Results

For the MMC the peak AC side phase voltage can never exceed half of the DC side pole voltage. In other words, the modulation index is limited to the interval  $0 \le MI \le 1$  [17]. Moreover, in [18], Pedram and Miller analyzed the modulation indexes of wind applications. They mentioned that for wind turbine applications, the perfect range of the modulation index is  $0.8\sim0.95$ . In [19], Li, et al. analyzed the maximum modulation index for an MMC, and they derived some equations for obtaining the limitation of the modulation index.

In addition, they pointed out that the modulation index is smaller than 1, and that a design with a larger capacitor voltage

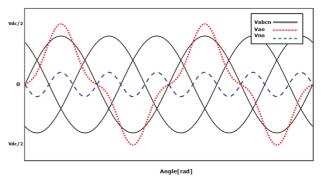

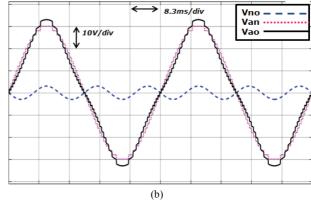

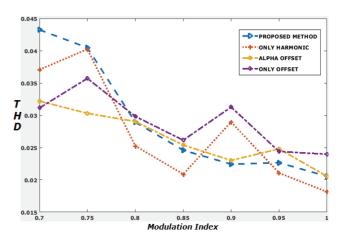

Fig. 7. Phase voltage THD analysis results for four modulation schemes.

can result in a higher penalty. From the above discussion, it can be seen that in a wind turbine based power system, the modulation index range is approximately 0.8~0.95.

In this range, the proposed method shows the lowest THD results for the phase voltage and line to line voltage. This can be seen in Fig. 7.

Fig. 7 depicts the THD values of the phase voltage for four modulation schemes with respect to different modulation indexes. The phase voltage THD is inversely proportional to the MI.

From Fig. 7, it can be seen that there are several fluctuations in the THD values with respect to the MI by using only the

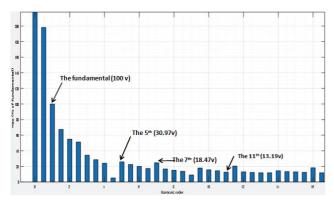

Fig. 8. Magnitude (% fundamental) and harmonic order.

offset voltage injection method and only the third harmonic addition method. Due to fluctuations in the THD results with respect to the MI, only the third harmonic and only the offset voltage injection methods are not suitable for wind turbine applications.

In addition, Fig. 7 shows that the proposed (alpha harmonic) method has a lower THD in the expected modulation index range than the alpha offset method.

Thus, it can be concluded that for wind power application that worked about the upper mentioned modulation index range (0.8~0.95), the proposed method shows a lower THD than the other three methods. Moreover, in the proposed method, the THD value always decreases with an increment of the MI. These phenomena are not present in other three methods.

Harmonic components are shown in Fig. 8. The results show that the fifth, seventh and eleven harmonics of the line voltage are very short in magnitude. Because of the 120-degree phase shift among the phase voltages, all of the triplen harmonics in the line voltage are very small.

# VI. EXPERIMENTAL RESULTS

To validate the efficacy of the proposed method, experiments were carried out with a HILS (Hardware in the Loop Simulation) system. For experimental results, a scaled hardware prototype was assembled in the lab.

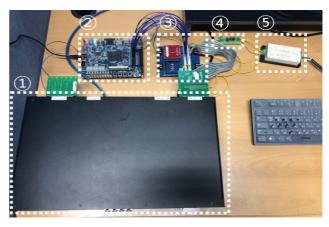

In Fig. 9 some devices are shown for the setup including an OP4510 RT-LAB ① for real time simulation, a control board with a FPGA ②, a signal interface board ③, a voltage regulator for making 3.3V ④, and a power supply ⑤.

An MMC model made by Simulink is implemented in the Real Time OS ① and the controller with a FPGA ② make output voltages for a wind turbine with the proposed offset voltage adjustment method.

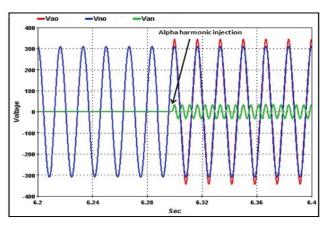

Fig. 10 shows experimental waveforms of the pole voltage, phase voltage and third harmonic voltage when the MMC is operated at 31-levels. After the third harmonic injection, the pole voltage changes. Simulation results and experimental waveforms confirm that after injecting alpha harmonics the

Fig. 9. Experimental setup.

Fig. 10. Experimental waveform of the pole, phase, and harmonic voltages.

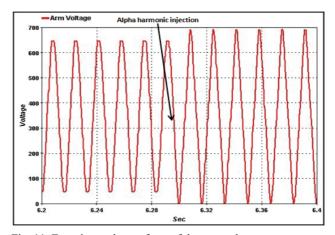

Fig. 11. Experimental waveform of the arm voltage.

pole has a level of  $V_{dc}/2$ , which is the maximum pole voltage. Thus, the THD results show a better improvement.

Fig. 11 shows the changes in the arm voltage after the alpha harmonic injection. After the alpha harmonic injection, the arm voltage maintains the maximum peak value which is the same as the DC bus voltage.

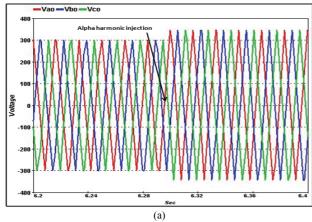

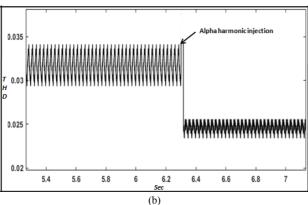

Fig. 12(a) shows an experimental waveform of the pole voltage, which is regulated in terms of magnitude and phase.

Fig. 12. Experimental waveforms. (a) Pole voltage. (b) THD value.

After the alpha harmonic injection, the pole voltage level has changed and reached the peak value. Moreover, after the alpha harmonic injection, the generated pole voltage is more linear than before. Fig. 12(b) shows the amount of change in the THD value after injecting the alpha harmonic.

In proposed system, the alpha harmonic injection time is 6.3 sec. Before the alpha harmonic injection, the THD of the pole voltage is 3.42%. After the alpha harmonic injection, the THD of pole voltage becomes 2.34%, which is a 31% reduction in the THD.

# VII. CONCLUSIONS

This paper proposed a new voltage control scheme for an NLM operated MMC to develop both the output voltage and line-to-line voltage THD, and to achieve the maximum level of the output voltage. The proposed method keeps the advantages of the traditional voltage control scheme such as easy implementation and low switching loss. In addition, it avoids the disadvantages of existing methods such as increased THD, increased voltage level, complex calculations, topology complexity, etc.

Moreover, for the MMC itself, the proposed technique offers an easy numerical algorithm for the MMC topology that can be used with any number of sub-modules per arm either experimentally or by simulation. The usefulness of the proposed scheme was evaluated with MATLAB simulations with 30 SMs per arm. The benefits of the proposed method were verified under different experiment conditions and the obtained results matched well with the design expectation. Moreover, the proposed scheme showed a promising application potential in MMCs.

#### ACKNOWLEDGMENT

This research was supported by Korea Electric Power Corporation (Grant number: R17XA05-18).

#### REFERENCES

- R. Marquardt, "Stromrichterschaltungen mit verteilten energiespeichrn," *German Patent*, DE10103031A1, 24 Jan. 2001.

- [2] T. Li and C. Zhao, "Characteristic analysis and fault-tolerant control of modular multilevel converters under sub-module faults," *Int. Trans Electr. Energy Syst.*, Vol. 26, No. 7, pp. 1444-1461, Jul. 2016.

- [3] G. Bergna, E. Berne, P. Egrot, P. Lefrance, A. Arzande, J. Vannier, and M. Molinas, "An energy based controller for HVDC modular multilevel converter in decoupled double synchronous reference frame for voltage oscillation," *IEEE Trans. Ind. Electron.*, Vol. 60, No. 6, pp. 2360-2371, Jun. 2013.

- [4] I. Gowaid, G. Adam, S. Ahmed, D. Holliday, and B. Williams, "Analysis and design of a modular multilevel converter with trapezoidal modulation for medium and high voltage dc-dc transformers," *IEEE Trans Power Electron.*, Vol. 30, No. 10, pp. 5439-5457, Oct. 2015.

- [5] S. Gangquan, J. Zhu, Y. Lei, L. Jia, and Y. Zhang, "An enhanced level increased nearest level modulation modular multilevel converter," *Int. Trans Electr. Energ. Syst.*, Vol. 29, No. 1, Aug. 2018.

- [6] J. Wang, H. Xu, M. Hao, and Z. Bai, "A hybrid modular multilevel converter topology with an improved nearest level modulation method," *J. Power Electron.*, Vol. 17, No. 1, pp. 96-105, Jan. 2017.

- [7] Y. H. Park, D. H. Kim, J. H. Kim, and B. M. Han, "A new scheme for nearest level control with average switching frequency reduction for modular multilevel converters," *J. Power Electron.*, Vol. 16, No. 2, pp. 522-531, Mar. 2016.

- [8] Z. Li, P. Wang, H. Zhu, and Y. Li, "An improved pulse width modulation method for chopper-cell-based modular multilevel converters," *IEEE Trans. Power Electron.*, Vol. 27, No. 8, pp. 3472-3481, Aug. 2012.

- [9] P. Hu and D. Jiang, "A level-increased nearest level modulation method for modular multilevel converter," *IEEE Trans. Power Electron.*, Vol. 30, No. 4, pp. 1836-1842, Apr. 2015.

- [10] Z. Du, L. M. Tolbert, J. N. Chiasson, and B. Ozpineci, "Reduced switching-frequency active harmonic elimination for multilevel converters," *IEEE Trans. Ind. Electron.*, Vol. 55, No. 4, pp. 1761-1770, Apr. 2008.

- [11] Q. Tu and Z. Xu, "Impact of sampling frequency on harmonic distortion for modular multilevel converter," *IEEE Trans. Power Electron.*, Vol. 26, No. 1, pp. 298-306, Jan. 2011.

- [12] Y. Liu, H. Hong, and A.Q. Huang, "Real-time calculation of switching angles minimizing THD for multilevel inverters with step modulation," *IEEE Trans. Ind. Electron.*, Vol. 56, No. 2, pp. 285-293, Feb. 2009.

- [13] Y. Liu, H. Hong, and A. Q. Huang, "Real-time algorithm for minimizing THD in multilevel inverters with unequal or varying voltage steps under staircase modulation," *IEEE Trans. Ind. Electron.*, Vol. 56, No. 6, pp. 2249-2258, Jun. 2009.

- [14] B. Han, B. Bae, S. Baek, and G. Jang, "Dynamic characteristics analysis of SSSC based on multibridge inverter," *IEEE Trans. Power Del.*, Vol. 17, No. 2, pp. 623-629, Apr. 2002.

- [15] S. Yashwant and A. Nampally, "Modular multilevel converter modulation using fundamental switching selective harmonic elimination method," *IEEE ICRERA*, pp. 736-741, Nov. 2016.

- [16] J. H. Kim, D. H. Kim, and B. M. Han, "Offset voltage control scheme for modular multilevel converter operated in nearest level control," *Energies*, Vol. 10, No. 7, pp. 863-880, Jun. 2017.

- [17] K. Sharifabadi, Design, Control, and Application of Modular Multilevel Converters for HVDC Transmission Systems, IEEE Press/Wiley, 2016.

- [18] P. Sotoodeh and R.D. Miller, "A new multi-level inverter with FACTS capabilities for wind applications," *IEEE Green Technologies Conference*, pp. 271-276, 2013.

- [19] Y. Li, X. Shi, B. Liu, F. Wang, and W. Lei, "Maximum modulation index for modular multilevel converter with circulating current control," *IEEE Energy Conversion Congress and Exposition*, pp. 491-498, 2014.

**Devnath Anupom** received his B.S. degree in Electrical and Electronic Engineering from the Chittagong University of Engineering and Technology, Chittagong, Bangladesh, in 2017. He is presently working towards his M.S. degree at Hongik University, Seoul, Korea. His current research interests include MMCs for HVDC systems and power

conversion systems for renewable energy source.

Dong-Cheol Shin received his B.S. and M.S. degrees in Electrical Engineering from Hongik University, Seoul, Korea, in 2017 and 2019, respectively, where he is presently working towards his Ph.D. degree. His current research interests include MMCs for HVDC systems and power conversion systems for renewable energy sources.

Dong-Myung Lee received his B.S. and M.S. degrees in Electrical Engineering from Hanyang University, Seoul, Korea, in 1994 and 1996, respectively. He received his Ph.D. degree in Electrical and Computer Engineering from the Georgia Institute of Technology, Atlanta, GA, USA, in 2004. From 1996 to 2000, he worked for LG Electronics Inc.,

Seoul, Korea. From 2004 to 2007, he was employed as a Senior Engineer at the Samsung SDI R&D Center, Yongin, Korea. From 2007 to 2008, he was a Research Professor in the Department of Electrical Engineering, Hanyang University. Since 2008, he has been a Professor in the School of Electronic and Electrical Engineering, Hongik University, Seoul, Korea. His current research interests include multi-level converters, variable speed drives, power quality compensation devices, power conversion systems for renewable energy sources and personal mobility.