JPE 19-6-13

https://doi.org/10.6113/JPE.2019.19.6.1477 ISSN(Print): 1598-2092 / ISSN(Online): 2093-4718

# Common-Mode Voltage and Current Harmonic Reduction for Five-Phase VSIs with Model Predictive Current Control

Huu-Cong Vu\* and Hong-Hee Lee†

<sup>†,\*</sup>School of Electrical Engineering, University of Ulsan, Ulsan, Korea

#### **Abstract**

This paper proposes an effective model predictive current control (MPCC) that involves using 10 virtual voltage vectors to reduce the current harmonics and common-mode voltage (CMV) for a two-level five-phase voltage source inverter (VSI). In the proposed scheme, 10 virtual voltage vectors are included to reduce the CMV and low-order current harmonics. These virtual voltage vectors are employed as the input control set for the MPCC. Among the 10 virtual voltage vectors, two are applied throughout the whole sampling period to reduce current ripples. The two selected virtual voltage vectors are based on location information of the reference voltage vector, and their duration times are calculated using a simple algorithm. This significantly reduces the computational burden. Simulation and experimental results are provided to verify the effectiveness of the proposed scheme.

Key words: Common-mode voltage (CMV), Five-phase voltage source inverter, Model predictive current control (MPCC), Reduced current harmonics

## I. INTRODUCTION

Over the last decade, a number of five-phase drives have been developed for various applications such as naval propulsion systems, more-electric aircraft, electric vehicle traction drives and offshore turbines due to their advantages over their three-phase counterparts: enhanced faulty tolerance, lower torque pulsation, higher torque density, reduced per phase current without an increased per phase voltage, and lower dc-link current harmonics [1]-[6]. Typically, five-phase drives are supplied by a two-level five-phase voltage source inverter (VSI).

Some of the modulation and control schemes that have been developed for five-phase VSIs include space vector pulse-width modulation (PWM) [7], carrier-based PWM [8], and model predictive current control [9]. Among these, model predictive current control (MPCC) is the most effective and simplest current control scheme for five-phase VSIs due to its

simple principle, quick response, and control flexibility [10]-[12]. In the MPCC for five-phase VSIs, the output current is predicted for all of the possible voltage vectors of a five-phase VSI, while the optimal voltage vector is selected using a predefined cost function with error terms between the predicted output current and the reference. Finally, the optimal voltage vector is applied during the sampling time period to drive the five-phase VSI.

Despite these advances, the MPCC for five-phase VSIs still suffers some certain problems, namely high computational burden, low-order current harmonics, and common-mode voltage (CMV). CMV causes electromagnetic interference effect where the fault activation of current detector circuits and common-mode currents leads to motor bearing failures [13], [14]. Some MPCC schemes have been developed in attempts to reduce the CMV for five-phase VSIs by selecting suitable voltage vectors for the input control set [15], [16]. When compared to the conventional MPCC scheme, the peak CMV of these schemes is reduced by 80%. However, large low-order current harmonics are inevitable due to the fact that only one voltage vector is applied during one sampling period to drive the VSI. In [17], virtual voltage vectors were employed as an input control set of MPCC to reduce low-order current

Manuscript received Jul. 28, 2019; accepted Aug. 20, 2019 Recommended for publication by Associate Editor Sung-Jin Choi. †Corresponding Author: hhlee@mail.ulsan.ac.kr

Tel: +82-52-259-2187, Fax: +82-52-259-1686, University of Ulsan

\*School of Electrical Engineering, University of Ulsan, Korea

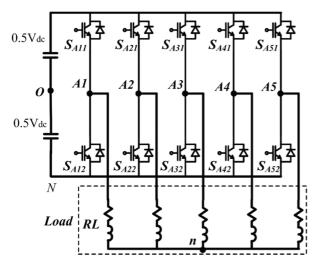

Fig. 1. Two-level five-phase voltage source inverter.

harmonics. Although the low-order current harmonics were significantly reduced in this scheme, the computation time remained relatively high since it involved a large number of current predictions and cost function evaluations. Furthermore, the CMV problem was not considered.

In order to overcome these limitations, this paper proposes an effective MPCC scheme using 10 virtual voltage vectors to reduce the CMV and current harmonics for a five-phase VSI. In the proposed scheme, 10 virtual voltage vectors are used as an input control set for the MPCC scheme to simultaneously reduce the CMV and low-order current harmonics. Furthermore, two of the 10 virtual voltage vectors are applied during one sampling period to reduce current ripples. The two virtual voltage vectors are determined according to the location of the reference voltage vector. In addition, their duration times are calculated using a simple algorithm. This considerably reduces the computation time. Simulation and experimental results are provided to verify the effectiveness of the proposed scheme.

# II. CONVENTIONAL MPCC SCHEME OF A TWO-LEVEL FIVE-PHASE VSI

# A. Model of Two-Level Five-Phase VSI

An electrical diagram of a two-level five-phase VSI is shown in Fig. 1. The switching function of each phase  $S_i$  (i=A1, A2, A3, A4, A5) is defined as:

$$S_i = \begin{cases} 1 \text{ if } S_{i1} = 1 \text{ and } S_{i2} = 0\\ 0 \text{ if } S_{i1} = 0 \text{ and } S_{i2} = 1 \end{cases}$$

(1)

Then, the inverter pole voltages are expressed as:

$$V_{iN} = S_i V_{dc} \,, \tag{2}$$

where  $V_{dc}$  is the DC-link voltage.

The inverter phase voltages are written as functions of the inverter pole voltages:

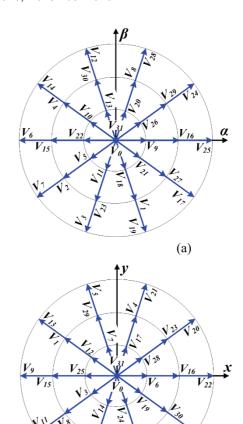

Fig. 2. Five-phase VSI voltage space vectors in: (a)  $(\alpha-\beta)$  plane, (b) (x-y) plane.

(b)

$$V_{A1} = (4/5)V_{A1N} - (1/5)(V_{A2N} + V_{A3N} + V_{A4N} + V_{A5N})$$

$$V_{A2} = (4/5)V_{A2N} - (1/5)(V_{A1N} + V_{A3N} + V_{A4N} + V_{A5N})$$

$$V_{A3} = (4/5)V_{A3N} - (1/5)(V_{A1N} + V_{A2N} + V_{A4N} + V_{A5N})$$

$$V_{A4} = (4/5)V_{A4N} - (1/5)(V_{A1N} + V_{A2N} + V_{A3N} + V_{A5N})$$

$$V_{A5} = (4/5)V_{A5N} - (1/5)(V_{A1N} + V_{A2N} + V_{A3N} + V_{A4N})$$

(3)

The five-phase VSI generates 32 switching state combinations. Each switching state combination corresponds to a voltage vector, which is mapped into both the  $(\alpha-\beta)$  and (x-y) planes using a Clarke transformation as follows [13]:

$$\begin{bmatrix} V_{\alpha} \\ V_{\beta} \\ V_{x} \\ V_{y} \end{bmatrix} = \frac{2}{5} \begin{bmatrix} 1 & \cos\delta & \cos2\delta & \cos3\delta & \cos4\delta \\ 0 & \sin\delta & \sin2\delta & \sin3\delta & \sin4\delta \\ 1 & \cos3\delta & \cos\delta & \cos4\delta & \cos2\delta \\ 0 & \sin3\delta & \sin\delta & \sin4\delta & \sin2\delta \end{bmatrix} \begin{bmatrix} V_{A1} \\ V_{A2} \\ V_{A3} \\ V_{A4} \\ V_{\alpha} \end{bmatrix}, \quad (4)$$

where  $\delta = 2\pi/5$ .

Figs. 2(a)-2(b) show the space vectors for the five-phase VSI in the  $(\alpha-\beta)$  and (x-y) planes. The obtained voltage vectors are classified into four groups, as shown in Table I: zero vectors (ZV), small vectors (SV), medium vectors (MV), and large vectors (LV).

| TABLE I                                           |    |

|---------------------------------------------------|----|

| CMV ASSOCIATED WITH DIFFERENT VOLTAGE VECTOR GROU | РS |

| Group | Voltage vectors                                                                                                                                                     | $ V_{lphaeta} $                | $ V_{xy} $            | $ V_{\rm CM} $ |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-----------------------|----------------|

| ZV    | $V_0(00000), V_{31}(11111)$                                                                                                                                         | 0                              | 0                     | $0.5V_{dc}$    |

| SV    | $V_9(01001), V_{26}(11010)$<br>$V_{20}(10100), V_{I3}(01101)$<br>$V_{I0}(01010), V_{22}(10110)$<br>$V_5(00101), V_{II}(01011)$<br>$V_{18}(10010), V_{2I}(10101)$    | 0.2472V <sub>dc</sub>          | 0.6472V <sub>dc</sub> | $0.1 V_{dc}$   |

| MV    | $V_{16}(10000), V_{29}(11101)$<br>$V_8(01000), V_{30}(11110)$<br>$V_4(00100), V_{15}(01111)$<br>$V_2(00010), V_{23}(10111)$<br>$V_1(00001), V_{27}(11011)$          | $0.4 \mathrm{V}_{\mathrm{dc}}$ | $0.4  m V_{dc}$       | $0.3 V_{dc}$   |

| LV    | $V_{25}(11001), V_{24}(11000)$<br>$V_{28}(11100), V_{12}(01100)$<br>$V_{14}(01110), V_{6}(00110)$<br>$V_{7}(00111), V_{3}(00011)$<br>$V_{19}(10011), V_{17}(10001)$ | 0.6472V <sub>dc</sub>          | 0.2472V <sub>dc</sub> | $0.1 V_{dc}$   |

# B. Common-Mode Voltage Analysis

The common-mode voltage (CMV) in a five-phase VSI is expressed as:

$$V_{CM} = V_{nQ} = V_{nN} - V_{dc} / 2$$

(5)

The absolute value of the CMV for each voltage vector group is:

$$|V_{CM}| = |V_{nN} - V_{dc} / 2| = \begin{cases} 0.5V_{dc} & \text{for zero vectors} \\ 0.1V_{dc} & \text{for small vectors} \\ 0.3V_{dc} & \text{for medium vectors} \\ 0.1V_{dc} & \text{for larger vectors} \end{cases}$$

(6)

From Table I, it can be clearly seen that the large voltage vector group provides the lowest CMV with the highest output voltage in the  $(\alpha-\beta)$  planes.

# C. Conventional MPCC Scheme

As shown in Fig. 1, the relationships between the output voltage and current of a five-phase VSI with an RL load in the  $(\alpha-\beta)$  and (x-y) planes are expressed as follows:

$$V_{\alpha\beta} = R\mathbf{i}_{\alpha\beta} + L\frac{d\mathbf{i}_{\alpha\beta}}{dt} \,, \tag{7}$$

$$V_{xy} = Ri_{xy} + L\frac{di_{xy}}{dt} \quad , \tag{8}$$

where  $i_{\alpha\beta}$  and  $V_{\alpha\beta}$  are the current and voltage vectors in the  $(\alpha-\beta)$  plane;  $i_{xy}$  and  $V_{xy}$  are current and voltage vectors in the (x-y) plane; and R and L are the load resistance and inductance, respectively.

The derivatives of the currents in (7) and (8) are approximated using a forward Euler approximation with a sampling period  $T_s$  as follows:

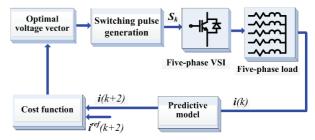

Fig. 3. Block diagram of the conventional MPCC scheme.

$$\frac{d\mathbf{i}_{\alpha\beta}}{dt} = \frac{\mathbf{i}_{\alpha\beta}(k+1) - \mathbf{i}_{\alpha\beta}(k)}{T_s} \tag{9}$$

$$\frac{d\mathbf{i}_{xy}}{dt} = \frac{\mathbf{i}_{xy}(k+1) - \mathbf{i}_{xy}(k)}{T_s}$$

(10)

By substituting (9) into (7) and (10) into (8), the relationship between the output voltage and current in the discrete-time domain can be obtained as follows:

$$\mathbf{i}_{\alpha\beta}(k+1) = \mathbf{i}_{\alpha\beta}(k) + \frac{T_s}{L}(V_{\alpha\beta}(k) - R\mathbf{i}_{\alpha\beta}(k))$$

(11)

$$\mathbf{i}_{xy}(k+1) = \mathbf{i}_{xy}(k) + \frac{T_s}{L}(V_{xy}(k) - R\mathbf{i}_{xy}(k))$$

(12)

A one-step delay compensation method is adopted to compensate for the time delay caused by the digital implementation, where the currents and voltages in (11) and (12) are shifted one step forward in time to obtain the currents at the instant (k+2), as in [18]:

$$\mathbf{i}_{\alpha\beta}(k+2) = \mathbf{i}_{\alpha\beta}(k+1) + \frac{T_s}{L}(V_{\alpha\beta}(k+1) - R\mathbf{i}_{\alpha\beta}(k+1))$$

(13)

$$\mathbf{i}_{xy}(k+2) = \mathbf{i}_{xy}(k+1) + \frac{T_s}{I}(V_{xy}(k+1) - R\mathbf{i}_{xy}(k+1))$$

(14)

In the MPCC for a five-phase VSI, four current components must be simultaneously controlled in two planes, and the cost function g is defined as follows:

$$g = |i_{\alpha}^{ref}(k+2) - i_{\alpha}(k+2)| + |i_{\beta}^{ref}(k+2) - i_{\beta}(k+2)| + \lambda_{xy}(|i_{x}^{ref}(k+2) - i_{x}(k+2)| + |i_{y}^{ref}(k+2) - i_{y}(k+2)|),$$

(15)

where  $i_{\alpha}$ ,  $i_{\beta}$ ,  $i_{x}$  and  $i_{y}$  are the  $\alpha$ ,  $\beta$ , x and y components of the current vector;  $i_{\alpha}^{ref}$ ,  $i_{\beta}^{ref}$ ,  $i_{x}^{ref}$  and  $i_{y}^{ref}$  are the  $\alpha$ ,  $\beta$ , x and y components of the reference current vector; and  $\lambda_{xy}$  is a weighting factor.

A block diagram of the conventional MPCC scheme for a five-phase VSI is shown in Fig. 3, where an optimal voltage vector that minimizes the cost function (15) is selected to drive a five-phase VSI. Since a larger number of current predictions and cost function evaluations are required to select the optimal voltage vector, the computation time of the MPCC scheme is high. Furthermore, only one voltage vector is applied during one sampling period. This means that the  $i_x$  and  $i_y$  currents cannot be eliminated. Thus, large low-order harmonics are inevitable in the output current.

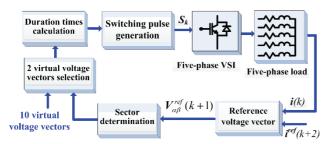

Fig. 4. Block diagram of the proposed MPCC scheme.

### III. PROPOSED MPCC SCHEME

In order to minimize the CMV and reduce the low-order current harmonics, 10 virtual voltage vectors with eliminated voltage components in the (x-y) sub-plane, which are synthesized from the voltage vectors of the LV group, are used as the input control set in the MPCC scheme. Then, two of the 10 virtual voltage vectors are applied throughout the whole sampling period to reduce the output current ripples. They are selected based on the location information of a reference voltage vector without current predictions. In addition, a new cost function is used to calculate the durations of the selected virtual voltage vectors. Therefore, the computational burden is significantly reduced. Fig. 4 shows a block diagram of the proposed MPCC scheme, which comprises three main parts: 1) the synthesized virtual vectors, 2) the selected virtual vectors and the calculation of their duration times, and 3) the generated switching pulse.

# A. Synthesized Virtual Vectors

In order to minimize CMV, 10 voltage vectors of the LV group with the lowest CMV and highest length in the  $(\alpha-\beta)$  plane are employed to construct the input control set of the proposed MPCC scheme. The input control set consists of 10 virtual voltage vectors, and each virtual voltage vector is obtained by combining three adjacent voltage vectors of the LV group to eliminate the x and y voltage components in order to reduce the low-order current harmonics.

For example, the virtual voltage vector  $V_{vl}$ , which is formed by a combination of voltage vectors  $V_{17}$ ,  $V_{25}$  and  $V_{24}$ , is expressed as:

$$V_{v1} = d_1 V_{17} + d_2 V_{25} + d_1 V_{24}$$

(16)

The factors  $d_1$  and  $d_2$  are calculated using the following constraint:

$$\begin{cases} d_1 V_{17xy} + d_2 V_{25xy} + d_1 V_{24xy} = \mathbf{0} \\ 2d_1 + d_2 = 1 \end{cases}$$

(17)

From (17), the factors  $d_1$  and  $d_2$  are given as follows:

$$\begin{cases}

d_1 = 0.381966 \\

d_2 = 0.236068

\end{cases}$$

(18)

By inserting (18) into (16), the virtual voltage vector  $V_{vl}$  is given as:

TABLE II Synthesized Virtual Voltage Vectors

| Virtual voltage vector    | Virtual voltage<br>vector synthesis    | $ V_{xy} $ | $ V_{\mathrm{CM}} $ |

|---------------------------|----------------------------------------|------------|---------------------|

| $V_{ m vl}$               | $d_1 V_{17} + d_2 V_{25} + d_1 V_{24}$ | 0          | $0.1 V_{dc}$        |

| $V_{ m v2}$               | $d_1 V_{25} + d_2 V_{24} + d_1 V_{28}$ | 0          | $0.1 V_{dc}$        |

| $V_{ m v3}$               | $d_1 V_{24} + d_2 V_{28} + d_1 V_{12}$ | 0          | $0.1 V_{dc}$        |

| $oldsymbol{V}_{	ext{v4}}$ | $d_1 V_{28} + d_2 V_{12} + d_1 V_{14}$ | 0          | $0.1 V_{dc}$        |

| $V_{ m v5}$               | $d_1 V_{12} + d_2 V_{14} + d_1 V_6$    | 0          | $0.1 V_{dc}$        |

| $oldsymbol{V}_{	ext{v6}}$ | $d_1 V_{14} + d_2 V_6 + d_1 V_7$       | 0          | $0.1 V_{dc}$        |

| $V_{ m v7}$               | $d_1 V_6 + d_2 V_7 + d_1 V_3$          | 0          | $0.1V_{dc}$         |

| $V_{ m v8}$               | $d_1 V_7 + d_2 V_3 + d_1 V_{19}$       | 0          | $0.1V_{dc}$         |

| $V_{ m v9}$               | $d_1 V_3 + d_2 V_{19} + d_1 V_{17}$    | 0          | $0.1V_{dc}$         |

| $V_{ m v10}$              | $d_1 V_{19} + d_2 V_{17} + d_1 V_{25}$ | 0          | $0.1 V_{dc}$        |

$$\begin{cases} V_{v1\alpha\beta} = d_1 V_{17\alpha\beta} + d_2 V_{25\alpha\beta} + d_1 V_{24\alpha\beta} = 0.5528 V_{dc} \angle 0^0 \\ V_{v1xy} = \mathbf{0} \end{cases}$$

(19)

The other virtual voltage vectors can be derived similarly based on the relationships presented in Table II. The 10 virtual voltage vectors have the minimum CMV as well as zero x and y voltage components. Therefore, the CMV is minimized and the  $i_x$ , and  $i_y$  currents are automatically nullified by employing these virtual voltage vectors as the input control set. As a result, the low-order current harmonics are significantly reduced and only the  $\alpha$  and  $\beta$  current components need to be controlled.

# B. Selected Virtual Vectors and Their Duration Time Calculation

By employing 10 virtual voltage vectors as the input control set, the low-order current harmonics are significantly reduced. However, if only a single virtual voltage vector is applied to drive a five-phase VSI, the output current ripples can remain high due to the absence of a zero voltage vector. In order to reduce the output current ripples, two virtual voltage vectors are selected to drive the five-phase VSI based on location information of the reference voltage vector. The reference voltage vector is obtained from the output current equation in (13):

$$V_{\alpha\beta}^{ref}(k+1) = \frac{L}{T_c} \boldsymbol{i}_{\alpha\beta}^{ref}(k+2) + \frac{R * T_s - L}{T_c} \boldsymbol{i}_{\alpha\beta}(k+1)$$

(20)

In the proposed MPCC scheme, the two virtual voltage vectors nearest the reference voltage vector are selected to drive the five-phase VSI. After calculating the reference voltage vector from (20), its location and the two virtual voltage vectors can be determined from the  $(\alpha-\beta)$  plane in Fig. 5, which is divided into 10 sectors.

For example, when the reference voltage vector is located in sector 1, the virtual voltage vectors  $V_{vl}$  and  $V_{v2}$  are selected to drive the five-phase VSI. Then, in order to calculate the duration time of  $V_{vl}$  and  $V_{v2}$ , a new cost function is defined as:

Fig. 5. Distributed virtual voltage vectors in the  $(\alpha-\beta)$  plane.

$$g_{new} = |V_{\alpha}^{ref}(k+1) - V_{v,\alpha}| + |V_{\beta}^{ref}(k+1) - V_{v,\beta}|,$$

(21)

where  $V_{\alpha}^{ref}$  and  $V_{\beta}^{ref}$  are the  $\alpha$  and  $\beta$  components of the reference voltage vector, while  $V_{i\alpha}$  and  $V_{i\beta}$  are the  $\alpha$  and  $\beta$  components of the virtual voltage vector i, respectively.

The cost function value in (21) of  $V_{v1}$  and  $V_{v2}$  is expressed as:

$$g_{new1} = \left| V_{\alpha}^{ref}(k+1) - V_{v1\alpha} \right| + \left| V_{\beta}^{ref}(k+1) - V_{v1\beta} \right|$$

$$g_{new2} = \left| V_{\alpha}^{ref}(k+1) - V_{v2\alpha} \right| + \left| V_{\beta}^{ref}(k+1) - V_{v2\beta} \right|$$

(22)

Then, the duration times of the two virtual voltage vectors, which are inversely proportional to their cost function values, are expressed as follows:

$$\begin{cases}

T_1 = g_{new2}T_s / (g_{new1} + g_{new2}) \\

T_2 = g_{new1}T_s / (g_{new1} + g_{new2})

\end{cases}$$

(23)

where  $T_1$  and  $T_2$  are the duration times of  $V_{vI}$  and  $V_{v2}$ , respectively.

It can be clearly seen that in the proposed scheme, the current predictions and weighting factor tuning are avoided and that the duration times of the selected virtual voltage vectors are calculated according to their cost function values. As a result, the computational burden is considerably reduced.

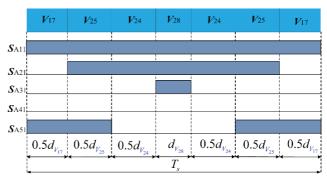

#### C. Generated Switching Pulse

After determining the two virtual voltage vectors, the corresponding switching pulses are required to drive the five-phase VSI. Typically, symmetrical switching pulses are adopted to reduce the output current harmonics [17]. To this end, the dwell times of the voltage vectors, which are used to synthesize the two selected virtual voltage vectors, must be determined. For example, when the virtual voltage vectors  $V_{VI}$  and  $V_{V2}$  are selected, the dwell times of the voltage vectors  $V_{17}$ ,  $V_{25}$ ,  $V_{24}$  and  $V_{28}$  are as follows:

$$\begin{cases}

d_{V_{17}} = d_1 T_1; d_{V_{25}} = d_2 T_1 + d_1 T_2; \\

d_{V_{24}} = d_1 T_1 + d_2 T_2; d_{V_{28}} = d_1 T_2;

\end{cases}$$

(24)

Fig. 6. Generated switching pulse in sector 1.

Fig. 7. Steady-state performance simulation of: (a) Conventional scheme, (b) Proposed scheme.

where  $d_{V17}$ ,  $d_{V25}$ ,  $d_{V24}$  and  $d_{V28}$  are the dwell times of the voltage vectors  $V_{17}$ ,  $V_{25}$ ,  $V_{24}$  and  $V_{28}$ , respectively. Fig. 6 shows the symmetrical switching pulses in sector 1, which are used to control the five-phase VSI.

Fig. 8. CMV waveform simulation of: (a) Conventional scheme, (b) Proposed scheme.

Fig. 9. Dynamic performance simulation of: (a) Conventional scheme, (b) Proposed scheme.

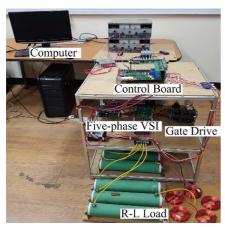

Fig. 10. Experimental system for a five-phase VSI.

# IV. SIMULATION RESULTS

Simulations were conducted using PSIM software to verify the effectiveness of the proposed MPCC scheme. The simulated parameters are as follows: the dc-link voltage Vdc is 120V; the R-L load has R = 13  $\Omega$  and L = 15 mH; the output frequency is 50 Hz; and the sampling period is 100us.

For the sake of simplicity, the conventional MPCC scheme directly evaluates 11 voltage vectors consisting of one zero voltage vector and 10 voltage vectors of the LV group with the cost function presented in (15).

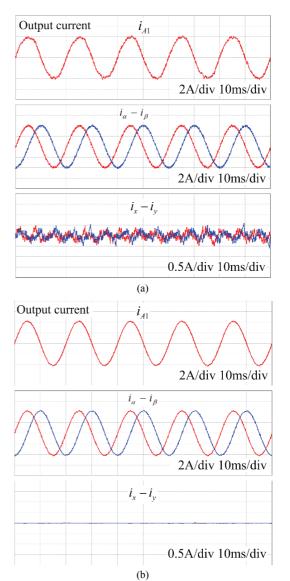

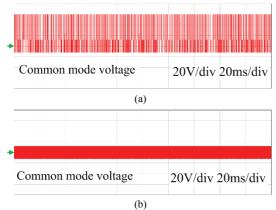

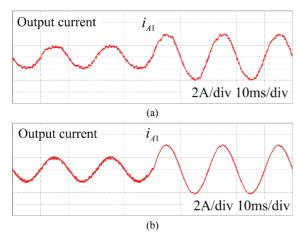

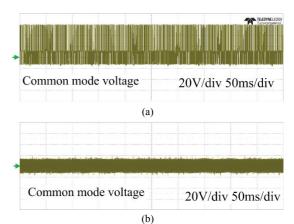

Fig. 7 shows the steady-state performances of the conventional and the proposed MPCC schemes when the amplitude of the reference current is 4A. From top to the bottom, the waveforms show the phase current i<sub>A1</sub> as well as the currents in the  $(\alpha-\beta)$  plane and (x-y) plane for both schemes. As shown in the figure, the currents in the  $(\alpha-\beta)$ plane are sinusoidal for both schemes. Meanwhile, the currents in the (x-y) plane of the proposed scheme are effectively eliminated by using virtual voltage vectors. Therefore, the phase current iA1 is sinusoidal with the proposed scheme. On the other hand, the phase current iA1 is distorted with the conventional scheme due to the large magnitudes of the x and y current components. In addition, CMV waveforms delivered by the two MPCC schemes are shown in Fig. 8. In the conventional scheme, the absolute peak value of the CMV is about 60V, which is 0.5V<sub>dc</sub>. Meanwhile, the absolute peak value of the CMV is reduced to 12V in the proposed scheme. This represents an 80% reduction in the absolute peak value of the CMV. In addition, Fig. 9 shows the dynamic performance when the amplitude of the reference current is suddenly changed from 2A to 4A. It can be clearly seen that the proposed scheme has a dynamic response that is similar to that of the conventional scheme.

## V. EXPERIMENTAL RESULTS

In order to validate the simulation results, a prototype of a five-phase VSI is implemented in the laboratory as shown in Fig. 10. The proposed scheme is realized using a DSP 32-bit floating-point TI TMS320F28335 and a CPLD Altera EPM7128SLC81-15. The parameters used in the experiment are the same as those used in the simulation.

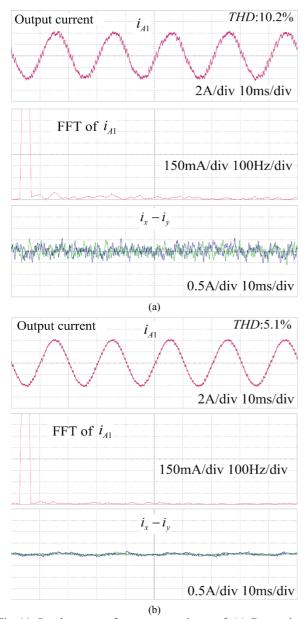

Fig. 11 shows experimental results of the conventional and the proposed MPCC schemes at the steady-state when the amplitude of the reference current is 4A. From top to bottom, the waveforms contain phase current iA1, its fast Fourier transform (FFT), and the x and y current components for both schemes. As shown in the figure, the x and y current components of the conventional scheme are substantially higher than those of the proposed scheme due to the fact that only one voltage vector is applied during the whole sampling period in the conventional scheme. As a result, the output current phase iA1 with the conventional scheme, which consists of high magnitude low-order harmonics (particularly third order), is seriously distorted. On the other hand, the output current phase iA1 is sinusoidal with the proposed scheme due to the utilization of two virtual voltage vectors in each sampling period. When compared with the conventional scheme, the total harmonic distortion (THD) of the output

Fig. 11. Steady-state performance experiment of: (a) Conventional scheme, (b) Proposed scheme.

current with the proposed scheme is effectively reduced. In addition, the CMV waveforms generated by the conventional and the proposed MPCC schemes are shown in Fig. 12. It can be seen that the proposed scheme reduced the absolute peak value by 80% when compared to the conventional scheme. This is attributed to the fact that only the voltage vectors of the LV group are used to construct the input control set in the proposed scheme.

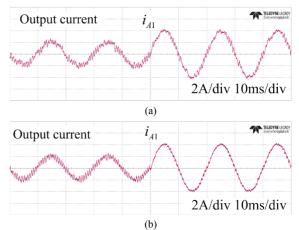

Fig. 13 shows experimental results for both of the MPCC schemes when the amplitude of the reference current instantly changes from 2A to 4A. It can be clearly seen that the dynamic performances of both schemes are similar. However, the proposed scheme provides lower current ripples. Furthermore, a computational cost comparison of two schemes is provided

Fig. 12. CMV waveform experiment of: (a) Conventional scheme, (b) Proposed scheme.

Fig. 13. Dynamic performance experiment of: (a) Conventional scheme, (b) Proposed scheme.

TABLE III

COMPUTATIONAL COST COMPARISON

| Parameters                                 | Conventional scheme | Proposed scheme |  |  |  |  |

|--------------------------------------------|---------------------|-----------------|--|--|--|--|

| Number of voltage vectors                  | 11                  | 10              |  |  |  |  |

| Number of current predictions calculations | 44( 44=11*4)        | 0               |  |  |  |  |

| Number of voltage reference calculations   | 0                   | 2(2=1*2)        |  |  |  |  |

| Number of cost function calculations       | 11                  | 2               |  |  |  |  |

| Computation time (us)                      | 31.5                | 22.4            |  |  |  |  |

in Table III. Since the proposed scheme eliminates current predictions and the duration times of selected virtual voltage vectors are determined according to their cost function values, the computation time is significantly reduced when compared to that of the conventional scheme, as presented in Table III.

### VI. CONCLUSION

This paper proposed an effective MPCC scheme to reduce the current harmonics and common-mode voltage (CMV) for a two-level five-phase voltage source inverter (VSI) without using a weighting factor. Since 10 virtual voltage vectors synthesized from the voltage vectors of the LV group are employed as the input control set of the proposed scheme, the absolute peak value of the CMV with the proposed scheme is reduced by 80% when compared to that of the conventional scheme. In the proposed scheme, two of the 10 virtual voltage vectors are selected based on location information of the reference voltage vector and are used to drive five-phase VSI. In addition, their duration times are calculated according to their cost function values. Therefore, the current harmonics and computational burden are considerably reduced. The effectiveness of the proposed scheme has been verified by the simulation and experimental results. When compared to the conventional scheme, the proposed scheme shows the same dynamic performance along with reductions in the current harmonics and computation time.

#### ACKNOWLEDGMENT

This work was supported by the National Research Foundation of Korea Grant funded by the Korean Government (NRF-2018R1D1A1A09081779).

### REFERENCES

- [1] G. Liu, Y. Yang, and Qian Chen, "Virtual signal injected MTPA control for DTC five-phase IPMSM drives," *J. Power Electron.*, Vol. 19, No. 4, pp.956-967, Jul. 2019.

- [2] X. Huang A. Goodman C. Gerada F. Youtong, and L. Qinfen "Design of a five-phase brushless DC motor for a safety critical aerospace application " *IEEE Trans. Ind. Electron.*, Vol. 59, No. 9 pp. 3532-3541, Sep. 2012.

- [3] F. Mekri S. B. Elghali, and M. E. H. Benbouzid "Fault-tolerant control performance comparison of three- and five-phase PMSG for marine current turbine applications" *IEEE Trans. Sustain. Energy*, Vol. 4, No. 2, pp. 425-433, Apr. 2013.

- [4] M. J. Duran, J. A. Riveros, f. barrero, h. guzman, and j. prieto, "reduction of common-mode voltage in five-phase induction motor drives using predictive control techniques," *IEEE Trans. Ind. Appl.*, Vol. 48, No. 6, pp. 2059-2067, Nov./Dec. 2012.

- [5] E. Levi, "Advances in Converter control and innovative exploitation of additional degrees of freedom for multiphase machines," *IEEE Trans. Ind. Electron.*, Vol. 63, No. 1, pp. 433-448, Jan. 2016.

- [6] Y. N. Tatte and M. V. Aware, "Torque ripple and harmonic current reduction in a three-level inverter-fed direct-torquecontrolled five-phase induction motor," *IEEE Trans. Ind. Electron.*, Vol. 64, No. 7, pp. 5265-5275, Jul. 2017.

- [7] J. Prieto, M. Jones, F. Barrero, E. Levi, and S. Toral, "Comparative analysis of discontinuous and continuous PWM techniques in VSI-fed five-phase induction motor," *IEEE Trans. Ind. Electron.*, Vol. 58, No. 12, pp. 5324-5335, Dec. 2011.

- [8] W. Xiong, Y. Sun, M. Su, J. Zhang, Y. Liu, and J. Yang, "Carrier-based modulation strategies with reduced common-

- mode voltage for five-phase voltage source inverters," *IEEE Trans. Power Electron.*, Vol. 33, No. 3, pp. 2381-2394, Mar 2018

- [9] A. Iqbal, H. Abu-Rub, P. Cortes, and J. Rodriguez, "Finite control set model predictive current control of a five-phase voltage source inverter," in *IEEE International Conference* on *Industrial Technology (ICIT)*, pp. 1787-1792, 2010.

- [10] P. Cortés, L. Vattuone, J. Rodriguez, and M. Duran, "A method of predictive current control with reduced number of calculations for five-phase voltage source inverters," in 35th Annual Conference of IEEE Industrial Electronics (IECON), pp. 53-58, 2009.

- [11] H. Guzman, F. Barrero, and M. J. Duran, "IGBT-gating failure effect on a fault-tolerant predictive current-controlled fivephase induction motor drive," *IEEE Trans. Ind. Electron.*, Vol. 62, No. 1, pp. 15-20, Jan. 2015.

- [12] X. Wang, J. Zhao, Q. Wang, G. Li, and M. Zhang, "Fast FCS-MPC-based SVPWM method to reduce switching states of multilevel cascaded H-bridge STATCOMs," J. Power Electron., Vol. 19, No. 1, pp.244-253, Jan. 2019.

- [13] Q. Tran and H. Lee, "An advanced modulation strategy for three-to-five-phase indirect matrix converters to reduce common-mode voltage with enhanced output performance," *IEEE Trans. Ind. Electron.*, Vol. 65, No. 7, pp. 5282-5291, Jul. 2018.

- [14] Q. Tran and H. Lee, "A new SVM method to reduce common-mode voltage of five-leg indirect matrix converter fed open-end load drives," *J. Power Electron.*, Vol. 17, No. 3, pp.641-652, May 2017.

- [15] S. M. Dabour, A. S. Abdel-Khalik, S. Ahmed, and A. Massoud, "Model-predictive control for common-mode voltage reduction and third-harmonic current injection techniques with five-phase inverters," in *Nineteenth International Middle East Power Systems Conference (MEPCON)*, pp. 1310-1315, 2017.

- [16] A. Iqbal, R. Alammari, M. Mosa and H. Abu-Rub, "Finite set model predictive current control with reduced and constant common mode voltage for a five-phase voltage source inverter," in *IEEE 23rd International Symposium on Industrial Electronics (ISIE)*, pp. 479-484, 2014.

- [17] C. Xue, W. Song, and X. Feng, "Finite control-set model predictive current control of five-phase permanent-magnet synchronous machine based on virtual voltage vectors," *IET Electric Power Appl.*, Vol. 11, No. 5, pp. 836-846, 2017.

- [18] P. Cortes, J. Rodriguez, C. Silva, and A. Flores, "Delay compensation in model predictive current control of a three-phase inverter," *IEEE Trans. Ind. Electron.*, Vol. 59, No. 2, pp. 1323-1325, Feb. 2012.

**Huu-Cong Vu** was born in Hai Duong Province, Vietnam, in 1990. He received his B.S. degree in Control and Automation Engineering from the Hanoi University of Science and Technology, Hanoi, Vietnam, in 2013. He is presently working towards his Ph.D. degree in the School of Electrical Engineering, University of Ulsan, Ulsan,

Korea. His current research interests include AC-AC converters, DC-AC inverters, pulse-width modulation and control techniques.

Hong-Hee Lee received his B.S., M.S. and Ph.D. degrees in Electrical Engineering from Seoul National University, Seoul, Korea, in 1980, 1982 and 1990, respectively. From 1994 to 1995, he was a Visiting Professor at Texas A&M University, College Station, TX, USA. Since 1985, he has been with the Department of Electrical Engineering,

University of Ulsan, Ulsan, Korea, where he is presently working as a Professor in the School of Electrical Engineering. He was also the Director of the Network-based Automation Research Center (NARC), which is sponsored by the Ministry of Trade, Industry and Energy. His current research interests include power electronics, network-based motor control and renewable energy. Dr. Lee is a Member of the Institute of Electrical and Electronics (ERE), the Korean Institute of Power Electronics (KIPE), the Korean Institute of Electrical Engineers (KIEE), and the Institute of Control, Robotics and Systems (ICROS). He was the President of KIPE in 2014.