JPE 19-6-11

https://doi.org/10.6113/JPE.2019.19.6.1458 ISSN(Print): 1598-2092 / ISSN(Online): 2093-4718

# Implementation of Cuckoo Search Optimized Firing Scheme in 5-Level Cascaded H-Bridge Multilevel Inverter for Power Quality Improvement

Deepshikha Singla\* and P.R.Sharma†

†,\*Department of Electrical Engineering, YMCA University of Science and Technology, Faridabad, India

#### **Abstract**

Multilevel inverters have appeared as a successful and utilitarian solution in many power applications. The prime objective of an inverter is to keep the fundamental component of the output voltage of a multilevel inverter at a preferred value. Equally important is the need to keep the harmonic components in the output voltage within stated harmonic limits. Therefore, the basis of this research is to develop a harmonic minimization function that optimizes the switching angles of cascaded H-bridge multilevel inverter. Due to benefits of the Cuckoo Search (CS) algorithm, it is applied to determine the switching angles, which are further used to generate the switching pattern for firing the H-bridges of multilevel inverter. Simulation results are compared with SPWM based firing scheme. The switching frequency for SPWM firing scheme is taken as 200 Hz since the switching losses are increased when switching frequency is high. To validate the ability of Cuckoo Search optimized firing scheme in minimization of harmonics, experimental results obtained from hardware prototype of Five Level Cascaded H-Bridge Multilevel Inverter equipped with a FPGA controller are presented to verify the simulation results.

**Key words:** Cascaded H-Bridge multilevel inverters, Cuckoo Search (CS) algorithm, Harmonic minimization, Power quality, Sinusoidal Pulse Width Modulation (SPWM)

#### I. Introduction

Nowadays, almost every domestic and industrial load is sensitive to power quality problems. Thus, there is an increased need for a low harmonics source. Multilevel inverters [1], [2] have appeared as a successful and pragmatic solution in the various power applications. Among the existing multilevel inverter topologies, the Cascaded H-bridge Multilevel Inverter (CHMLI) [3], [4] has caught the most attention due to its characteristic feature of producing a staircase voltage output with 'M' steps from an arrangement association of (M-1)/2 control units provided from separate dc inputs. With an increase in the number of units of multilevel inverter, the output resembles a near sinusoidal output voltage. This impressive feature results in better power quality, reduced dv/dt stresses, minimum total harmonic distortion (THD),

improved electromagnetic compatibility (EMC), reduced switching losses, and higher-voltage capability. It can also lead to elimination of the coupling transformer, which results in a reduction in costs. However, the performance of multilevel inverters depends on the firing scheme employed for creating the switching pattern for its H-bridges so the harmonics are reduced and power quality of the system is enhanced.

Sinusoidal-PWM (SPWM) [5]-[7] methods are the most commonly used methods for generating a switching pattern by employing a switching frequency in the order of kHz. However, the higher the switching frequency, the greater the switching loss. Selective Harmonic Elimination [8]-[10] technique has replaced the traditional PWM technique to a great extent in harmonic minimization problems. It refers to choosing switching angles so that the specific higher order harmonics such as the 5th, 7th, 11th and 13th are minimized from the output voltage of the inverter. Optimal Minimization of THD (OMTHD) [11] is another well-known method that focuses on minimization of THD. However, the prime objective of an inverter is to keep the fundamental component of the output voltage of multilevel inverter at a desired value.

Manuscript received Dec. 18, 2018; accepted Jun. 21, 2019 Recommended for publication by Associate Editor S. Padmanaban.

<sup>&</sup>lt;sup>†</sup>Corresponding Author: deepshikha\_16s@yahoo.com

Tel: +917988720847, YMCA University of Science and Technology

<sup>\*</sup>Dept. of Electr. Eng., YMCA Univ. of Science and Technology, India

Equally important, is the need to keep the harmonic components in the output voltage within specified harmonic limits. Therefore, the basic idea of this study is to develop a harmonic minimization function that optimizes the switching angles of a multilevel inverter. Afterwards, choosing an appropriate optimization search algorithm is as important as framing a well-defined optimization problem.

Nowadays, various optimization algorithms are being explored to solve the harmonic minimization problem. A number of research papers discuss the application of Genetic Algorithm (GA) [12], [13], Particle Swarming Optimization (PSO) [14]-[16], Simulated Annealing (SA) [17], and numerous other algorithms [18]-[20]. The benefits of these optimization algorithms are utilized in solving different harmonic minimization problems to obtain a particular switching pattern for the H-bridges of multilevel inverter. This is done in a manner to achieve a minimum THD and a better quality waveform. Each of these algorithms has its own pros and cons and area of application where it benefits the most. However, GA seems to be the most explored optimization technique, in spite of the fact that it involves multiple operations such as crossover, mutation, etc. for a single iteration, which makes it one of the longest techniques. Moreover, most optimization algorithms require tuning of their internal parameters to achieve good performance, which adds to their simulation times. Thus, considering the simplicity and efficiency of the Cuckoo Search [21]-[25] algorithm for solving highly non-linear optimization problems in real-world engineering applications, this research study utilized Cuckoo Search optimization for the power quality improvement of multilevel inverter. Simulation results of a Cuckoo Search optimization based firing scheme employed to a five level cascaded H-bridge multilevel inverter are compared with results obtained using a SPWM based firing scheme. This study implements a hardware prototype of a FPGA controlled five level cascaded H-bridge multilevel inverter for validation of these simulation results.

# II. HARMONIC MINIMIZATION IN CASCADED H-BRIDGE MULTILEVEL INVERTERS

In this paper, a three-phase cascaded H-bridge configuration of multilevel inverter is used to evaluate the effectiveness of the proposed method. An m-level cascaded H-bridge inverter comprises of a series combination of five H-bridges with separate dc inputs as  $V_{dc1}$ ,  $V_{dc2}$ ,  $V_{dc3}$ , .... $V_{dcm}$ . If the H-bridges of multilevel inverter are fired by the switching pattern generated using the switching angles  $\alpha_1$ ,  $\alpha_2$ ,  $\alpha_3$ , .... $\alpha_m$ , the output voltage of multilevel inverter [8] can be expressed in terms of Fourier series expansion as follows:

$$\begin{split} V(t) = \sum\nolimits_{n=1,3,5}^{\infty} \frac{{}_{4}V_{dc}}{n\pi} (\cos n\alpha_{1} + \cos n\alpha_{2} + ... + \\ \cos n\alpha_{m}) \sin n\alpha_{n} \end{split} \tag{1} \label{eq:Vt}$$

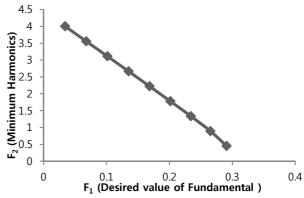

Fig. 1. Graphical representation of two objective functions.

Due to the odd quarter-wave symmetric characteristic, even order harmonics become zero. Meanwhile, considering the line voltage, triplen harmonics do not need to be considered.

Therefore, the THD [8] of the line voltage can be expressed as follows:

Line Voltage THD =

$$\frac{\sqrt{\sum_{n=5,7,11,13,...}^{\infty}V_{n}^{2}}}{V_{1}}*100$$

(2)

where nth component can be written as:

$$V_{n} = \frac{4V_{dc}}{n\pi} (\cos n\alpha_{1} + \cos n\alpha_{2} + ... + \cos n\alpha_{m})$$

The prime objective of an inverter is to keep the fundamental component of the output voltage of multilevel inverter at a desired value. However, equally important is the need to keep the harmonic components in the output voltage within specified harmonic limits. Therefore, a minimization function is developed to obtain the optimized switching angles for generating a switching pattern for firing the H-bridges of multilevel inverter so that both the objectives are achieved.

The objective function to be minimized is framed as follows:

$$F(\alpha_{1}, \alpha_{2}, ..., \alpha_{m}) = W_{1} \times \left(1 - \frac{V_{1}}{V_{1 \text{max}}}\right)^{4} + W_{2} \times \sum_{n=5,7,11,...}^{49} \left(\frac{V_{n}}{V_{1 \text{max}}}\right)^{2}$$

(3)

The condition to obtain a staircase waveform is that the switching angles should be within zero and  $\pi/2$  (0 <  $\alpha_1 < \alpha_2 < .... < \alpha_m < \pi/2$ ). The weights  $W_1$  and  $W_2$  are set so that their sum is unity. To determine the optimum weights  $W_1$  and  $W_2$ , two-objective functions are geometrically represented for different combinations of weights as given in Fig. 1. Then a set of weights is chosen so that the minimum value of the objective function, as sum of two functions, is found.

There is a wide range of algorithms available for resolving different types of optimization problems. Therefore, after selecting the optimum weights, the function is optimized using an optimization algorithm. There are many limitations to commonly used swarm intelligence techniques such as getting trapped at local mid-optimum points. In addition, GA requires selection of too many parameters. So, there is a need for an optimization algorithm that works efficiently with a minimum of parameters.

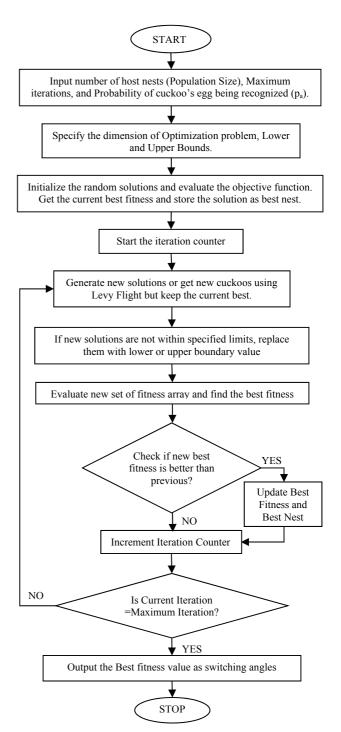

# III. CUCKOO SEARCH OPTIMIZATION BASED SWITCHING SCHEME

Cuckoo search is a heuristic approach, proposed in 2009 by Xin-she Yang and Suash Deb [20], used for solving optimization problems in different fields of engineering. The number of parameters to be tuned is much smaller than other algorithms such as GA and PSO. Hence, it is possibly more capable for a wide class of the optimization procedures. The algorithm is inspired by the behavior of cuckoo birds, also known as brood parasites, that never build their own nest and lays their eggs in the nests of other host birds (of different species). Eggs in a nest represent solutions, whereas an egg of a cuckoo bird is a new solution. Normally, a cuckoo lays one egg at a time in a randomly chosen nest. The number of host nests is fixed. So, each nest has one cuckoo bird egg and remaining eggs are from the host bird. Sometimes, host birds get involved into direct conflicts with intruding cuckoos. If the host bird recognizes an egg as someone else's, they either throw it out of the nest or move to build a new nest. The probability of cuckoo's egg being recognized is pa, and is generally fixed at 25% [21], [24]. However, if a cuckoo's egg matures, it moves to the next generation. The ability of the algorithm to maintain a balance between local and global random walks using switching parameter makes it suitable for global optimization problems. A flowchart for the optimizing switching angles being used to generate a switching pattern using Cuckoo Search is given in Fig. 2.

### IV. EXPERIMENTAL RESULTS AND DISCUSSION

In this paper, Cuckoo Search Algorithm is employed for the optimization of switching angles to obtain minimum harmonics and better power quality. The proposed method is implemented by developing code in the MATLAB programming environment. The obtained results are further used in SIMULINK model to observe various power quality related parameters and FFT analysis. The simulation results are validated experimentally with Five-Level CHMLI setup equipped with a FPGA controller. Different case studies are performed to substantiate the effectiveness of the Cuckoo Search Algorithm for the power quality improvement of CHMLIs.

# A. Implementation and Performance of Cuckoo Search Optimization for Harmonic Minimization

A model of Five-Level CHMLI is developed in MATLAB/ Simulink software and the switching angles to fire the H-bridges

Fig. 2. Algorithm for Cuckoo Search Optimized Switching Scheme.

of Inverter are acquired using the developed harmonic minimization function. The objective function is minimized by applying Cuckoo Search Optimization algorithm. The parameters for the population size, maximum iterations and number of runs are taken as 25, 100 and 10. The angles are found to be same, i.e.  $\alpha_1$ =7.63 and  $\alpha_2$ =24.52 in every run.

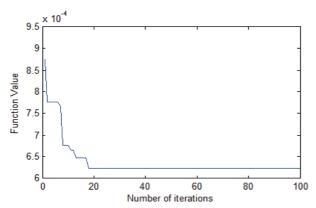

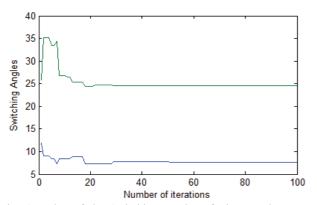

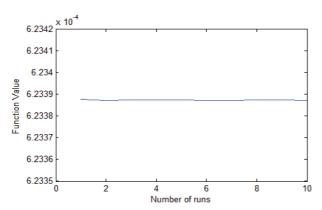

The value of minimization function and the optimized switching angles of five-level inverter are plotted with

Fig. 3. Value of the minimization function with different iterations.

Fig. 4. Value of the Switching Angles of Five-Level Inverter with different numbers of iterations.

Fig. 5. Optimized Function value at different runs.

different numbers of iterations in Fig. 3 and Fig. 4, respectively. The function value during each run is same as shown in Fig. 5, therefore, the effectiveness of this algorithm is confirmed. The computational time taken by the algorithm to determine results, i.e. the switching angles is  $0.7 \sim 0.9$ s only for 100 iterations in one run.

B. Simulation and Analysis of Five-Level Cascaded H-Bridge Inverter using SPWM Firing Scheme and Cuckoo Search Optimized Firing Scheme

Since the results of Cuckoo Search Optimization algorithm

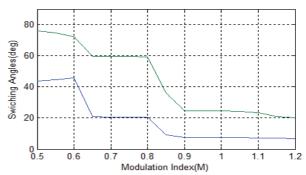

Fig. 6. Optimized value of Switching Angles at different values of the modulation index.

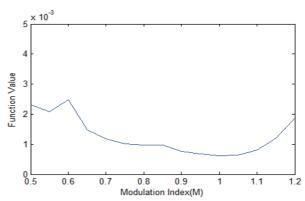

Fig. 7. Optimized Function Value at different value of Modulation Index.

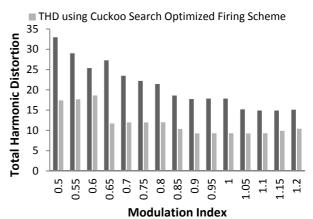

## ■ THD using SPWM Firing Scheme

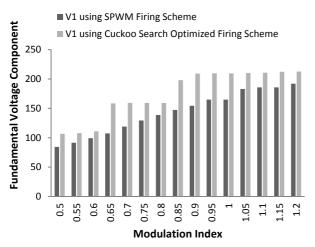

Fig. 8. Line Voltage THD using two firing schemes at different values of Modulation Index.

are same on every run, only a single run is considered for further study. The program is executed for different modulation indexes, and the optimum values of switching angles for five-level inverter are obtained and plotted in Fig. 6.

In addition, the function value with respect to the modulation index is shown in Fig. 7. The step size here is taken as 0.05. From this figure, it can be seen that the function value at every modulation index lies within  $10^{-3}$  to  $10^{-4}$ . Thus, the algorithm is efficient in optimizing the

Fig. 9. Fundamental Voltage using two firing schemes at different values of Modulation Index.

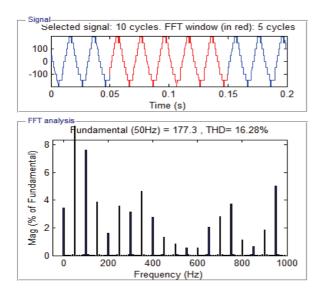

Fig. 10. FFT Analysis of Five-Level Inverter using SPWM Firing Scheme.

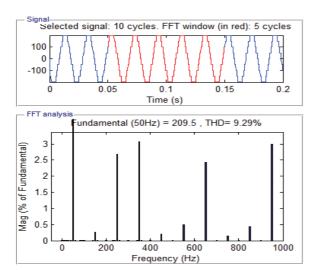

Fig. 11. FFT Analysis of Five –Level Inverter using Cuckoo Search Optimized Firing Scheme.

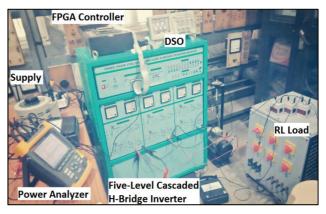

Fig. 12. Hardware prototype of FPGA Controlled Five –Level Cascaded H-Bridge Inverter.

switching angles for minimum harmonics.

Different power quality related parameters such as THD and fundamental voltage values are observed. A comparison between Cuckoo Search optimized firing scheme and SPWM firing scheme is made based on these parameters. Graphical representations shown in Fig. 8 and Fig. 9 summarizes the comparison and verify the effectiveness of Cuckoo Search as THD is minimized and the fundamental voltage component is enhanced near the desired value for all of the values of modulation index. The model of Five-level inverter is simulated at m=1 using both schemes and FFT analysis is presented in Fig. 10 and 11. It can be clearly seen from the FFT analysis that THD is minimized from 16.28% with SPWM Firing Scheme and 9.29% with Cuckoo Search Optimized Firing Scheme. Also, the even-order and other inadequate harmonics are minimized.

## C. Experimental Validation of FPGA Controlled Five-Level Cascaded H-Bridge Inverter

For the validation of simulation results, a hardware prototype of FPGA controller based three-phase five-level cascaded H-bridge inverter has been setup as shown in Fig. 12. A single-phase autotransformer is connected to six separate isolation transformers and rectifiers to generate six isolated DC supply for six H-bridges in the three phases of inverter. A Xilinx Spartan-6 FPGA controller is programmed to drive the gates of H-bridges using switching pattern obtained from both of the firing schemes. As switching losses are more when the switching frequency is high, and the major focus of this research is on power quality improvement, so the switching frequency for SPWM firing scheme is taken as 200 Hz. A non-linear star-connected load with  $300 \Omega$ , 40 mH in each phase is connected to the inverter.

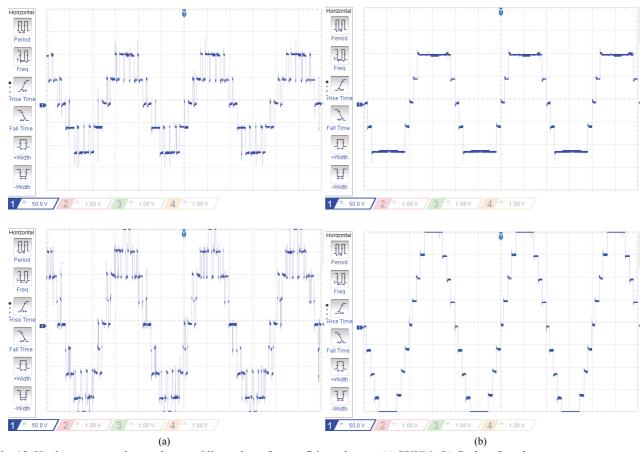

All the simulations and implementations are done at m=1. Experimental results of the output phase and line voltages for SPWM firing scheme and Cuckoo Search optimization based firing scheme are obtained from DSO and are shown in Fig. 13. It can be clearly seen from these figures that the waveforms obtained using Cuckoo Search optimization based firing scheme

Fig. 13. Hardware output phase voltage and line voltage for two firing schemes. (a) SPWM. (b) Cuckoo Search.

Fig. 14. Voltage and Harmonic graphs obtained from Hardware using SPWM and Cuckoo Search optimization based firing schemes.

$\label{eq:table_interpolation} TABLE\ I$  Voltage, Current and Power at the Input and Output

|                                   |                                       | SPWM Scheme | Proposed Scheme |

|-----------------------------------|---------------------------------------|-------------|-----------------|

|                                   | $V_{RMS}(V)$ 85<br>S $I_{RMS}(A)$ 1.2 | 85          | 85              |

| Input Side Readings               |                                       | 1.2         | 1.6             |

|                                   | $P_{IN}(W)$                           | 65          | 90              |

|                                   | $V_{RMS}(V)$                          | 74          | 85              |

| Output Side Readings / phase      | $I_{RMS}(A)$                          | 0.2         | 0.3             |

|                                   | $P_{IN}(W)$                           | 13.5        | 25              |

| Total Output P <sub>OUT</sub> (W) |                                       | 40.5        | 75              |

| Apparent Power (VA)               |                                       | 44.4        | 76.5            |

| Reactive Power (VAR)              |                                       | 6.06        | 5.07            |

TABLE II

COMPARISON BETWEEN HARDWARE RESULTS OBTAINED USING SPWM AND CS OPTIMIZED FIRING SCHEMES

| S.No. | Factors that assess Power<br>Quality | Measured Parameters        | SPWM Based Firing Scheme | Cuckoo Search based<br>Optimization Scheme |

|-------|--------------------------------------|----------------------------|--------------------------|--------------------------------------------|

| 1     | THD                                  | Phase Voltage THD          | 27.5%                    | 23.1%                                      |

|       |                                      | Current THD                | 22.1%                    | 21.7%                                      |

|       |                                      | Line Voltage THD           | 25.3%                    | 7.9%                                       |

| 2     | RMS Value                            | RMS Value of Fundamental   | 123.2 V                  | 156.0 V                                    |

| 3     | Peak Value                           | Peak value of Line Voltage | 210.1 V                  | 214 V                                      |

| 4     | Crest Factor                         | CF                         | 1.70                     | 1.37                                       |

| 5     | Even Order Harmonics                 | 2 <sup>nd</sup> Harmonic   | 0.6%                     | 0                                          |

|       |                                      | 4 <sup>th</sup> Harmonic   | 0.3%                     | 0                                          |

|       |                                      | 6 <sup>th</sup> Harmonic   | 0.3%                     | 0                                          |

|       |                                      | 8 <sup>th</sup> Harmonic   | 0.4%                     | 0                                          |

|       |                                      | 10 <sup>th</sup> Harmonic  | 0.6%                     | 0                                          |

|       |                                      | 12 <sup>th</sup> Harmonic  | 0.5%                     | 0                                          |

|       |                                      | 14th Harmonic              | 0.3%                     | 0                                          |

|       |                                      | 16th Harmonic              | 0.7%                     | 0                                          |

|       |                                      | 18th Harmonic              | 0.5%                     | 0                                          |

| 6     | Lower Order Harmonics or             | 3 <sup>rd</sup> Harmonic   | 0.5%                     | 0.6                                        |

|       | Distortion Factor                    | 5 <sup>th</sup> Harmonic   | 0.5%                     | 2.1                                        |

|       |                                      | 7 <sup>th</sup> Harmonic   | 3.9%                     | 3.4                                        |

|       |                                      | 9 <sup>th</sup> Harmonic   | 12.1%                    | 0                                          |

|       |                                      | 11th Harmonic              | 0.3%                     | 0.4                                        |

|       |                                      | 13 <sup>th</sup> Harmonic  | 9.7%                     | 2.4                                        |

|       |                                      | 15 <sup>th</sup> Harmonic  | 9.8%                     | 0                                          |

|       |                                      | 17 <sup>th</sup> Harmonic  | 0.5%                     | 0.3                                        |

|       |                                      | 19th Harmonic              | 1.3%                     | 3.1                                        |

| 7     | Reactive Power                       | Q (VAR)                    | 6.06                     | 5.07                                       |

| 8     | Power Factor                         | PF                         | 0.91                     | 0.98                                       |

| 9     | Power Loss                           | Input-Output (W)           | 24.5                     | 15                                         |

| 10    | Efficiency                           | η (%)                      | 62.3                     | 83.3                                       |

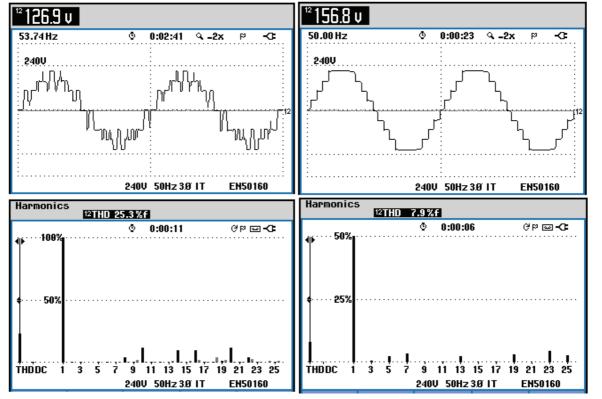

are much better than those obtained with SPWM firing scheme. A THD analysis is done using power analyzer, line voltage waveforms and Harmonic graphs for both the firing schemes are shown in Fig. 14. The obtained experimental results support the simulation since they are found to be comparable to the simulated results shown in Fig. 11. To provide a clear vision of the power quality, a detailed analysis and comparison of the power quality assessment of SPWM

and proposed CS Optimized firing scheme is done.

Observations made using an ammeter, voltmeter and wattmeter connected to the hardware setup are shown in Table I. These values are further used to calculate active power, apparent power, reactive power, power factor, power loss, and efficiency. For better understanding, a comparison between experimental results obtained using SPWM Firing Scheme and CS Optimized Firing Scheme is presented in

Table II.

From the tabulated results, it can be seen that THD of the line voltage is measured as 7.9% using CS optimization based firing scheme whereas it is 25.3% using SPWM firing scheme. Also, all the power quality parameters, other than harmonics, such as the reactive power drawn by the circuit, power factor, and efficiency of multilevel inverter have improved. Thus, it is obvious that the proposed method is efficient in improving the power quality and minimizing the harmonics.

#### V. CONCLUSIONS

In this paper, a minimization function is developed as the weighted sum of two main objectives, i.e. minimum harmonics and desired value of fundamental voltage output, so as to obtain the optimized switching angles for generating the switching pattern for firing H-bridges of multilevel inverter. The observed results verify the efficiency of Cuckoo Search algorithm based optimization in determining the optimum switching angles. Since there is only a single parameter  $\rho_a$  required in Cuckoo Search, apart from the population size, it is easy to implement. This paper presents a SPWM based firing scheme with a reduced switching frequency equal to 200Hz and Cuckoo Search optimization based firing scheme, to generate switching pattern for firing the H-bridges of five-level cascaded H-bridge inverter. Simulations have been carried out in MATLAB/Simulink with a nonlinear load, and a comparison on the basis of different performance parameters has been done. At all of the values of modulation index, THD and fundamental voltage component are observed to be better with CS optimized firing scheme. A FFT analysis confirms that the even order harmonics are zero and that the other lower order harmonics are controlled within allowable limits to comply with IEEE 519-1992 harmonic guidelines. The computational time required for determining the switching angles is only 0.7~ 0.9s. The algorithm can be easily implemented for an inverter with any number of levels. Experimental results obtained with hardware prototype are presented for validation of simulation results. The two firing schemes are implemented experimentally and the obtained voltage waveform and THD analysis results are found to be similar to the simulation results in both cases. The power factor has been increased from 0.91 to 0.98 and the efficiency has improved by 20%. Hence, it is confirmed that CS optimized switching scheme provides a better switching pattern to achieve the minimum THD and a better quality voltage output.

#### REFERENCES

[1] J. S. Lai and F. Z. Peng, "Multilevel converters – A new breed of power converters," *IEEE Trans. Ind. Appl.*, Vol.

- 32, No. 3, pp. 509-517, May/Jun. 1996.

- [2] J. Rodriguez, J. S. Lai, and F. Z. Peng, "Multilevel inverters: a survey of topologies, controls, and applications," *IEEE Trans. Ind. Electron.*, Vol. 49, No. 4, pp. 724-738, Aug. 2002.

- [3] M. Malinowski, K. Gopakumar, J. Rodriguez, and M. A. Perez "A survey on cascaded multilevel inverters," *IEEE Trans. Ind. Electron.*, Vol. 57, No. 7, pp. 2197-2206, Jul. 2010

- [4] F. Z. Peng and Q. Z. Ming, "Applications of cascaded multilevel inverters," *J. Zhejiang Univ.- SCIENCE A*, Vol. 4, No. 6, pp. 658-665, Nov. 2003.

- [5] B. P. McGrath and D. G. Holmes, "Multicarrier PWM strategies for multilevel inverters," *IEEE Trans. Ind. Electron.*, Vol. 49, No. 4, pp. 858-867, Aug. 2002.

- [6] S. S. Dash, P. Palanivel, and S. Premalatha, "Performance analysis of multilevel inverters using variable switching frequency carrier based PWM techniques," *Renew. Energy Power Quality J.*, Vol. 10, Mar. 2012.

- [7] O. A. Lysenko and I. Y. Marchinskiy, "The study of five-level inverters with the various PWM," in *Proceedings* of Electronic and Networking Technologies (MWENT), Moscow IEEE Workshop, pp. 1-5, Mar. 2018.

- [8] J. Kumar, B. Das, and P. Agarwal, "Harmonic reduction technique for a cascade multilevel inverter," *Int. J. Recent Trends in Eng.*, Vol. 1, No. 3, pp.181-185, 2009.

- [9] J. Napoles, A. J. Watson, J. J. Padilla, J. I. Leon, L. G. Franquelo, P. W. Wheeler, and M. A. Aguirre, "Selective harmonic mitigation technique for cascaded H-bridge converters with nonequal DC link voltages," *IEEE Trans. Ind. Electron.*, Vol. 60, No. 5, pp. 1963-1971, May 2013

- [10] D. Kumar and P. Kaur, "Selective harmonic elimination PWM technique implementation for a multilevel converter," *Int. J. Eng. Res.*, Vol. 4, No. 6, pp. 303-308, Jun. 2015.

- [11] H. Toodeji, "An improved OMTHD technique for an n-level cascaded multilevel inverter with adjustable DC sources," *Turkish J. Electr. Eng. Comput. Sci.*, Vol. 25, pp. 4841-4853, Dec. 2017.

- [12] B. Ozpineci B, L. Tolbert, and J. Chiasson, "Harmonic optimization of multilevel converters using genetic algorithms," *IEEE Power Electronics Lett.*, Vol. 3, No. 3, pp. 92-95, Jun. 2005.

- [13] A. Salami and B. Bayat, "Total harmonic distortion minimization of multilevel converters using genetic algorithms," *Applied Mathematics*, Vol. 4, No. 7, pp. 1023-1027, Jun. 2013.

- [14] R. Mohanty, S. Rath, and S. P. Mishra, "Comparison study of harmonic elimination in cascade multilevel inverter using particle swarm optimization and genetic algorithm," *IOSR J. Electr. Electron. Eng.*, Vol. 5, No. 1, pp. 43-49, Mar. 2013.

- [15] M. Mythili and N. Kayalvizhi, "Comparison of GA and PSO algorithms in cascaded multilevel inverter using selective harmonic elimination PWM technique," *Int. J. Adv. Res. Electr.*, *Electron. Instrum. Eng.*, Vol. 3, No. 4, pp. 8621-8628, Apr. 2014.

- [16] V. K. Gupta and R. Mahanty, "Optimized switching scheme of cascaded H-bridge multilevel inverter using PSO," *Int. J. Electr. Power Energy Syst.*, Vol. 64, pp. 699-

- 707, Jan. 2015.

- [17] N. Vinothkumar, V. K. Chinnaiyan, M. Pradisha, and S. P. Karthikeyana, "Simulated annealing based selective harmonic elimination for multi-level inverter," *Energy Procedia*, Vol. 117, pp. 855-861, Jun. 2017.

- [18] T. Gajpal and N. Hedau, "A comparative survey on harmonic optimization of multilevel inverter," *Imperial J. Interdisciplinary Res.*, Vol. 2, No. 9, Aug. 2016.

- [19] V. J. Manohar, M. Trinad, and K. V. Ramana, "Comparative analysis of NR and TBLO algorithms in control of cascaded MLI at low switching frequency," in *Proc. Procedia Computer Science*, Vol. 85, pp. 976-986, Jan. 2016.

- [20] J. Olamaei and M. Karimi, "THD minimization in multilevel inverters using teaching-learning-based optimization algorithm," *Int. J. Ambient Energy*, Vol. 39, No. 11, pp. 1-9, Feb. 2017.

- [21] X. S. Yang and S. Deb, "Cuckoo search via Lévy flights," *IEEE World Congress on Nature & Biologically Inspired Computing* (NaBIC), pp. 210-214, 2009.

- [22] A. H. Gandomi, X. S. Yang, and A. H. Alavi, "Cuckoo search algorithm: A metaheuristic approach to solve structural optimization problems," *Engineering with Computers*, Vol. 29, No. 1, pp. 17-35, Jan. 2013.

- [23] S. Roy and S. S. Chaudhuri, "Cuckoo search algorithm using Lévy flight: a review," *Int. J. Modern Education Comput. Sci.*, Vol. 5, No. 12, pp. 10-15, 2013.

- [24] W. M. Aly, "Evaluation of cuckoo search usage for model parameters estimation," *Int. J. Comput. Appl.*, Vol. 78, No. 11, Sep. 2013.

- [25] D. Singla and P. R. Sharma, "Optimal minimization of THD and loss analysis in multilevel inverter using cuckoo search algorithm," *J. Emerg. Technol. Innovative Res.*, Vol. 5, No. 8, pp. 1104-1110, Aug. 2018.

**Deepshikha Singla** was born in India, in 1986. She received her Degree of Bachelor of Engineering in Electronics and Instrumentation Engineering in 2007. and her Master of Technology in Electrical Engineering (Power System and Drives) from the YMCA University of Science and Technology (YMCAUST), Faridabad, India, in 2011,

where she is presently working towards her Ph.D. degree. She has five years of teaching experience at the Manav Rachna International University (MRIU), Faridabad, India. She is presently working as an Assistant Professor in the Department of Electrical Engineering, YMCAUST. Her current research interests include power quality improvements in multilevel inverters.

P.R. Sharma was born in India, in 1966. He received his Degree of Bachelor of Engineering in Electrical Engineering from Punjab University, Chandigarh, India, in 1988; Degree of Master of Technology in Electrical Engineering (Power System) from Regional Engineering College, Kurukshetra, India, in 1990; and his Ph.D. degree from

Maharshi Dayanand University, Rohtak, India in 2005. He began his carrier in industry. He has a great deal of experience both in industry and teaching. He is presently working as Professor of Electrical Engineering in Department of Electrical and Electronics Engineering in YMCA University of Science and Technology, Faridabad, India. His current research interests include Optimal Location and Coordinated Control of FACTS Devices in Power System. He has over 92 publications in international journals and conference proceedings. He is a reviewer of IET, IE (INDIA), TUBITAK, IJEST and IEEE International conferences.