# 용액공정용 불소 도핑된 인듐 갈륨 징크 산화물 반도체의 박막 트랜지스터 적용 연구

#### 정선호†

경희대학교 정보전자신소재공학과

## Solution-Processed Fluorine-Doped Indium Gallium Zinc Oxide Channel Layers for Thin-Film Transistors

### Sunho Jeong<sup>†</sup>

Department of Advanced Materials Engineering for Information and Electronics, Kyung Hee University, 1732 Deogyeong-daero, Giheung-gu, Yongin-Si, Gyeonggi-do 17104, Korea

(Received August 19, 2019: Corrected September 10, 2019: Accepted September 13, 2019)

초 록: 본 논문은 용액공정용 불소 도핑된 인듈 갈륨 징크 산화물 반도체를 연구하였으며, 박막 트랜지스터 적용 가능성을 확인하였다. 용액형 산화물 반도체를 형성하기 위해, 금속염 전구체 기반 용액을 제조하였으며, 추가적인 불소 도핑을 유도하기 위해 화학적 첨가제로서 암모늄 플로라이드를 이용하였다. 열처리 온도 및 불소 도핑양에 따른 전기적 물성을 고찰함으로서, 300도 저온 열처리를 통해 제조된 산화물 반도체층의 전기적 특성을 향상시켰다. 20 mol% 불소를 도핑하는 경우, 1.2 cm²/V·sec의 이동도 및 7×10<sup>6</sup>의 점멸비 특성이 발현 가능함을 확인하였다.

**Abstract:** In this study, we have developed solution-processed, F-doped In-Ga-Zn-O semiconductors and investigated their applications to thin-film transistors. In order for forming the appropriate channel layer, precursor solutions were formulated by dissolving the metal salts in the designated solvent and an additive, ammonium fluoride, was incorporated additionally as a chemical modifier. We have studied thermal and chemical contributions by a thermal annealing and an incorporation of chemical modifier, from which it was revealed that electrical performances of the thin-film transistors comprising the channel layer annealed at a low temperature can be improved significantly along with an addition of ammonium fluoride. As a result, when the 20 mol% fluorine was incorporated into the semiconductor layer, electrical characteristics were accomplished with a field-effect mobility of 1.2 cm<sup>2</sup>/V·sec and an  $I_{on/off}$  of  $7 \times 10^6$ .

Keywords: solution, oxide, semiconductor, fluorine

## 1. 서 론

박막 트랜지스터 적용이 가능한 산화물 반도체 소재는 최근 많은 관심을 이끌고 있다. <sup>1,2)</sup> 특히, 산화물 반도체는 비정질/결정질 실리콘 반도체와 비교했을 때, 비정질상임 에도 불구하고 비교적 높은 이동도 특성이 발현되는 특 징적인 장점을 가지고 있다. 결정화 공정이 필요하지 않 기 때문에 대면적 공정이 가능하다. 또한, 기존 비정질 실 리콘 반도체의 낮은 이동도 특성을 극복할 수 있는 대안 소재로서 디스플레이 백플레인용 박막 트랜지스터 채널 층으로 각광받고 있다. <sup>3,4)</sup> 더불어, 차세대 디스플레이의 저가격화를 위해, 용액 공정이 가능한 산화물 반도체 소재에 대한 연구가 활발히 진행되고 있다. 초기에는 콜로이달 기반 용액 공정용 소재에 대한 연구가 주로 제시되었지만, 치밀구조 박막층을 형성하지 못하는 한계점과 입자간 계면에서의 전자 산란으로 인한 특성 저하가 문제점으로 지적되고 있다. 5.60 이를 극복하기 위해 전구체 기반 용액형 소재 합성에 대한 연구가 제시되고 있다. 다양한 전구체가 제안되고 있지만, 다양한 조성물의 합성이가능한 금속염 전구체에 대한 연구가 주를 이루고 있다. 금속염 전구체를 이용한 용액형 산화물 반도체 소재를

합성함에 있어서 가장 중요한 이슈는 이동도 특성을 향

<sup>†</sup>Corresponding author E-mail: sjeong@khu.ac.kr

This is an Open-Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License(http://creativecommons.org/licenses/by-nc/3.0) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

<sup>© 2019,</sup> The Korean Microelectronics and Packaging Society

60 정선호

상시킬 수 있는 첨가제이다. 특정 조성물 구현을 위해 화학양론비를 조절하여 금속염 전구체들을 용매에 혼합하고, 금속염 전구체의 용해도를 향상시키기 위해 착화물유도제를 기본적으로 첨가한다. 금속염 전구체들의 솔젠 반응을 유도하기 위해, 400도 내외의 온도 범위에서열처리를 진행함으로서 산화물 반도체 채널층을 제조한다. 금속염 전구체 기반 산화물 반도체 층의 전기적 특성은 기본적으로 조성에 의해 좌우된다. 또한, 열처리 온도에 따라 활성화되는 산소 공공 반응에 의해 결정된다. 산소 공공이 하나 형성될 때 두 개의 전자가 형성되는 과정이 기본적으로 전자를 생성하는 기구이다. 따라서, 전기적 특성을 향상시키기 위해, 조성물 및 열처리 온도에 의한 전기적 특성 제어 방법과는 다른 추가적인 전자 생성기구 도입이 필요하다.

본 연구에서는 산업적으로 현재 적용되고 있는 인듐 갈륨 징크 산화물(IGZO) 산화물 반도체 채널층을 형성하기위해 금속염 전구체 기반 용액을 제조하였으며, IGZO 산화물 반도체층의 전기적 특성을 향상시키기위해 불소를 도핑하였다. 특정 용매에 용해된 금속염 전구체와 더불어 암모늄 플로라이드를 첨가함으로서 불소 도핑된 IGZO 산화물 층을 형성하기위한 전구체용액을 제조하였다. 박막 트랜지스터를 제조하여 형성된 산화물 반도체 채널층의 전기적 특성을 고찰하였다. 특히, 열처리온도 및 불소 도핑 양에 따른 전기적 특성을 고찰함으로서, 300도의 저온 열처리를 통해 제조된 산화물 반도체층의 특성 향상기저기구를 파악하였다.

## 2. 실험방법

인듐 갈륨 징크 산화물(IGZO) 전구체 용액을 합성하기 위해, 인듐 나이트레이트 하이드레이트(Indium nitrate hydrate), 갈륨 나이트레이트 하이드레이트 (gallium nitrate hydrate), 징크 아세테이트 다이하이드레이트(zinc acetate dihydrate)를 이용하였다. 각각의 금속염 전구체의 몰비율 은 In:Ga:Zn = 63:10:27이 되도록 조성을 제어하였다. 금 속염 전구체의 용해를 위한 용매로서는 메톡시에탄올(2methoxyethanol)을 이용하였으며, 금속염의 원활한 용해 및 안정화를 위해 에탄올아민(ethanolamine)을 이용하였 다. 전구체의 전구체 몰 농도는 0.375 M이며, 에탄올아민 의 몰 농도 0.87 M로 제어하였다. 또한, 불소 도핑을 위 한 전구체 용액을 합성하기 위해, 0.317 M의 암모니움 플 로라이드(NH4F)를 메톡시에탄올에 용해시켰으며, 원활 한 용해 및 안정화를 위해 1.42 M 에탄올아민을 첨가하 였다. 준비된 불소 도핑 전구체 용액과 인듐 갈륨 징크 전 구체 용액을 특정한 비율로 혼합한 후, 상온에서 3시간 동안 교반하였다.

박막 트랜지스터 제작을 위해, 300 나노미터의 두께를 가지는  $SiO_2$ 가 열성장 된 heavily-doped Si 웨이퍼를 아세톤(acetone), 이소프로필알코올(isopropyl alcohol), 메탄올

(methanol), 에탄올(ethanol)을 이용하여 세척 및 질소건을 통한 건조과정을 거친 후, 플라즈마 클리너를 이용하여 표면을 세척하였다. 그 후, 상기 제조된 혼합용액을 스핀코팅을 통해 코팅하였으며, 코팅된 기판은 300~400도 온도 조건에서 30분 동안 열처리되었다. 소스 및 드레인 전극 형성을 위한 알루미늄 전극은 열 증착법을 통해 형성되었다.

## 3. 결과 및 토의

금속염 전구체 용액 기반 산화물 반도체의 전기적 특 성은 수산화물의 조성과 산소 공공의 농도로 결정된다.<sup>7)</sup> 금속염 전구체는 용매에 용해되면서 solvation 반응을 거 치고, 금속 양이온을 둘러싸고 있는 리간드 그룹들의 수 화 반응 및 축합반응을 통해 산화물을 형성하게 된다. 이 러한 반응들은 상온에서도 진행되지만 반응 상수가 매우 낮다. 따라서, 산화물 형성 반응을 완료하고 중간 생성물 인 수산화물의 양을 줄이기 위해 일반적으로 추가적인 에 너지 공급이 필요하다. 이를 위해, 금속염 전구체 용액을 기판상에 코팅한 후, 열처리 과정을 진행하게 된다. 대부 분 조성물의 경우, 400도 내외의 온도에서 열처리 공정이 진행된다. 하지만, 용액 공정이 지향하는 유연 기판 사용 측면에서 400도의 열처리 온도는 극히 제한적이다. 열적 안정성이 우수한 폴리이미드 기판의 경우에도 400도의 열처리 온도는 허용되지 않는다. 300도 내외의 열처리 공 정을 통해 우수한 전기적 특성 발현이 가능한 산화물 반 도체 층을 개발하는 것이 중요하다.

산화물 반도체는 밴드갭 에너지가 큰 물질이다. 따라서, n-type 산화물 반도체의 특성을 향상시키기위해, 전자를 생성시키는 것은 필수 불가결적인 요소이다. 산화물 반도체에서 전자는 산소 공공 형성과정에서 주로 생성된다. 전기적 중성을 유지하기 위해 산소 공공이 하나 형성될 때 전자가 두 개 생성되는 기구이다. 이러한 산소 공공 형성 반응 역시 열에너지에 의해 활성화된다. 즉, 열처리 온도가 높아질수록 많은 산소 공공이 형성되고 이로 인해 전자 생성이 보다 촉진되는 양태이다. 8,9)

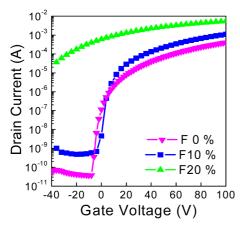

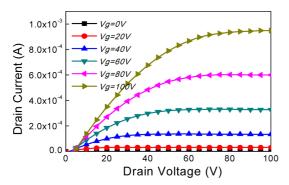

Fig. 1에서 확인되듯이, 400도 열처리된 IGZO 채널층이 포함된 소자의 경우, 1.1 cm²/V·sec의 이동도, 6×10<sup>6</sup>의 점멸비, 및 25 V의 문턱전압 특성을 보인다. 이는 일반적으로 보고되는 IGZO 박막 트랜지스터의 물성과 비슷한수준이다. 10 mol%의 불소가 도핑되는 경우, 2.6 cm²/V·sec의 이동도, 10<sup>6</sup>의 점멸비, 및 8.5 V의 문턱전압 특성이 발현된다. 오프 전류의 증가로 인해 점멸비가 약간 감소하였다. 하지만, 오프전류 변화 양상과 더불어, 이동도가 향상되었으며 문턱전압은 감소하였다. 이러한 전기적특성 변화는 불소 도핑을 통한 추가적인 전자 공급에 기인하는 결과이다. 추가적으로 형성된 전자에 의해 이동도가 향상되고 문턱전압이 감소한다. Fig. 2에서 확인되듯이 10 mol% 불소가 도핑된 IGZO 박막 트랜지스터의

**Fig. 1.** Transfer data for transistors prepared from 400°C-annealed F-IGZO semiconductors as a function of F composition.

**Fig. 2.** Output data for the transistor employing the channel layer prepared from 400°C-annealed 10% F-IGZO semiconductor.

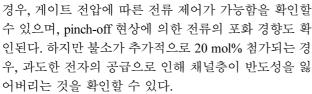

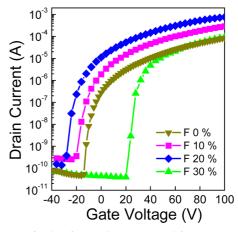

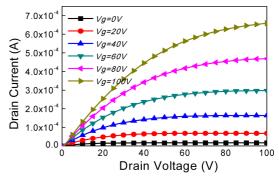

이러한 불소 도핑에 따른 추가적인 전자 공급 효과는 저온에서 열처리된 산화물 반도체 층에서도 확인된다. Fig. 3에서 확인되듯이, 300도 열처리된 IGZO 채널층을 기반으로 제작된 박막 트랜지스터는 0.2 cm²/V·sec의 이 동도, 5×10<sup>5</sup>의 점멸비, 및 5.1 V의 문턱전압 특성을 보인 다. 10 mol%의 불소가 도핑되는 경우, 이동도는 0.5 cm²/ V·sec 값으로 향상되고, 문턱적압은 1.2 V로 감소한다. 오 프전류는 약간 증가하시면 온전류의 증가분으로 인해 점 멸비는 5×10<sup>5</sup> 값을 유지한다. 이는 400도 열처리된 불소 도핑 IGZO 채널층에서 확인된 불소 도핑에 따른 결과와 일치한다. 이러한 경향은 불소가 추가적으로 도핑되면서 도 확인된다. 불소가 20 mol% 도핑되는 경우, 1.2 cm<sup>2</sup>/ V·sec의 이동도, 7×10<sup>6</sup>의 점멸비, 및 -14.5 V의 문턱전압 특성을 보인다. Fig. 4에서 확인되듯이, 이와 같이 향상된 이동도 및 점멸비 특성을 보이는 20 mol% 도핑된 IGZO 산화물 반도체 트랜지스터는 게이트 전압에 따른 전류 제 어 및 전류 포화 현상이 나타나는 우수한 특성의 ouput

**Fig. 3.** Transfer data for transistors prepared from 300°C-annealed F-IGZO semiconductors as a function of F composition

**Fig. 4.** Output data for the transistor employing the channel layer prepared from 300°C-annealed 20% F-IGZO semiconductor.

특성을 보인다. 불소가 추가적으로 도핑되는 경우, 불필 요한 산란 효과로 인해 오히려 특성이 감소한다.

최근 많은 연구 보고에서 300도 내외 저온 열처리를 이용한 용액공정 기반 산화물 반도체 트랜지스터가 제시되고 있다. 하지만, 열에너지 이외의 추가적인 화학 에너지를 공급할 수 있는 새로운 열처리 방법에 대한 보고가 주를 이루고 있다. 이는 추가적인 장치가 필요하다는 것을 의미하며, 용액공정 기술이 지향하는 바와 배치되는 경향이 있다. 본 연구에서는 이러한 추가적인 장치의 필요 없이, 화학적 첨가제를 금속염 전구체 용액에 첨가함으로서 용액형 산화물 반도체의 전기적 특성을 제어할 수있는 방법을 제시하였다.

## 4. 결 론

본 논문에서는 금속염 전구체 기반 용액으로부터 제조 된 산화물 반도체 층의 전기적 물성을 제어하기 위한 화 학적 첨가제를 제시하였다. 암모늄 플로라이드를 첨가함 으로서, 산소 공공 형성에 의한 전자 형성 기구와 더불어 추가적인 전자를 공급함으로 산화물 반도체 박막 트랜지 스터의 물성을 향상시켰다. 특히, 금속염 전구체 용액 공 정의 가장 큰 한계점인 저온 열처리 산화물 반도체층의 62 정선호

열악한 전기적 특성을 개선하였다. 300도 열처리된 IGZO 채널층 기반 박막 트랜지스터의 경우, 20 mol% 불소를 도핑함으로서 1.2 cm²/V·sec의 이동도 및 7×10<sup>6</sup>의 점멸비를 보이는 우수한 특성이 발현 가능함을 확인하였다. 암모늄 플로라이드를 이용한 화학적 첨가제 기법은 용액공정용 산화물 반도체 채널층의 전기적 특성을 개선할 수 있는 방법으로서 향후 다양한 산화물 반도체 조성물로 확장적 적용이 가능할 것으로 기대된다.

## Acknowledgement

This research was supported by the Nano Material Technology Development Program through the National Research Foundation of Korea funded by the Ministry of Science, Information and Communication Technologies and Future Planning (NRF-2015M3A7B4050306). This work was also supported by a grant from Kyung Hee University in 2019 (KHU-20191040).

#### References

- K. Nomura, H. Ohta, A. Takagi, T. Kamiya, M. Hirano, and H. Hosono, "Room-Temperature Fabrication of Transparent Flexible Thin-Film Transistors Using Amorphous Oxide Semiconductors", Nature, 432, 488 (2004).

- 2. S. Jeong, and J. Moon, "Low-Temperature, Solution-Processed Metal Oxide Thin Film Transistors", J. Mater. Chem.,

- 22, 1243 (2012).

- 3. E. Fortunato, P. Barquinha, and R. Marins, "Oxide Semiconductor Thin-Film Transistors: A Review of Recent Advances", Adv. Mater., 24, 2945 (2012).

- J. S. Park, W.-J. Maeng, H.-S. Kim, and J.-S. Park, "Review of Recent Developments in Amorphous Oxide Semiconductor Thin-Film Transistor Devices", Thini Solid Films, 520, 1679 (2012).

- J.-Y. Oh, J. Park, S.-Y. Kang, C.-S. Hwang, and H.-K. Shim, "Room Temperature Fabrication of ZnO Nanorod Films: Synthesis and Application as a Channel Layer of Transparent Thin Film Transistors", Chem. Commun., 45, 4545 (2009).

- T. V. Richer, F. Stetzl, J. Schulz-Gericke, B. Kerscher, U. Würfel, M. Niggemann, and S. Ludwigs, "Room temperature Vacuum-induced Ligand Removal and Patterning of ZnO Nanoparticles: from Semiconducting Films Towards Printed Electronics", J. Mater. Chem., 20, 874 (2010).

- G. R. Hong, S. S. Lee, Y. Jo, M. J. Choi, Y. C. Kang, B.-H. Ryu, K.-B. Chung, Y. Choi, and S. Jeong, "Extremely Low-Cost, Scalable Oxide Semiconductors Employing Poly(acrylic acid)-Decorated Carbon Nanotubes for Thin-Film Transistor Applications", ACS Appl. Mater. Interfaces., 8, 29858 (2016).

- S. J. Kim, A. R. Song, S. S. Lee, S. Nahm, Y. Choi, and K.-B. Chung, S. Jeong, "Independent Chemical/Physical Role of Combustive Exothermic Heat in Solution-Processed Metal Oxide Semiconductors for Thin-Film Transistors", J. Mater. Chem. C., 3, 1457 (2015).

- S. Jeong, Y.-G. Ha, J. Moon, A. Facchetti, and T. J. Marks, "Role of Gallium Doping in Dramatically Lowering Amorphous-Oxide Processing Temperatures for Solution-Derived Indium Zinc Oxide Thin-Film Transistors", Adv. Mater., 22, 1346 (2010).