ISSN: 1226-7244 (Print) ISSN: 2288-243X (Online) 논문번호 19-03-36

238

# CNTFET 기반 디지털 회로 디자인 방법에 관한 연구 A Study on the Design Methodology of CNTFET-based Digital Circuit

조 근 호\*<sup>★</sup>

Geunho Cho\*\*

#### **Abstract**

Over the past decades, the semiconductor industry has continuously scaled down the size of semiconductor devices to increase those performance and to integrate them at higher density on the chip. However, facing the reduction of gate control, higher leakage current, and short channel effect, there is a growing interest in next-generation semiconductors which can overcome these problems. In this paper, we discuss digital circuit design techniques using CNTFET(Carbon NanuTube Field Effect Transistor), which are attracting attention as candidates for the next generation of semiconductors. Since the structure of CNTFETs are clearly different from the structure of the structure of conventional MOSFETs, we will discuss how to utilize existing digital circuit methodology when designing digital circuits using the CNTFETs, and then simulate the performance differences between the two devices.

### 요 약

지난 수십 년간 반도체 업계에서는 반도체 소자의 성능을 높이고 높은 밀도로 반도체 소자를 칩 위에 집적하기 위해 끊임 없이 그 크기를 축소해 왔다. 하지만, 게이트 제어의 감소, 높아진 누설 전류, 그리고 단 채널 효과와 같은 다양한 문제점에 직면하면서 이를 극복할 수 있는 차세대 반도체에 점점 더 많은 관심을 보이고 있다. 본 논문에서는 다음 반도체 세대를 이끌 후보로 관심을 받고 있는 CNTFET(Carbon NanuTube Field Effect Transistor)을 활용하여 디지털 회로를 디자인하는 방법에 대해 논하고자 한다. CNTFET이 분명 구조적으로 기존 MOSFET과 다른 구조를 가진 만큼, CNTFET을 활용하여 디지털 회로를 디자인할 때, 기존 디지털 회로 기법을 어떻게 활용할 수 있는지 자세히 알아보고 시뮬레이션을 통해 두 소자의 성능 차이를 확인해 보고자 한다.

Key words: CNTFET, CNT, CNT Density, Digital Circuit, Delay

E-mail: choroot@skuniv.ac.kr, Tel: +82-2-940-7730

Acknowledgment

This research was supported by Seokyeong University in 2019.

The EDA tool was supported by the IC Design Education Center(IDEC), Korea

Manuscript received Sep. 5, 2019; revised Sep. 24, 2019; accepted Sep. 26, 2019.

This is an Open-Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License(http://creativecommons.org/licenses/by-nc/3.0) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

# 1. 서론

지난 수십 년간 반도체 업계는 무어의 법칙에 따라 끊임없이 반도체 소자의 크기를 축소해 왔으나, 최근 게이트 제어의 감소, 높아진 누설 전류, 그리고 단 채널 효과와 같은 다양한 문제점에 직면하면서 기존 반도체 소자의 추가적인 축소에 어려움을 겪고 있다. 무엇보다 소스와 드레인 사이가 5nm 보다 작아질 경우, 양자 터널링(quan-tum tunneling) 효과에 의해 전자의 이동을 게이트 전압으로 제어될 수 없어, 5nm는 기존 실리콘 기반 트랜지스터스케일링(scaling)의 한계로 받아들여지고 있다. 이

<sup>\*</sup> Dept. of Electronics Engineering, Seokyeong University

<sup>★</sup> Corresponding author

러한 상황에서 최근 CNT(Car- bon NanoTube)로 1nm의 gate length를 갖는 트랜지스터가 제작에 성공하여 CNT가 기존 실리콘 기반 트랜지스터의 한계를 극복할 수 있는 물질로 기대를 받고 있으며, 최근(2019년 8월) MIT에서 CNTFET 1만4000개로 16비트 프로세서를 만드는데 성공하여 CNT로 만든 마이크로프로세서가 컴퓨터 프로그램을 구동시키는데 처음으로 성공하였다. IBM은 2014년 5년간 30억 달러를 투자를 통해 7nm 칩을 개발 계획을 발표하면서 "탄소나노튜브가 가장 유력한 차세대 반도체 재료"라고 언급하였으며, 미국 방위고 등연구계획국(DAPRA)도 2018년 MIT 슐레이커 교수의 연구와 탄소나노튜브 차세대 칩 개발에 15억 달러를 지원하고 있다[1]-[6].

CNTFET이 기존 MOSFET과 그 구조가 다른 만큼, CNTFET을 활용한 CNTFET 회로를 디자인 할 때, 최적화해야 할 변수와 변수의 변화에 따른 소자 특성이 다를 수밖에 없으며, CNTFET이 정교 한 CNT 배치를 요구하는 만큼, 높은 밀도로 CNT 를 배치시키는 기술이 CNTFET을 개발하는데 있 어 극복해야할 중요한 기술로 여겨지고 있다. 본 논문에서는 CNTFET을 활용하여 디지털 회로 블 록을 디자인 하는데 있어 기존 MOSFET 회로 디 자인 룰이 어떻게 활용될 수 있는지 CNT 밀도와 함께 알아보고, 최적화된 CNTFET 회로와 기존 MOSFET 회로의 성능차를 비교하고자 한다. 성능 차 비교를 위한 시뮬레이션 툴로 HSPICE를 사용 하였으며, 공정한 비교를 위해 동일한 32nm gate length의 CNTFET Model[7]과 PTM MOSFET Model[8]을 사용하였다[7]-[12].

# Ⅱ. 본론

# 1. CNTFET

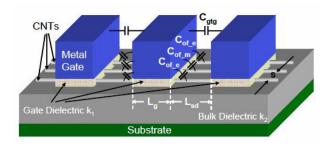

Fig. 1. CNTFET Structure[1]. 그림 1. CNTFET 구조[1]

CNTFET은 그림 1과 같이 반도체 기판(Substrate)과 금속 게이트(Metal Gate) 사이에 CNT를 배치시켜 CNT를 소스(Souce)와 드레인(Drain) 사이에 전류가 흐르는 통로로 활용하고, 게이트(Gate), 소스, 그리고 드레인 전압으로 전류의 양을 제어하는 구조로 되어 있다[1].

CNT를 통해 전류가 흐르는 만큼, CNT의 수를 증가시키면 전류의 양은 증가되어 CNTFET 회로 의 지연 시간(delay)은 감소될 수 있으나, 제한된 CNTFET 공간 안에 CNT의 숫자를 증가시키기 위해 CNT 사이의 간격을 좁게 만들면, 즉, CNT의 밀도를 증가시키면, 스크리닝 효과(screening effect)에 의해 각 CNT에 흐르는 전류의 양이 감소될 수 있으며, 동시에, 그림 1의  $C_{of_{-m}}$  그리고  $C_{of_{-e}}$ 와 같이, 다양한 커패시턴스 요소들을 증가시켜 CNTFET의 게이트 커패시턴스(gate capaci-tance) 값이 증가 될 수 있다. 이는 CNT 사이의 간격이 넓을 때는 CNT 수의 증가가 CNTFET 회로의 지연 시간을 감소시키는 역할을 할 수 있으나, CNT 사이의 간 격이 좁아질 경우 CNTFET 회로의 지연을 오히려 증가시킬 수 있음을 보여준다. 따라서, CNTFET을 활용하여 회로를 디자인할 때, CNTFET의 gate width, CNT의 수, 그리고 CNT 밀도에 대한 신중 한 선택이 중요하다[1]-[3].

#### 2. CNT 밀도 선택

그동안 많은 연구들이 CNTFET을 활용한 다양한 회로 블록들을 제안하고, 그 결과를 동일한 MOS-FET 회로 블록과 비교를 해왔으나, 두 회로 블록 의 성능을 비교하는데 사용된 회로 구성에 대한 자 세한 설명이 없어, 어떤 환경에서 CNTFET 회로의 성능이 측정되었는지 그리고 어떤 CNTFET 특성이 회로 성능에 반영 되었는지 그 자세한 원리를 이해 하는데 어려움이 있었다. CNT의 밀도가 CNTFET 의 게이트 커패시턴스와 전류의 양을 결정하는 만 큼, CNTFET의 CNT 밀도가 변할 때, 테스트하고자 하는 CNTFET 회로 블록(test block)은 CNT 밀도 에 따라 신호를 입력하는 회로 블록(input block)의 영향을 받고, 동시에 신호를 받는 회로 블록(output block)에 영향을 주는 상황에서 그 성능이 결정하게 되므로, 본 논문에서는 CNT-FET 성능 분석을 위 한 회로 구성과 함께 CNT 밀도가 CNTFET 성능 에 미치는 영항을 논하고자 한다[1]-[3], [9]-[12].

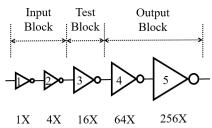

Fig. 2. FO4 Inverter Chain. 그림 2. FO4 인버터 체인

CNT의 밀도를 선택하는데 있어, 본 논문에서는 그림 2와 같이 5 stage FO4(Fan-out of 4) inverter를 이용하여, 즉, 회로 관점에서 각 디지털 회로 블록에서 요구하는 최적의 CNT 밀도를 선택하고자한다. 논하고자 하는 디지털 회로 블록은 Inverter, NAND2, 그리고 NOR2를 기본으로 그 성능을 기존 MOSFET의 Inverter, NAND2, 그리고 NOR2와 그성능을 비교하고자 하며, 회로 블록을 NAND3와 NOR3로 확장하였을 경우, 즉, 전원과 접지 사이에더 많은 트랜지스터를 연결하였을 경우, 두 소자의성능 변화를 살펴보고자 한다. 더 나아가 XOR2를 앞서 언급한 NAND2로 입력 단자와 출련 단자 사이에 연속으로 연결하여, 두 반도체 소자가 시리즈로 연결되었을 때 성능의 변화 역시 같이 논하고자한다.

다양한 디지털 블록의 FO4를 논할 때 그림 2와 같이 input block과 output block은 test block과 같은 종류의 회로 블록을 사용하며 그 사이즈를 4배로 늘려야만 각 회로 블록의 출력 커패시턴스가 4배로 늘어나는 FO4 인버터 체인을 구성할 수 있다. 따라서, test block이 inverter가 아닌 다른 회로 블록인 경우, 예를 들어, NAND2인 경우, 그림 2의 input block과 output block은 NAND2로 구성되어야지만 이론적으로 FO4 회로가 구성된다.

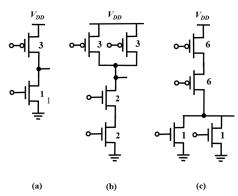

Fig. 3. Conventional Digital Circuit Design[13]. 그림 3. 기존 디지털 회로 디자인[13]

하지만, 본 논문에서는 inverter가 아닌 다른 디 지털 블록을 테스트할 때 input block과 output block은 그림 2와 같이 inverter로 구성하고자 한 다. 왜냐하면, 일반적으로 디지털 회로를 디자인하 는데 있어서, 특정 위치에 있는 회로 블록까지 신 호를 전달하는데 있어 일반적으로 inverter가 많이 사용되고, 일부러 FO4를 맞추겠다고 제한된 칩 디 자인 면적 안에 신호를 전달하는 회로 블록을 신호 를 받는 회로 블록과 같은 회로 블록을 사용하지 않기 때문이다. 이는 test block과 out- put block 사이의 관계에서도 마찬가지이다. 그리고 무엇보다 이러한 접근 방법이 중요한 이유는 현재 기술 수준 에서 충분한 CNT 순도와 밀도를 확보하기 어려운 상황에서 회로 위치별로 다른 CNT 밀도를 구현하 는 것은 더욱 어려운 일이기 때문에, CNT 밀도를 적용할 때는 전체 CNTFET 회로에 동일하게 적용 할 수 있는 하나의 CNT 밀도만을 고려해야 한다 [12][13].

## 3. 디지털 회로 디자인 룰

전통적으로 MOSFET을 이용하여 다양한 디지털 회로를 디자인할 때, 일반적으로 디지털 회로를 구 성하는 PMOS와 NMOS의 gate length는 반도체를 제조하는 공정에 따라 일정하게 정해지며, gate width 는 gate length의 배수로 디자인 된다. 그림 3의 (a) 가장 기본적인 디지털 블록인 inver-ter를 나타내며, 일반적으로 NMOS의 gate width는 gate length와 동일한 값을 갖기 때문에, '1'이라는 값으로 표기를 하였으며, PMOS는 NMOS보다 부족한 이동도 (mobility)를 보상하기 위해 gate length보다 3배 더 넓은 gate width를 필요로 하기 때문에 '3'이라는 숫자로 표기하였다. 이와 같은 디자인 룰을 NAND2 와 NOR2에 적용할 때, 그림 3의 (a)와 비교하여 트 랜지스터가 추가로 그리고 직렬(전원과 접지 사이 에)로 연결된 경우, gate width를 2배로 늘려 트랜 지스터 직렬 연결로 인한 저항의 증가를 보상해야 한다. 이러한 NAND2 그리과 NOR2 디자인 결과 는 그림 3의 (b) 그리고 (c)와 같다[13].

이와 같은 전통적인 디지털 회로 디자인 룰은 gate width가 늘어날 때, 회로의 지연 시간을 결정하는 gate capacitance와 current가 동시에 늘어나기 때문에 그림 3과 같은 반복적인 확장이 가능하지만, CNTFET인 경우, 앞서 언급한 바와 같이, 전

Fig. 4. Delay of Inverter, NAND2, and N- AND3. 그림 4. Inverter, NAND2, 그리고 NAND3의 지연

류가 CNT를 통해 흐르고, CNT의 수와 위치가 gate capacitance를 변화시키기 때문에 그림 3과 같은 단순한 확장이 불가능하다[1]-[3].

본 논문에서는 앞서 2장에서 언급한 시뮬레이션 조건 하에 그림 3과 같은 디지털 회로 디자인 룰이 CNTFET에 어떻게 정해질 수 있는지 그 결과를 MOSFET과 비교해가며 논하고자 한다.

#### 4. 시뮬레이션 검토

그림 2와 같은 조건하에 inverter, NAND2, 그리고 NAND3의 하강 시간(FT, Fall Time), 상승 시간(RT, Rise Time), 그리고 두 시간의 평균인 지연시간을 시뮬레이션 하면 그림 4와 같다. CNT의 지름은 1.5nm이며, gate width 32nm 기본으로 CNT사이의 간격을 일정하게 줄이며 그 숫자를 늘렸을때, 즉, CNT의 밀도를 일정하게 증가시켰을 때, 하강시간, 상승 시간, 그리고 지연 시간을 계산하였다. Power는 CNT가 수가 증가할수록 PDP를 지속적으로 증가시킬 정도로 그 값이 빠르게 증가하였기 때문에 본 논문에서 최적의 밀도를 찾을 때 고려하지 않았다.

CNTFET 안의 CNT 수가 증가할수록 그림 4와 같이 CNTFET에 흐르는 전류의 양이 증가하면 지연 시간은 감소되나, 어느 이상 밀도가 증가하면, 앞서 언급한 스크리닝 효과에 의해 각 CNT에 흐르는 전류의 양은 감소하고, gate capacitance는 증가하여 inverter의 지연은 다시 증가하게 된다. Inverter의 PFET과 NFET의 비율은 1:1로 시뮬레

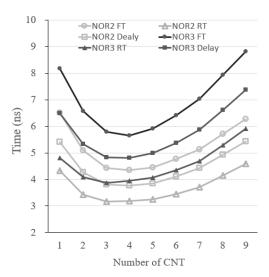

Fig. 5. Delay of NOR2 and NOR3. 그림 5. NOR2 그리고 NOR3의 지연

이션을 시작하여 그 비율을 증가시키려 하였으나, 그림 4와 같이 inverter의 상승 시간은 하강 시간보다 작기 때문에 MOSFET과 달리 CNTFET은 PFET 의 이동도를 보상하기 위해 gate width를 증가시킬 필요가 없었다. 이러한 inverter 특징은 본논문에서 언급한 다른 디지털 블록에서도 동일하게 나타나, 이동도 보상을 위한 PFET의 gate width 증가는 고려하지 않았다.

그림 4에서 NAND2 그리고 NAND3에서의 PFET 그리고 NFET 사이의 비율은 그림 3의 (b)와 같이 수직으로 연결되는 NFET의 숫자가 늘어날수록 gate width를 늘려주었다. 하지만, 같은 방식으로, NOR2 그리고 NOR3에서 PFET의 gate width를 늘려주었을 경우, 그림 5와 같이, 수직으로 연결하는 PFET 수가 늘어날수록 상승 시간과 하강 시간사이의 차이가 크게 벌어짐을 알 수 있었다. 원인을 밝히기 위해 그림 6과 같이 다양한 PFET 그리고 NFET 비율로 시뮬레이션을 검토한 결과 PFET과 NFET 비율이 2:1일 때, 상승 시간과 하강 시간사이의 차이가 가장 적었다. 이는 PFET과 NFET의 비율을 2:1 보다 크게 증가 할 경우, PFET과 NFET 사이의 성능차이가 너무 커져 상승 시간과 하강 시간의 차이가 커진 것으로 볼 수 있다.

그림 4부터 그림 6까지의 시뮬레이션 검토 결과 gate width가 32nm 기준으로 CNT 4개가 같은 간격으로 배치되었을 때, 본 논문에서 언급한 대부분의 디지털 회로 블록에서 가장 우수한 성능을 보여주었다. 이와 같은 CNT 밀도로 구성된 CNT-

Fig. 6. Delay of NOR3 when PFET and NFET ratio is changed.

그림 6. PFET과 NFET 비율 변화에 따른 NOR3의 지연 시간

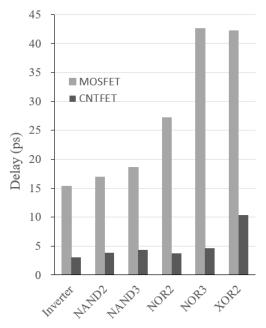

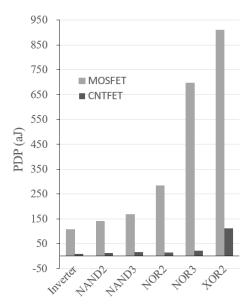

FET 디지털 회로와 MOSFET 디지털 회로와의 지연 시간과 PDP(Power Delay Product)를 비교하면 각각 그림 7과 그림 8과 같다. 그림 7 그리고 그림 8을 통해 CNTFET은 MOSFET 보다 지연시간 그리고 PDP 측면에서 각각 5.4배 그리고 12.6배의 성능 향상이 있음을 알 수 있다.

Fig. 7. Delay of MOSFET Digital Circuit and CNTFET Digital Circuit

그림 7. MOSFET 디지털 회로와 CNTFET 디지털 회로의 지연 시간

Fig. 8. PDP of MOSFET Digital Circuit and CNTFET Digital Circuit.

그림 8. MOSFET 디지털 회로와 CNTFET 디지털 회로의 PDP

## Ⅲ. 결론

CNT를 활용하여 기존 MOSFET보다 높은 성능을 구현한 CNTFET은 MOSFET과 다른 구조를 가진 만큼, 디지털 회로 블록을 디자인할 때, 고려해야할 변수와 접근 방법이 기존 MOSFET의 디지털 회로 블록 디자인 방법과 다를 수밖에 없다. 본논문에서는 CNT 밀도를 고려한 CNTFET 디지털 회로 성능 최적화 방법에 대해 논의 하였으며, 이러한 최적화가 적용된 후, CNTFET 디지털 회로의 지연 시간과 PDP는 기존 MOSFET에 비해 각각 평균 약 5.4배 그리고 약 12.6배 개선되었음을 알 수 있었다.

## References

[1] J. Deng, et al., "A Compact SPICE Model for Carbon-Nan, otube Field-Effect Transis-tors Including Nonidealities and Its Appli-cation-Part I: Model of the Intrinsic Chan-nel Region," *IEEE Transactions on Elec-tron Devices*, vol.54, pp.3186-3194, 2007. DOI: 10.1109/TED.2007.909030

[2] J. Deng, et al., "A compact SPICE model for carbon nanotube field effect transistors including

non-idealities and its application—Part II: Full device model and circuit performance benchmarking," *IEEE Transac-tions on Electron Devices*, vol.54, pp.3195–3205, 2007. DOI: 10.1109/ted.2007.909 043 [3] J. Deng and H. S. P. Wong, "Modeling and Analysis of Planar–Gate Electrostatic Capacitance of 1–D FET With Multiple Cylin–drical Conducting Channels," *IEEE Trans. Electron Devices*, vol.54, no.9, pp.2377–2385, 2007.

DOI: 10.1109/TED.2007. 902047

[4] Sujay B. Desai, et al, "MoS2 transistors with 1-nanometer gate lengths," Science, vol.354, pp. 99-102, 2016. DOI: 10.1126 /science.aah4698

[5] Gage Hills, *et al.*, "Modern microprocessor built from complementary carbon nanotube transistors," *Nature*, vol.572, pp.595–615, 2019.

DOI: 10.1038/s41586-019-1493-8

[6] S. H. CHO, "New material 'carbon nanotube' to advance the dream of ultra-fast semiconductors," http://www.donga.com/news/article/all/20190830/97186868/1

[7] CNFET Models. http://nano.stanford.edu/models.php

[8] PTM Models, http://ptm.asu.edu/

[9] J. Si *et al.*, "Scalable Preparation of High Density Semiconducting Carbon Nanotube Arrays for High-Performance Field-Effect Transistors," *ACS Nano*, vol.12, no.1, pp.627 - 634, 2018.

DOI: 10.1021/acsnano.7b07665

[10] S. Waykol, et al., "Performance Analysis of Classical Two Stage Opamp Using CMOS and CNFET at 32nm Technology," 2018 Fourth International Conference on Computing Communication Control and Automation (ICCUBEA), 2018.

[11] G. Cho, *et al.*, "Assessment of CNTFET based circuit performance and robust-ness to PVT variations," in Proc. of 52nd IEEE International Midwest Sympo-sium on Circuits and Systems (MWS-CAS 2009), pp.1106–1109, 2009.

DOI: 10.1109/MWSCAS.2009.5235961

[12] Nishant Patil, et al., "Design Methods for Misaligned and Mispositioned Carbon-Nano-tube Immune Circuits," IEEE Transactions on Computer-

Aided Design of Integrated Circuits and Systems, vol.27, pp.1725–1736, 2008.

DOI: 10.1109/TCAD. 2008.2003278

[13] Jan M, et al., "Digital Integrated Circuits - A Design Perspective," Prentice Hall, 2003

# **BIOGRAPHY**

#### Geunho Cho (Member)

2004: BS degree in Electronic Engineering, Sogang University. 2006: MS degree in Electronic Engineering, Sogang University. 2012: PhD degree in Electrical Engineering, Northeatern University.

2012~2017: Senior Engineer, Samsung Display. 2017~present: Assistant Professor, Seokyeong University.