JPE 19-5-25

https://doi.org/10.6113/JPE.2019.19.5.1326 ISSN(Print): 1598-2092 / ISSN(Online): 2093-4718

# Equivalent Parallel Capacitance Cancellation of Common Mode Chokes Using Negative Impedance Converter for Common Mode Noise Reduction

Guangdong Dong<sup>†</sup> and Fanghua Zhang<sup>\*</sup>

<sup>†,\*</sup>College of Automation Engineering, Nanjing University of Aeronautics and Astronautics, Nanjing, China

#### **Abstract**

Common mode (CM) chokes are a crucial part in EMI filters for mitigating the electromagnetic interference (EMI) of switched-mode power supplies (SMPS) and for meeting electromagnetic compatibility standards. However, the parasitic capacitances of a CM choke deteriorate its high frequency filtering performance, which results in increases in the design cycle and cost of EMI filters. Therefore, this paper introduces a negative capacitance generated by a negative impedance converter (NIC) to cancel the influence of equivalent parallel capacitance (EPC). In this paper, based on a CM choke equivalent circuit, the EPCs of CM choke windings are accurately calculated by measuring their impedance. The negative capacitance is designed quantitatively and the EPC cancellation mechanisms are analyzed. The impedance of the CM choke in parallel with negative capacitances is tested and compared with the original CM choke using an impedance analyzer. Moreover, a CL type CM filter is added to a fabricated NIC prototype, and the insertion loss of the prototype is measured to verify the cancellation effect. The prototype is applied to a power converter to test the CM conducted noise. Both small signal and EMI measurement results show that the proposed technique can effectively cancel the EPCs and improve the CM filter's high frequency filtering performance.

**Key words:** Common mode choke, Electromagnetic interference, Equivalent parallel capacitance, Negative impedance converter, Winding capacitance cancellation

#### I. INTRODUCTION

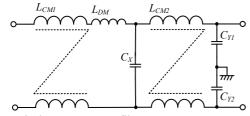

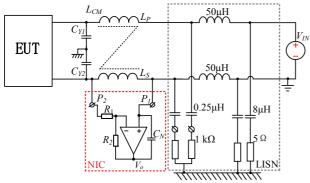

With the two driving forces of high efficiency and high power density for switched-mode power supplies (SMPS), the push for a higher switching frequency and a faster switching action are the major motivations for performance improvements of power electronics. However, high *dv/dt* and *di/dt* in a SMPS are the sources of common mode (CM) and differential mode (DM) noises, and they generate severe EMI noise [1]-[4]. EMI filters are widely used to suppress conducted emissions in order to meet EMI standards. Conducted EMI includes DM and CM noises, while DM and CM filters are used to suppress EMI. Generally, CM noise is more difficult to solve than DM noise [5]. A typical two-stage EMI filter in a SMPS is shown in Fig. 1. Since the leakage

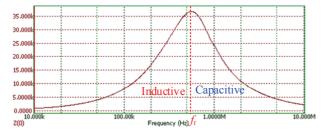

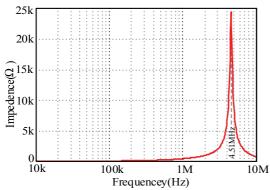

$L_{CMI}$  consist of three kinds of parasitic capacitances, between turn and turn, between turn and core, and between different layers of the same winding. The resonance between the EPC and  $L_{CMI}$  leads to a deterioration of the inductor's high frequency attenuation performance. Even if the CM choke is over-designed, it may not be able to achieve the required attenuation amplitude.  $L_{CM2}$ , in the second stage, is used to deal with very high frequency range CM noise, which is usually wrapped around a small core with few turns. The measured impedance versus the frequency of a CM choke is shown in Fig. 2, where  $f_r$  is the self-resonance frequency. When the frequency is lower than  $f_r$ , the inductor is inductive

and the impedance is proportional to the frequency. Meanwhile,

at high frequencies above  $f_r$ , the property of the CM choke is

changed from inductive to capacitive. The high frequency

current through the Y-capacitor is limited by safety

regulations [6], [7], the inductance of the CM choke is in the

order of several mH.  $L_{CMI}$ , in the first stage, is the major CM

choke with a large number of turns to attenuate the switching

frequency and low harmonic frequency noise. The EPCs of

Manuscript received Jan. 21, 2019; accepted May 14, 2019 Recommended for publication by Associate Editor Jongwon Shin.

<sup>†</sup>Corresponding Author: donggd@nuaa.edu.cn

Tel: +86-25-84892368, Nanjing Univ. of Aeronautics and Astronautics

<sup>\*</sup>College of Automotive Engineering, Nanjing University of Aeronautics and Astronautics, China

Fig. 1. Typical two-stage EMI filter structure.

Fig. 2. Impedance versus frequency of a CM choke.

noise is passed by the EPCs, but is not well attenuated. The existence of EPCs deteriorates the effects of the CM filter. Therefore, it is critical to improve the attenuation performance of the EMI filter in the high frequency range by cancelling the EPCs of the CM choke. The effects of an EPC on EMI filter performance have been analyzed and quantified. For CM filters, the authors of [8]-[10] concluded that the EPC is usually the crucial parasitic parameter, since it may resonate with the CM inductance at very low frequencies. Over the past decade, several methods have been proposed to reduce or cancel the EPCs of CM chokes [11]-[16]. Integrated EMI filters have larger EPCs than discrete EMI filters due to the larger winding surface area, closer distance, and larger number of winding layers [11]. After inserting a grounded copper layer into the CM windings, the parasitic capacitance between the CM choke winding and the embedded grounded layer is used to cancel the EPCs [12]. Similarly, the discrete CM choke requires two grounded capacitors connected to the center tap of the CM choke windings to cancel EPCs [13]. The authors of [14], [15] used the concept of mutual capacitance to generate coupling capacitors to cancel EPC. In [14], it is necessary to adjust the winding coupling capacitance of the CM choke to achieve the best cancellation effect. The authors of [16] introduced an additional passive inductor and capacitor to cancel the effects of winding capacitances. However, it consumed a lot of time identifying the proper capacitance from a range of compensation capacitors. Existing research usually uses passive devices such as inductors, capacitors or copper foil to establish a cancellation circuit, and a specific coupling factor is needed to achieve an optimal cancellation effect [11]-[16]. However, due to the complexity of the magnetic field and the electric field distribution, it is difficult to accurately design the theoretical coupling factor in applications. Therefore, a trial-and-error process is often necessary, which increases both the design cycle and complexity.

Furthermore, the self- parasitic parameters of the inductors and capacitors in the cancellation circuit can deteriorate the cancellation effect at high frequencies. A method of using the negative capacitance concept to cancel the EPC of CM chokes was proposed in [17], and there are many important research contents expanded in this paper. The paper extensions mainly include the following details. 1) In the conference paper, the method of extracting the EPC of CM chokes involves measuring its resonant frequency with the assumption that the inductance is unchanged from a low-frequency up to the resonance frequency. Since the complex magnetic permeability of a ferrite core changes with frequency, inaccuracies are possible in the calculation of inductance using the initial permeability. An improved method for extracting the EPC of CM chokes is adopted in this paper. Thus, the EPCs of two windings can be accurately extracted. 2) In order to ensure that the NIC circuit work stably and normally in a wide band range, design guidelines for the NIC are provided in this paper. They include an analysis of the key parameters affecting the performance of the operational amplifier and the design method of the peripheral circuit. 3) The small signal measured method is adopted to verify the cancellation effect of the NIC including the two aspects of the impedance characteristics and S-parameters. 4) The NIC circuit is applied to the practical switching power converter. This can effectively reduce the CM noise. At the same time, it has no bad effect on the DM noise. Both the small signal and EMI measurement results demonstrate that the proposed technique can effectively cancel the EPC and improve the CM filter's high frequency filtering performance. The quantitative design cancellation parameter, convenient implementation and available circuit application are the key techniques for the EPC cancellation.

In this paper, a method of using the negative capacitance generated by the NIC to cancel the EPC of CM chokes is proposed for CM noise deduction. The mechanism of the NIC cancellation of CM noise is analyzed in detail. In addition, the design criteria of the NIC circuit are given to ensure that it can work stably and normally in a wide band range. The proposed NIC is simply constructed with an Op-Amp and several peripheral passive components. The desired negative capacitance can be quantitatively obtained by adjusting the ratio of the peripheral circuit parameters. The EPCs of the CM choke windings are measured by an impedance analyzer. Then, the impedance characteristics of the CM choke before and after adding the NIC are measured and compared. The NIC is further applied in a practical power converter to measure the CM conducted noise. The power supply of the NIC circuit is convenient, and can be obtained directly from the internal power supply of the converter. The size of the NIC circuit is small when it is added in the SMPS. Thus, it does not affect the structure of the converter. Both small signal and EMI measurement results show that the cancellation

Fig. 3. Photo of a CM choke.

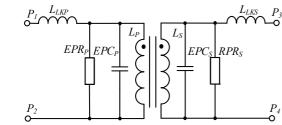

Fig. 4. Equivalent circuit of a CM choke.

technique can effectively reduce the EPC and significantly improve the CM filter's high frequency attenuation performance.

#### II. EXTRACTION OF THE EPC FOR THE CM CHOKE

#### A. Equivalent Circuit of the CM Choke

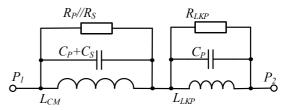

The EPC is a crucial parameter that affects the attenuation performance of CM chokes. Accurate measurement of the EPC is the premise for designing the NIC circuit and for evaluating the high frequency characteristic of a CM choke. A CM choke where each winding occupies two layers and consists of 35 turns of varnished wire with a diameter of 1 mm is built. A photo of the CM choke is shown in Fig. 3. The magnetic core is a T37 Mn-Zn material ferrite core from TDK with a size of 25.3 mm (outer diameter) × 14.8 mm (inner diameter) × 10 mm (height). The CM choke equivalent circuit is shown in Fig. 4, where the two windings are named the P and S windings. The equivalent parallel capacitances  $C_P$ and Cs represent the lumped capacitance between turn and turn, turn and core, and different layers of the same winding, which are parallel to the CM choke. The equivalent parallel resistances  $R_P$  and  $R_S$  represent the lumped effects of winding loss and core loss, which are parallel to the CM choke. The leakage inductances  $L_{PLK}$  and  $L_{SLK}$  are caused by the magnetic flux diffused in the air, and are in series with the CM choke.

# B. Extraction of the EPC

The method for extracting the equivalent parallel capacitance of a CM choke by measuring its resonant frequency, which is caused by the EPC resonance with inductance, is adopted in this paper. The resonance frequency is determined by:

$$f_r = \frac{1}{2\pi\sqrt{L \cdot EPC}} \tag{1}$$

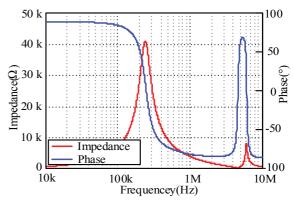

Fig. 5. Measured impedance and phase of the *P* winding with the *S* winding opened.

Fig. 6. Equivalent circuit of a CM choke.

Fig. 7. Measured impedance of a CM choke with the S winding short circuited.

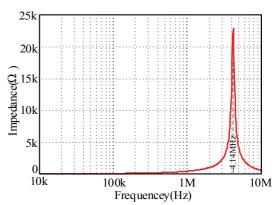

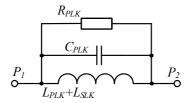

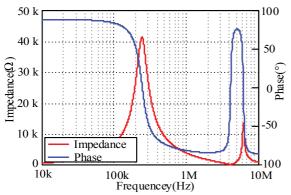

With the pins  $P_3$  and  $P_4$  of the S windings opened, the measured impedance and phase versus the frequency characteristics of the P winding are shown in Fig. 5. The measured results show that there are two resonance frequencies. The first resonance frequency is determined by the CM inductance and the sum of the EPCs in both the P winding and the S winding. The second resonance frequency is determined by the leakage inductance and  $C_P$  of the Pwinding. The equivalent circuit is shown in Fig. 6. With the pins  $P_3$  and  $P_4$  of the S windings directly shorted, the leakage inductance of the CM choke can be obtained, and the measured impedance versus frequency is shown in Fig. 7. An equivalent circuit is shown in Fig. 8. Similarly, with the pins  $P_1$  and  $P_2$  of the P windings opened, the measured impedance and phase versus frequency characteristics of the S winding are shown in Fig. 9. With the pins  $P_1$  and  $P_2$  of the P winding

Fig. 8. Equivalent circuit of a CM choke.

Fig. 9. Measured impedance and phase of the *S* winding with the *P* winding opened.

Fig. 10. Measured impedance of a CM choke with the *P* winding short circuited.

directly shorted, the measured impedance versus frequency is shown in Fig. 10. According to test results of the CM choke, the main parameters of the CM choke can be obtained as follows:  $L_{CM}$ =9.23 mH,  $L_{LK}$ =66.85 uH,  $C_P$ + $C_S$  = 46.93pF,  $C_P$ =25.21 pF and  $C_S$ =21.72 pF. The difference between  $C_P$  and  $C_S$  is that the physical structure of two windings cannot be completely consistent during the winding process.

# III. DESIGN OF THE NIC CIRCUIT

# A. Theoretical Analysis of the NIC

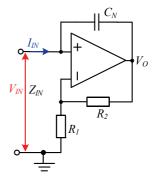

An NIC is a single port operational amplifier circuit acting as a negative load. The schematic of an NIC is shown in Fig. 11, which is also called a current inversion NIC. It employs both positive and negative feedback circuits. The capacitor  $C_N$  is connected between the output port and the non-differential port of the operational amplifier (Op-Amp) to

Fig. 11. Schematic of an NIC.

build a positive feedback circuit, and  $R_I$  and  $R_2$  constitute a negative feedback circuit.  $V_O$  is the output voltage of the Op-Amp.  $V_{IN}$  and  $I_{IN}$  are the input voltage and current of the NIC, respectively.  $Z_{IN}$  is the input impedance of the NIC, which can be obtained by dividing  $V_{IN}$  with  $I_{IN}$ . To simplify the analysis, the Op-Amp is regarded as an ideal device. Based on the golden rules and Kirchhoff's law, the output voltage can be expressed as:

$$V_O = V_{\rm IN} (1 + \frac{R_2}{R_1}) \tag{2}$$

The current from the Op-Amp output port and through the capacitor  $C_N$  toward the source  $V_{IN}$  is:

$$-I_{\rm IN} = \frac{V_{\rm O} - V_{\rm IN}}{Z_{C_{\rm N}}} = V_{\rm IN} \frac{R_2}{R_1 Z_{C_{\rm N}}}$$

(3)

In addition,  $Z_{IN}$  can be expressed as:

$$Z_{\rm IN} = \frac{V_{\rm IN}}{I_{\rm IN}} = -Z_{C_N} \, \frac{R_1}{R_2} \tag{4}$$

The input negative capacitance can be adjusted by changing the values of  $R_I$ ,  $R_2$  and  $C_N$ . As a special case, in the case of  $R_I=R_2$ ,  $Z_{IN}$  is simplified and turned into:

$$Z_{IN} = -Z_{C_N} = \frac{1}{SC_N}$$

(5)

# B. Design of the NIC

The design of the NIC circuit must meet certain design criteria to ensure that it can work stably and normally in a wide band range.

- The bandwidth of the Op-Amp needs to be high enough.

The gain bandwidth product of the Op-Amp should be much higher than the maximum operating frequency of the NIC. This depends on the frequency bandwidth of the CM noise to be cancelled.

- 2) The negative feedback gain of the Op-Amp should be as close as possible to the unit. With a certain gain bandwidth product, a low gain is helpful to increase the bandwidth. Therefore, it is recommended that  $R_1$  and  $R_2$  have the same resistance. In addition, in order to reduce the output current passing through the negative feedback

- circuit and the power consumption of the NIC circuit, two several kilo-ohm of resistors are preferred.

- 3) The input bias current and input offset voltage of the Op-Amp should be small. When the positive feedback network is introduced, the input bias current and input offset voltage are too large which leads to saturation of the Op-Amp output voltage. Therefore, it is advised to select a precision Op-Amp.

- 4) The Op-Amp should have enough driving capacity. The output current capability of the op-amp should be greater than the maximum value of the CM noise current flowing through the CM choke, since the Op-Amp should produce a compensation current to counteract the noisy current introduced by the EPCs of the CM choke windings.

- 5) When the NIC circuit is applied in a practical power converter, the NIC circuit should be paralleled to one of the CM choke windings that is connected to the negative bus of the input power supply. In addition, the maximum voltage of the CM choke does not exceed the maximum rated voltage of the Op-Amp.

- 6) The Op-Amp should have an isolated power supply. The ground of the Op-Amp should be connected to the converter's case in series with the EMI measurement earth. The power supply of the Op-Amp comes from internal power supply of the converter which means they are two different grounds.

- 7) The parasitic inductance in the NIC circuit should be small. Because the NIC needs to work in a high frequency band, passive devices with a low ESL are suggested. Furthermore, the PCB wires should be as short as possible.

In order to meet the aforementioned criteria, a precision Op-Amp LM4562 from Texas Instruments is chosen. When the supply voltage is  $\pm 15$  V, the gain bandwidth product can be as high as 55 MHz. The input bias current and input offset voltage are 10 nA and  $\pm 0.1$  mV, respectively. An isolated module power supply VWRAT2-D24-D15-SMT is used to supply the NIC. The input voltage ranges from 18 to 36  $V_{DC}$  and the output voltage is  $\pm 15$   $V_{DC}$ . The NIC circuit is designed as shown in Fig. 12, and the size of the NIC printed circuit board including all of the devices is 25 mm (length) × 32 mm (width) × 9.5 mm (height).

# C. Generation of Negative Capacitance

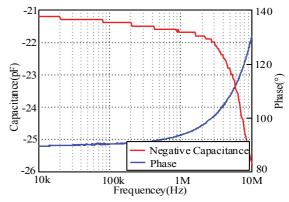

To validate the function of the negative capacitance, a 25 pF capacitor and two 4.99 k $\Omega$  resistors are chosen for  $C_N$ ,  $R_I$  and  $R_2$ . The capacitance and phase extracted from the imaginary part of the NIC input impedance are shown in Fig. 13. The measured equivalent negative capacitance is between -21.26 to -25.78 pF which is almost equal to the theoretical value -25 pF. The actual negative capacitance varies somewhat due to the variations in real components as well as the effect

Fig. 12. Photo of an NIC Circuit.

Fig. 13. Negative capacitance generated by the NIC.

of PCB conductors' parasitic parameters [18]. In addition, the finite gain and bandwidth of the operational amplifier circuit have significant influences on the NIC performance [19].

#### IV. EPC CANCELLATION FOR THE CM CHOKE

EPC cancellation for a CM choke using the negative capacitance generated by the NIC will be tested and verified in this section.

# A. EPC Cancellation for P and S Windings

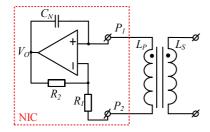

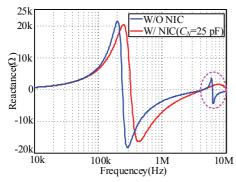

According to the measurement results in the last section, the total EPC of two windings is  $C_{CM}$  =46.93 pF, and the EPCs of the P winding and the S winding are  $C_P = 25.21 \text{ pF}$ and  $C_s$ =21.72 pF. In order to verify the cancellation effect of the negative capacitance generated by the NIC on the EPC of CM chokes, two designed NIC are paralleled with P winding and S winding. With the S winding being open circuited, a 25 pF capacitor is selected as  $C_N$  to cancel the EPC of the Pwinding. The connection structure between the NIC and the CM choke is shown in Fig. 14. The negative capacitance of the NIC tested by an impedance analyzer is -21.26 pF. The reactance of the P winding versus the frequency before and after adding the NIC circuit is shown in Fig. 15. The resonance frequency is increased from 273.65 kHz to 318.98 kHz, and the remaining EPC is 25.92 pF. The total EPC of the CM choke minus the negative capacitance parallel with the P winding is 25.67 pF, which is consistent with the measured results. The second resonance frequency at 5.95

Fig. 14. Diagram of the CM choke paralleled with NIC.

Fig. 15. Measured reactance of the P winding with and without the NIC.

Fig. 16. Measured reactance of the *S* winding with and without the NIC.

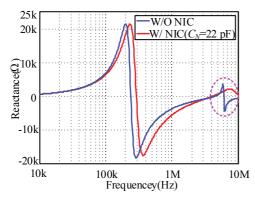

MHz is caused by the leakage inductance and the EPC of the P winding. Since the effect of the EPC is cancelled after adding the NIC, the resonance frequency is removed. Only the leakage inductance characteristic is reflected in this frequency band, as shown in the dotted line region in Fig. 15, which indirectly verifies that the EPC of the P winding is cancelled. Similarly, with the P winding being open circuited, a 22 pF capacitor is selected as  $C_N$  to cancel the EPC of the S winding. The reactance versus the frequency of the S winding before and after adding the NIC is shown in Fig. 16. Experimental results verify that the NIC can cancel the EPC of the two windings very well. In practical applications, only one NIC circuit needs to be installed and it can be connected in parallel with any winding. The value of  $C_N$  in this NIC circuit is the sum of the EPCs in two windings. The detail reasons are explained in section IV A.

Fig. 17. Platform for the insert loss measurement of a CM filter.

Fig. 18. Insertion loss of a CM filter with and without an NIC.

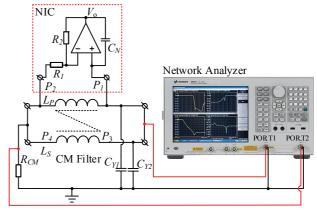

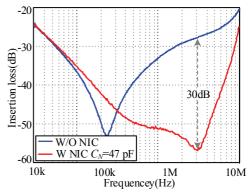

# B. Application of the CM Filter

A CL type CM filter is constructed by applying this CM choke and two 1nF Y-capacitors. The NIC is parallel to one of the CM choke windings. In addition, a 47 pF capacitor is chosen as  $C_N$ . An Agilent E5061B network analyzer is used in the experiments. The insertion loss measurement platform for the CM filters is built and shown in Fig. 17 [5]. The measured insertion loss versus the frequency with and without the NIC results are compared from 30 kHz to 10MHz as shown in Fig. 18. The filtering performance is significantly promoted from 300 kHz to 10 MHz and a 30 dB improvement is obtained at 3.2 MHz.

# V. EMI NOISE MEASUREMENTS

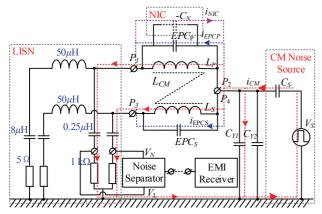

# A. Application of the CM Noise Equivalent Circuit

The CM conducted noise generated by the SMPS is caused by the displacement current due to the high dv/dt across the parasitic capacitances at the switching time. Based on the CM noise generation mechanism of the SMPS [4], a CM noise equivalent circuit is built to investigate the improvement of CM filter performance. The CM conducted EMI measurement platform consists of a noise source  $V_S$ , a lumped parasitic capacitance  $C_S$ , a CL type CM filter, two line stabilization networks (LISN), a CM noise separator, and an EMI receiver,

Fig. 19. Platform for the CM conducted measurement and the CM noise propagation paths of a CM equivalent circuit.

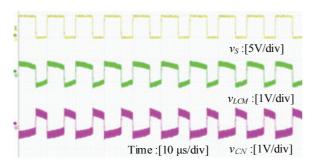

Fig. 20. Key waveforms of a CM noise equivalent circuit.

as shown in Fig. 19. The CM noise source represents the time domain voltage waveform of the power switching devices in the SMPS. C<sub>S</sub> is the lumped capacitance parameter, which includes the parasitic capacitances between heat sink and the earth as well as those between the high dv/dt voltage nodes on the PCB conductors and the earth, etc. In this circuit, the noise source is produced with a signal generator. The main parameters of the noise source are: switching frequency  $f_s$ =100 kHz, high level amplitude  $V_P$ =5 V, rising and falling time  $t_r = t_f = 100$  ns, and duty cycle D = 60 %. In addition, the value of Cs is set to 66 pF with reference to the parasitic capacitances in practical power converters. A CL type CM filter is constructed with a CM choke  $L_{CM}$  and two Y-capacitors  $C_{YI}$  and  $C_{Y2}$ . Both the L and N lines are connected through a LISN to the EMI measurement earth. The CM noise is separated by a CM noise separator. Then it is sent to the EMI receiver.

The mechanism of the EPC cancellation is that the NIC circuit injects a compensation current to cancel the noise current caused by the EPCs. The compensation current should have the same amplitudes and opposite directions with the sum of the currents flowing through the EPCs of the CM choke's two windings. This can be expresses as:

$$i_{NIC} = i_{EPC_p} + i_{EPC_s} \tag{6}$$

Since the current is too small, it is not easy to measure. The voltage is used to evaluate the cancellation effect. The voltage

Fig. 21. Platform for the CM conducted EMI measurement.

Fig. 22. Measured peak CM noises with three different measurement conditions in a CM equivalent circuit.

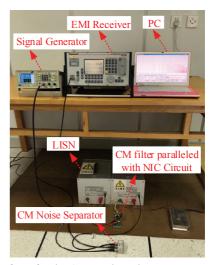

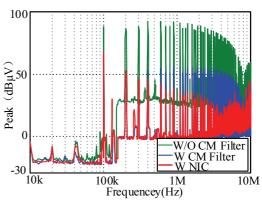

between the P or S winding of the CM choke and  $C_N$  in the NIC should have the same amplitudes and opposite phases. Measured key waveforms of the CM equivalent circuit are shown in Fig. 20. It can be observed that  $V_{LCM}$  and  $V_{CN}$  are out-of-phase which satisfies the condition of the EPC cancellation. To verify the effectiveness of the EPC cancellation technique in terms of improving the CM filter performance, three test conditions have been implemented including without the CM filter, with the CM filter, and with the CM filter paralleled with the NIC circuit. The CM conducted noise is measured in the electromagnetic shielding chamber. During the test process, the LISN uses a schwarzbeck mess-elektronik NNBL8226, the CM noise separator utilizes a Mini-Circuit ZSC-2-2+, and the EMI receiver employs a Schaffner SCR3502. The power converter used in this design is an aeronautical static converter, which is applied to military aircraft. The MIL-STD-461 CE102 standard is adopted with peak noise requirements. The measured frequency bandwidth is from 10 kHz to 10MHz. The CM conducted EMI measurement platform is shown in Fig. 21. CM noise test results under three different conditions are illustrated in Fig. 22. The CM noise is reduced with the CM

Fig. 23. Schematic diagram of an NIC circuit installed in the power converter.

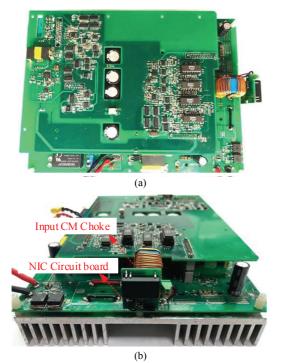

Fig. 24. Photo of the converter used in the experiment. (a) Flyback converter. (b) Position of the NIC circuit in the input CM filter.

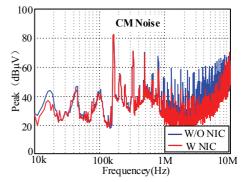

filter in the whole frequency bandwidth, and the CM noise is further mitigated after adding the NIC circuit above 300 kHz. There is a 34 dB $\mu V$  improvement at 4 MHz. When the frequency is less than 300 KHz, the CM choke is inductive. The CM noise is mainly suppressed by the inductive reactance, and the CM current flowing through the EPCs is negligible. Therefore, the NIC does not exhibit the cancellation effect. When the EPC dominates the CM impedance, the NIC gradually has a cancellation effect.

# B. Application in Practical Power Converters

To further verify the effectiveness of the NIC, it is applied to an input CM filter in a practical power converter. When the NIC circuit is applied in this converter, in order to prevent the input voltage from becoming too high to exceed the Op-Amp

Fig. 25. Measured peak CM noises with the EPC cancellation technique in a practical converter.

Fig. 26. Measured peak DM noises with and without the NIC in a practical converter.

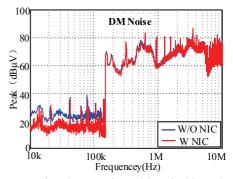

withstand maximum rated voltage, the position of the NIC circuit added in the power converter has specific requirements. The NIC circuit should be parallel to one of the CM choke's windings, which is connected to the negative bus of the input power supply. A schematic diagram of the NIC circuit installed in the power converter is shown in Fig. 23. Under this connection structure, the maximum operating voltage of the Op-Amp in the NIC circuit is equal to the peak voltage of the CM choke. A flyback converter is chosen and the specifications of the flyback converter are given as follows. The input and output voltage are 28  $V_{DC}$  and 180  $V_{DC}$ , respectively. The output power is 100-W, and the switching frequency is 160 kHz. The whole structure of the converter system is shown in Fig. 24. The power supply of the NIC circuit comes directly from the input bus voltage of the flyback converter. The size of the NIC is small. Thus, it is installed near the CM choke and does not have a great influence on the original converter structure. In order to reflect the effect of the NIC on the improvement of the CM filter attenuation characteristics during the EMI noise test process, the influence of the near magnetic field coupling should be minimized. The CM filter and the NIC circuit are shielded by a grounded copper foil, and the input power lines are twisted to minimize the loop area of the magnetic field coupling [20]. Using the same EMI noise measurement platform, the CM noises are measured before and after adding the NIC circuit in the input CM filter of the flyback converter, as shown in Fig. 25. The measurement results show that the CM noise with the EPC cancellation has a lower value than that without the EPC cancellation above the second switching frequency harmonic. A 21.3 dB $\mu$ V improvement is obtained at 3.75 MHz. In addition, the DM noises with and without the NIC circuit are also tested using the DM noise separator Mini-Circuit ZSCJ-2-2+, as shown in Fig. 26. Experimental results show that the NIC has no effect on the DM noise spectrum. Therefore, the NIC can effectively improve the high frequency filtering performance of CM filters.

# VI. CONCLUSIONS

In this paper, an EPC cancellation technique is proposed to improve the filtering performance of CM filters. Based on a CM choke equivalent circuit, the EPCs of the CM choke are accurately calculated. The operating principle of the NIC as well as the EPC cancellation mechanism are analyzed in detail. Then the NIC circuit is designed with the features of a simple topology, small size and convenient implementation. The negative capacitance can be quantitatively acquired without a trial-and-error process. The impedance characteristics of the CM choke in the parallel with negative capacitances generated by the NIC are obtained and compared using an impedance analyzer, and the insertion loss of a CL type CM filter added to the NIC circuit is measured under the test conditions of a small signal excitation with a network analyzer. Furthermore, the CM filter added with the NIC circuit is applied to a 100-W flyback converter to verify the effects of the CM noise reduction. In the frequency bandwidth where the EPC deteriorates the attenuation characteristics of the CM filter, more than 20 dBµV CM noise attenuation is achieved. Both small signal and EMI measurement results verify that the proposed technique can effectively cancel the EPC and improve the CM filter's high frequency filtering performance.

#### ACKNOWLEDGMENT

This work was supported by the National Natural Science Foundation of China under grant No.51777094.

# REFERENCES

- [1] Y. B. Chu and S. Wang, "A generalized common-mode current cancellation approach for power converters," *IEEE Trans. Ind. Electron.*, Vol. 62, No. 7, pp. 4130-4140, Jul. 2015.

- [2] K. H. Lee, B. G. Kang, Y. Choi, and S. K. Chung, "Design and implementation of an active EMI filter," *J. Power Electron.*, Vol. 16, No.3, pp. 1236-1243, May 2016.

- [3] X. C, Huang, J. J. Feng, F. C. Lee, Q. Li, and Y. C. Yang, "Conducted EMI analysis and filter design for MHz active clamp flyback front-end converter," *Proc. IEEE APEC*, pp. 1534-1540, 2016.

- [4] Y. Murata, K, Takahashi. T, Kanamoto, and M, Kubota, "Analysis of parasitic couplings in EMI filters and coupling

- reduction methods," *IEEE Trans. Electromagn. Compat,* Vol. 59, No. 6, pp. 1880-1886, Dec. 2017.

- [5] C. K. Lee, D. T. Xu, B, H, pong, S. Kiratipongvoot, and W. Man, "A three-winding common mode inductor," *IEEE Trans. Ind. Electron.*, Vol. 32, No. 7, pp. 5180-5187, Jul. 2017.

- [6] B. G. Kang, S. K. Chung, J. S. Won, and H. S. Kim, "EMI reduction technique of flyback converter based on capacitance model of transformer with wire shield," in *Proc. IEEE-ECCE*, pp. 163-169, 2015.

- [7] Y. J. Bai, X. Yang, D. Zhang, W. J. Chen, and W. H. Hu, "Conducted EMI mitigation schemes in isolated switchingmode power supply without the need of a Y-capacitor," *IEEE Trans. Power Electron.*, Vol. 32, No. 4, pp. 2687-2703, April. 2017.

- [8] S. Wang, F. C. Lee, D. Y. Chen, and W. G. Odendaal, "Effects of parasitic parameters on EMI filter performance," *IEEE Trans. Power Electron.*, Vol. 19, No. 3, pp. 869-877, May 2004.

- [9] S. Wang, F. C. Lee, and J. D. V. Wyk, "A study of integration of parasitic cancellation techniques for EMI filter design with discrete components," *IEEE Trans. Power Electron,* Vol. 23, No. 6, pp. 3094-3102, Nov. 2008.

- [10] S. Wang, D. V. W. Jacobus, and C. F. Lee, "Effects of interactions between filter parasitics and power interconnects on EMI filter performance," *IEEE Trans. Ind. Electron.*, Vol. 54, No. 6, pp. 3344-3352, Dec. 2007.

- [11] R, G, Chen, J. D. V. Wyk, S. Wang, and W.G. Odendaal, "Improving the characteristics of integrated EMI filters by embedded conductive Layers," *IEEE Trans. Power Electron.* Vol. 20, No. 3, pp. 611-619, May 2005.

- [12] H. F. Huang, M. Ye, and S. Y. Liu, "Equivalent parallel capacitance cancellation of integrated EMI filter using coupled components," in *Proc. IEEE Int. Symp. Electromagn. Compat.*, pp. 133-136, 2012.

- [13] S. Wang, C. F. Lee, and D.V.W. Jacobus, "Design of inductor winding capacitance cancellation for EMI suppression," *IEEE Trans. Power Electron.*, Vol. 21, No. 6, pp. 1825-1832, Nov. 2006.

- [14] W. H. Tan, X. Margueron, T. Duquesne, and N. Idir, "An improved parasitic capacitance cancellation method for planar differential mode inductor in EMI filters," in *Proc. IEEE CIPS*, pp. 1-6, 2012.

- [15] S. Wang, C. F. Lee, and D. V. W. Jacobus, "Inductor winding capacitance cancellation using mutual capacitance concept for noise reduction application," *IEEE Trans. Electromagn. Compat.*, Vol. 48, No. 2, pp. 311-318. May 2006.

- [16] T. C. Neugebauer and D. J. Perreault, "Parasitic capacitance cancellation in filter inductors," *IEEE Trans. Power Electron.*, Vol. 21, No. 1, pp. 282-288, Jan. 2006.

- [17] G. D. Dong, F. H. Zhang, and Wuji Meng, "Equivalent parallel capacitance cancellation for improving the characteristics of CM filters using negative impedance converter," in *Proc. IEEE ICPES*, pp. 29-33, 2018.

- [18] L. Batel, L. Rudantet, J. F. Pintos, and K. Mahdjoubi, "Sensitivity of negative impedance converter circuit with respect to PCB design effects" in *Proc. IEEE iWAT*, pp. 221-224, 2015.

- [19] D. V. Belenko, A. A. Golovkov, and E. I. Mozhaeva, "Operational amplifier finite gain and bandwidth influence to non-foster impedance matching," in *Proc. IEEE EIConRus*, pp. 1233-1235, 2017.

- [20] L. M. Feng, W. Chen. H. L. Chen, and M. M. Qian, "Study on the conducted EMI due to radiated coupling in SMPS" in *Proc. IEEE APEC*, pp. 1048-2334, 2006.

Guangdong Dong was born in Henan, China, in 1988. He received his B.S. degree in Electrical Engineering from Anyang Normal University, Anyang, China, in 2012; and his M.S. degree in Electrical Engineering from Xidian University, Xi'an, China, in 2015. He is presently working toward his Ph.D. degree in Electrical Engineering at the Nanjing

University of Aeronautics and Astronautics (NUAA), Nanjing, China. His current research interests include EMI filter modeling, transformer modeling, EMI prediction and EMI reduction techniques in switched-mode power supplies (SMPSs).

Fanghua Zhang was born in Shandong, China, in 1974. He received his B.S. degree in Automation and Electrical Engineering from Jinan University, Jinan, China, in 1999; and his Ph.D. degree in Electrical Engineering from the Nanjing University of Aeronautics and Astronautics (NUAA), Nanjing, China, in 2004. In June 2004, he began working as a

Lecturer in the College of Automation Engineering, NUAA, where he became an Associate Professor in March 2006. His current research interests include dc-dc converters, high-performance aeronautical static inverters for aerospace applications, power electronic system stability and power quality.