203

# 전류 감지 회로를 이용한 빠른 과도응답특성을 갖는 capless LDO 레귤레이터

# Capless Low Drop Out Regulator With Fast Transient Response Using Current Sensing Circuit

정 준 모\*

Jun-Mo Jung\*\*

#### **Abstract**

This paper present a capless low drop out regulator (LDO) that improves the load transient response characteristics by using a current regulator. A voltage regulator circuit is placed between the error amplifier and the pass transistor inside the LDO regulator to improve the current characteristics of the voltage line, The proposed fast transient LDO structure was designed by a 0.18 um process with cadence's virtuoso simulation. according to test results, the proposed circuit has a improved transient characteristics compare with conventional LDO. the simulation results show that the transient of rising increases from 1.954 us to 1.378 us and the transient of falling decreases from 19.48 us to 13.33 us compared with conventional capless LDO. this Result has improved response rate of about 29%, 28%.

#### 요 약

본 논문에서는 전류 제어 회로를 이용하여 load Transient response 특성을 향상시킨 capless LDO(low drop-out) 레귤레이터를 제안하였다. LDO 레귤레이터 내부의 오차증폭기와 패스 트랜지스터 사이에 전류 조절 회로를 두어 전압 라인에 들어오는 전류특성을 개선시켜 기존의 LDO 레귤레이터보다 향상된 transient 응답특성을 갖는다. 제안된 회로는 cadence의 virtuoso, spectre 시뮬레이터를 이용하여 0.18 um 공정에서 특성을 분석하였다. 실험 결과에 따르면, 제안된 회로 구성을 이용한 LDO의 load transient response는 기존 LDO과 비교하여 부하 전류가 rising time인 경우 1.954 us에서 1.378 us, falling time인 경우 19.48 us에서 13.33 us으로 약 29%, 28% 개선된 응답속도를 가진다.

Key words: Capless LDO Regulator, Pass Transistor, Low Drop Out Regulator, Load Transient Response

ISSN: 1226-7244 (Print) ISSN: 2288-243X (Online)

논문번호 19-02-32

E-mail: jjmo@skuniv.ac.kr, Tel: +82-2-940-7732

\* Acknowledgment

Manuscript received Jun. 17, 2019; revised Jun. 20, 2019; accepted Jun. 26, 2019.

This is an Open-Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License(http://creativecommons.org/licenses/by-nc/3.0) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

#### 1. 서론

모바일 기기들은 스마트폰의 등장 이후 하나의 모바일 기기로 다른 전자기기를 컨트롤하는 등 다 양한 작업을 수행하기 위하여 고성능, 다기능 시스 템이 하나의 모바일 기기에 구현됨에 따라 소비전 력이 급격하게 증가하였다. 전자, 전기 시스템에서 전원 공급 및 조절은 필수적인 기능이다. 스마트폰, 태블릿 PC 등의 휴대기기들은 안정적인 에너지의 공급 없이는 정상적인 동작을 할 수 없다. 레귤레 이터는 예측할 수 없고 노이즈가 있는 에너지 공급

<sup>\*</sup> Dept. of Electronics, Seokyeong University

<sup>★</sup> Corresponding author

원을 부하 전압에 독립적이며 안정하고 일정한 전원을 공급 할 수 있도록 한다. 또한 Power Management IC(PMIC)는 입력 전력을 적절한 출력 전력으로 변환하여 각 시스템이 요구하는 전원을 공급하는 목적을 가진 장치이다[1]. 이런 PMIC는 전력 변환 과정에서 빠르면서도 안정적인 전원 공급과 높은 변환 효율이 가장 중요한 요소이다. PMIC는 크게 선형 레귤레이터인 LDO 레귤레이터와 스위칭 레귤레이터로 나누어진다. 선형 레귤레이터는 응답속도가 빠르고 노이즈가 적지만 상대적으로 낮은 효율을 갖는다. 반면, 스위칭 레귤레이터는 효율은 높지만 외부 소자가 필요하며 노이즈가 많기 때문에 고성능을 위한 아날로그 시스템에서는 선형 레귤레이터 가 많이 사용된다[2].

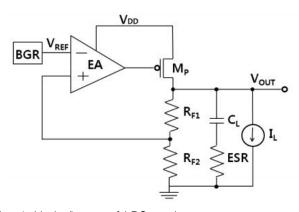

Fig. 1. block diagram of LDO regulator. 그림 1. LDO 레귤레이터의 블록 다이어그램

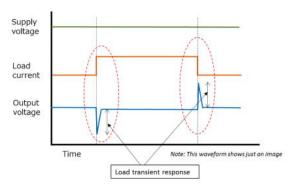

LDO 성능에서 중요한 요소를 확인하려면 다음과 같이 볼 수 있다. 그림 2의 로드 전류에 따른 출력 전압의 빠른 시간을 가지기 위해서는 빠른 속도 및 높은 슬루율을 가지는 증폭기를 설계해야 하고, 출력 전압이 빠르게 정상 전압을 가지게 하기 위해서는 출력 커패시터의 크기를 줄여야 한다. 또한 출력전압의 델타량을 감소시키기 위해서는 커패시터의 크기를 크게 해야 한다. 특정 기기의 성능을 만족시키기 위해서는 각각의 Trade-Off 관계가 존재하게 된다. 외부에 큰 커패시터의 사용은 제품의소형화를 어렵게 한다[3].

LDO 회로는 패스 트랜지스터, 출력전압을 고정시키기 위한 오차 증폭기, 피드백 저항, 그리고 큰 외부 출력 커패시터로 구성 되어져 있다. 최근 system on chip(SOC)의 경향에 따라 LDO 등의 전원 회로도 외부 핀 절약과 시스템 성능향상을 위해 칩에

내장되는 추세이다. 칩 내부에 LDO를 내장하게 되면 기존에 외부에 LDO를 장착하는 기술에 비해 시스템 크기와 노이즈 발생 요인을 감소시키고, 전압 변동률의 감소 및 부하의 과도현상으로 인한 전압스파이크를 제거 할 수 있다. 또한 그림 1의 일반적인 LDO는 외부 커패시터가 크므로 첫 번째 극점이 LDO 출력 단에 위치하지만 외부 커패시터가 없는 LDO는 첫 번째 극점이 오차 증폭기에 의해 발생하고 두 번째 극점은 LDO 출력 단에서 발생한다[3].

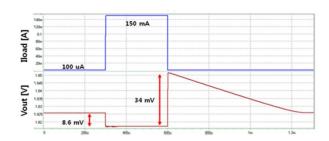

Fig. 2. load transient response of conventional LDO. 그림 2. LDO 레귤레이터의 과도 응답

본 논문에서는 커패시터가 없이 빠른 과도응답을 가지는 LDO를 제안하였으며 패스 트랜지스터와 오차증폭기 사이에 흔들리는 전류 감지 회로를 추 가하여 기존의 LDO 레귤레이터 보다 더욱 향상된 load 과도응답속도와 작은 면적을 갖는 선형 레귤 레이터를 제안한다[4].

### Ⅱ. 본론

### 1. 제안된 Low Drop-Out 레귤레이터

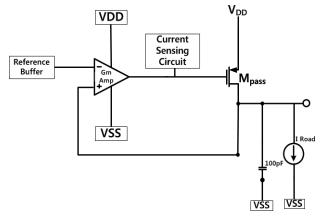

Fig. 3. proposed capless LDO regulator. 그림 3. 제안된 커패시터 없는 LDO 레귤레이터

그림 3는 본 논문에서 제안하는 LDO 레귤레이터의의 블록 다이어그램이다. 기존 LDO 레귤레이터의공급 전원단과 패스 트랜지스터 게이트 입력단 사이에 전류 감지 회로를 추가하였다. 또한 커패시터가 conventional LDO에 비해 없는 것이 아니라 본논문에서는 100 pF 크기에 커패시터가 존재한다[5]. 설계자의 의도나 제품의 특성에 따라 0 pF~100 pF 사이 커패시터의 크기를 사용 할 수 있다. 또한 기존 amp와는 다르게 gm amp를 사용했기때문에 출력저항은 아래의 식과 같이 표현 할 수 있다[6][7].

$$Rout = r_{0,pass}//r_{0,load}//\frac{1}{gm_{amp}} \tag{1} \label{eq:rout}$$

conventional LDO와는 dominant Pole의 차이가 존재하기 때문에 제안된 capless LDO는 아래 식처럼 표현 할 수 있다.

$$P_{dominant} = \frac{Gm_{amp}}{C_{out}}, \ P_a = \frac{1}{R_{outAmp}^* Cpass} \eqno(2)$$

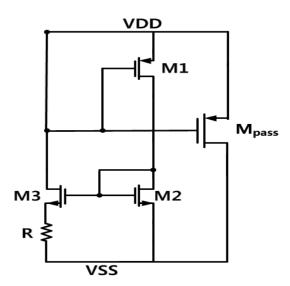

그림 4는 제안된 전류 감지 회로이다. 1개의 PMOS와 2개의 NMOS로 구성되어 있으며, 공급 전원 라인과 패스 트랜지스터 사이에서 동작한다. LDO의 출력전압이 상승하게 된다면 오차증폭기의 출력이 상승하게 되고, 그로 인하여 M1 게이트 전압이 상승하고, M2, M3의 게이트 전압이 하강한다. 따라서 오차증폭기로 인해 상승된 출력 전압을

Fig. 4. proposed current transient sensing circuit. 그림 4. 제안된 전류 감지 회로

조금 더 빠르게 상승시켜주는 효과를 갖는다. 이로 인하여 패스 트랜지스터의 게이트의 전압이 상승하는 효과를 가져 올 수 있기 때문에 패스 트랜지스터의 전류는 감소하게 되며, 기존 출력대비 상승한 전압을 다시 하강시켜주는 효과를 갖는다. LDO의 출력전압이 감소하게 되면 오차증폭기의 출력이 기존 대비 감소하게 되면서 M1 게이트 전압이하강하게 되고, M2, M3의 게이트 전압이 상승하게된다. 따라서 오차증폭기로 인해 하강된 출력 전압을 보다 더 빠르게 하강시켜 패스 트랜지스터의 게이트단의 전압이 하강하게 된다. 결국 패스 트랜지스터의 게이트의 전압이 하강하는 효과를 가져 올수 있기 때문에 패스 트랜지스터의 전류는 상승할 것이고, 기존 출력대비 하강한 전압을 다시 상승시켜주는 효과를 갖는다.

## 2. 시뮬레이션 결과

본 논문에서 제안하는 LDO 레귤레이터는 cadence 의 virtuso, pectre 툴을 통해 시뮬레이션 되었고, 0.18 um BCD 공정을 이용하였다. conventional LDO는 2.7 V~4.5 V의 입력전압, 1.2 V~3.3 V의 출력전압 범위를 가지며, 150 mA의 출력 전류를 공급한다. 또한 출력 커패시터는 3.2 uF을 사용하였다. 그리고 proposed LDO는 3 V~3.3 V의 입력전압을 가지며, 2.7 V~3 V의 출력 전압 범위를 가진다. 제안된 LDO는 capless 레귤레이터이기 때문에 출력커패시터는 100 pF을 사용하였다[8].

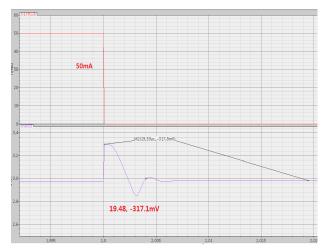

Fig. 5. transient response of the LDO regulator. 그림 5. LDO 레귤레이터의 과도응답

그림 5는 로드 레귤레이션 시뮬레이션 결과이며, 부하전류를 100 uA~150 mA로 변화 시켰을 때 출 력 전압은 8.6 mV 변화하였고, 부하전류를 150 mA~100 uA로 변화시켰을 때 출력 전압은 34 mV 변화하였다. 그림 6은 제안된 Capless LDO의 시뮬 레이션 결과이다. 커패시터가 100 pF이기 때문에

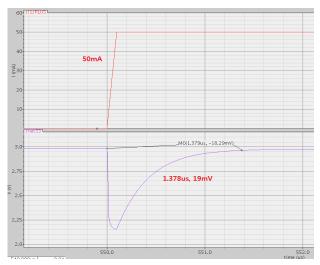

Fig. 6. transient response of the proposed LDO regulator. 그림 6. 제안된 LDO 레귤레이터의 과도응답

Fig. 7. transient response of the proposed LDO regulator. 그림 7. 제안된 LDO 레귤레이터의 과도응답

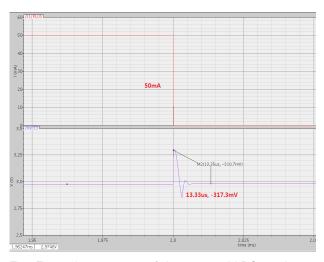

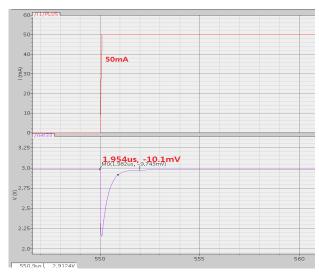

Fig. 8. transient response of the capless LDO regulator. 그림 8. capless LDO 레귤레이터의 과도응답

부하전류에 따른 전압의 언더슈트가 존재하지만 빠른 응답속도를 보여준다. 부하전류를 50 mA로 변화시킬 때 1.378 us안에 본래의 출력전압을 찾는다.

Fig. 9. transient response of the capless LDO regulator. 그림 9. capless LDO 레귤레이터의 과도응답

Table 1. voltage simulation result. 표 1. 전압 시뮬레이션 결과

| Load Transient<br>Response  | Rising Time | Falling Time |

|-----------------------------|-------------|--------------|

| conventional capless<br>LDO | -10.1 mV    | −317.1 mV    |

| proposed capless LDO        | -13 mV      | −317.3 mV    |

Table 2. load transient response result.

### 표 2. 과도응답시간 결과

| Load Transient<br>Response  | Rising Time | Falling Time |

|-----------------------------|-------------|--------------|

| conventional LDO            | 64.82 us    | 48.67 us     |

| conventional capless<br>LDO | 1.954 us    | 19.48 us     |

| proposed capless LDO        | 1.378 us    | 13.33 us     |

Table 3. proposed LDO data.

표 3. 제안된 회로 데이터

| proposed circuit with capless LDO regulator |                    |  |

|---------------------------------------------|--------------------|--|

| input voltage                               | 3.3 V              |  |

| output voltage                              | 3 V                |  |

| reference voltage                           | 1.2 V              |  |

| dropout voltage                             | 300 mV             |  |

| load transient response<br>(I Load=50mA)    | Δ13 mV, Δ317.1 mV  |  |

| load transient response<br>(I Load=50mA)    | 1.378 us, 13.33 us |  |

그림 6, 7은 제안된 회로를 추가하여 빠른 과도응 답 특성을 가지는 capless LDO의 시뮬레이션 결과 이다. 그림 8, 9는 conventional Capless LDO의 과도 응답 특성 시뮬레이션 결과이다. 시뮬레이션 결과에 따르면, load전류가 50mA로 상승할 때, conventional LDO는 -836.2 uV의 변화가 있었고 load 전류가 50 mA 떨어질 때는 892.6 uV의 변화가 존재하였다. 또한 propoesd capless LDO는 - 13 mV, -317.3 mV 의 변화를 가져 왔다. conventional LDO는 커패시 터의 크기 때문에 전압 변화량이 작을 수 밖에 없 다. 하지만 응답시간을 보게 된다면 conventional LDO는 64.82 us, 48.67 us의 시간 안에 피드백을 거쳐 정상적인 출력전압으로 돌아오게 되었고, proposed capless LDO 는 1.378 us, 13.33 us의 시간동안 빠 른 피드백을 거쳐 정상적인 출력전압으로 돌아오게 되었다. 제안된 LDO는 응답시간이 conventional LDO 보다 개선되었다. 제안된 LDO 회로는 conventional capless LDO 보다 rising time때는 29%, falling time때는 28% 향상되어진 과도응답을 가지게 되었 고, 커패시터가 존재하는 conventional LDO보다는 97.8% 향상된 빠른 과도응답을 가지게 되었다.

# Ⅲ. 결론

본 논문에서는 기존 LDO 레귤레이터와는 다르게 커패시터 없는 capless LDO 레귤레이터를 제안하였다. 또한 공급전원단과 패스 트랜지스터 게이트 입력단 사이에 전류 감지 회로를 추가하여 load transient response의 응답시간을 개선시킨 capless LDO를 제안하였다. 시뮬레이션을 통하여 전류 감지회로를 추가하여 기존의 capless LDO 보다 전류에 대한 transient을 개선시켰다. 제안된 LDO는 기존 LDO보다 rising time때는 29%, falling time때는 28% 향상되어진 응답속도를 가지게 되었다. 그결과 출력 전류 변동에도 빠른 응답속도와 커패시터를 작게 함으로써 적은 면적을 가지게 된 LDO 레귤레이터를 개발하였다.

### References

[1] Al-Shyoukh, M, Hoi Lee; Perez, R, "A Transient-Enhanced Low-Quiescent Current Low-

Dropout Regulator With Buffer Impedance Attenuation," *Solid-State Circuits, IEEE Journal of,* vol.42, pp.1732–1742, 2007.

DOI: 10.1109/JSSC.2007.900281

- [2] Yong-Seo Koo, Kang-Yoon-Lee, Jae-Hwan Ha, Yil-Suk Yang. "A Design of Power Management IC for CCD Image Sensor," *IKEEE*, vol.13, no.4, pp.63-68, 2009.

- [3] Behzad Razavi, "Design of Analog CMOS Integrated Circuits," *Hanbit media*, pp.353–406, 2011.

- [4] Liu Zhiming, "A 1.8V LDO voltage regulator with foldback current limit and thermal protection," *Journal of semiconductors*, vol.30, No.8. 2008.

DOI: 10.1088/1674-4926/30/8/085007

- [5] H. Pooya Forghani-Zadeh and Gabriel A. Rincon-Mora(2006) Low-Power CMOS Ramp Generator Circuit for DC-DC Converters. journal. ASP.

- [6] Behzad Razavi, "Design of Analog CMOS Integrated Circuits," *Hanbit media*, pp.353–406, 2011.

- [7] Behzad Razavi, "Design of Analog CMOS Integrated Circuits," *Hanbit media*, pp.295–326, 2011.

- [8] Yong-Seo Koo, "A design of low-area low drop-out regulator using body bias technique," *IEICE Electronics Expresss*, vol.10, no.19, pp.1–12. 2013. DOI: 10.1587/elex.10.20130300

### **BIOGRAPHY**

Jun-Mo Jung (Member)

1985: BS degree in Electronics

Engineering, Hanyang University.

1987: MS degree in Electronics

Engineering, Hanyang University.

1992: PhD degree in Electronics

Engineering, Hanyang University.

1995~presently: assistance professor in Seokyeong University.

main interesting field: integrated circuit, micro processor