https://doi.org/10.7236/JIIBC.2019.19.3.135 JIIBC 2019-3-18

# GaAs HBT 공정을 이용한 주파수 분배 방식의 광대역 구동증폭기 설계

Design for Broadband Drive Amplifier of Frequency Split Type using GaAs HBT Process

김민철\*, 김정현\*\*

# Minchul Kim\*, Junghyun Kim\*\*

요 약 본 논문에서는 L, S 및 C 대역에서 동작하는 주파수 분배 방식의 광대역 구동증폭기를 설계 및 제작하였다. 구동증폭기의 비대역폭이 100% 이상인 경우에는 트랜지스터를 효율적으로 이용하기 어려우며, 특히 주파수 대역에 따라 출력 전력 및 효율의 특성이 민감하게 변하는 전력증폭기를 동작시키기 위해서는 구동증폭기의 특성이 중요하게 작용한다. 본 논문에서는 구동증폭기의 대역폭을 최대화하고, 구동증폭기의 뒤쪽에 위치 할 전력증폭기의 트랜지스터를 효율적으로 이용 할 수 있도록 구동증폭기의 출력을 저대역과 고대역으로 나누어주는 주파수 분배 방식을 적용하였다. 설계된 회로는 GaAs HBT (Heterojunction Bipolar Transistor) 공정 및 9-layer의 SiP (System in Package)를 이용하여 제작하였고, 측정을 통해 성능을 검증하였다. 제작된 회로는 동작 주파수 범위에서 8 dB이상의 이득과 15 dBm이상의 출력전력을 보여주었다.

Abstract In this paper, a frequency split type broadband drive amplifier operating in the L, S and C bands was designed and fabricated. Transistor is difficult to efficiently use when the fractional bandwidth of the drive amplifier is more than 100%, In particular, the characteristics of the driving amplifier are important for operating the power amplifier in which the characteristics of the output power and the efficiency are sensitively changed according to the frequency band. A frequency split methods was applied to maximize the bandwidth of a drive amplifier and to divide the output of the drive amplifier into low band and high band so that the transistor of the power amplifier located at the rear of the drive amplifier can be efficiently used. The designed drive amplifier was fabricated in GaAs HBT technology and 9-layer SiP, and verified by the measurements. The fabricated drive amplifier shows a gain of more than 8 dB and an output power of more than 15 dBm in the operating frequency range.

Key Words: Broadband, Drive amplifier, Frequency split

Received: 12 May, 2019 / Revised: 3 June, 2019 /

Accepted: 7 June, 2019

\*Corresponding Author: junhkim@hanyang.ac.kr

Dept. of Electronic Engineering, Hanyang University, Korea

<sup>\*</sup>정회원, 한양대학교 전자시스템공학과

\*\*정회원, 한양대학교 전자공학부 (교신저자) 접수일자 2019년 5월 12일, 수정완료 2019년 6월 3일 게재확정일자 2019년 6월 7일

## I. 서 론

구동증폭기는 전력증폭기에 전력을 공급하기 위해 사용되며 송신기 구성에 있어서 필수적인 회로이다<sup>[1][2]</sup>.

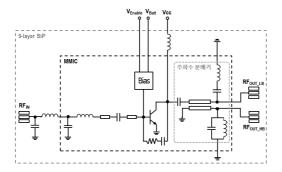

그림 1. 설계된 주파수 방식의 분배 구동증폭기 Fig. 1. Schematic of the designed frequency split type broadband drive amplifier

구동증폭기의 구조 및 성능은 전체 송신기 회로의 특성에 큰 영향을 준다. 특히, 동작 주파수 범위가 넓은 송신기 회로일수록 구동증폭기의 특성은 더 큰 중요성을 갖는다.

비대역폭을 100% 이상 갖는 광대역 증폭기는 일반적 으로 리액티브 정합 구조<sup>[3][4]</sup> 또는 분산 증폭기의 구조 [5][6]를 채택한다. 리액티브 정합 구조의 경우, 분산 증폭 기 구조에 비해 더 높은 이득을 갖지만 정합 특성에 따라 동작 대역에서의 이득 편차가 크다는 단점을 가지고 있 다. 반면, 분산증폭기 구조는 리액티브 정합 구조에 비해 낮은 이득을 갖지만 동작대역 내에서 이득의 편차가 적 으며, 저주파 통과 필터 구조를 형성하는 분산증폭기의 특징으로 인해 낮은 주파수에서의 이득을 확보하기에 더 유리하다는 장점을 갖는다. 하지만, 위에서 언급한 두 가 지 구조는 모든 주파수 대역에서 최적의 성능을 낼 수 있 도록 임피던스 정합을 할 수 없으며, 주파수에 따라 최적 의 성능을 낼 수 있는 임피던스가 존재하는 트랜지스터 의 특징으로 인해 동작 주파수 범위가 넓어질수록 증폭 기의 성능이 전반적으로 감소 할 수밖에 없는 한계를 가 지고 있다.

광대역 특성을 갖는 송신기 회로에서 구동증폭기가 효 과적으로 대역을 나누어 전력을 공급 할 수 있다면, 나눠 진 주파수 대역에서 동작하는 전력증폭기들의 대역폭이 줄어들 수 있기 때문에 각 전력증폭기의 출력 전력 및 효 율을 증가 시킬 수 있어 전체 송신기 회로의 성능향상을 기대 할 수 있다.

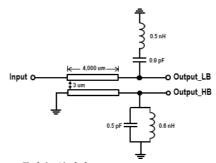

그림 2. 주파수 분배기 Fig. 2. Frequency splitter

본 논문에서는 GaAs HBT 공정 및 9-layer SiP를 이용하여 L, S 및 C 대역에서 동작하며, 저주파 대역 (1 - 4 GHz)과 고주파 대역(4 - 7 GHz)으로 신호를 분배하는 구동증폭기를 설계하여 새로운 송신 구조의 가능성을 확인하는 것에 초점을 두었다. 주파수 분배를 구현하기위해 결합선로 커플러(Coupled line coupler) 구조를 응용하였으며, 설계된 구동증폭기는 측정을 통해 검증하였다.

## Ⅱ. 광대역 구동증폭기 설계

#### 1. 주파수 분배기 설계

그림 1은 제안된 광대역 구동증폭기의 회로도를 보여준다. 구동증폭기는 하나의 트랜지스터와 출력신호를 저대역 및 고대역으로 분배해주는 주파수 분배기로 구성된다. 주파수 분배기의 동작은 일반 다이플렉서와 유사하지만, 결합선로의 특성을 활용하여, 통과대역이 아닌 출력포트의 임피던스가 표준화 된 값이 아니어도 주파수 분배 특성에 큰 영향을 받지 않는 장점을 가지고 있다. 실제 다이플렉서의 설계를 위해서는 저대역 - 고대역 간의격리를 위한 설계의 최적화 과정이 필요하다는 내용이보고된 바 있으며<sup>[7]</sup>, 통과대역이 아닌 출력 포트의 임피던스가 표준화 된 값이 아닐 경우에는 다이플렉서의 기본 동작특성이 변할 수 있는 가능성을 가지고 있다. 무선통신 시스템의 구조 및 동작이 복잡해지고 있는 상황에서 구동증폭기의 특성이 출력 포트 임피던스의 영향이적다는 것은 큰 장점으로 작용할 수 있다.

단순한 결합선로는 입력 신호를 저대역과 고대역으로 나눌 수 없기 때문에, 그림 2와같이 두 개의 공진 회로를 이용하여 주파수 분배 특성을 갖도록 설계하였다. 저대역 의 동작을 위해서는 인덕터와 커패시터를 직렬로 연결하여 공진회로를 구성하였으며, 고대역의 동작의 경우 인덕터와 커패시터를 병렬로 연결한 공진회로를 이용하였다. 직렬 공진회로는 공진 주파수에서 단락시키고, 병렬 공진회로는 공진주파수에서 개방 시킨다는 반대 특성을 이용하였으며, 주파수 분배의 경계 지점을 4.5 GHz로 설정하기 위한 결합선로 및 공진회로의 최적화를 진행하였다.

### 2. 바이어스 회로 및 정합회로 구성

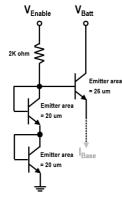

증폭기의 설계를 위해서 트랜지스터의 DC 동작점을 설정하는 것은 가장 기초적이며 중요한 내용이다. BJT는 베이스 전류에 따라 콜렉터 전류가 결정되므로, 동작점설정을 위해서 전류 거울 회로가 필요하며, 온도나 전압의 변화에 민감하지 않도록 설계하는 것이 중요하다. 그림 3은 트랜지스터에 전류를 공급하기 위한 전류 거울회로의 회로도이며,  $V_{Bett}$ 와  $V_{Enable}$  전압을 각각 3.7 V 및 3.25 V로 설정하였을 때 약 350 UA의 전류를 트랜지스터의 베이스에 공급한다.

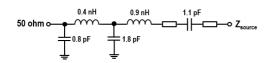

구동증폭기의 성능을 결정하는 가장 중요한 요소는 입력 및 출력의 정합회로이다. 제안된 구조의 구동증폭기는 광대역 특성을 확보하기 위해서, 로드-풀 시뮬레이션을 이용하였다. 로드-풀 시뮬레이션 결과를 기반으로, 그림 4와 같이 여러 단의 정합회로 구조의 입력 정합회로를 채택하였다. 출력단의 경우에는 광대역에서 표준화된 임

그림 3. 전류 거울(바이어스) 회로 Fig. 3. Current mirror(Bias) circuit

그림 4. 입력정합 회로 Fig. 4. Input matching network

피던스에 가까운 특성을 갖는 주파수 분배기 구조의 정 합회로를 이용하여 광대역 특성을 확보하였다.

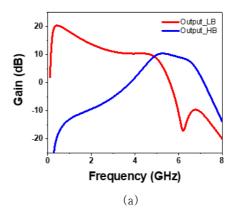

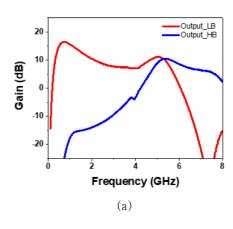

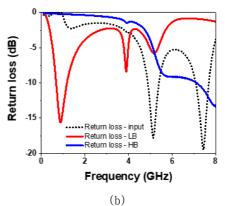

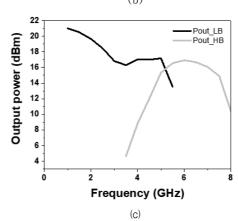

그림 5. 설계된 구동증폭기의 시뮬레이션 결과: (a) 주파수에 따른 이득, (b) 주파수에 따른 반사손실, (c) 주파수에 따른 출력 전력

Fig. 5. Simulation results of the designed drive amplifier according to frequency: (a) gain, (b) return loss, and (c) output power.

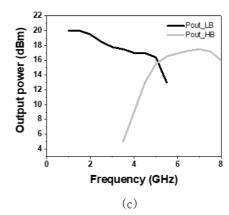

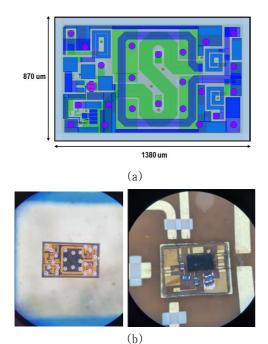

그림 6. 제작된 구동증폭기의 (a)레이아웃, (b)칩 및 모듈사진 Fig. 6. The fabricated drive amplifier: (a) Layout, (b) photograph of chip and module.

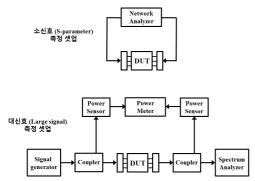

그림 7. 구동증폭기의 측정셋업

Fig. 7. Measurement setup of the fabricated drive amplifier

# Ⅲ. 시뮬레이션 결과 및 분석

그림 5는 설계된 광대역 구동증폭기의 시뮬레이션 결과를 보여준다. 설계된 구동증폭기의 소신호 시뮬레이션을 위해서 -10 dBm의 입력전력을 인가하였으며. 그림 5(a)에서 볼 수 있듯이, 설계된 구동증폭기는 1 GHz부터 7 GHz의 주파수 대역에서 10 dB 이상의 이득을 보였다. 그림 5(b)는 입, 출력 반사손실을 보여주며, 동작대역내

에서 최소 -2 dB 이상을 성능을 보였다. 일반적인 협대역 증폭기의 반사손실에 비해 좋지 않은 성능이지만, 일

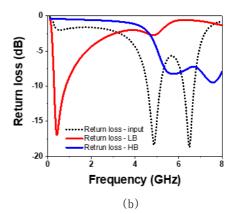

그림 8. 설계된 구동증폭기의 측정 결과: (a) 주파수에 따른 이 득, (b) 주파수에 따른 반사손실, (c) 주파수에 따른 출 력 전력

Fig. 8. Measurement results of the designed drive amplifier according to frequency: (a) gain, (b) return loss, and (c) output power.

반적인 초광대역 증폭기의 특성과는 비슷한 성능을 보였다. 구동증폭기의 출력 전력을 확인하기 위해서 입력 전력은 10 dBm을 인가하였으며, 그림 5(c)에서 볼 수 있듯이, 전체 주파수 동작범위에서 16 dBm 이상의 출력 전력 특성을 보여주었다.

# Ⅳ. 실험 및 결과

설계된 구동증폭기는 GaAs HBT 공정 및 9-layer SiP를 이용하여 제작되었다. 그림 5는 제작된 회로의 레이아웃, 칩 및 모듈의 사진을 보여준다. 칩의 크기는 RF 및 DC 패드를 포함하여 1380 μm × 870 μm이며, 전체 모듈사이즈는 3.2 mm × 2.2 mm이다.

그림 6은 제작된 구동증폭기의 측정에 사용된 셋업의 구성을 보여준다. 구동증폭기의 소신호 동작특성을 확인하기 위해서 네트워크 분석기가 이용되었으며, 대신호 동작특성은 신호발생기, 스펙트럼 분석기 및 파워미터를 이용하여 측정을 진행하였다. 소신호 및 대신호 특성 모두온—웨이퍼 프로브(on—wafer probe)를 이용하여 측정하였다. 입력 및 출력 전력의 정확한 수치를 파악하기 위해, 커플러를 통해 검출된 전력을 파워센서 및 파워미터를 이용하여 모니터링 하였다. 또한 출력 신호의 주파수성분을 정확하게 확인하기 위하여 스펙트럼 분석기를 이용하였으며, 트랜지스터의 비선형 특성으로 인해 발생하는 고조파 성분을 제외하면 입력 및 출력 신호의 주파수가 동일함을 확인하였다. DC 바이어스의 공급을 위해서 와이어 본당(Wire—Bonding)과 전원 공급기를 이용하였다.

그림 8은 제작된 광대역 구동증폭기의 측정결과를 보여준다. 그림 8(a)를 통해 제작된 주파수 분배 방식의 구동증폭기는 1 GHz부터 7 GHz의 주파수 범위에서 8 dB이상의 이득을 증명하였으며. 1 GHz에서는 약 14 dB의이득을 보였다. 그림 8(b)는 입, 출력 반사손실 측정결과를 보여주며, 시뮬레이션 결과 대비 약 0.5 dB에서 1 dB정도 개선되었다. 그림 8(c)는 구동증폭기의 출력 전력특성을 보여주며, 최소 15 dBm 이상의 특성을 보였다. 이득과 마찬가지로 저대역에서 더 높은 출력을 보이는 경향을 가지고 있으며, 1 GHz에서 최대 21 dBm의 출력전력 특성을 보였다.

# V. 결 론

본 논문에서는 주파수 분배 방식으로 동작하는 광대역 의 구동증폭기를 설계하였다. 구동증폭기의 광대역 특성을 확보하기 위해 새로운 방식의 주파수 분배기를 이용하였으며, 직렬 및 병렬 공진회로를 이용하여 최적화하였다. 설계된 구동증폭기는 GaAs HBT 공정을 이용해 제작되었고 9-layer SiP를 이용하여 모듈화 하였다. 설계결과는 측정을 통해 성능을 검증하였다. 측정된 구동증폭기의 성능은 시뮬레이션과 잘 일치된 결과를 보이며, 1 GHz부터 7 GHz의 주파수 대역에서 8 dB 이상의 이득과 15 dBm 이상의 출력전력이 측정되었다.

#### References

- [1] Wan-sik Kim, "Development of W-band Transceiver Module using Manufactured MMIC", The Journal of The Institute of Internet, Broadcasting and Communication, Vol 17, No. 2, pp. 233-237, Apr 2017.

- [2] B. Nam, G. Chae, "Design of a K-band CW Radar Transceiver", Journal of the Korea Academia-Industrial cooperation Society(JKAIS), Vol. 10, No. 7, pp. 1532-1535, 2009.

- [3] G. Mouginot, Z. Ouarch, B. Lefebvre, S. Heckmann, J. Lhortolary, D. Baglieri, D. Floriot, M. Camiade, H. Blanck, M. Le Pipec, D. Mesnager, and P. Le Helleye, "Three stage 6-18 GHz high gain and high power amplifier based on GaN technology," in IEEE MTT-S Int. Microw. Symp. Dig., May 2010, pp. 1392-1395. DOI: https://doi.org/10.1109/MWSYM.2010.5515897

- [4] P. Saad, C. Fager, H. Cao, H. Zirath, and K. Andersson, "Design of a highly efficient 2-4-GHz octave bandwidth GaN-HEMT power amplifier," IEEE Trans. Microw. Theory Tech., vol. 58, no. 7, pp. 1677-1685, Jul. 2010

- DOI: https://doi.org/10.1109/TMTT.2011.2169080

- [5] Z. Xing, L. Roy, and R. E. Amaya, "1 W, highly efficient, ultra-broadband non-uniform distributed power amplifier in GaN," IEEE Microw Compon. Lett., vol. 23, no. 4, pp. 208-210, Apr. 2013. DOI: https://doi.org/10.1109/TMTT.2015.2403843

- [6] J.-C. Kao, P. Chen, P.-C. Huang, and H. Wang, "A novel distributed amplifier with high gain, low noise, and high output power in 0.18-mm CMOS technology," IEEE Trans. Microw. Theory Techn., vol. 61, no.4, pp. 1533-1542, Apr. 2013.

DOI: https://doi.org/10.1109/TMTT.2013.2271614

- [7] Y. Heng, "Design and optimization of a superconducting contiguous diplexer comprising doubly terminated filters," IEEE Trans. Appl. Supercond., vol. 23, no. 4, p. 1501706, Aug. 2013. DOI: https://doi.org/10.1109/TASC.2013.2250284

#### 저 자 소 개

## 김 민 철(정회원)

- •2012년 2월 : 한양대학교 전자시스템 공학과 (공학사)

- •2013년 3월 ~ 현재 : 한양대학교 전자 시스템공학과 석·박사 통합과정

- •주관심분야 : 밀리미터파파 회로 및 RF 전력증폭기 MMIC 설계

#### 김 정 현(정회원) 교신저자

- •1998년 2월 : 성균관대학교 전자공학과 (공학사)

- •2000년 2월 : 서울대학교 전기공학부 (공학석사)

- •2005년 8월 : 서울대학교 전기컴퓨터 공학부 (공학박사)

- •2000년 7월 ~ 2005년 2월 : WavICs 창업 및 설계팀 팀장

- •2005년 2월 ~ 2007년 8월 : ㈜아바고 테크놀로지스 Wireless Semiconductor Division(WSD) 설계그룹 그룹장

- •2007년 9월 ~ 2013년 2월: ㈜아바고 테크놀로지스 WSD 기술자문위원

- •2013년 3월 ~ 2018년9월: 브로드컴 WSD 사외이사

- •2007년 9월 ~ 현재 : 한양대학교 공학대학 전자공학부 교수

- •주요관심분야: 마이크로파/밀리미터파 집적회로 및 모듈, RF 전력증폭기

- •Affiliation: Department of Electonic Engineering, Hanyang University, Ansan 15588, Korea.