J. Adv. Navig. Technol. 23(2): 172-178, Apr. 2019

# 무선통신용 LTCC 다층기판의 수동소자 라이브러리 구현

# Passive Device Library Implementation of LTCC Multilayer Board for Wireless Communications

**조 학 래<sup>1,2</sup> · 구 경 헌**<sup>1\*</sup> <sup>1</sup>인천대학교 전자공학과 <sup>2</sup>(주)이너트론

# Hak-Rae Cho<sup>1,2</sup>· Kyung Heon Koo<sup>1\*</sup>

<sup>1</sup>Department of Electronics Engineering, Incheon National University, Incheon, 22012, Korea <sup>2</sup>Innertron Inc., Incheon, 22014, Korea

# [요 약]

본 논문에서는 LTCC 다층기판으로 구현할 수동 소자를 수축공정과 무수축공정으로 구분하여 설계, 제작하고 분석하였다. 유전율 7 또는 40의 두 종류 세라믹 소재를 사용하여 기본 형태의 수동소자를 다양하게 두 가지 공정으로 제작하여 특성을 비교하였다. 유전율 40 기판을 사용할 때 수축공정은 X, Y 방향에서 17%, Z 방향에서 36%의 수축율을 보이는 것과 비교하여, 무수축공정은 X,Y 방향에서 변화하지 않고 Z 방향으로만 43% 수축하여 평면상에서 높은 치수 정밀도와 표면 평탄도를 얻을 수 있다. 측정 값으로 부터 매개 변수를 이용한 경험적 해석 식을 이용하여 제작한 LTCC 소자의 인덕턴스 및 커패시턴스를 추정하였으며 설계라이브러리 형태로 구현하였다. 유전율과 제작 공정에 따라 인덕터의 권선수와 단위 면적에 따른 커패시턴스를 측정하여 권선수 및 단위면적에 따른 소자값을 예측할 수 있는 다항식을 제시하였다.

## [Abstract]

This paper has designed, fabricated, and analyzed the passive devices realized using low temperature co-fired ceramic (LTCC) multi layer substrates by dividing into the shrinkage process and the non-shrinkage process. Using two types of ceramic materials with dielectric constant 7 or 40, we have fabricated the same shape of various elements in 2 different processes and compared the characteristics. For the substrate of dielectric constant 40, compared with the shrinkage process which has 17% shrink in the X and Y directions with 36% shrink in the Z direction, the non-shrinkage process has 43% shrink in the Z direction without shrink in the X and Y directions, so high dimensional accuracy and surface flatness can be obtained. The inductances and capacitances of the fabricated elements are estimated from measurement using empirical analysis equations of parameters and implemented as a design library. Depending on the substrate and the process, the inductance and capacitance depending on the turn number of winding and unit area have been measured, and empirical polynomials are proposed to predict element values.

Key word: LTCC, Library, Helical inductor, MIM capacitor.

# https://doi.org/10.12673/jant.2019.23.2.172

This is an Open Access article distributed under the terms of the Creative Commons Attribution Non-CommercialLicense(http://creativecommons

.org/licenses/by-nc/3.0/) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

Received 18 March 2019; Revised 5 April 2019 Accepted (Publication) 23 April 2019 (30 April 2019)

\*Corresponding Author; Kyung-Heon Koo

**Tel:** +82-32-835-4766 **E-mail:** khkoo@inu.a.kr

## │. 서 론

무선통신용 부품은 더 높은 주파수에서 동작 가능하고, 작은 크기, 경제적인 가격 등의 특성이 요구되며, 이는 저온 동시소결이 가능한 고유전율 세라믹인 LTCC (low temperature co-fired ceramic) 소재 및 공정을 이용하여 다양한 기능의 다층 회로를 구현할 수 있다[1-3]. LTCC의 이러한 특징을 이용하면 다층으로 수동소자를 적층하고 회로 소자 및 모듈의 소형화를 달성할 수 있다. LTCC 다층 회로 설계에서 수동부품은 RF 초크, 커플링, 바이패스, 임피던스 정합 등과 같은 여러 용도로 사용되며, 구현 수동소자의 정확한 모델링은 LTCC 회로설계에 매우 중요한 요소이다[4].

본 논문에서는 인덕터 및 커패시터의 라이브러리를 나선 인 덕터(사각형구조)와 MIM (metal-insulator-metal)커패시터에 대 하여 구현하였다. 각 구성요소에 기준 레이아웃 다이어그램이 있으며, 측정값에서 매개 변수에 대한 경험적 분석 방정식을 이 용하여 제작될 LTCC 소자의 인덕턴스 및 커패시턴스를 예측 하였다. 다층 세라믹 기판을 형성하기 위해 제작 시 소성과정을 거치면 수축이 발생하게 되며 보통 15% 정도의 오차를 갖게 되 고 불규칙한 수축으로 배선전극의 변형 및 위치정밀도가 저하 되게 된다. 근래에는 xy 방향인 횡방향으로 수축을 없애기 위해 특별히 제작된 무수축 시트를 이용한 무수축공정을 시도하고 있으나 전체시트를 활용하는 것은 가격이 기존 시트의 수배 이 상으로 쉽지 않다. 본 논문에서는 제작 방법과 사용 시트는 동 일하면서. 상하에 무수축용 가이드 시트를 사용해서 수축을 줄 이는 방법으로 무수축 공정의 단점을 보완하였다. 수동소자인 인덕터와 커패시터를 제작하고 이를 설계 라이브러리 형태로 구현하기 위해 2종류의 유전체 재료와 수축 공정과 무수축 공 정을 동시에 사용하여 총 4 가지 경우로 제작 비교하였다[5-6]. 사용 유전체는 유전상수 (또는 유전율, relative permittivity) 가 40 또는 7이며 2가지 형태로 구분하여 같은 패턴으로 각각 설 계 제작하여 측정 및 분석하였다. 측정값을 활용하여 다항식 커 브 피팅 (polynomial curve fitting)을 통하여 측정 및 기본 라이 브러리에서 완전히 제공하지 않는 수동 소자의 모델을 확장하 여 추정할 수 있도록 하였다.

# Ⅱ. LTCC 라이브러리 개발

LTCC 공정에서 중요 파라미터 중 하나는 소성시 수축률로, 수축공정과 무수축 공정의 두 제작 공정에서 실제 발생한 평균 수축율을 표 1에 제시하였다. 본 연구에서는 수축공정용 시트를 사용하면서 공정 위, 아래에 특별 제작한 무수축 시트를 가이드로 활용하여 무수축 공정을 진행하였다. 평균적으로 X-Y 평면에서 수축공정은 약 15% 수축하며, 무수축공정은 약 1% 수축하고 Z 방향은 모두 약 40% 수축률을 나타내고 있다.

표 1. 수축공정과 무수축공정의 수축률 비교

**Table 1.** Comparison of shrinkage ratio between the shrinkage process and the non-shrinkage process.

|            |                    |      |         |          | • •       |

|------------|--------------------|------|---------|----------|-----------|

| sheet      | process            | axis | simula- | measure- | shrinkage |

|            |                    |      | tion    | ment     | ratio     |

| RNE<br>-40 | shirinkage         | X    | 9.6     | 7.925    | 17.44%    |

|            |                    | Y    | 10      | 8.220    | 17.80%    |

|            |                    | Z    | 1.8     | 1.138    | 36.81%    |

|            | non-<br>shrinkage  | X    | 9.6     | 9.466    | 1.39%     |

|            |                    | Y    | 10      | 9.846    | 1.54%     |

|            |                    | Z    | 1.8     | 1.020    | 43.33%    |

| L7SH       | shirinkage         | X    | 9.6     | 8.353    | 12.99%    |

|            |                    | Y    | 10      | 8.564    | 14.36%    |

|            |                    | Z    | 1.96    | 1.338    | 31.76%    |

|            | non-<br>shirinkage | X    | 9.6     | 9.547    | 0.55%     |

|            |                    | Y    | 10      | 9.947    | 0.53%     |

|            |                    | Z    | 1.96    | 1.178    | 39.92%    |

### 2-1 인덕터 라이브러리

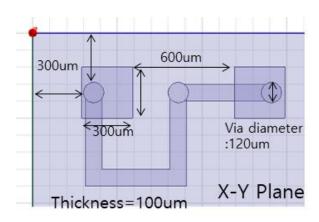

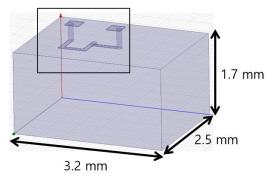

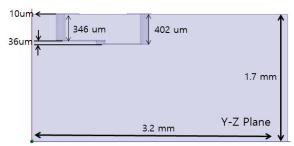

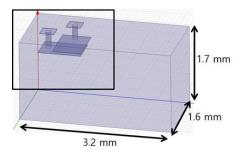

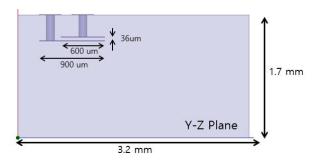

사각형 구조의 인덕터는 레이아웃이 용이하여 평면형 수동소자로 많이 사용된다. Q값을 높이기 위해 금속 두께를 증가하거나 나선형 인덕터 중심을 비우는 형태로 설계한다. 보통 인덕터 중심 반경이 선폭의 5배정도가 바람직하다. 인덕터 라이브러리를 구현하기 위해 그림 1과 같이 감은 회수 1회 (권선수 1)에 대해 모양을 정의하여, 금속 선폭은 100 µm, 권선수 1에서 5배의 중심반경을 갖도록 외각크기를 600 µm 로 설정하였다. 제작된 권선수 1의 인덕터를 그림 2와 같이 3.2 x 2.5 x 1.7 mm³(이하 3225 구조라 약칭함)의 직육면체 공간에 형성하고 측정패드를 윗면에 노출하도록 설계하였다. 그림 2의 형상을 Y-Z평면으로 확인하면 그림 3과 같으며 패드 노출 길이를 최소로하도록 상단에 형성하여 구성하였다.

**그림 1.** 권선수 1 인덕터 구조

**Fig. 1.** Structure of 1 turn inductor.

173 www.koni.or.kr

**그림 2.** 권선수 1 인덕터의 3225 크기 내 구성

Fig. 2. Inductor configuration of 1 turn in 3225 size.

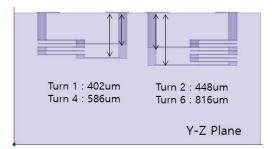

그림 3. 권선수 1 인덕터의 3225 크기 내 Y-Z 평면 구성

Fig. 3. Y-Z plane configuration of 1 turn inductor in 3225 size.

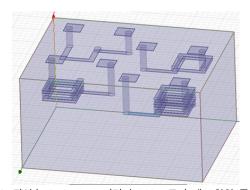

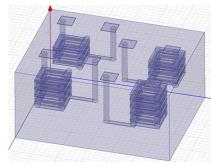

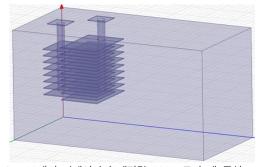

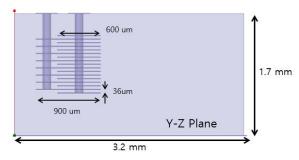

**그림 4.** 권선수 1, 2, 4, 6 인덕터 3225 크기 내 3차원 구성

**Fig. 4.** 3D configuration of 1, 2, 4 and 6 turns inductor in 3225 size.

그림 5. 권선수 1, 2, 4, 6 인덕터 3225 크기 내 Y-Z 평면 구성

**Fig. 5.** Y-Z plane configuration of 1, 2, 4 and 6 turns inductor in 3225 size.

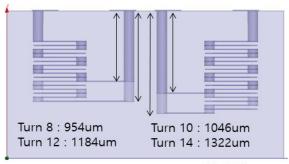

그림 6. 권선수 8, 10, 12, 14 인덕터 3225 크기 내 3차원 구성 Fig. 6. 3D configuration of 8, 10, 12 and 14 turns inductor in 3225 size.

Y-Z Plane

그림 7. 권선수 8, 10, 12, 14 인덕터 3225 크기 Y-Z 평면구성 Fig. 7. Y-Z plane configuration of 8, 10, 12 and 14 turns inductor in 3225 size.

제작된 권선수 1 의 형상을 이용하여 권선수 2, 4,6을 그림 4와 같이 구성하였으며 그림 5와 같이 Y-Z 평면으로 높이를 확인하였다. 다음으로 권선수 8, 10, 12, 14를 그림 6과 같이 구성하였으며 그림 7에 Y-Z 평면으로 높이를 확인하였다.

제작된 인덕터를 3차원 전자계 시뮬레이터 및 등가회로 소자치 추출 기능을 이용하여 500 MHz 주파수를 기준으로 예상 인덕턴스 값을 시뮬레이션하였으며 표 2 에 제시하였다.

표 2. 권선수 별 인덕턴스 예상 값

Table 2. Estimated inductance by turn number.

| Table 1: 10 marca made and by tam mamber |                               |        |           |  |

|------------------------------------------|-------------------------------|--------|-----------|--|

| Turn number                              | Inductance<br>(nH_at 500 MHz) | W (um) | Size (um) |  |

| 1                                        | 1.22                          |        |           |  |

| 2                                        | 2.68                          |        |           |  |

| 4                                        | 7.44                          |        |           |  |

| 6                                        | 13.26                         | 100    | 600*600   |  |

| 8                                        | 19.75                         | 100    | 800.800   |  |

| 10                                       | 26.68                         |        |           |  |

| 12                                       | 33.6                          |        |           |  |

| 14                                       | 40.67                         |        |           |  |

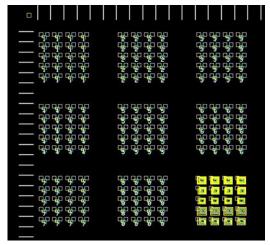

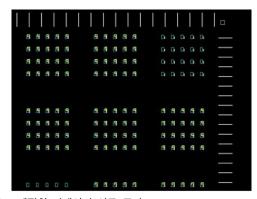

그림 8. 제작한 인덕터 시트 도면

Fig. 8. Fabricated Inductor sheet.

표 3. 본 연구에 사용된 각 공정의 명칭

Table 3. Notation of each process used in this research.

| permittivity | shrinkage process | non-shrinkage process |

|--------------|-------------------|-----------------------|

| 40           | RNE40             | RNE40(N)              |

| 7            | L7SH              | LT7SH(N)              |

시뮬레이션 결과를 토대로 4가지 경우에 적합하게 설계하였으며 제작을 위한 각각의 sheet를 그림 8과 같이 레이아웃 하였다. 또한 기판 종류와 제작 공정에 따라 4가지 종류로 인덕터를 제작하였으며 각 인덕터의 공정 명칭을 표 3에 정리하였다.

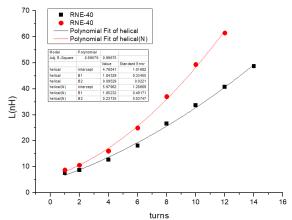

유전율 40인 세라믹 시트를 적충하여 인덕터를 제작하고 수 축공정과 무수축공정에 따른 인덕턴스를 측정하였으며 그림 9 와 같이 커브피팅하여 권선수에 따른 다항식을 제시하였다.

그림 9. 유전율 40 LTCC의 수축공정 및 무수축 공정시 권선수에 따른 인덕턴스 측정값 및 다항식 커브 피팅

Fig. 9. Measured values of inductance with the sheet of dielectric constant 40 for shrinkage or non-shrinkage process and polynomial curve fitting with the number of turns.

유전율 40 경우의 인덕턴스 값을 권선수 N에 따른 2차 다 항식으로 커브 피팅하였으며 그 결과를 식 1과 2로 제시하였다.

$$L(무수축) = 4.7804 + 1.8432*N + 0.0952*N^2$$

(1)

$$L(\dot{\uparrow} = 5.9796 + 1.8523*N + 0.2373*N^2$$

(2)

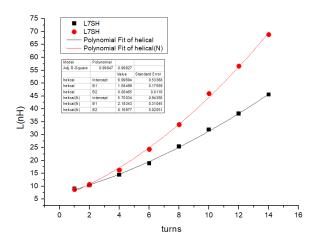

또한, 유전율 7인 세라믹 시트를 적충하여 인덕터를 제작하여 수축공정과 무수축공정에 따른 인덕턴스를 측정하고 그림 10과 같이 모델링하여 계산식을 권선수에 맞게 결정하였다. 이때 인덕턴스 값을 2차 다항식으로 커브 피팅 하였으며 그 결과는 식 3과 4와 같다.

$$L(무수축) = 5.7003 + 2.1834*N$$

+0.1697\* $N^2$  (3)

$$L(\dot{\uparrow} = 6.9969 + 1.5749*N + 0.0846*N^2$$

(4)

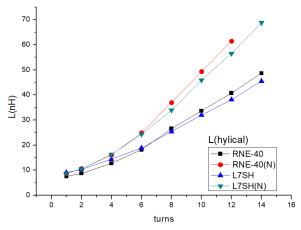

인덕턴스 측정값을 유전율에 따라 커브피팅으로 예측한 값과 함께 제시하면 그림 11과 같으며 유전율이 높은 제품이 상대적으로 같은 권선수인 경우 인덕턴스의 값이 크다.

그림 10. 유전율 7 LTCC의 수축공정 및 무수축 공정의 권선수에 따른 인덕턴스 측정값 및 다항식 커브 피팅

Fig. 10. Measured values of inductance with the sheet of dielectric constant 7 for shrinkage or non-shrinkage process and polynomial curve fitting with the number of turns.

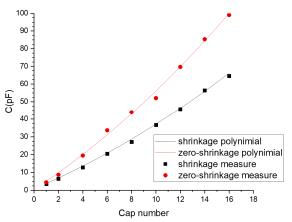

## 2-2 커패시터 라이브러리

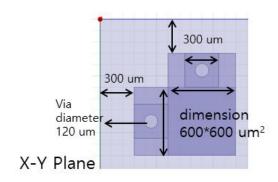

커패시터 구현 및 설계 라이브러리 구축을 위해 그림 12의 MIM 구조에서 두 금속 패드의 마주보는 부분이 커패시턴스를 갖도록 하였고, 기본을 한면의 길이가 600 um인 정사각형으로

175 www.koni.or.kr

그림 11. 각 공정별 권선수에 따른 인덕턴스 변화

**Fig. 11.** Inductance of each process with increasing the number of winding turns.

설정하고 각 금속 간격을 36 um로 기준을 정의하고 적층하여 쌓아 올려서 커패시턴스가 증가되는 형태로 구성하였다.

그림 13의 형상을 Y-Z 평면으로 확인하면 그림 14와 같으며 패드 노출의 길이를 최소로 하고자 상단에 형성하여 구성하였다. 인덕터 라이브러리와 마찬가지로 적층 구조에 따른 커패시터를 확인하였으며 그림 15와 16과 같이 최대 16개 적층 구조에 대해 확인하였다.

그림 12. 600\*600um² 커패시터 구조

Fig. 12. Capacitor structure in 600\*600um<sup>2</sup>.

그림 13. 1개의 커패시터의 3216 size 내 구성

Fig. 13. 3D configuration of a capacitor in 3216 size.

그림 14. 1개의 커패시터의 3216 크기 내 Y-Z 평면구성 Fig. 14. Y-Z plane configuration of a capacitor in 3216

그림 15. 16개의 커패시터의 세라믹 3216 크기 내 구성 Fig. 15. 3D configuration of 16 capacitors in 3216 size.

그림 16. 16개의 커패시터의 세라믹 3216 크기 내 Y-Z 평면구성

**Fig. 16.** Y-Z plane configuration of 16 capacitors in 3216 size.

표 4. 적층 수에 따른 커패시턴스 시뮬레이션 값

Table 4. Simulated capacitance with the number of layers.

| Layer | Capacitance<br>(pF_2GHz) | Size (um) |

|-------|--------------------------|-----------|

| 1     | 4.13                     |           |

| 2     | 7.26                     |           |

| 4     | 13.37                    |           |

| 6     | 20.49                    | 600*600   |

| 8     | 27.13                    | 000.000   |

| 10    | 33.89                    |           |

| 12    | 40.56                    |           |

| 14    | 47.46                    |           |

제작된 커패시터를 3차원 전자계 시뮬레이터와 등가회로 소자치 추출 기능을 이용하여 2 GHz 주파수에서 예상되는 커 패시턴스 값을 시뮬레이션 하였으며 표 4에 보였다. 시뮬레이 션 결과를 기준으로 커패시터를 유전율과 공정에 따라 4가지 경우로 설계하였으며 제작하기 위한 각각의 시트를 그림 17에 제시하였다.

커페시턴스 값은 수축공정과 무수축공정에 따라 값이 변화하며 면적에 관계하여 소자 값이 결정되는 특성을 그림 18에 나타내었다. 각 공정에 따른 커페시턴스 값을 2차 다항식으로 커브 피팅을 하였으며 그 결과는 식 5와 6와 같다.

$$C(shrinkage) = 0.817505 + 2.886*N$$

$$+0.07486*N^{2}$$

(5)

$$C(non - shrinkage) = 0.5523 + 4.4398*N$$

$$+0.1108*N^{2}$$

(6)

그림 17. 제작한 커패시터 시트 도면

Fig. 17. Fabricated capacitors sheet.

그림 18. 유전율 40 LTCC의 수축공정과 무수축공정에 따른 단위 면적 갯수에 따른 커패시턴스 측정값 및 다항식 커브 피팅

**Fig. 18.** Measurement value of capacitance with dielectric constant 40 and polynomial curve fitting according to the number of unit area in shrinkage or non-shrinkage process.

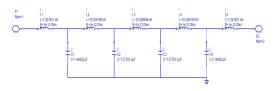

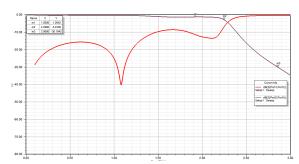

### 2-3 구현된 라이브러리를 활용한 9차 LPF 설계

본 연구에서는 LTCC 다층 기판에서 사용 가능한 인덕터와 커패시터 라이브러리를 구축하였으며 라이브러리를 활용하여 하모닉 제거용 9차 저역통과필터(LPF)를 회로 및 전자계 시뮬 레이터로 설계하였다. 목표로 하는 LPF 전기적특성은 표5와 같 으며 그림 19에 설계된 9차 LPF 회로를 제시하였다. LPF 설 계를 통하여 개발된 인덕터 및 커패시터 라이브러리의 유용성 을 알 수 있다.

표 5. LPF 전기적 특성

**Table 5.** Electrical specification of LPF.

| Pass band      | DC - 2.2GHz            |

|----------------|------------------------|

| Atten          | <30dB @ 2.8GHz - 13GHz |

| Insertion loss | +/- 1dB                |

| Туре           | Chebyshev              |

| Order          | 9                      |

그림 19. 설계된 LPF 회로도

Fig. 19. Circuit of the designed LPF.

그림 20. 설계된 LPF 시뮬레이션 결과

Fig. 20. Simulation result of the designed LPF.

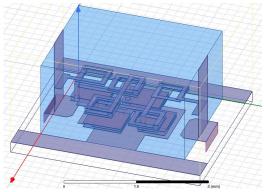

그림 21. 설계된 LPF의 3225 size 내 구성

**Fig. 21.** 3D configuration of the designed LPF in 3225 size.

177 www.koni.or.kr

## Ⅲ. 결 론

본 논문에서는 LTCC 다층 기판에서 사용 가능한 수동소자 인 인덕터와 커패시터 라이브러리 구축을 위하여 다양한 크기의 레이아웃을 진행하였다. 유전율 7과 40의 두 종류 세라믹 소재를 사용하고, 수축공정과 무수축 공정으로 제작하여 총 4가지 경우로 설계하고 제작하였다. 제작 소자의 측정값에서 매개변수에 대한 경험적 분석 방정식을 이용하여 Polynomial curve fitting으로 다양한 LTCC 소자의 인덕턴스 및 커패시턴스를 예측하였다. 이를 통해 측정값에서 완전히 제공하지 않는 수동소자의 구성요소의 모델을 확장하여 추정할 수 있도록 라이브러리를 구현하였으며 개발 라이브러리를 이용하여 9차 LPF(저역통과필터)를 설계하여 그 활용성을 제시하였다.

인덕터의 경우 공심을 갖는 사각형의 나선(헬리컬) 구조로 제작하였으나, 다양한 모양이 가능하도록 라운드형 및 스파이 럴 형태까지 라이브러리 구축을 확대하는 것이 필요하며 5G용주파수에서 사용가능하도록 더욱 높은 주파수까지 활용 가능한 라이브러리 구축으로 확대되면 향후 RF 소자 및 모듈 개발시간을 크게 개선할 수 있을 것이다.

### References

[1] W. Blood, F. Ling, T. Myers and M. Petras, "Library development process for embedded capacitors in LTCC," in *IEEE 9th Topical Meeting on Electrical Performance of*

- Electronic Packaging (Cat. No.00TH8524), Scottsdale: AZ, pp. 147-150, 2000.

- [2] A. Sutono, A. Pham, J. Laskar and W. Smith, "RF/microwave characterization of multilayer ceramic-based MCM technology," *IEEE Transactions on Advanced Packaging*, Vol. 22, No. 3, pp. 326-331, Aug. 1999.

- [3] K. Chen and S. Chung, "A novel compact balanced-tounbalanced low-temperature co-fired ceramic bandpass filter with three coupled lines configuration," *IEEE Transactions* on *Microwave Theory and Techniques*, Vol. 56, No. 7, pp. 1714-1720, July 2008.

- [4] J. Sieiro, J. M. López-Villegas, J. A. Osorio, T. Carrasco, M. N. Vidal and S. Ahyoune, "Synthesis of compact planar inductors in LTCC technology," in 2012 International Conference on Synthesis, Modeling, Analysis and Simulation Methods and Applications to Circuit Design (SMACD), Seville: Spain, pp. 45-4, 2012.

- [5] M. Nicák, B. Psota, P. Kosina, J. Starý and J. Šandera, "Zero shrink LTCC 3D structure interconnections," in 2012 35th International Spring Seminar on Electronics Technology, Bad Aussee: Austria, 2012, pp. 128-132.

- [6] K. Tokita, Y. Hashimoto, K. Fujiwara, A. Suzuki, Y. Ishida and H. Yamaoka, "Development of zero-shrinkage-LTCC substrate for millimeter-wave applications," in 2018 Asia-Pacific Microwave Conference (APMC), Kyoto: Japan, pp. 1274-127, 2018.

조 학 래 (Hak-Rae Cho)

1999년 2월: 경남대학교 재료공학과 (공학사) 2000년 3월~2000년 12월: 에이스테크놀로지 대리 2001년 1월~2002년 2월: 이노웨이브 이사 2002년 2월~현재: ㈜이너트론 대표이사

2015년 9월<sup>~</sup> 현재: 인천대학교 전자공학과 석박사통합 과정 ※관심분야: 무선중계기 및 기지국시스템, 정보경영

구 경 헌 (Kyung Heon Koo)

1981년 : 서울대학교 전자공학과 (공학사), 1991년 : 서울대학교 전자공학과 (공학박사), 1987년 <sup>~</sup> 현재 : 인천대학교 전자공학과 교수

1998년 ~ 현재: 한국항행학회 이사, 연구회 위원장, 회장, 명예회장 ※관심분야: RF 회로 및 모듈설계, 무선통신 시스템, 차세대 항행시스템 등 1983년 : 서울대학교 전자공학과 (공학석사) 1999년 ~ 2000년 : UC San Diego 방문학자