ISSN: 1226-7244 (Print) ISSN: 2288-243X (Online) 논문번호 19-01-49

326

# 질화갈륨 전력반도체와 Si CMOS 소자의 단일기판 집적화를 위한 Si(110) CMOS 공정개발

# Development of Si(110) CMOS process for monolithic integration with GaN power semiconductor

김 형 탁\*

Hyung-tak Kim\*

#### **Abstract**

Gallium nitride(GaN) has been a superior candidate for the next generation power electronics. As GaN-on-Si substrate technology is mature, there has been new demand for monolithic integration of GaN technology with Si CMOS devices. In this work, (110)Si CMOS process was developed and the fabricated devices were evaluated in order to confirm the feasibility of utilizing domestic foundry facility for monolithic integration of Si CMOS and GaN power devices.

### 요 약

차세대 전력반도체 소재인 질화갈륨(GaN)이 증착된 GaN-on-Si 기판의 기술성숙도가 높아지면서 Si CMOS 소자와의 단일기판 집적화에 대한 관심이 고조되고 있다. CMOS 특성이 상대적으로 저하되는 (111)Si 보다 (110)Si의 CMOS소자가 집적화 관점에서 유리할 것으로 판단되며, 따라서 향후 전개될 GaN-on-(110)Si 플랫폼을 활용한 GaN 전력반도체 스위치소자와 Si CMOS소자의 단일기판 집적화에 적용될 수 있도록 국내 Si CMOS 파운드리 공정을 (110)Si 기판에 진행하였다. 제작된 CMOS소자의 기본특성 및 인버터체인 회로특성, 그리고 게이트 산화막의 신뢰성 분석을 통해 향후 국내 파운드리공정을 활용한 (110)Si CMOS기술과 GaN의 집적화의 가능성을 검증하였다.

Key words: GaN, (110)Si, monolithic integration, power semiconductor, CMOS

# 1. 서론

전력반도체 기술의 차세대 주자로 질화갈륨(GaN) 반도체는 지난 10 여 년간 국내외에서 매우 활발하 게 연구개발이 진행되었다. GaN-on-Si 기판은 전 력 스위칭 시장을 점유하고 있는 Si 기반 소자기술 과의 원가 경쟁력 확보 관점에서 반드시 필요한 기술이다. 상용 GaN-on-Si 웨이퍼는 다른 방향과 비교하여 AlN seed 층과의 보다 나은 원자 배열 때문에 Si(111) 기판이 사용되어 왔다[1]. 그러나 Si

\* School of Electronics and Electrical Engineering, Hongik University

★ Corresponding author

E-mail: hkim@hongik.ac.kr, Tel: +82-2-320-3013

Acknowledgment

This research was supported by Korea Electric Power Corporation. (Grant number: R18XA06-05)

Manuscript received Mar. 9, 2019; revised Mar. 17, 2019; accepted Mar. 19, 2019.

This is an Open-Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License (http://creativecommons.org/licenses/by-nc/3.0) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

(111) 웨이퍼는 전기적 특성이 좋지 않아 오늘날의 CMOS 제조에는 사용되지 않으므로 GaN-on-Si (111) 웨이퍼에서 CMOS IC와 GaN 디바이스 간의 단일기판 집적화(monolithic integration)를 달성하 기가 어렵다. Si(100) 기판은 CMOS 산업에서 중요 한 재료이지만, Si(100) 기판상의 GaN 성장은 일반 적으로 다결정 구조 또는 원자 배열의 어려움으로 인해 많은 입자로 구성된 거친 표면을 초래한다 [2][3]. 반면 Si(110) 기판은 높은 정공 이동도를 활 용할 수 있어 CMOS 제조에 제한적으로 사용되어 왔다[4]. GaN 기반 파워 IC의 효율 및 주파수 성능은 GaN 디바이스와 제어 CMOS IC 사이의 monolithic integration에 의해 향상 될 수 있기 때문에 GaN on Si(110) 웨이퍼의 활용도가 점차 높아질 가능성 이 크다[3][4]. 여기서 하나 고려해야할 점은 GaN과 같은 III-V족 반도체의 경우 생산라인의 오염 문제로 Si CMOS 생산시설에서의 공정진행이 사실상 불가 하다. 따라서 Si과 GaN의 monolithic integration을 위해서는 Si CMOS 공정이 우선 진행된후 GaN이 Si 기판에 증착되어야 한다. 이때, CMOS가 형성된 Si 기판에서의 선택적 GaN 박막성장, 즉 epitaxy가 진행되는 동안 고온에 Si CMOS가 노출된다는 점 을 유의해야한다. 이 관점에서, 분자선 성장(MBE) 은 상대적으로 낮은 성장 온도 때문에 금속유기화 학기상 증착 (MOCVD)보다 더 나은 선택이 될 수 있다. (110) Si 기판 위에 MBE를 사용하여 형성한 AlGaN/GaN 이종접합을 활용하여 온전류 460 mA/ mm, 항복전압 610 V, 온저항 2.84 mΩ/cm<sup>2</sup>의 성능 을 보이는 이종접합 전력반도체 트랜지스터가 개 발된 바 있다[5]. Si(110) 기판은 Si(100) 대비 보다 우수한 Si CMOS 소자 특성을 확보할 수 있어 고 전압 GaN 스위칭소자와 이를 구동하는 Si CMOS 회로의 단일기판 집적화가 실현되었을 때 시스템 의 고도화가 가능하다. 국내에서 Si(110) CMOS 소 자의 제작이 보고된 바가 전무하며 이는 파운드리 진행의 사례가 없었기 때문이다. 따라서 국내 파운 드리 서비스를 활용하여 Si(110) CMOS 소자 공정 을 진행하고 측정결과를 공유하여 향후 발생할 수 요에 대응하는 기반을 마련하고자 하였다. 최근 GaN 반도체 기술을 사물인터넷(IoT)향 센서로 개 발하고자 하는 추세가 있어 Si CMOS 기술과의 집 적화는 매우 유용할 것으로 기대된다.

# Ⅱ. 본론

#### 1. (110) Si CMOS 공정

GaN 반도체의 우수한 전하수송특성으로 인하여 GaN 전력반도체 스위칭 소자를 구동하는데 있어 고성능의 Si CMOS 특성이 요구되지 않아 구경 6 인치 Si(110) 기판에 0.8 µm 기준 공정을 진행하였 다. Well 구조는 twin well 구조를 적용하였고 소 자 isolation은 LOCOS 공정을 통해 형성하였다. 기 존 Si(100) 게이트 산화막 성장공정을 (110) 기판에 적용하면 표면 원자 밀도의 차이로 인하여 성장속 도가 달라진다. 공정안정성 확보를 위하여 성장 온 도와 증기압은 기존 조건을 유지하고 성장시간을 조절하여 표 1의 성장두께별 공정을 확보하여 19 nm의 산화막을 성장하였다. Si(110) 기판에 제작된 CMOS 소자는 전자의 이동도는 감소하고 정공의 이동도가 증가하여 NMOS와 PMOS 소자의 정합 성 확보가 중요하다. 따라서 Silvaco사의 공정시뮬 레이션을 통해 불순물 주입 조건, 특히 불순물 주 입량에 대한 조건을 도출하여 이온주입을 진행하 였다. 서론에서 언급한 바와 같이 GaN 반도체 소 자와의 단일기판 집적화를 위해서는 CMOS 공정 이 완료된 후 GaN 이종접합구조를 증착하여야 한 다. MOCVD는 1000 ℃도 이상, MBE의 경우 750 ℃를 넘는 고온에서 증착이 진행되므로 고온을 견 딜 수 있는 금속배선 공정이 진행되어야 한다. 따 라서 기존 Si(100) CMOS공정에서 적용되는 Al 기 반 배선 공정을 Ti/TiN/Ti 배선으로 전환하여 고 온 안정성을 유지하도록 하였다. 모든 공정은 한국 전자통신연구원(ET) 융합부품기술센터가 지원하는 0.8 μm Si CMOS 파운드리에서 진행되었다.

Table 1. SiO<sub>2</sub> growth on Si(100) and (110) wafer. 표 1. Si(100)과 (110) 기판에 성장한 게이트 산화막

| Si wafer<br>type | Temp<br>(℃) | time(m) | thickness(Å) |         |

|------------------|-------------|---------|--------------|---------|

|                  |             |         | target       | average |

| 100              | 850         | 11      | 60           | 58.624  |

| 110              | 850         | 8       | 60           | 60.118  |

| 110              | 850         | 11      | 90           | 92.172  |

| 110              | 850         | 30      | 130          | 129.98  |

# 2. (110) Si CMOS 소자특성

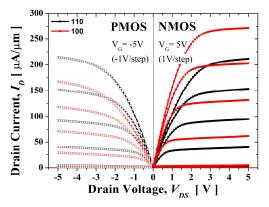

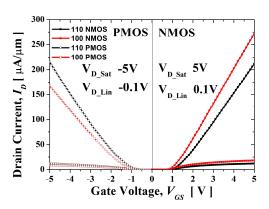

그림 1과 2는 Si(110) 기판위에 제작된 CMOS 소

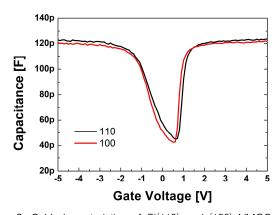

자의 전기적 특성을 보여주고 있다.  $I_D$ - $V_G$ 의 전달 특성 중 선형영역인  $V_D$ =0.1 V 조건에서 NMOS와 PMOS 모두 1.0 V의 문턱전압을 나타내었으며 포화전류는  $V_D$ =5.0 V에서 215  $\mu$ A/ $\mu$ m 수준으로 측정되었다. Si(100) CMOS 소자의 경우에는 동일한 문턱전압을 갖는 경우 전자와 정공의 이동도 차이로인해 NMOS의 전류가 PMOS 대비 상당히 높은 불일치(mismatching)가 존재하나 Si(110) CMOS 소자의 경우 NMOS의 전자이동도는 감소하고 PMOS의 정공이동도는 증가하여 불일치가 해소되었음을 알수 있다. 그림 3은 커패시턴스-전압특성 측정의 결과이다. NMOS와 PMOS 모두 서로 유사하고 정상적인 특성을 나타내었다.

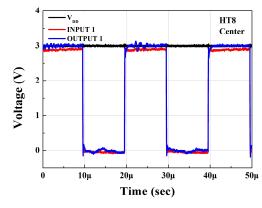

진행한 Si(110) CMOS 공정을 활용한 CMOS 회로 제작능력을 검증하기 위하여 6단 인버터 체인회로를 개별소자와 함께 제작하여 측정하였다. 그림 4는 50 kHz의 입력신호에 대한 Si(110) CMOS 인버터 체인의 동작특성을 측정한 결과이며 입력신호에 대해 정상적인 특성을 나타내었다.

#### 3. Si(110) 게이트 산화막 신뢰성 특성

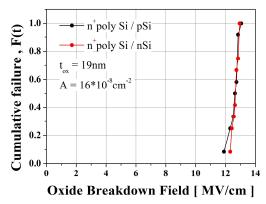

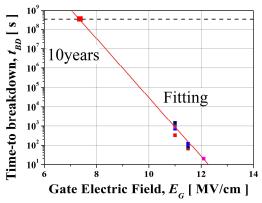

Si(100)에서 Si(110)으로의 기판 변경에 따라 게이트 산화막에 대한 신뢰성 검증이 필요하여 이에 대한 분석을 진행하였다. 그림 5는 NMOS와 PMOS 게이트 산화막의 전계에 의한 누적불량(cumulative failure) 시험에 대한 결과이고 그림 6은 가속실험으로 수명(life time)시험을 진행한 결과이다. NMOS와 PMOS의 게이트 산화막의 불량 발생은 서로 차이가 거의 없었다. 그림 6이 보여주는 10년 수명 전

Fig. 1. Output(ID-VD) characteristics of Si(110) and (100) CMOS devices.

그림 1. Si(110)과 (100) 기판에 제작된 CMOS소자의 출력 특성 계를 소자의 19 nm 게이트 산화막에 대한 동작전 압으로 환산하면 대략 15 V의 수준의 게이트 전압 이 10년 수명의 한계전압임을 알 수 있다.

Fig. 2. Transfer(ID-VG) characteristics of Si(110) and (100) CMOS devices in saturation and triode mode.

그림 2. Si(110)과 (100) 기판에 제작된 CMOS소자의 포화 및 선형영역 전달특성

Fig. 3. C-V characteristics of Si(110) and (100) NMOS capacitor. f=10 MHz.

그림 3. Si(110)과 (100) NMOS 커패시터의 C-V 특성

Fig. 4. 6-stage inverter chain characteristics on Si(110) wafer with f=50 KHz.

그림 4. Si(110) 6-stage 인버터체인회로의 응답특성

Fig. 5. Cumulative failure rate of gate oxide on Si(110). 그림 5. Si(110) 게이트 산화막의 cumulative failure rate

Fig. 6. Extrapolated life time from time-to-breakdown measurement.

그림 6. Time-to-breakdown 측정으로부터 추정되는 게이트 산화막의 수명

#### Ⅲ. 결론

국내 0.8 µm Si CMOS 파운드리 공정을 적용하여 Si(110)과 (100) 기판에 CMOS 소자 및 회로를 제작하고 특성을 분석하여 개발된 Si(110) 공정의유효성을 검증하였다. 정공이동도의 향상으로 인해 Si(110)의 PMOS의 성능이 개선되어 동일 문턱전압 기준 NMOS와 동일한 전류가 측정되었다. 또한 Si(110) 인버터체인 회로의 정상적인 동작과 게이트산화막의 신뢰성을 확보하였다. 향후 GaN-on-Si(110) 플랫폼을 활용하여 Si CMOS회로와 GaN전력반도체의 단일기판 집적화를 진행함에 있어 본공정의 활용이 가능할 것이다.

# References

[1] A. Dadgar, F. Schulze, M. Wienecke, A. Gadanecz, J. Basing, P. Veit, T. Hempel, A. Diez, J. Christen, and A. Krost, "Epitaxy of GaN on silicon.impact of symmetry and surface reconstruction," *New J. Phys.*, vol. 9, p. 389, 2007.

DOI: 10.1088/1367-2630/9/10/389/meta

[2] J.-H. Boo, S.-B. Lee, Y.-S. Kim, J. T. Park, K.-S. Yu, and Y. Kim, "Growth of AlN and GaN thin films on Si(100) using new single molecular precursors by MOCVD method," *Phys. Status Solidi a*, vol. 176, no. 1, pp. 711–717, 1999. DOI: 10.1002/(SICI)1521–396X(199911)176:1<711::AID-PSSA711>3.0.CO;2-Y|

[3] T. N. Bhat, M. K. Rajpalke, B. Roul, M. Kumar, and S. B. Krupanidhi, "Substrate nitridation induced modulations in transport properties of wurtzite GaN/p-Si (100) heterojunctions grown by molecular beam epitaxy," *J. Appl. Phys.*, vol. 110, no. 9, p. 093718, 2011. DOI: 10.1063/1.3658867 [4] A. Teramoto, T. Hamada, M. Yamamoto, P. Gaubert, H. Akahori, K. Nii, M. Hirayama, K. Arima, K. Endo, S. Sugawa, and T. Ohmi, "Very high carrier mobility for high-performance CMOS on a Si(110) surface," *IEEE Trans. Electron Devices*, vol. 54, no. 6, pp. 1438-1445, 2007.

DOI: 10.1109/TED.2007.896372

[5] S. Han, Y. Noh, M. Jo, S. Kim, J. Oh, K. Seo, and H. Cha, "Normally-Off MOS-HFET on AlGaN/GaN-on-Si(110) Grown by NH<sub>3</sub> MBE," *IEEE Trans. Electron Devices*, vol. 37, no. 12, pp. 1613–1616, 2016. DOI: 10.1109/LED.2016.2621184