ISSN: 2288-243X (Online)

ISSN: 1226-7244 (Print)

논문번호 19-01-05

# 10 nm 이하 무접합 원통형 MOSFET의 온-오프전압 $\Delta V_{on-off}$ 에 대한 분석

Analysis of On-Off Voltage  $\Delta V_{on-off}$  in Sub-10 nm Junctionless Cylindrical Surrounding Gate MOSFET

정 학 기\*\*

Hak-kee Jung\*★

#### Abstract

We investigated on-off voltage  $\Delta V_{on-off}$  of sub-10 nm JLCSG (Junctionless Cylindrical Surrounding Gate) MOSFET. The gate voltage was defined as ON voltage for the subthreshold current of  $10^{-7}A$  and OFF voltage for the subthreshold current of 10<sup>-12</sup> A, and the difference between ON and OFF voltage was obtained. Since the tunneling current was not negligible at 10 nm or less, we observe the change of  $\Delta V_{on-off}$  depending on the presence or absence of the tunneling current. For this purpose, the potential distribution in the channel was calculated using the Poisson equation and the tunneling current was calculated using the WKB approximation. As a result, it was found that  $\Delta V_{on-off}$  was increased due to the tunneling current in JLCSG MOSFETs below 10 nm. Especially, it increased rapidly with channel lengths less than 8 nm and increased with increasing channel radius and oxide thickness.

#### 요 약

본 논문에서는  $10~\mathrm{nm}$  이하 무접합 원통형 MOSFET의 온-오프 전압  $\Delta V_{on-off}$ 에 대하여 고찰하였다. 문턱전압이하 전류 가  $10^{-7}A$ 일 때 게이트 전압을 온 전압,  $10^{-12}A$ 일 때 게이트 전압을 오프 전압으로 정의하고 그 차를 구하였다. 10 nm 이하 에서는 터널링 전류를 무시할 수 없기 때문에 터널링 전류의 유무에 따라  $\Delta V_{on-off}$ 의 변화를 관찰하였다. 이를 위하여 포아 송방정식을 이용하여 채널 내 전위분포를 구하였으며 WKB 근사를 이용하여 터널링 전류를 구하였다. 결과적으로 10 nm 이 하 JLCSG MOSFET에서 터널링 전류에 기인하여  $\Delta V_{on-off}$ 가 증가하는 것을 알 수 있었다. 특히 8 nm 이하의 채널길이에 서 급격히 증가하였으며 채널 반지름과 산화막 두께가 증가할수록  $\Delta V_{on-off}$ 는 증가하는 것을 알 수 있었다.

Key words: junctionless cylindrical surrounding,  $\Delta V_{on-off}$ , channel radius, subthreshold current

E-mail: hkjung@kunsan.ac.kr, Tel: +82-63-469-4684

Acknowledgment

Manuscript received Feb. 11, 2019; revised Mar. 25, 2019; accepted Mar. 26, 2019.

This is an Open-Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License(http://creativecommons.org/licenses/by-nc/3.0) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

## I. 서론

전자시스템이 고도화되면서 고성능 소자의 필요 성이 대두되었다. 트랜지스터 소자의 고속, 저전력, 고집적도를 위하여 필수적인 사항은 트랜지스터의 미세화이다. 그러나 기존의 MOSFET 구조를 이용 한 미세화는 문턱전압이하 스윙저하, 문턱전압이동 및 차단전류의 증가 등 단채널 효과에 기인한 단점 을 나타내고 있다. 단채널 효과는 게이트 전압을

<sup>\*</sup> Dept. of Electronic Engineering, Kunsan National University ★Corresponding author

이용한 채널 내 캐리어의 제어능력을 향상시킴으로 써 해결할 수 있다. 이와 같이 게이트의 제어능력 향상을 위하여 개발된 트랜지스터구조가 다중게이 트 MOSFET이다. 다중게이트 구조는 이중게이트, 삼중게이트 및 원통형 게이트 등으로 발전하고 있 다. 원통형 게이트는 채널을 원통형으로 제작하고 게이트 단자에 의하여 채널을 감싸는 구조로 제작하 므로 게이트 단자에 의한 채널 내 캐리어에 대한 제 어능력을 극대화할 수 있다는 장점이 있다[1, 2]. 특 히 채널과 소스/드레인 영역의 도핑농도 및 도핑형 태를 동일하게 제작하는 무접합 구조의 경우, pn 접 합 구조를 이용하는 기존의 MOSFET 보다 10 nm 이하에서 발생할 수 있는 도핑분포의 급격한 변화를 방지할 수 있다는 장점이 있다[3]. 무접합 원통형 게 이트(Junctionless Cylindrical Surrounding Gate: JLCSG) MOSFET의 경우, 채널 도핑을 소스/드레 인 도핑과 같이 고농도로 도핑하기 때문에 접합 원 통형 게이트(Junction-based Cylindrical Surrounding Gate: JBCSG) MOSFET에서 주로 사용하는 저농 도 도핑 채널에서 발생할 수 있는 도핑농도의 모호 함 등을 해결할 수 있다[4]. 즉, 채널길이 50 nm, 채널 반지름 10 nm, 채널 도핑농도  $10^{15}/cm^3$ 의 JBCSG MOSFET의 경우 채널 내 존재하는 불순물의 개수가  $\sim 10^{-2}$ 개 라는 모호한 값을 갖게 되나 도핑농도가  $10^{19}/cm^3$  인 JLCSG MOSFET의 경우는  $\sim 10^2$ 개라 는 합리적인 개수를 갖게될 수 있을 것이다. 10 nm 이하구조에서는 이와 같은 현상은 더욱 심화될 것 이다. 그러므로 본 논문에서는 고농도로 도핑된 채 널을 갖는 10 nm 이하의 JLCSG MOSFET의 문턱 전압이하 전류-전압 특성을 고찰하고자한다. 채널 길이가 10 nm 이하로 감소하면 터널링 전류는 무 시할 수 없게 되므로 전송특성에 확산-표동 전류 뿐만이 아니라 터널링 전류도 포함한 드레인 전류 를 이용하였다. 특히 터널링 전류의 대수값은 게이 트 전압에 비선형적으로 변화하기 때문에 일반적 인 문턱전압이하 스윙을 정의할 수 없다[5]. 그러므 로 온전류  $10^{-7}(W/L)A$  일 때의 게이트 전압과 오프전류  $10^{-12}(W/L)A$ 에서의 게이트 전압의 차 인  $\Delta V_{on-off}$ 를 구하여 채널 길이 및 채널 반지름, 그리고 산화막 두께 등에 따라  $\Delta V_{on-off}$ 변화를 관찰하여 최적의 JLCSG MOSFET의 설계조건 등 을 제시하고자 한다.

2장에서는 10 nm 이하 JLCSG 구조 MOSFET의 해석학적 전위분포 및 전류-전압 관계의 유도 과정을 설명할 것이다. 3장에서는 구해진 $\Delta V_{on-off}$ 를 채널구조에 따라 분석할 것이며 4장에서 결론을 맺는다.

# Ⅱ. 본론

# 1. JLCSG 구조 MOSFET의 전송특성

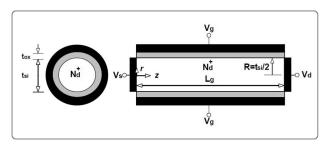

Fig. 1. Schematic cross sectional diagram of Junctionless Cylindrical Surrounding Gate (JLCSG) MOSFET. 그림 1. 무접합 원통형 게이트 MOSFET의 단면도

그림 1에 JLCSG 구조 MOSFET를 도시하였다. JLCSG 구조는 채널이 원통형 구조이다. 소스/드레인과 채널 간 무접합 구조인 경우로써 본 연구에서는  $N_d^+=10^{19}/cm^3$ 을 사용하였으며 소스/드레인 영역은  $10^{20}/cm^3$ 을 사용하였다. 채널길이는 5~nm에서 10~nm, 채널반지름은 1~nm에서 2~nm, 그리고산화막 두께는 0.5~nm에서 3~nm사이로 변화할 때중심전위와 드레인전류-게이트전압의 관계를 비교, 분석하였다. 그림 1의 10~nm 이하 축적형 JLCSG MOSFET의 경우, 문턱전압이하 영역에서드레인 전류는 다음과 같은 확산-표동 전류( $I_{d-d}$ ) 및 터널링 전류( $I_{tunn}$ )로 구성된다.

$$I_{d-d} = \frac{2\pi N_d^+ \mu_n k T \left(1 - \exp\left\{\frac{-q V_d}{k T}\right\}\right)}{\int_0^{L_g} \frac{1}{\int_0^R r \exp\left\{\frac{q \phi(r,z)}{k T}\right\} dr} dz} \tag{1}$$

$$\begin{split} I_{tunn} &= \left(\frac{qN_d\pi R^2}{6}\right) \left(\frac{2\,T_t v_{th_t}}{3} + \frac{T_l v_{th_l}}{3}\right) \\ T_{t,l} &= \exp\left[-2\int_{z_1}^{z_2} \left|\alpha_{t,l}(z)\right| dz\right] \\ \alpha_{t,l}(y) &= \sqrt{\frac{2m_{t,l} \left[q\phi(r,z) - E_{fm}\right]}{\kappa^2}} \end{split} \tag{2}$$

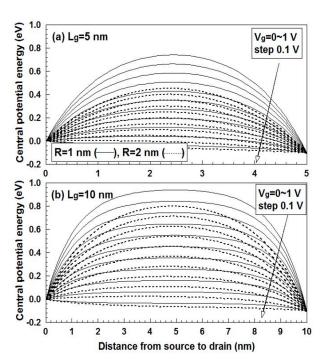

여기서 사용한 기호는 참고문헌 [6, 7]에 표기하 였다. 식 (1)에서  $\phi(r,z)$ 는 포아송방정식을 이용하 여 구한 채널 내 전위분포이다[8]. 전술한 바와 같 이 10 nm 이하 JLCSG MOSFET에서 문턱전압이 하 영역에서의 터널링 전류를 무시할 수 없으며 터 널링 전류는 식 (2)에서 알 수 있듯이 전위분포와 관계된 변수이다. JLCSG MOSFET의 경우 대부분 의 캐리어는 중심을 통하여 전송되기 때문에 중심 전위를 이용하여 구한 포텐셜에너지의 변화를 채 널길이 및 드레인 전압의 변화에 따라 그림 2에 도 시하였다. 그림 2에서 알 수 있듯이 게이트 전압이 증가할수록 포텐셜에너지 분포의 최대값은 작아져 결국 터널링 전류는 증가할 것이다. 또한 채널 반 지름이 증가하면 더욱 포텐셜에너지의 최대값이 감소하여 문턱전압이하 영역에서 확산-표동 전류 와 터널링 전류의 구성비에 영향을 미칠 것이다.

그림 2(a)와 2(b)의 채널 길이에 따른 변화를 관찰해 보면, 채널길이가 감소할수록 포텐셜에너지의 최대값이 감소하는 것을 알 수 있다. 여기서채널길이 감소에 따라 터널링 전류가 더욱 큰 영향을 미칠 수 있다는 것을 알 수 있다.

Fig. 2. Comparison with potential energy of this model for channel length under given conditions for (a)  $L_q=5\,nm$  and (b)  $L_q=10\,nm$ .

그림 2. 주어진 조건에서 채널길이에 대한 포텐셜에너지 비교 (a)  $L_{q}=5\,nm$ 와 (b)  $L_{q}=10\,nm$

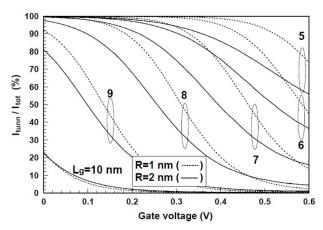

Fig. 3. Comparison with composition of tunneling current for drain current in subthreshold region with channel length and radius as parameters.

그림 3. 파라미터가 채널길이 및 반지름일 경우, 문턱전압 이하 영역에서 드레인 전류에 대한 터널링 전류의 구성비 비교

그림 3에 채널길이 변화에 따른 터널링 전류의 구성비를 도시하였다. 전술한 바와 같이 채널 길이가 감소할수록 터널링전류의 구성비는 크게 증가하는 것을 알 수 있다. 게이트 전압이 증가하면 그림 2에서 알 수 있듯이 포텐셜에너지의 최대값은 감소하여 터널링 전류가 증가하지만 상대적으로 확산-표동 전류가 더욱 증가하기 때문에 터널링 전류의 구성비가 게이트 전압 증가에 따라 감소하는 것을 알 수 있다. 이와 같은 현상은 채널 반지름 R이 증가할 때도 발생한다. 즉, 채널 반지름이 증가하면 그림 2에서 알 수 있듯이 포텐셜에너지의 최대값은 감소하므로 터널링 전류 뿐만이 아니라확산-표동 전류도 더욱 크게 증가하므로 채널 반지름 증가와 함께 터널링 전류의 구성비는 감소하는 것을 그림 3에서 관찰할 수 있다.

식 (2)에서 터널링 전류의 대수값은 게이트 전압에 선형적으로 변화하지 않는다는 것을 알 수 있다. 문턱전압이하 스윙은 문턱전압이하 영역에서 드레인 전류의 대수값이 게이트 전압에 선형적으로 변화할 때, 기울기로써 정의된다. 그러나  $10~\rm nm$ 이하 영역에서 터널링 전류의 영향으로 문턱전압이하 영역에서 드레인 전류의 대수값은 게이트 전압에 선형적으로 변화하지 않을 것이다. 그러므로본 논문에서 문턱전압이하 영역에서의 차단전류감소정도를 파악하기 위하여 온전압과 오프전압의차  $\Delta V_{on-off}$ 를 다음과 같이 정의하여 채널 크기

및 산화막 두께 변화에 따른  $\Delta V_{on-off}$ 의 변화를 관찰하였다.

$$\Delta V_{on-off} = V_{on} - V_{off}[V]$$

$$V_{on} = 10^{-7} (2\pi R/L_g) [A]$$

$$V_{off} = 10^{-12} (2\pi R/L_g) [A]$$

(3)

여기서 채널 폭은 채널의 둘레인  $2\pi R$ 을 이용하였다.

# 2. 10 nm 이하 JLCSG MOSFET의 $\Delta V_{on-off}$

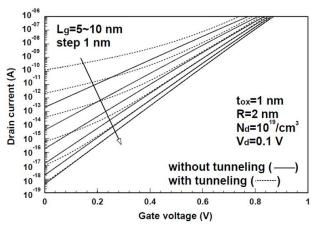

Fig. 4. Transfer curves of drain current vs. gate voltage with a channel length as a parameter.

그림 4. 파라미터가 채널길이일 경우, 드레인 전류와 게이트 전압의 전송특성곡선

본 논문에서 제시한 확산-표동 전류방정식과 터 널링 전류에 대한 타당성은 이미 발표한 논문[6, 7] 에서 입증하였으므로 식 (1)과 식 (2)를 이용하여 드레인 전압 0.1 V 일 때, 게이트 전압 변화에 따른 드레인 전류를 그림 4에 도시하였다. 여기서 산화 막 두께는 1 nm, 채널 반지름은 2 nm 일 경우이다. 그림 4에서 알 수 있듯이 확산-표동 전류만을 이용 한 문턱전압이하 전류의 대수값은 게이트 전압에 선형적으로 비례하는 것을 관찰할 수 있다. 채널 길이가 감소할수록 드레인전류의 증가는 더욱 크 게 나타나는 것을 관찰할 수 있다. 게이트 전압이 감소할수록 채널 길이 변화에 따른 문턱전압이하 전류의 변화는 더욱 증가하는 것을 관찰할 수 있 다. 그림 4에서 터널링 전류를 포함한 문턱전압이 하 전류의 대수값 변화는 게이트 전압에 비선형적 이라는 것을 관찰할 수 있다. 그러므로 드레인 전 류의 대수값이 게이트 전압에 선형적으로 변화할 때, 그 기울기로 정의되는 문턱전압이하 스윙을 정의할 수 없을 것이다. 문턱 전압이하 영역에서 가장 중요한 것은 온 전압 이하에서 급속한 드레인전류 감소이다. 즉, 온 전압 이하로 게이트 전압을 감소시켰을 경우, 드레인 전류는 급속히 0으로 가야만 오프상태에서 소비전력을 감소시킬 수 있을 것이다. 그러나 그림 4에서 알 수 있듯이 터널링 전류가 중요한 문턱전압이하 영역에서 드레인 전류는 급속히 감소하지 않는다는 것을 관찰할 수 있다. 드레인 전류의 감소 정도를 표시하기 위하여본 논문에서는 식 (3)을 이용하였다.

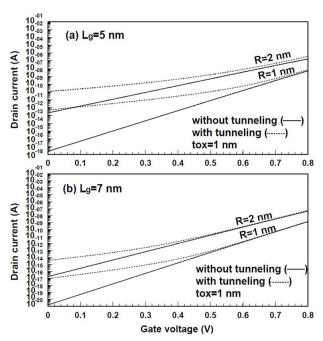

Fig. 5. Transfer curves of drain current vs. gate voltage with a channel radius as a parameter for (a)  $L_q=5\,nm$  and (b)  $L_q=7\,nm$ .

그림 5. 파라미터가 채널 반지름일 경우, 드레인 전류와 게이트 전압의 전송특성곡선 (a)  $L_g=5\,nm\,$ 와 (b)  $L_g=7\,nm$

채널 반지름을 파라미터로 구한 문턱전압이하 전류특성을 그림 5에 도시하였다. 그림 5에서 알 수 있듯이 채널반지름이 증가하면 문턱전압이하 전류는 증가하는 것을 관찰할 수 있다. 그림 5(a)와 (b)를 비교해보면 채 널 길이가 짧아질수록 터널링 전류가 문턱전압이하 전류에 미치는 영향은 크게 증가하고 있었다. 특히 채널 반지름이 감소할수록 터널링전류의 유무에 따른 문턱전압이하 전류의 차이는 심하게 나타나고 있었다. 또한 게이트 전압이

감소할수록 채널 반지름에 따른 문턱전압이하 전 류의 변화도 심해지는 것을 관찰할 수 있다.

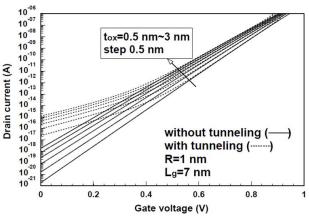

Fig. 6. Transfers curves of drain current vs. gate voltage with a gate oxide thickness as a parameter.

그림 6. 파라미터가 산화막 두께인 경우, 드레인 전류와 게이트 전압의 전송특성곡선

게이트 산화막 두께 변화에 따른 게이트 전압에 따른 문턱전압이하 전류의 변화를 그림 6에 도시하였다. 이때 채널 반지름은 1 nm, 채널 길이는 7 nm의 경우이다. 산화막 두께가 증가하면 터널링 전류가 문턱전압이하 전류에 더욱 큰 영향을 미치는 것을 관찰할 수 있다. 또한 게이트 전압이 증가하면 산화막 두께 변화에 따른 문턱전압이하 전류의 변화가 크게 감소하는 것을 관찰할 수 있다. 이상의결과를 이용하여 채널 길이, 채널 반지름 그리고게이트 산화막 두께 변화에 따른  $\Delta V_{on-off}$ 를 식(3)을 이용하여 관찰하고자한다.

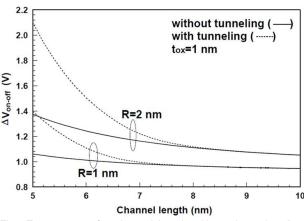

Fig. 7.  $\Delta V_{on-off}$  for channel length with a channel radius as a parameter.

그림 7. 채널 반지름이 파라미터일 경우, 채널길이에 대한  $\Delta V_{on-off}$

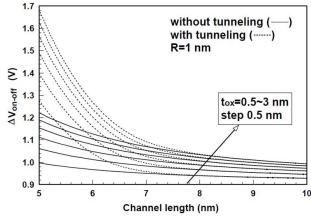

Fig. 8.  $\Delta\,V_{on-off}$  for channel length with a gate oxide thickness as a parameter.

그림 8. 산화막 두께가 파라미터일 경우, 채널길이에 대한  $\Delta V_{on-off}$

터널링 전류의 유무에 따라 채널길이에 따른  $\Delta V_{on-off}$ 의 변화를 채널 반지름을 파라미터로 그림 7에 도시하였다. 그림에서 알 수 있듯이 채널 길이가 8 nm 이상에서는 터널링 전류의 영향이 무시할 수 있을 정도로 작다는 것을 관찰할 수 있다. 터널링 전류의 영향은 채널길이가 짧아질수록 그리고 채널 반지름이 증가할수록 커진다는 것을 관찰할 수 있다. 그러므로 채널 길이를 감소시킬 때 채널 반지름도 감소하여야만  $\Delta V_{on-off}$ 를 작게 유지할 수 있을 것이다.

산화막 두께 변화에 따른  $\Delta V_{on-off}$ 의 변화를 터널링 전류의 유무에 따라 그림 8에 도시하였다. 그림 8에서 알 수 있듯이 산화막 두께가 증가하면  $\Delta V_{on-off}$ 도 증가하는 것을 알 수 있으며 터널링 전류의 영향도 증가하는 것을 알 수 있다. 그림 7에서 설명하였듯이 그림 8에서도 채널 길이가 8 nm 이상에서는 터널링 전류의 영향이 미미하게 나타나고 있었다. 그러나 7 nm 이하로 채널길이가 감소하면 채널 반지름뿐만이 아니라 게이트 산화막 두께에 따른  $\Delta V_{on-off}$ 의 변화가 매우 크게 나타나는 것을 관찰할 수 있다.

### Ⅲ. 결론

본 논문에서는  $10~\mathrm{nm}$  이하 JLSCG MOSFET에 대한 문턱전압이하 영역에서의 온-오프 전압차  $\Delta V_{on-off}$ 를 고찰하였다.  $10~\mathrm{nm}$  이하 채널 길이에

서는 터널링 전류의 영향이 증가하여 문턱전압이 하 전류에 영향을 미치게 된다. 그러나 터널링 전 류의 대수값은 게이트 전압에 선형적으로 비례하 지 않기 때문에 문턱전압이하 스윙을 정의할 수 없 게 된다. 그러므로 본 논문에서는 온 전압과 오프 전압의 차이인  $\Delta V_{on-off}$ 에 의하여 문턱전압이하 영역에서 게이트 전압에 대한 문턱전압이하 전류 의 감소정도를 나타내었다. 결과적으로 채널 길이 가 감소할수록 터널링 전류의 영향이 증가하여  $\Delta V_{on-off}$ 가 급격히 증가하는 것을 알 수 있었다. 또한 채널 반지름이 증가할수록  $\Delta V_{on-off}$ 가 증가 하였으며 산화막 두께가 증가할 때에도  $\Delta \, V_{on-off}$ 는 증가하였다. 특히 채널길이가 8 nm 이하에서는 터널링 전류의 급격한 증가로 인하여 터널링 전류 의 유무에 따라  $\Delta V_{on-off}$ 가 급격히 변화하였다. 이상의 결과에서 JLCSG MOSFET의 경우 채널길 이를 8 nm 이하로 감소시켜 미세화할 경우, 채널 반지름 및 산화막 두께도 함께 감소시켜 터널링 전 류의 영향을 감소시키고  $\Delta V_{on-off}$ 도 감소시켜야 할 것이다.

### References

[1] C. Li, Y. Zhuang, S. Di and R. Han and G. Jin, "Subthreshold Behavior Models for Nanoscale Short-Channel Junctionless Cylindrical Surrounding-Gate MOSFETs," *IEEE Transactions on Electron Devices*, vol. 60, no. 11, pp. 3655–3662, 2013. DOI: 10.1109/TED.2013.2281395

[2] C. Jiang, R. Liang, J. Wang and J. Xu, "A Study of Subthreshold Behavior of Short Channel Junctionless Cylindrical Surrounding-Gate MOSFETs from an Electrostatic Potential Viewpoint," 2015 International Symposium on Next-Generation Electronics (ISNE), Taipei, Taiwan, pp. 1-4, 2015. DOI: 10.1109/ISNE.2015.7131955

[3] Z. Ding, G. Hu, J. Gu, R. Liu, L. Wang and T. Tang, "An analytical model for channel potential and subthreshold swing of the symmetric and asymmetric double-gate MOSFETs," *Microelectronics Journal*, vol. 42, pp. 515–519, 2011. DOI: 10.1016/j.mejo.2010.11.002

[4] M. K. Pandian and N. B. Balamurugan, "Analytical Threshold Voltage Modeling of Surrounding Gate Silicon Nanowire Transistors with Different Geometries," *Journal of Electrical Engineering & Technology*, vol. 9, no. 6, pp. 2079–2088, 2014. DOI: 10.5370/JEET.2014.9.6.2079 [5] H. K. Jung, and S. Dimitrijev, "Optimum top and bottom thickness and flat-band voltage for improving subthreshold characteristics of 5 nm DGMOSFET," *Superlattices and Microstructures*, vol. 101, no. 1, pp. 285–292, 2017.

DOI: 10.1016/j.spmi.2016.11.040

[6] C. Li, Y. Zhuang, R. Han and G. Jin, "Subthreshold behavior models for short-channel junctionless tri-material cylindrical surrounding-gate MOSFET," *Microelectronics Reliability*, vol. 54, no. 6-7, pp. 1274–1281, 2014.

DOI: 10.1016/j.microrel.2014.02.007

[7] H. K. Jung, and S. Dimitrijev, "The Impact of Tunneling on the Subthreshold Swing in Sub-20 nm Asymmetric Double Gate MOSFETs," *International Journal of Electrical and Computer Engineering*, vol. 6, no. 6, pp. 2730-2734, 2016.

DOI: 10.11591/ijece.v6i6.pp2730-2734

[8] N. Trivedi, M. Kumar, S. Haldar, S. Deswal, M. Gupta and R. S. Gupta, "Analytical modeling of Junctionless Accumulation Mode Cylindrical Surrounding Gate MOSFET (JAM-CSG)," *International Journal of Numerical Modeling*, vol. 29, no. 6, pp. Nov./Dec. 2016. DOI: 10.1002/jnm.2162

## BIOGRAPHY

Hak-kee Jung (Member)

1983: BS degree in Electronic Engineering, Ajou University. 1985: MS degree in Electronic Engineering, Yonsei University. 1990: PhD degree in Electronic Engineering, Yonsei University.

1990~: Professor, Kunsan National University