# 습식 화학적 식각 방법에 의한 시간에 따른 GaAs(100) 단결정 웨이퍼에서의 마이크로 구멍의 제작 및 분석

이하영 · 곽민섭 · 임경원 · 안형수 · 이삼녕<sup>†</sup> 한국해양대학교 전자소재공학과

# Fabrication and Time-Dependent Analysis of Micro-Hole in GaAs(100) Single Crystal Wafer Using Wet Chemical Etching Method

Ha Young Lee, Min Sub Kwak, Kyung-Won Lim, Hyung Soo Ahn and Sam Nyung Yi<sup>T</sup>

Department of Electronic Materials Engineering, Korea Maritime and Ocean University, Busan 49112, Republic of Korea

(Received December 7, 2018: Revised December 17, 2018: Accepted January 8, 2019)

Abstracts Surface plasmon resonance is the resonant oscillation of conduction electrons at the interface between negative and positive permittivity material stimulated by incident light. In particular, when light transmits through the metallic microhole structures, it shows an increased intensity of light. Thus, it is used to increase the efficiency of devices such as LEDs, solar cells, and sensors. There are various methods to make micro-hole structures. In this experiment, micro holes are formed using a wet chemical etching method, which is inexpensive and can be mass processed. The shape of the holes depends on crystal facets, temperature, the concentration of the etchant solution, and etching time. We select a GaAs(100) single crystal wafer in this experiment and satisfactory results are obtained under the ratio of etchant solution with  $H_2SO_4:H_2O_2:H_2O=1:5:5$ . The morphology of micro holes according to the temperature and time is observed using field emission - scanning electron microscopy (FE-SEM). The etching mechanism at the corners and sidewalls is explained through the configuration of atoms.

Key words GaAs, wet-chemical etching, micro-hole, surface plasmon.

# 1. 서 론

최근 진행되고 있는 반도체 소자의 나노 사이즈 크기의 제작과 이의 효율 증대를 위해서는 공정 장비의 첨단화, 소자 구조의 집적화, 재료의 고품질화 등 여러가지 개선 요소가 있는데 그 중 패터닝 기술의 개발 또한 필수적 요소 이다. 1-6) 지금까지 여러 분야에서 개발되어 온 패터닝 기술은 최근에는 마이크로 구멍 제작에응용되어 LED, OLED, 태양전지 및 센서의 효율 증가와 같은 영역에 사용 되고 있을 뿐만 아니라 새로운 물리적 현상에 대한 연구도 보고되고 있다. 7-9) 특히 금속나노 구멍은 표면 플라즈몬 주파수 부근에서 강한 공명

을 나타내어 다양한 영역에서의 응용 가능성을 보이고 있다. 10-12) 한편, 본 실험에서 관심을 가지는 GaAs 단결정 웨이퍼는 통신위성이나 레이더 시스템 등 고급 장비나 높은 효율의 태양전지, 13) 발광 효율이 좋은 광원 장치 14)에 광범위하게 활용되고 있다. 이때 소자의 효율을 올리기 위해서는 단결정 웨이퍼의 패터닝 혹은 플라즈 몬 형성을 위한 나노 또는 마이크로 구멍의 공정이 행하여 지는데 GaAs 단결정 웨이퍼인 경우, 습식 화학적식각 방법으로 제작된 마이크로 구멍을 제작할 시 크기와 모양에 있어서 많은 제약이 있다. 따라서 주로 소자제작에 필요한 에피탁시 구조를 형성하기 위한 용도로만 습식 화학적 식각 방법이 이용되어 왔고 나노 또는

<sup>†</sup>Corresponding author

E-Mail: snyi@kmou.ac.kr (S. N. Yi, Korea Maritime and Ocean Univ.)

© Materials Research Society of Korea, All rights reserved.

This is an Open-Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License (http://creative-commons.org/licenses/by-nc/3.0) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

마이크로 구멍의 제작은 집속 이온 범<sup>15-17)</sup>과 반응성 이온 에칭<sup>18-21)</sup>의 방법을 이용하여 왔다. 이에 본 실험에서는 GaAs 단결정 웨이퍼에 대해 습식 화학적 식각 방법만을 사용하여 나노 또는 마이크로 구멍 제작에 필요한조건을 찾아 봄으로써 고가의 장비를 사용하지 않고 미세구멍을 제작하는 방법에 대한 가능성을 제시 하고자하였다.

### 2. 실험 방법

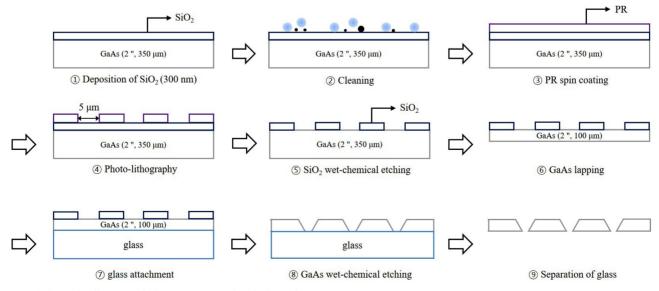

마이크로 구멍 구조는 2" 크기, 350 um 두께의 GaAs (100) 단결정 웨이퍼에서 제조되었다. Fig. 1에는 습식 화 학적 식각의 모식도를 나타내었다. 패턴을 형성하기 전 에 2개의 층이 GaAs(100) 단결정 웨이퍼 위에 증착 되 었다. 먼저, 300 nm 두께의 SiO2층을 RF-sputter의 방법 으로 증착하였다((1)). 그 다음 아세톤 및 메탄올을 사용 하여 단결정 웨이퍼를 세정 한 후 포토 레지스트를 스 핀 코팅 방법으로 올린 후 패턴을 노광 및 현상 단계를 통하여 얻었다(②~④). 이 때 패턴의 크기는 5 µm의 구 멍으로 제작하였다. 5 μm의 좁은 패턴을 사용한 이유는 GaAs(100) 단결정 웨이퍼는 식각시 구멍의 크기가 시간 의 영향을 많이 받는데 좁은 패턴을 통해 투입하는 식각 용액의 양을 최소한으로 하여 구멍의 크기를 조절하기 쉽 도록 하기 위함이다. SiO2층은 실온에서 buffered oxide etchant(6:1) 용액에 의해 선택적으로 식각되었다(⑤). SiO<sub>2</sub> 패턴이 형성된 단결정 웨이퍼를 래핑 공정을 통하 여 두께를 100 um까지 얇게 하였는데 그 이유는 GaAs (100) 단결정 웨이퍼는 식각율이 낮기 때문에 식각 공 정 시간을 줄이기 위해서 단결정 웨이퍼를 얇게 해주었 다(⑥). 래핑이 완료된 샘플을 1 cm × 1 cm 사이즈로 커팅한 후 투명 송진을 이용하여 유리 기판에 샘플을 부착하였다(⑦). 이러한 공정을 채택한 이유는 GaAs(100) 단결정 웨이퍼 자체가 잘 부서지기도 하지만 식각시 단결정 웨이퍼의 취급을 쉽게 하기 위함이기도 하다. 마지막 단계에서는 H<sub>2</sub>SO<sub>4</sub>:H<sub>2</sub>O<sub>2</sub>:H<sub>2</sub>O = 1:5:5의 비율로 식각 용액을 제조한 후 온도가 상온이 될 때까지 기다린 뒤 습식 식각을 시작하여 미세 구멍을 형성하였다(⑧). 마지막으로 유리 기판과 식각된 단결정 웨이퍼를 투명 송진을 녹여 분리하였다(⑨). 마이크로 구멍 구조의 식각 메커니즘은 FE-SEM(field emission-scanning electron microscopy)과 원자 구조 해석을 통해 분석되었다.

#### 3. 결과 및 고찰

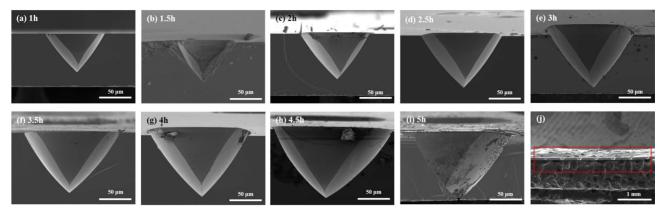

Fig. 2에서는 상온에서 시간에 따라 습식 식각 된 GaAs(100) 단결정 웨이퍼의 단면 FE-SEM 이미지를 나타내었다. Fig. 2의 (a)~(i)까지는 1시간부터 5시간 동안식각 된 샘플을 나타내고 있고 (j)에는 다수의 구멍 이미지를 나타내었다. 모든 샘플은 약 54°의 동일한 각도를 가지고 식각이 된 것을 볼 수 있지만 시간이 경과될수록 깊이와 넓이가 커지는 것을 관찰 할 수 있다. 샘플의 패턴은 5 μm의 구멍으로 시작했지만 제작된 구멍은 훨씬 넓은 크기를 가지는 것을 볼 수 있다. 샘플은 시간의 영향을 받아 등방성으로 식각 되는 것을 관찰 할수 있고 5시간이 지나게 되면 구멍을 관측할수 있다. 이는 식각 깊이가 100 μm의 단결정 웨이퍼 두께를 초과하였기 때문이다. 구멍이 생성된 이후에도 식각이 계속되면 구멍의 크기가 계속 확장된다. Fig. 2의 (j)에서

Fig. 1. Schematic diagram of GaAs(100) wet-chemical etching process.

Fig. 2. Cross-sectional FE-SEM images of GaAs(100) etched for (a) 1, (b) 1.5, (c) 2, (d) 2.5, (e) 3, (f) 3.5, (g) 4, (h) 4.5 and (i) 5 h, and (j) many micro holes made on GaAs(100) single crystal wafer.

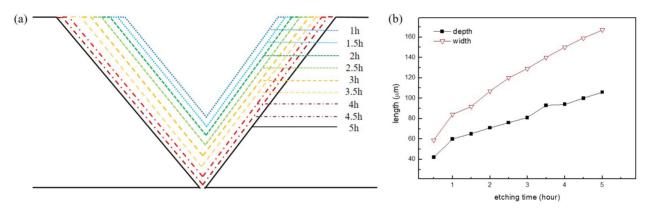

Fig. 3. (a) Proceeding of GaAs(100) etching for 1~5 h. (b) Dependence of etching depth and width on etching duration.

는 동일한 형태로 식각된 구멍이 주기적으로 배열되어 있음을 관찰 할 수 있다.

Fig. 3(a)는 시간이 진행 됨에 따라 식각이 진행되는 과정을 모식도로 나타내었다. 구멍은 시간이 갈수록 깊고 넓어졌으며 5시간이 지났을 때 100 μm의 깊이가 식각 되어 구멍이 생성되고 있음을 알 수 있다. 따라서 시간을 조절하면 원하는 깊이의 단결정 웨이퍼에 구멍을 제작할 수 있고 크기도 제어할 수 있다. Fig. 3의 (b)에는 식각 시간과 구멍의 깊이 사이의 관계를 그래프로 나타내었다. 깊이에 대한 식각 속도가 약 11 μm/h이며 폭에 대한 식각 속도는 약 19 μm/h가 되어 기울기가 일정하게 형성되고 있음을 볼 수 있고, 깊이보다는 폭의식각이 더 빠름을 알 수 있다.

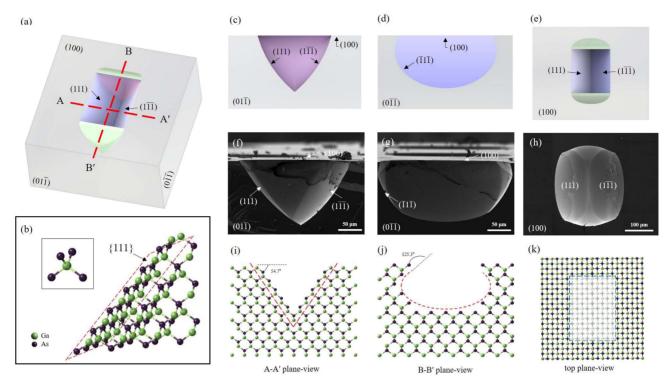

원자 구조 분석은 식각 프로세스를 이해하는데 많은 도움이 된다. Fig. 4의 (a)와 (b)에는 식각된 GaAs 단결정웨이퍼의 3차원 구조 및 그에 해당하는 원자 결합 모식도를 나타내었는데 원자 모식도에서 보라색 원자는 As원자, 초록색 원자는 Ga 원자이며, 식각 되는 면인 {111}면을 빨간색 점선으로 표시하였다. GaAs 격자에서 Ga

이 As에 의해 1개의 원자 결합이 되고 그 반대쪽 층에서는 3개의 공유결합을 하고 있으며 이는 As도 같은 형태를 보인다. Fig. 4의 (c)에는 A-A' 방향, (d)에는 B-B' 방향으로 잘랐을 때의 단면과, (e)에는 top-view의 모식도를 나타내었다. Fig. 4의 (c)~(e)의 모식도에 해당하는 샘플의 FE-SEM 이미지를 (f)~(h)에 각각 나타내었으며이때 샘플은 7시간 동안 식각 된 것이다. Fig. 4의 (i), (j), (k)는 (f), (g), (h)의 각각의 FE-SEM 이미지를 원자모식도로 나타내고 있다. Fig. 4의 (k)의 파란색 점선 내부는 바닥까지의 경사진 면으로서 희미하게 처리하였다. 아래 식 (1)에는 GaAs와 식각 용액의 반응식을 나타내었다.

$$4GaAs + 3H_2O_2 \rightarrow 2As_2O_3 + 2Ga_2 + 3H_2$$

$As_2O_3(s) + 3H_2SO_4(aq) \rightarrow As_2(SO_4)_3(aq) + 3H_2O$  (1)

위의 식에서  $H_2O_2$ (산화제),  $H_2SO_4$ (산화층 제거 용액),  $H_2O$ (중화제)의 3가지 용액을 섞은 혼합 용액과 GaAs 단 결정 웨이퍼와의 반응을 볼 수 있다. 첫번째 과정은 반

Fig. 4. ((c), (f), (i)), ((d), (g), (j)), and ((e), (h), (k)) are the schematic diagrams, FE-SEM images of sample, and atomic diagrams observed at A-A' plane, B-B' plane, and top view of Fig. 4 (a), respectively.

응물인 GaAs에서 As가 산화되어 As<sub>2</sub>O<sub>3</sub>와 Ga<sub>2</sub>로 분리 되면서 결정의 표면이 식각되고, 두번째는 산화된 As<sub>2</sub>O<sub>3</sub> 가 식각 용액인 H<sub>2</sub>SO<sub>4</sub>와 만나 이중 치환 반응을 일으 켜 As<sub>2</sub>(SO<sub>4</sub>),를 생성하며 다시 이것이 H<sub>2</sub>O에 녹아 용 해 되는 순서로 진행된다.<sup>22)</sup> 이 때 Fig. 4의 모식도 (b), (i)와 (j)에서는 As면으로 식각이 되는 것을 보여주고 있 는데 이는 Ga 원자의 활성화 에너지보다 As 원자의 활 성화 에너지가 더 크기 때문이다.<sup>23)</sup> GaAs를 {111} 면 으로 자르게 되면 그 표면은 Ga 또는 As 한 가지의 원 자들만 남게 된다. Ga이 {111} 면의 가장 위쪽에 남아 있게 되면 3개의 가전자(31Ga-4s<sup>2</sup>4p<sup>1</sup>)가 모두 결합을 이 루어 자유전자가 생성되지 않지만 As가 {111} 면의 가 장 위쪽에 남아있게 되면 5개의 가전자(33As-4s<sup>2</sup>4p<sup>3</sup>) 중 2개의 자유 전자를 발생 할 수 있어 Ga 보다는 As면이 식각이 되기 쉬운 산화 상태가 되어 더 빠른 식각 속 도를 가지게 된다.<sup>24)</sup> GaAs를 산화 시키는 H<sub>2</sub>O<sub>2</sub> 용액은 활성화 에너지가 큰 As면과 반응을 일으키면서 위와 같 은 반응식을 나타내게 되어 As 원자 면을 따라 식각이 진행 된다.<sup>25)</sup>

# 4. 결 론

본 논문에서는 습식 화학적 식각 방법에 의해 H<sub>2</sub>SO<sub>4</sub>:

H<sub>2</sub>O<sub>2</sub>:H<sub>2</sub>O = 1:5:5의 비율로 섞은 혼합 용액을 사용하여 GaAs(100) 단결정 웨이퍼에 마이크로 구멍을 형성하였다. 이를 통해 그동안 에피탁시 공정에 주로 사용되어 오던 화학적 식각 공정 방법을 마이크로 구멍제작에까지 확대하여 적용함으로써 고가의 장비를 사용하는 것보다 상대적으로 좀더 간단하게 마이크로 구멍 공정을할 수 있었다. 이 실험에서 얻은 식각 공정의 결과는 더욱 정밀한 에칭 조건이 필요한 에피탁시 제작에 응용되거나 금속 증착을 통한 표명 플라즈몬 형성을 통해 소자의 효율을 증대시키는데 기여하게 될 것이다.

# Acknowledgements

This research was supported by the Basic Science Research Program through the National Research Foundation of Korea (NRF) funded by the Ministry of Education (No. 2017R1A2B4009832).

#### References

- E. Menard, M. A. Meitl, Y. Sun, J. Park, D. J. Shir, Y. Nam, S. Jeon and J. A. Rogers, Chem. Rev., 107, 1117 (2007)

- 2. D. L. Wilson, R. Martin, S. Hong, M. C. Golomb, C. A.

- Mirkin and D. L. Kaplan, PNAS, 98, 13660 (2001).

- D. Choi, H. K. Yu, S. G. Jang and S. Yang, J. Am. Chem. Soc., 126, 7019 (2004).

- O. Fenwick, L. Bozec, D. Credgington, A. Hammiche, G. M. Lazzerini, Y. R. Silberg and F. Cacialli, Nat. Nanotechnol., 4, 664 (2009).

- F. Withers, T. H. Bointon, M. Dubois, S. Russo and M. F. Craciun, Nano Lett., 11, 3912 (2011).

- 6. Y. Lu and S. C. Chen, Nanotechnology, 14, 505 (2003).

- Y. Bahk, B. J. Kang, Y. S. Kim, J. Kim, W. T. Kim, T. Y. Kim, T. Kang, J. Rhie, S. Han, C. -H. Park, F. Rotermund and D. -S. Kim, Phys. Rev. Lett., 115, 125501 (2015).

- 8. M. Najiminaini, F. Vasefi, B. Kaminska and J. J. L. Carson, Appl. Phys. Lett., **100**, 043105 (2012).

- 9. C. Genet and T. W. Ebbesen, Nature, 445, 39 (2007).

- A. Lesuffleur, H. Im, N. C. Lindquist and S. Oh, Appl. Phys. Lett., 90, 243110 (2007).

- J. Parsons, E. Hendry, C. P. Burrows, B. Auquie, J. R. Sambles and W. L. Barnes, Phys. Rev. B, 79, 073412 (2009).

- T. Sannomiya, O. Scholder, K. Jefimovs, C. Hafner and A. B. Dahlin, Small, 7, 1653 (2011).

- K. Nakayama, K. Tanabe and H. A. Atwater, Appl. Phys. Lett., 93, 121904 (2008).

- 14. S. Iida, T. Sugimoto, S. Suzuki, S. Kishimoto and Y. Yagi, J. Cryst. Growth, 72, 51 (1985).

- K. Gamo, Y. Ochiai and S. Namba, Jpn. J. Appl. Phys.,

L792 (1982).

- Y. Ochiai, K. Gamo and S. Namba, J. Vac. Sci. Technol., B, 3, 67 (1985).

- 17. K. P. Hilton and J. Woodward, Electron. Lett., **21**, 962 (1985).

- R. J. Young, J. R. A. Cleaver and H. Ahmed, J. Vac. Sci. Technol. B, 11, 234 (1993).

- 19. Y. Sugimoto, M. Taneya, H. Hidaka and K. Akita, J. Appl. Phys., **68**, 2392 (1990).

- 20. E. Miyauchi, H. Arimoto, H. Hashimoto and T. Utsumi, J. Vac. Sci. Technol., B, 1, 1113 (1983).

- 21. R. Cheung, S. Thoms, S. P. Beamont, G. Doughty, V. Law and C. D. W. Wilkinson, Electron. Lett., 23, 857 (1987).

- 22. J. L. Vossen and W. Kern, Thin film processes, p.403, J. L. Vossen, Academic press, London (1978).

- 23. J. S. Kim, Master Thesis (in Korean), p. 1-4, Korea Maritime and Ocean University, Busan (2004).

- 24. S. M. Sze, Physics of Semiconductor Devices, John Wiley, New York (2012).

- 25. H. Y. Lee, Master Thesis (in Korean), p. 59-60, Korea Maritime and Ocean University, Busan (2018).