# A software-controlled bandwidth allocation scheme for multiple router on-chip-networks

Phan-Duy Bui\*, Chanho Lee\*\*

# Abstract

As the number of IP cores has been increasing in a System-on-Chip (SoC), multiple routers are included in on-chip-networks. Each router has its own arbitration policy and it is difficult to obtain a desired arbitration result by combining multiple routers. Allocating desired bandwidths to the ports across the routers is more difficult. In this paper, a guaranteed bandwidth allocation scheme using an IP-level QoS control is proposed to overcome the limitations of existing local arbitration policies. Each IP can control the priority of a packet depending on the data communication requirement within the allocated bandwidth. The experimental results show that the proposed mechanism guarantees for IPs to utilize the allocated bandwidth in multiple router on-chip-networks. The maximum error rate of bandwidth allocation of the proposed scheme is only 1.9%.

Key words : on-chip-network, SoC, bandwidth allocation, QoS, arbitration, multiple routers

# I. Introduction

As the number of IP cores has been increasing in a system-on-chip (SoC), multiple routers (or interconnects) are included in on-chip-networks because multiple small routers are more efficient than a single large router[1]. The arbitration stages of routers determine the request to be granted to access to a channel according to arbitration policies such as static-priority (static), round-robin (RR), time division multiple access (TDMA) and lottery[2, 3]. A communication bandwidth can be allocated to each IP or to each port of routers according to demands using the TDMA or the lottery scheme. The arbitration policies can be easily implemented in a single router. However, they require very complex analysis to implement in multiple-router systems, and the complexity increases rapidly as the number of routers increases. In addition, the allocated bandwidths may be changed according to the revised software running on the system. However, another complex analysis and re-design of the arbitration logic are required if the values of bandwidths change and the conventional arbitration policies are used. That is, the dynamic reconfigurations of the bandwidths are impossible.

In this paper, we present a software-controlled arbitration scheme to guarantee bandwidth allocation for multiple router on-chip-networks. An IP generates packets with a priority (or QoS packets) by software according to the bandwidths allocated

<sup>\*</sup> Dept. of Information Technology and Telecommunication Engineering, Soongsil University

$<sup>\</sup>bigstar$  Corresponding author

E-mail:chlee@ssu.ac.kr, Tel:+82-2-820-0710

<sup>\*\*</sup> This work was supported by the National Research Foundation of Korea (NRF) grant (NRF-2016R1D1A1B01008846). The EDA tools were supported by IDEC.

Manuscript received Nov. 27, 2019; revised Dec. 11, 2019; accepted Dec. 16, 2019.

This is an Open-Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License (http://creativecommons.org/licenses/by-nc/3.0) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

to the corresponding port. The allocated bandwidths are guaranteed regardless of the arbitration policy of routers if the routers support the QoS packet transfers. The bandwidth allocation can be modified dynamically at runtime. The proposed arbitration scheme was implemented for a dual router system and it was verified that the actually allocated bandwidths were very close to the desired bandwidths by simulation.

### II. Proposed arbitration scheme

The proposed programmable arbitration scheme utilizes the QoS functions of network interface protocols. Most of the modern protocols such as AXI and USIP support QoS packets which are processed with higher priority on on-chip-networks [4, 5]. Once the desired bandwidth for a master is determined and configured, the master sends normal packets as long as the actually allocated bandwidth by on-chip-networks is similar to the desired one. However, the master generates QoS packets if it encounters a deadline of an operation, which means the allocated bandwidth is less than the desired one. The QoS packets arrive at slaves with the minimum latencies since they are processed with higher priority in each router of the on-chip-networks regardless of the arbitration policy of the router.

The number of QoS packets would not be large because the normal packets from the masters with high desired bandwidths usually have high priorities. The QoS packets would be generated at the masters with low desired bandwidth and priority in routers. Therefore, the QoS packets rarely compete with others. The proposed scheme may be implemented by software or programmable hardware, and the desired bandwidth can be modified dynamically. The software implementation enables the modification of the policy of the QoS packet generation. The main difference between the proposed scheme and others is that arbitrations are made based on the variable priorities of incoming packets in the proposed scheme while arbitrations of the conventional schemes are made among masters according to fixed policies. The arbitration policies are compared in Table 1. The proposed scheme requires a negligible hardware overhead at a router as only a simple static priority logic and multiplexors are added. In addition, the interface logics of masters need to support the QoS packet injection, which is included in modern network interface protocols.

Table 1. Comparison of conventional and proposed arbitration policies.

| Arbitration<br>policy                   | Static | Round-<br>robin | TDMA     | Lottery | Proposed |

|-----------------------------------------|--------|-----------------|----------|---------|----------|

| Starvation<br>Prevention                | No     | Yes             | Yes      | Yes     | Yes      |

| Proportional<br>Bandwidth<br>Allocation | No     | Even*           | Yes*     | Yes*    | Yes      |

| Implementation<br>Complexity            | Low    | Low             | Moderate | High    | Low      |

\* Single router system only.

#### III. Experimental results

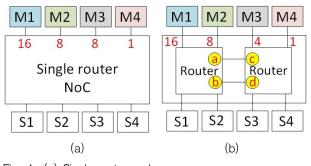

A single router system and a dual router system employing USIP interfaces are designed using Verilog-HDL and the operations are verified by simulation. Fig. 1 shows on-chip-network systems with a single and a dual routers using USIP[5]. Each port of the router consists of two unidirectional channels. The single router system includes 4 masters and 4 slaves and the ratio of desired bandwidths to masters is 16:8:8:1. The desired bandwidth refers to the predefined expected portion of bandwidth that should be ideally allocated to a master. All the masters communicate with a slave, S1. The dual router system also includes 4 masters and 4 slaves, and M1 and M2 belong to the left router and M3 and M4 belong to the right router, respectively. The ratio of desired bandwidths to masters is 16:8:4:1 and the dual router system has another parameter set,

the ratio of desired bandwidths a:b:c:d at inter-router ports as shown in Fig. 1(b). The masters generate packets continuously according to the desired bandwidths, and the actually allocated bandwidths are obtained from the number of packets delivered to the designated slaves during a predefined time. The TDMA and lottery arbitration policies are mainly evaluated while the static and RR are used as references due to the fact that they are not able to allocate bandwidth proportionally. The routers employ the static policy for the normal packets.

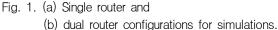

We first investigate how arbitration policies affect the bandwidth allocation among masters based on the single router configuration as shown in Fig. 1(a). Fig. 2 shows that most of bandwidth is consumed by the highest priorities M1 and M2 while causing bandwidth starvation to M3 and M4 in case of static-priority. The M4 takes less bandwidths than the desired in the round-robin arbitration because it generates fewer packets and often loses its tokens. Noted that in case of round-robin, the bandwidths should be evenly allocated to masters as desired. The TDMA and lottery arbitration schemes perform quite well in terms of bandwidth allocation. The maximum error rates of the TDMA and lottery are 9.6% and 10.5%, respectively. The error rates would be reduced if the masters generate packets continuously. On the other hand, the bandwidth allocation is improved by using the secondary static-priority arbitration.

Fig. 2. The single router's bandwidth allocation using various arbitration policies.

Fig. 3. The bandwidth allocation on dual router system using various arbitration policies where a:b:c:d = 4:1:16:8. The priority of inter-router ports is higher in (a), and is lower in (b) than the priority of local ports.

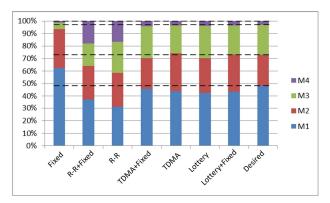

Fig. 3 shows bandwidth allocation results on dual router system. The ratio of desired bandwidths, a:b:c:d is 4:1:16:8, and all the masters communicate with S3 only. A global arbiter uses the staticpriority scheme between local and inter-router ports. The results on Fig. 3(a) and (b) correspond to the cases that the inter-router ports have the higher and the lower priority than the local ports, respectively. The function of arbitrations, therefore, may not work well as expected in such a case. Fig. 3 shows that the conventional arbitration schemes do not work across the multiple routers, and the global arbitration scheme affects the bandwidth allocation. The bandwidth allocation is not successful across the routers although the desired bandwidths of the inter-router ports are determined so that the ports of each router have the same bandwidth ratio as the desired one. The data transfers are affected by two local arbitration schemes as well as the global arbitration scheme. However, the bandwidth allocation results using the proposed SW-controlled arbitration are quite similar to the desired bandwidth, and are not affected by the global arbitration scheme.

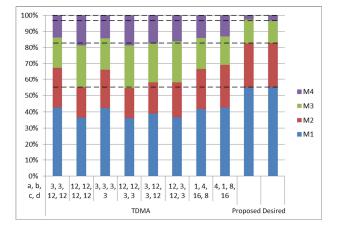

The bandwidth allocation is measured for various ratios of desired bandwidths of inter-router ports to investigate the effect of the ratio on the bandwidth allocation. The local arbitration scheme is the TDMA. Fig. 4 shows that the TDMA does not easily meet the requirement even if the various ratios of the desired bandwidths of inter-router ports are applied. We may find the ratio that results in the similar error rate to that of the single router system if we search it exhaustively after tedious computation. However, the bandwidth allocations using the proposed arbitration scheme are the same regardless of the ratio of desired bandwidths of inter-router ports.

Fig. 4. The bandwidth allocation according to the ratio of the desired bandwidth of inter-router ports on dual router system.

The maximum error rates of the conventional arbitration schemes and the proposed scheme are shown in Table 2. The error rates of the conventional scheme are much larger on the dual router system than those on the single router system while that of the proposed scheme is similar to both systems.

Table 2. Maximum error rate of bandwidth allocation using various arbitration policies compared with the desired case.

| Arbitration policy | Maximum error rate (%) |             |  |  |

|--------------------|------------------------|-------------|--|--|

| Arbitration policy | Single router          | Dual router |  |  |

| Round-robin        | 36                     | 51.2        |  |  |

| TDMA               | 9.6                    | 28          |  |  |

| Lottery            | 10.5                   | 28.8        |  |  |

| Proposed           | 0.9                    | 1.9         |  |  |

## IV. Conclusion

In this paper, we propose a SW-controlled arbitration scheme for multiple router on-chipnetwork systems to globally guarantee the bandwidth allocation to each port. The proposed scheme satisfies the desired bandwidth on the multiple router system by generating normal and QoS packets using SW according to the desired bandwidth. A dual router system was implemented using Verilog-HDL and the bandwidth allocation was measured. They were quite close to the desired bandwidths for the proposed scheme while those for the conventional schemes showed up to 29% errors.

# References

[1] S. Lee, C. Lee, and H.-J. Lee, "High Performance SoC On-chip-bus Architecture with Multiple Channels and Simultaneous Routing," *Journal of IEEK*, 44SD(4), pp. 322–329, 2007.

[2] C.-M. Chung, D.-A. Chiang, and Y. Qing, "A comparative analysis of different arbitration protocols for multiple-bus multiprocessors," *J.*

*Computer Science Technology,* vol.11, no.3, pp. 313–325, 1996. DOI: 10.1007/BF02943137

[3] K. Lahiri, A. Raghunathan, and G. Lakshminarayana, "The LOTTERYBUS on-chip communication architecture," *IEEE Trans. Very Large Scale Integration (VLSI) System*, vol.14, no.6, pp.596–608, 2006.

DOI: 10.1109/TVLSI.2006.878210

[4] ARM, "AMBA AXI Specification," Revision 2.0, 2010.

[5] C. Lee, "On-chip-network Protocol for Efficient Network Utilization," *Journal of IEEK*, 47SD(1), pp.86–93, 2010.

# BIOGRAPHY

# Phan-Duy Bui (Member)

2017 : BS degree in Computer Engineering, University of Information Technology, Hochiminh, Vietnam. 2017 : MS student in Dept. of Information Technology and Telecommunication, Soongsil University.

Chanho Lee (Member)

1987 : BS in Electronic Engineering,Seoul National University.1989 : MS in Electronic Engineering,Seoul National University.1994 : Ph.D in Electrical Engineering,UCLA.

<Research Area> SoC on-chip-network, Memory controller, Image Pattern recognition