https://doi.org/10.6113/TKPE.2019.24.6.406

# 결합 인덕터를 적용한 고효율 3레벨 컨버터

김건우<sup>1</sup>, 한정규<sup>1</sup>, 문건우<sup>†</sup>

## A New Zero-Voltage Switching Three-Level Converter with Reduced Rectifier Voltage Stress

Keon-Woo Kim<sup>1</sup>, Jung-Kyu Han<sup>1</sup>, and Gun-Woo Moon<sup>†</sup>

#### Abstract

Three-level (3L) DC - DC converters are appropriate for high-input-voltage applications. Although the voltage stress of TL converter switches can be reduced to half of the input voltage, the primary side has a large circulating current, which degrades efficiency. In this study, a dual half-bridge cascaded TL converter is presented to reduce this circulating current and thus decrease the conduction loss of the primary circuit. Moreover, the proposed converter can reduce the voltage stress of rectifier diodes, thereby reducing their conduction loss. Therefore, efficiency can be improved by reducing the conduction loss of the primary circuit and rectifier diodes.

Key words: Three-level converter, Coupled inductor, High efficiency

#### 1. 서 론

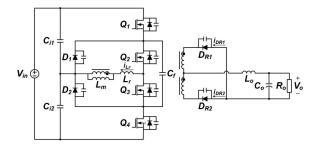

지난 몇 년간 높은 입력전압을 갖는 DC-DC 컨버터는 많은 분야에서 중요한 이슈로 떠오르고 있다. 삼상 입력전원을 갖는 AC-DC PFC 컨버터의 경우, 정류된 출력전압이 700V에 달한다. 따라서 이 뒤에 연결되는 DC-DC 컨버터는 높은 전압 스트레스를 견뎌야하고, 이를 줄이기 위해 많은 연구들이 진행되어져 왔다<sup>[1]-[3]</sup>. 그중 그림 1에 나와 있는 3레벨 컨버터는 전압 스트레스를 입력 전압의 절반으로 줄일 수 있어 널리 사용되고 있다<sup>[4]-[10]</sup>. 하지만 기존의 3레벨 컨버터는 경부하에서 영전압스위칭이 되지 않는다는 문제점이 있다. 또한 1차측에환류 전류가 흐르기 때문에 1차측에 큰 도통손실이 발생하고, 정류기 다이오드의 높은 전압 스트레스로 인해 큰 포워드 전압 드립을 갖는 다이오드를 사용해야하는 문제점도 있다. 따라서 높은 효율을 얻기 위해서 이러한 스위칭손실과 도통손실을 줄이는 것이 필수적이다.

Fig. 1. Conventional three-level converter.

먼저 스위칭 손실을 개선하기 위해서 많은 연구자들이 영전압 스위칭을 달성할 수 있는 방법들을 제안해왔다 [11], 면저 [11]의 연구는 추가 다이오드를 사용하여 lagging 스위치의 영전압 스위칭 범위를 늘린 연구이다.이 연구는 경부하의 스위칭 손실을 줄일 수 있지만 많은 수의 소자를 필요로 하고 여전히 1차측의 환류전류를 갖고 있다는 단점이 있다. 다음으로 [12]에서 제안하는 컨버터의 경우 전부하에서 모든 스위치가 영전압 스위치가 가능하다. 하지만 1차측에 큰 공진전류를 갖고 있기 때문에 큰 도통 손실로 낮은 효율을 갖는다.

다음으로 도통손실을 낮추기 위해서도 많은 연구들이 진행되어져 왔다<sup>[13]-[16]</sup>. 먼저 [13]의 연구는 1차측 회로의 도통 손실을 저감하여 높은 효율을 가질 수 있는 회로를 제안했다. 하지만 추가적인 스위치를 필요로 하고, 정류기 다이오드에 높은 전압 스트레스가 걸린다는 문제

Paper number: TKPE-2019-24-6-3

Print ISSN: 1229-2214 Online ISSN: 2288-6281

Corresponding author: gwmoon@kaist.ac.kr, School of Electrical Engineering, KAIST

Tel: +82-42-350-8075 Fax: +82-42-350-8520

School of Electrical Engineering, KAIST Manuscript received May 9, 2019; revised Jun. 3, 2019 accepted Jun. 8, 2019

<sup>—</sup> 본 논문은 2018년 전력전자학술대회 우수논문상 수상논문임

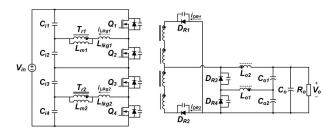

Fig. 2. Proposed three-level converter.

가 있다. 다음으로 [14]-[16]에서 제안하는 컨버터들은 1 차측에 환류전류가 없고, 정류기의 다이오드가 낮은 전압 스트레스를 갖는다. 이 컨버터들의 leading 스위치는 MOSFET을 사용하며 영전압 스위칭이 가능하다. 하지만 lagging 스위치는 IGBT를 사용하며 영전류 스위칭이 가능하지만, IGBT는 tail current 현상이 존재하며 높은 스위칭 주파수를 사용하지 못한다는 문제점이 있다.

앞서 설명한 [13]-[16]의 컨버터들은 모두 1차측에 클램핑 다이오드를 필요로 하고, 이 때문에 회로의 복잡도와 가격이 증가한다. 따라서 1차측 클램핑 다이오드를 제거한 듀얼 하프-브리지 캐스케이드 컨버터가 제안되었다<sup>[17]</sup>. 이는 두 개의 하프-브리지 구조를 결합하여 1차측에 클램핑 다이오드와 플라잉 커패시터를 제거한 구조이다. 이 컨버터는 정류기 다이오드의 전압 스트레스를 낮추고 절반의 환류전류를 제거했다는 장점을 갖고있지만 경부하에서 영전압 스위칭이 되지 않는다는 단점이 있다.

이 논문에서는 정류기 회로에 결합 인덕터를 적용한 새로운 3레벨 컨버터를 제안한다. 제안하는 컨버터는 2 차측 회로에서만 환류 전류가 흐르도록 하여 1차측에 환류전류가 없는 구조이고, 정규기 다이오드의 전압 링잉을 줄어 낮은 전압 스트레스를 가진다. 따라서 컨버터의 도통손실을 줄일 수 있다. 또한 전부하에서 영전압스위칭이 가능해 스위칭 손실을 줄일 수 있다는 장점이었다.

## 2. 제안회로의 동작 분석

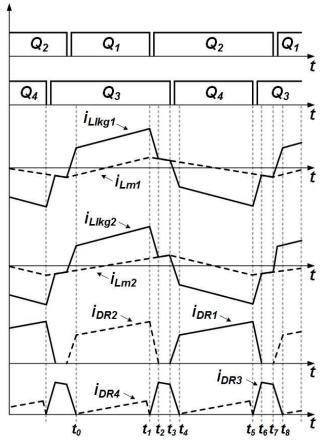

그림 2는 제안하는 컨버터의 회로를 나타내고 있다. 제안하는 컨버터는 2차측 회로에 결합 인덕터와 2개의다이오드를 사용한 구조이다. 스위치 Q<sub>1</sub>과 Q<sub>2</sub>는 서로 상보적으로 스위칭 동작을 하고 스위치 Q<sub>3</sub>와 Q<sub>4</sub> 또한 180도의 위상차를 가지며 서로 상보적으로 스위칭 동작을한다. 그림 3은 제안하는 컨버터의 동작 파형을 나타낸다. 두 개의 하프 사이클은 동일하기 때문에 하나의 동작만 설명한다.

모드 1 [ $t_0 \sim t_1$ ]: 모드 1 동안 스위치  $Q_1$ 과  $Q_3$ 가 켜져 있다. 이 모드동안 파워가 1차측에서 2차측으로 넘어간다. 출력전류는 다이오드  $D_{RS}$ 를 통해 흐르고, 결합 인덕

Fig. 3. Operational waveforms of proposed three-level converter.

터로 전류가 흐르기 때문에 다이오드  $D_{R4}$ 를 통해서도 전류가 흐른다. 다이오드  $D_4$ 로 흐르는 전류는 커패시터  $C_{c2}$ 의 current-sec balance를 맞출 수 있게 흐른다.

모드 2 [ $t_1 \sim t_2$ ]: 모드 2 동안 스위치  $Q_1$ 은 꺼지고 스위치  $Q_2$ 는 켜진다. 이 모드동안 스위치  $Q_2$ 의 영전압 스위칭이 달성된다. 처음에는 기생 인덕터 에너지가 영전압 스위칭을 돕지만 기생 인덕터 전류가 자화 인덕터전류와 같아진 이후부터는 자화 인덕터에너지 또한 영전압 스위칭을 돕기 때문에 스위치  $Q_1$ 과  $Q_4$ 에 비해 비교적 쉽게 영전압 스위칭을 달성할 수 있다.

모드 3  $[t_2 \sim t_3]$ : 모드 3 동안 스위치  $Q_2$ 와  $Q_3$ 가 켜져 있다. 이 모드동안 정류기 회로에서 환류전류가 흐르는 동작을 하게 된다. 환류전류가 결합 인덕터와 다이오드  $D_{R3}$ 를 통해 흐르기 때문에 정류기 회로에서만 흐르게 되고 1차측으로 환류전류가 넘어가지 않게 된다.

모드 4 [ $t_3 \sim t_4$ ]: 모드 4 동안 스위치  $Q_3$ 가 꺼지고 스위치  $Q_4$ 가 켜진다. 이 모드동안 스위치  $Q_4$ 의 영전압 스위칭이 달성된다. 기생 인덕터의 에너지로 영전압 스위칭을 돕기 때문에 스위치  $Q_2$ 와  $Q_3$ 에 비해 영전압 스위칭을 달성하기 어렵다.

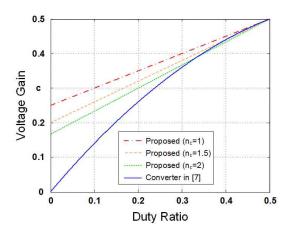

Fig. 4. Voltage gain according to duty ratio.

### 3. 제안회로의 특징 분석

## 3.1 DC 전압 이득

듀티 사이클 손실을 무시했을 때 컨버터의 전압 이득은 출력 인덕터의 voltage-sec balance식을 통해 구할 수 있다. 제안하는 컨버터의 출력 인덕터에 걸리는 평균전압, VLoavg은 다음과 같다.

$$v_{Lo,avg} = \left(\frac{V_{in}}{2n} - V_o\right)DT_s + \left(-\frac{n_c}{1 + n_c}V_{o1}\right)\frac{(1 - 2D)T_s}{2} = 0 \tag{1}$$

이때  $V_o$ 은 출력전압, n은 트랜스포머의 턴비, D는 스위치  $Q_1$ 과  $Q_4$ 의 듀티비,  $T_s$ 는 스위칭 주기 그리고  $n_c$ 는 결합 인덕터의 턴비이다.

따라서 제안하는 컨버터의 전압이득,  $M_{prop}$ 은 아래와 같이 구할 수 있다.

$$M_{prop} = \frac{1 + 2Dn_c}{2n(1 + n_c)} \,. \tag{2}$$

제안하는 컨버터의 전압 이득은 nc가 작아짐에 따라 커진다. 앞서 구한 방식과 같은 방식으로 [7]에서 제안 한 컨버터의 전압 이득,  $M_{conv}$ 을 구해보면 아래와 같고 이는 그림 4에 나타나 있다.

$$M_{conv} = \frac{D(3 - 2D)}{2n} \tag{3}$$

## 3.2 정류기 다이오드의 전압 스트레스

일반적으로 출력 인덕터가 있는 형태의 컨버터는 기생 인덕터와 정류기 다이오드의 기생 커페시터간의 공진으로 인해 정류기 다이오드에 큰 전압 오실레이션이존재한다.  $Q_1$ 과  $Q_3$ 가 켜졌을 때  $D_{R2}$ 와  $D_{R4}$ 를 따라 전류가 흐른다. 정류단 회로가 센터-탭 형태를 가지기 때문에  $D_{R1}$ 에 걸리는 전압,  $V_{DR1}$ 은  $D_{R3}$ 에 걸리는 전압  $V_{DR3}$ 에 비해 2배의 값을 가진다. 정류기 다이오드의 기생 커패

시턴스를  $C_D$ , 그리고 2차측 기생 인덕턴스를  $L_{lkg,c}$ 라고 했을 때  $v_{DR1}(t)$ 와  $v_{DR2}(t)$ 는 다음과 같이 표현된다.

$$v_{DR1}(t) = 2\left(V_o + n_c V_{o2} \cos(\omega_c t)\right). \tag{4}$$

$$v_{DR3}(t) = V_o + n_c V_{o2} \cos(\omega_c t) \tag{5}$$

여기서  $\omega_c = (L_{lkg,c}C_D)^{1/2}$  이다.

$Q_2$ 과  $Q_3$ 가 켜졌을 때  $D_{R3}$ 를 따라 전류가 흐른다.  $D_{R4}$ 에 걸리는 전압,  $v_{DR4}$ 은 다음과 같이 표현된다.

$$v_{DR4}(t) = V_{o2} + \frac{V_{o1}}{n_c + 1} \cos(\omega_c t)$$

(6)

다이오드의 리버스 리커버리 현상을 무시했을 때  $D_{R1}$ 과  $D_{R2}$ 에 걸리는 최대 전압은  $(2V_{in}/n-2V_o)$ 이고  $D_{R3}$ 에 걸리는 최대 전압은  $(V_{in}/n-V_o)$ 이고  $D_{R4}$ 에 걸리는 최대 전압은  $((n_c-1)V_{in}/(2nn_c(n_c+1))+V_o/n_c)$  이다. 마찬가지 방법으로 [7]에서 제안한 컨버터의 정류기의 다이오드에 걸리는 최대 전압을 구할 수 있다.  $D_{R1}$ 과  $D_{R4}$ 에 걸리는 최대 전압은  $(2V_{in}/n-AV_{in}/8n)$ 이고  $D_{R2}$ 와  $D_{R3}$ 에 걸리는 최대 전압은  $(2V_{in}/n-AV_{in}/4n)$ 이고 이때  $A=(3-(9-16nV_o/V_{in})^{1/2})$ .

#### 3.3 영전압 스위칭 조건

제안하는 컨버터의 leading 스위치는 기생 인덕터 에너지와 자화 인덕터 에너지가 모두 영전압 스위칭을 돕기 때문에 쉽게 영전압 스위칭을 달성할 수 있다. 하지만 lagging 스위치는 기생 인덕터 에너지로 영전압 스위칭을 달성하기 때문에 충분한 피크 자화 인덕터 전류가요구된다. 따라서 영전압 스위칭을 달성하기 위한 조건은 다음과 같다.

$$\frac{1}{2} \left( L_{lkg1} + L_{lkg2} \right) I_{Lm,peak}^{2} \ge C_{oss} \left( \frac{V_{in}^{2}}{2D} \right)^{2} \frac{1}{2D+1} . \tag{7}$$

여기서  $L_{lkgl}$ 은  $T_{r1}$ 의 기생 인덕턴스이고  $L_{lkg2}$ 는  $T_{r2}$ 의 기생 인덕턴스이고  $I_{Lm,peak}$ 는 피크 자화 인덕터 전류이고  $C_{oss}$ 는 1차측 스위치의 기생 캐패시턴스이다.

(7)을 이용하여 전부하에서 영전압 스위칭을 달성하기 위한 자화 인덕턴스의 조건을 구해보면 다음과 같다.

$$L_{m} \le \sqrt{\frac{(L_{lkg1} + L_{lkg2})(2D+1)}{2C_{oss}} \frac{D(1-D)}{2f_{s}}},$$

(8)

여기서  $L_m$ 은 자화 인덕턴스이고  $f_s$ 는 스위칭 주파수이다.

## 4. 실험 결과

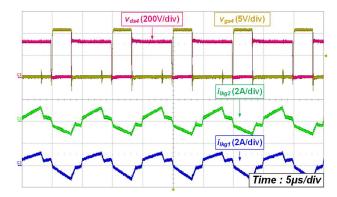

그림 5는 50% 부하 조건에서 제안한 컨버터의 실험 파형을 나타내고 있다. 그림의 기생인덕터 전류를 보면

Fig. 5. Experimental waveforms of proposed converter.

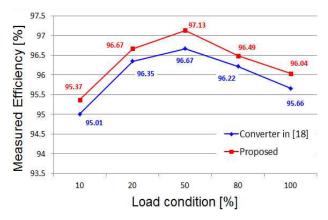

Fig. 6. Efficiency of proposed and conventional converters.

알 수 있듯이 환류모드동안 1차측에 환류 전류가 흐르지 않는다는 것을 확인할 수 있다. 그림 6은 제안한 컨버터와 [7]에서 제안한 컨버터의 효율을 나타내고 있다. 제안한 컨버터가 전부하에서 모두 효율이 높은 것을 확인할 수 있다. 경부하에서는 제안한 컨버터만 영전압 스위칭을 달성할 수 있어 낮은 스위칭 손실로 인해 높은 효율을 달성한다. 중부하에서는 1차측 회로의 환류전류를 제거하여 1차측 도통 손실을 줄이고 낮은 전압 스트레스를 갖는 정류기 다이오드를 사용하여 정류단 회로의 도통 손실을 감소시켜 높은 효율을 얻는다. 따라서 제안한 컨버터가 모든 부하 조건에서 [7]에서 제안한 컨버터에 비해 높은 효율을 달성할 수 있다.

#### 5. 결 론

본 논문에서는 전부하에서 영전압 스위칭을 달성하고 정류기 다이오드의 전압 스트레스를 낮출 수 있는 새로운 3레벨 컨버터를 제시하였다. 제안하는 컨버터는 영전압 스위칭 동작으로 경부하에서 높은 효율을 가지고 정류기 회로와 일차측 회로의 낮은 도통 손실로 인해 중부하에서 높은 효율을 얻을 수 있다. 따라서 제안하는 컨버터는 높은 입력전압을 갖는 어플리케이션에서 높은효율을 얻을 수 있을 것이라 기대된다.

본 연구는 한국전력공사 전력연구원의 지원을 받아 수행되었습니다.

#### References

- [1] T. C. Lim, B. W. Williams, S. J. Finney, and P. R. Palmer, "Series connected IGBTs using active voltage control technique," *IEEE Trans. Power Electron.*, Vol. 28, No. 8, pp. 4083–4103, Aug. 2013.

- [2] D. Sha, K. Deng, and X. Liao, "Duty cycle exchanging control for input series-output-series connected two PS-FB DC-DC converters," *IEEE Trans. Power Electron.*, Vol. 27, No. 3, pp. 1490-1501, Mar. 2012.

- [3] J. R. Pinheiro and I. Barbi, "The three-level ZVS-PWM DC-to-DC converter," *IEEE Trans. Power Electron.*, Vol. 8, No. 4, pp. 486-492, Oct. 1993.

- [4] W. Li, Q. Luo, S. Zong, X. He, and C. Xia, "Flying-capacitor-based hybrid LLC converters with voltage autobalance ability for high voltage applications," *IEEE Trans. Power Electron.*, Vol. 31, No. 3, pp. 1908–1920, Mar. 2016.

- [5] Y. Jang and M. M. Jovanovic, "A new three-level soft-switched converter," *IEEE Trans. Power Electron*, Vol. 20, No. 1, pp. 75–81, Jan. 2005.

- [6] D. Y. Kim, J. K. Kim, and G. W. Moon, "A three-level converter with reduced filter size using two transformers and flying capacitors," *IEEE Trans. Power Electron.*, Vol. 28, No. 1, pp. 46–53, Jan. 2013.

- [7] S. Han, G. Moon, and M. Youn, "A voltage-balanced phase-shifted three level DC/DC converter operating from high-input voltage," *IEEE Power Electron. Lett.*, Vol. 1, No. 3, pp. 74-77, Sep. 2003.

- [8] K. Jin, X. Ruan, and F. Liu, "An improved ZVS PWM three-level converter," *IEEE Trans. Ind. Electron.*, Vol. 54, No. 1, pp. 319–329, Feb. 2007.

- [9] I. O. Lee and G. W. Moon, "Analysis and design of a three-level LLC series resonant converter for high- and wide-input-voltage applications," *IEEE Trans. Power Electron.*, Vol. 27, No. 6, pp. 2966–2979, Jun. 2012.

- [10] J. R. Pinhiero and I. Barbi, "The three-level ZVS-PWM DC-to-DC converter," *IEEE Trans. Power Electron.*, Vol. 8, No. 4, pp. 486-492, Oct. 1993.

- [11] X. B. Ruan, D. Y. Xu, L. Q. Zhou, B. L. Li, and Q. H. Chen, "Zero voltage-switching PWM three-level converter with two clamping diodes," *IEEE Trans. Ind. Electron.*, Vol. 49, No. 4, pp. 790-799, Aug. 2002.

- [12] Y. Shi and X. Yang, "Wide load range ZVS three-level DC-DC converter: Four primary switches, capacitor clamped, two secondary switches, and smaller output filter volume," *IEEE Trans. Power Electron.*, Vol. 31, No. 5, pp. 3431–3443, May 2016.

- [13] F. Canales, P. M. Barbosa, and F. C. Lee, "A

- zero-voltage and zero current-switching three level DC/DC converter," *IEEE Trans. Power Electron.*, Vol. 17, No. 6, pp. 898–904, Nov. 2002.

- [14] T. T. Song, N. Huang, and A. Ioinovici, "A zero-voltage and zero-current switching three-level DC-DC converter with reduced rectifier voltage stress and soft-switching-oriented optimized design," *IEEE Trans. Power Electron.*, Vol. 21, No. 5, pp. 1204–1212, Sep. 2006.

- [15] E. Chu, X. Hou, H. Zhang, M. Wu, and X. Liu, "Novel zero-voltage and zero-current switching (ZVZCS) PWM three-level DC/DC converter using output coupled inductor," *IEEE Trans. Power Electron.*, Vol. 29, No. 3, pp. 1082–1093, Mar. 2014.

- [16] F. Liu, J. Yan, and X. Ruan, "Zero-voltage and zero-current switching PWM combined three-level DC/DC converter," *IEEE Trans. Ind. Electron.*, Vol. 57, No. 5, pp. 1644–1654, May 2010.

- [17] Z. Guo, K. Sun, and L. Zhang, "Analysis and evaluation of dual half-bridge cascaded three-level DC-DC converter for reducing circulating current loss," *IEEE J. Emerg. Sel. Topics Power Electron.*, Vol. 5, No. 1, pp. 351–362, Mar. 2017.

## 김건우(金建佑)

1993년 6월 25일생. 2015년 한국과학기술원 전기 및 전자공학부 졸업. 2017년 동 대학 원 전기 및 전자공학부 졸업(석사). 2017 년~현재 동 대학원 전기 및 전자공학부 박 사과정.

## 한정규(韓晶奎)

1991년 7월 15일생. 2014년 한국과학기술원 전기 및 전자공학부 졸업. 2016년 동 대학 원 전기 및 전자공학부 졸업(석사). 2016 년~현재 동 대학원 전기 및 전자공학부 박 사과정.

## 문건우(文建又)

1966년 10월 3일생. 1990년 한양대 전자공학과 졸업. 1992년 한국과학기술원 전기 및 전자공학과 졸업(석사). 1996년 동 대학원전기 및 전자공학과 졸업(공박). 2000년~현재 한국과학기술원 교수.