논문 2018-13-28

# 낮은 쓰기 성능을 갖는 비휘발성 메인 메모리 시스템을 위한 성능 및 에너지 최적화 기법

(Performance and Energy Optimization for Low-Write Performance Non-volatile Main Memory Systems)

정 우 순, 이 형 규\*

(Woo-Soon Jung, Hyung-Gyu Lee)

Abstract: Non-volatile RAM devices have been increasingly viewed as an alternative of DRAM main memory system. However some technologies including phase-change memory (PCM) are still suffering from relatively poor write performance as well as limited endurance. In this paper, we introduce a proactive last-level cache management to efficiently hide a low write performance of non-volatile main memory systems. The proposed method significantly reduces the cache miss penalty by proactively evicting the part of cachelines when the non-volatile main memory system is in idle state. Our trace-driven simulation demonstrates 24% performance enhancement, compared with a conventional LRU cache management, on the average.

Keywords: Non-Volatile RAM, Phase-Change memory, Cache memory, Proactive cache

## 1. 서 론

메인 메모리 장치로 많이 사용되는 DRAM의 단 점을 극복하기 위해 최근 다양한 종류의 비휘발성 메모리 (Non-volatile memory)에 관한 기술들이 연구/개발되고 있다. 특히, 상변화 메모리 (PCM, Phase-Change Memory) 기술은 나노미터 반도체 공정기술 (Nano-meter Semiconductor Processing Technology)을 통한 성능 및 집적도 개선이 가능하 므로 이에 관한 활발한 연구가 진행되어 오고 있다 [1]. 상변화 메모리는 물질의 상태 (State)에 따라 물질의 전기 전도도 차이가 존재하는 특성을 이용 한 비휘발성 메모리로서, 기존 DRAM과 유사한 읽 기성능을 보이면서 집적도가 높은 특성이 있지만 쓰기 성능은 수백 ns에서 수 us로 매우 낮다 [1]. 이에 PCM의 낮은 쓰기 성능을 극복하기 위해 반도 체 소자 수준에서부터, 마이크로구조, 시스템 수준 까지 다양한 연구들이 이루어져 왔다 [2,3].

비휘발성 메모리를 메인 메모리로 활용하고자

\*Corresponding Author (hglee@daegu.ac.kr)

Received: Aug. 16. 2018, Revised: Oct. 1. 2018.

Accepted Oct. 2. 2018.

W.S. Jung, H.G. Lee: Daegu University

하는 초기 연구들의 대부분은 쓰기 위주의 데이터는 DRAM에, 읽기 위주의 데이터는 PCM에 저장하는 PCM/DRAM 병행구조를 제시하였다 [4-7]. 이러한 방법은 PCM의 쓰기 횟수를 줄이는 데 많은 도움이 되지만, 이 방법을 구현하기 위해서는 컴파일러, 운영체제 또는 전용하드웨어를 통해 메모리접근 통계를 유지/관찰해야 할 뿐 아니라, 일부 상황에서는 추가적인 DRAM과 PCM간의 데이터이동으로 인한 성능/내구성 저하의 부담이 뒤따른다.

DRAM을 PCM의 상위차원 캐시 (Cache) 또는 버퍼(Buffer)형태 [8-10]로 연구한 논문들이 있다. 이러한 연구들은 설계 목적이 읽기성능을 향상하거나 [8], PCM의 내구성 (Endurance)을 향상할 목적으로 이에 대한 구체적인 설계내용이 빠져 있거나 [9], 압축을 통해 DRAM 캐시의 실효적인 크기(Effective size)를 최대화하여 성능을 높이고자 하는 연구 [10]가 대부분이다. 위와 같은 연구들은 DRAM을 활용하여 PCM으로의 쓰기 연산을 최소화하는 데는 많은 도움이 되고 있지만, 캐시실패(Cache miss)가 발생하거나 버퍼가 풀 (Full)이 되면 여전히 명시적인 PCM으로의 쓰기가 발생하고이 경우 PCM의 낮은 쓰기 성능으로 인한 시스템의성등 저하가 나타날 수 있다.

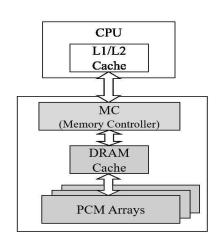

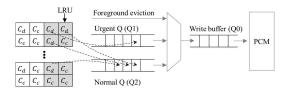

그림 1. DRAM 캐시-PCM 메인메모리 구조 Fig. 1 DRAM as a cache memory for PCM

본 연구에서는 그림 1과 같이 DRAM을 PCM을 비롯한 낮은 쓰기 성능을 갖는 비휘발성 메인 메모 리의 상위차원 캐시로 사용할 때, 캐시 실패나 버퍼 풀의 상황에서도 비휘발성 메모리의 낮은 쓰기 성 능으로 인한 실행시간 지연을 최소화할 수 있는 정 책인 선제적 반출 기법 (Proactive eviction technique)을 제안한다.

제안된 선제적 반출 기법은 사용되지 않으리라 고 예측되는 특정 캐시라인이 "Dirty"상태에 있으면 캐시실패가 발생하지 않더라도 메인 메모리가 유휴 상태에 있을 경우, 선제적으로 해당 캐시라인을 반 출 (Proactive eviction)하는 것이다. 선제적 반출로 확보된 캐시공간은 향후 동일한 캐시세트 (Cache set)내에서 캐시실패가 발생하더라도 새로운 데이터 를 캐시에 적재하기 위해 특정 캐시라인을 메인 메 모리로 반출하는 동작을 필요로 하지 않기 때문에 캐시실패로 인한 성능 저하를 최소화 할 수 있다.

제시된 선반출 기반의 캐시관리 정책의 효용성 을 검증하기 위해 실제 응용에서 추출한 메모리 트 레이스 (Trace)를 이용하여 시뮬레이션 평가를 실 시한 결과 제안된 기법은 선반출을 포함하지 않은 캐시 관리기법보다 평균 24%의 성능 향상 및 6% 의 에너지 소모 절감을 보였다.

본 논문의 구성은 본론인 II장에서 먼저 상변화 메모리에 대한 기초소개를 시작으로, 제시하고 있는 선반출 기반 캐쉬 메모리 기법에 관해 설명한다. 이 후 실험을 통해 제안된 기법의 효용성을 검증/분석 하고, III장에서 결론을 맺는다.

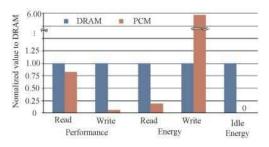

그림 2. DRAM과 PCM 비교 Fig. 2 DRAM vs. PCM: Device-level comparison

#### Ⅱ. 본론

# 1. 상변화 메모리 기초 및 DRAM과의 성능/에너 지 비교

메모리 셀이 포함하고 있는 전하의 양에 따른 전압 변화를 관측하는 DRAM과는 다르게 상변화 메모리는 셀을 구성하고 있는 칼코그나이드

(Calcognide)와 같은 특수 물질의 가열 후 냉각 방식에 따라 비결정질 (Amorphous) 상태와 결정질 (Crystalline) 상태의 두 가지 상태를 가지며 각 상 태의 저항 값의 차이를 이용하여 0과 1을 표현한 다. 비결정질 상태의 저항 값은 결정질 상태의 저항 값과 비교할 때 1,000~10,000배 더 큰 값을 갖는 다 [11].

그림 2는 DRAM과 PCM을 성능과 에너지 측면 에서 비교한 결과이다. 읽기 동작의 경우 PCM은 DRAM에 비해 유사하거나 조금 낮은 성능을 보이 지만, 소모되는 에너지는 DRAM의 20~30% 수준으 로 상당히 낮은 편이다. 반면 쓰기 동작은 DRAM에 비해 PCM이 상당히 낮은 성능을 보일 뿐 아니라, 쓰기 과정에서 소모되는 에너지 또한 6배 정도 높 게 나타난다. 따라서 PCM의 쓰기 동작을 최소화하 는 것은 PCM기반 메모리 시스템의 성능향상 및 예 너지 소모 절감에 큰 도움이 되지만, 반대로 쓰기 동작이 발생할 경우 큰 지연 시간 및 에너지 소모 증가는 피할 수 없게 된다. 마지막으로 PCM은 비 휘발성 기반 메모리이므로 유휴상태 (Idle)의 에너 지 소모는 0에 가까운 장점이 있다.

#### 2. 선반출 기반 DRAM 캐시 관리 기법

앞장에서 언급했듯, PCM을 사용하는 메모리 시 스템에서 쓰기동작이 발생할 경우 막대한 지연시간 의 증가를 피할 수 없게 된다. PCM을 메인 메모리 로 사용하는 시스템에서 PCM의 쓰기 동작은 일반

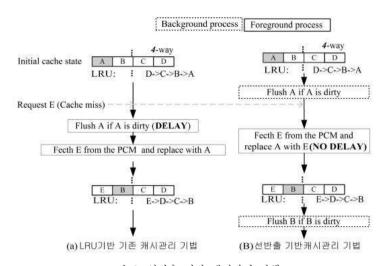

그림 3. 선반출 기반 캐시관리 정책

Fig. 3 Cache management based on a proactive eviction

적으로 상위차원의 캐시에서 캐시실패가 발생했을 때 주로 발생한다. 캐시실패가 발생하면 캐시제어기 는 해당 캐시세트 내에 새로운 데이터를 적재할 공 간을 마련하기 위해 1) 캐시라인 중 하나를 교체 블록으로 선정, 2) 선정된 캐시라인의 갱신 (dirty) 비트가 1로 설정되었을 경우 해당 캐시라인의 내용 을 메인 메모리 (여기서는 PCM)에 기록하는 반출 (Eviction 또는 Flush) 작업을 수행, 3) 반출이 완 료되면 반출된 캐시라인의 위치에 새로운 캐시라인 을 적재하는 동작을 한다. 본 논문에서 제안하는 관 리 기법은 가장 많은 시간이 소모되는 2)의 동작을 캐시실패에 따른 명시적 요청이 있을시 수행하는 것이 아니라, 선제적으로 수행함으로써 캐시실패 시 에 캐시라인의 교체를 큰 지연시간 없이 수행할 수 있도록 한다. 이러한 방법은 캐시실패에 따른 지연 시간을 줄이는 데 많은 도움이 되지만, 선반출 시점 및 선반출 대상을 선정하는 방법에 따라 많은 성능 의 차이를 보인다.

#### 2.1 임계점 기반 선반출 지원 DRAM 캐시 설계

선반출 기반 캐시관리 정책에 있어서 선반출 대상 및 시점을 결정하는 것은 성능향상에 중요한 요소이다. 본 연구에서 제안하는 선반출 대상 선정은 캐시적증률 (Cache Hit Rate)에 영향을 주지 않기위해 기존 연구에서 많이 사용하는 지역성 (Locality)에 기반을 둔 LRU (Least Recently Used) 교체 정책과 유사한 방법을 사용한다. 다만기존의 관리기법에서 LRU에 해당하는 캐시라인이

캐시실패시점에서 반출되는 반면, 본 연구에서 제안하는 선반출 기반 관리 기법은 여러 개의 캐시라인으로 구성된 각 캐시세트에 접근이 발생할 때마다수행되는 LRU 상태 업데이트 시점에서, 해당하는 캐시라인의 갱신비트가 설정되었을 경우 캐시실패가 없어도 선반출을 시작하게 된다. 그림 3은 LRU기반 기존 캐시관리 기법과 제안된 선반출 기반 캐시관리 기법을 비교 설명한다.

기존 캐시관리기법의 경우 그림 3 (a)에 표시된 것과 같이 "Request E"가 발생했을 때 캐시실패가 발생하며 새로운 캐시라인 E를 적재하기 위해 해당 캐시세트에서 LRU에 해당하는 캐시라인 A를 포어 그라운드 (Foreground)로 반출하게 되고, 이 경우 포어그라운드에서의 PCM 쓰기동작으로 인한 성능 지연이 뒤따르게 된다. 반면 그림 3 (b)와 같이 제 안된 기법의 경우 해당 캐시라인 A가 LRU 블록으 로 업데이트 되는 동시에 만약 A가 갱신비트가 1로 설정되었다면 캐시실패가 발생하지 않아도 캐시라 인 A를 즉시 선반출하게 된다. 이때 선반출 과정은 백그라운드 (Background)로 수행이 되기 때문에 전체 수행시간에 영향을 주지 않게 된다. 선반출이 완료된 이후 "Request E"가 발생했을 경우 LRU기 반 기존 캐시기법과 동일하게 캐시실패가 발생하지 만 제안된 방법에서는 시간이 많이 소요되는 캐시 라인 반출과정 없이 캐시라인 A의 위치에 새로운 캐시라인 E를 바로 적재할 수 있다. 이후 해당 캐 시세트의 LRU 캐시라인이 B로 바뀌게 되며, 이때 B의 갱신비트가 설정되었을 경우 동일한 선반출 과

# 248 낮은 쓰기 성능을 갖는 비휘발성 메인 메모리 시스템을 위한 성능 및 에너지 최적화 기법

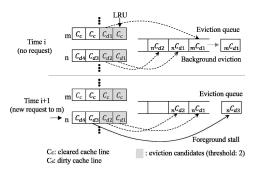

그림 4. 긴급성을 고려한 백그라운드 선반출 제어의 필요성 (임계값=2)

Fig. 4 Criticality-aware background eviction (Eviction threshold=2)

정이 백그라운드로 반복되게 된다.

제안된 기법의 가장 큰 목적은 포어그라운드로 수행되는 반출과정을 백그라운드로 변환하여 성능 지연을 최소화하는 것이 목표이다. 따라서 LRU에 해당하는 캐시라인 뿐 아니라 동일 캐시세트 내 에 갱신비트가 설정된 다른 캐시라인들도 가능하면 많 이 선반출 하는 것이 유리하겠지만, 너무 많은 캐시 라인을 선반출 할 경우 백그라운드 처리가 복잡하 게 될 뿐 아니라, 빈번한 선반출로 인해 PCM에서 의 에너지 소모가 증가된다. 따라서 선반출 가능한 캐시라인의 개수를 적절히 선정하여 백그라운드 반 출 제어의 복잡성을 줄이고 성능은 향상시키면서 에너지 소모 증가를 최소화하는 설정이 필수적이다. 이를 위해 본 연구에서는 동일 캐시세트 내에서 선 반출 가능한 캐시라인의 개수를 (Threshold)이라 정하고, 임계값 선정기법을 제안 하며 그에 따른 성능 비교 결과를 분석하였으며, 이 에 관한 결과는 실험 부분에서 설명한다.

# 2.2 백그라운드 반출 동작을 위한 효율적 큐 (Queue) 관리 기법

제안된 선반출 기반 캐시관리 기법의 가장 큰 장점은 향후 교체가 유력한 캐시라인들을 백그라운 드로 선반출 함으로써 포어그라운드 지연을 최소화하는데 있다. 따라서 효율적인 백그라운드 반출에 대한 제어가 필수적이다. 메모리 접근이 많지 않은 응용의 경우 백그라운드로 선반출 되는 캐시라인의수가 많지 않기 때문에 하나의 간단한 FIFO (First In First Out) 방식의 선반출 큐 (Eviction Queue)만으로도 효율적인 백그라운드 처리가 가능하다. 하지만 메모리 집중적인 (Memory-Intensive) 응용의

그림 5. 포어그라운드 지연을 최소화하기 위한 우선순위 기반 3-레벨 선반출 큐 관리 기법

Fig. 5 Priority-based 3-level eventing queue management for minimizing the foreground delay

경우 하나의 캐시세트 내에서 선반출 되는 캐시라 인의 수를 결정하는 임계값을 2 이상으로 설정하여 야 하며, 이럴 경우 잦은 백그라운드 반출로 인해 자칫 포어그라운드 반출까지 지연되는 현상이 발생 할 수 있다.

그림 4는 긴급성을 고려한 백그라운드 선반출 기법의 필요성을 설명한다. 그림에서 m, n은 캐시 세트의 번호를, C는 하나의 캐시라인을, d와 c는 캐시라인 C의 갱신 상태를 나타내는 "Dirty"와 "Clean"을 의미한다. 배경이 회색인 사각형은 해당 캐시세트에서 가장 높은 2개의 LRU에 해당하며, 반출 후보를 나타낸다 (임계값: 2). 위 경우, 선반출 을 위한 임계값은 2로 설정되어 있기 때문에 하나 의 캐시세트에서 최대 2개의 캐시라인이 선반출 되 는 것을 허용하며 하나의 FIFO방식의 선반출 큐를 사용하는 것을 가정한다. 이 경우 PCM의 낮은 쓰 기 성능 및 빈번한 선반출 요구로 인해 하나 이상 의 캐시라인들이 선반출 후보로 선정된 채 선반출 큐에서 대기하여 지연이 발생할 수 있다. 대기 중인 선반출 큐에 있는 캐시라인들은 PCM으로 완전히 반출되기 전까지 갱신비트를 "Dirty"로 유지한다.

캐시 요청이 없는 상태 (Time: i)를 나타내는 위 그림에서는 세 개의 캐시라인  $_{m}C_{d1},_{n}C_{d1},_{n}C_{d2}$ 가 순서대로 선반출 큐에 대기하고 있으며, PCM이 사용가능 한 상태일 경우  $_{m}C_{d1}$ 이 가장 먼저 반출되다

이 상태에서 새로운 캐시 요청이 있으며, 캐시실 패가 캐시세트 n에서 발생하는 경우 (Time: i+1) 캐시세트 n에는 "Clean" 상태의 캐시라인이 존재하지 않는다. 여기서  $_nC_{d8}$ 가  $_nC_{d4}$ 4 보다 높은 LRU를 갖는다고 가정하면, 선반출 큐의 반출 순서와 상 관없이  $_nC_{d8}$ 가 즉시 반출되어야 한다. 이 예는 선반출 기반 캐시라 할지라도 포어그라운드 지연이 발생할 수 있다는 점을 보여준다. 반출 큐 내부에

| 丑     | . 1. | . 시뮬레이션   | 면 시스템  | 의 구성       |

|-------|------|-----------|--------|------------|

| Table | 1.   | Simulated | system | parameters |

| No. of C          | CMP cores    | 16                               |  |  |

|-------------------|--------------|----------------------------------|--|--|

| Proc. co          | re type      | UltraSPARC-Ⅲ+, 2 GHz             |  |  |

| L1 cach           | es (private) | I/D-cache 32 KBs, 4-way, 64Bytes |  |  |

| L2 cach           | e (Shared)   | 2 MBs, 4-way, 64Bytes            |  |  |

| L3 cache (Shared) |              | 256 MBs DRAM, 8-way              |  |  |

| Main<br>memory    | DRAM Cache   | 256 MBs, 8-way                   |  |  |

|                   | PCM          | 8 GBs                            |  |  |

오직 캐시세트 n의 캐시라인들만 존재하는 매우 간단한 상황을 나타낸 예이며, 훨씬 복잡한 경우가 발생할 수 있다.

위와 같은 상황이 발생하는 경우, 반출 요구 시 점과 상관없이 더 많은 "Dirty" 상태를 갖는 캐시세 트를 보다 긴급성을 가지고 처리할 필요가 있다. 따 라서 본 연구에서는 우선순위에 기반한 백그라운드 선반출 처리를 위해 그림 5와 같이 우선순위를 정 할 수 있는 3단계 선반출 큐 관리 기법을 제안한다. 제안된 관리 기법은 PCM에 쓰기가 완료될 때까지 해당 캐시라인을 임시로 저장하고 있는 하나의 데 이터 큐 (Q0), 선반출 될 캐시라인을 가리키는 2개 의 포인터 큐 (Q1, Q2)와 하나의 멀티플렉서로 구 성되어 있다. Q0는 포어그라운드 반출요구를 가장 우선으로 처리하기 때문에 Q0에서 풀 (Full)이 발생 하지 않을 경우 포어그라운드 지연은 발생하지 않 는 다는 것을 의미한다. Q1과 Q2는 백그라운드 선 반출 큐로 사용되며, 포어그라운드 반출이 발생하지 않을 경우 긴급한 백그라운드 반출요구를 담고 있 는 Q1에 대한 선반출 요구가 먼저 진행되고, Q1에 대기하고 있는 선반출 요구 캐시라인이 없을 경우 마지막으로 Q2에 있는 선반출 요구가 가장 낮은 우 선순위로 백그라운드 반출을 수행하는 구조로 설계 되었다.

각 캐시라인이 어떤 반출 큐에 할당될 것인지를 정하는 우선순위는 해당 캐시세트의 "Dirty" 상태 캐시라인의 개수로 결정된다. 가장 높은 우선순위는 포어그라운드 반출이며, 총 4개의 캐시라인 중 3개 의 캐시라인이 "Dirty"인 경우 포어그라운드 반출에 이은 높은 우선순위를 가지므로, 반출 후보 캐시라 인들을 Q1과 Q2에 각각 적재하게 된다. 반면, 2개 이하의 캐시라인이 "Dirty"인 경우 Q1에는 적재하 지 않고, Q2에만 적재하게 된다.

표 2. PCM/DRAM의 성능/에너지 화라미터 Table 2. The performance/energy parameters used for PCM and DRAM

| Parar         | neter   | PCM      | DRAM   |

|---------------|---------|----------|--------|

| Latency(ns)   | Read    | 75       | 30     |

| Latelicy(lis) | Write   | 200      | 30     |

|               | Read    | 47.02    | 244.98 |

| Energy(ns)    | Write   | 2,504.35 | 227.10 |

|               | Idle(W) | 0        | 2.42   |

표 3. 사용된 벤치마크의 특성 Table 3. Benchmark characteristics

| Group<br># | Name         | R/W rate | Mem. access<br>per CPU cycle |

|------------|--------------|----------|------------------------------|

| 1          | dedup        | 1.40     | 0.0047                       |

|            | fluidanimate | 1.39     | 0.0047                       |

| 2          | x264         | 1.78     | 0.0023                       |

|            | vips         | 1.33     | 0.0016                       |

| 3          | freqmine     | 1.55     | 0.0016                       |

|            | ferret       | 1.53     | 0.0009                       |

| 4          | bodytrack    | 1.71     | 0.0008                       |

|            | Facesim      | 6.58     | 0.0002                       |

### 3. 실험

#### 3.1 실험환경

제안된 선반출 기반 캐시관리 기법을 평가하기위해 자체적으로 제작한 트레이스 기반의 메모리시뮬레이터 (In-house trace-driven memory simulator)를 사용하였다. 실험에서 사용된 메모리트레이스는 Simics [12] 시스템 수준의 시뮬레이터에서 실제 응용 프로그램을 수행하면서 추출하였다. 시뮬레이션 대상 시스템의 자세한 구성은 표 1에제시되어 있다. 표 2는 시뮬레이션에서 사용한 DRAM과 PCM의 성능/에너지 파라미터로서 기존의논문들 [13-15]을 참조하여 도출하였으며, 성능/에너지 값 64바이트 데이터 즉 하나의 캐시라인을 읽거나 쓰는 것을 기준으로 계산 하였다.

사용된 메모리 트레이스들은 PARSEC 벤치마크 [16]에 포함된 여러 개의 응용 프로그램을 이용하여 추출하였으며 벤치마크를 구성하고 있는 각 응용에 대한 특성들은 표 3에 정리되어 있다. 개별 응용에 대한 평가와 함께 좀 더 메모리 집중적인 응용을 구성하기 위해 각 응용의 특성에 따라 전체응용들을 4개의 응용그룹으로 분류 하였다. 그룹 1

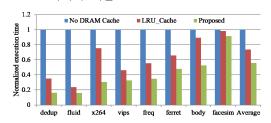

그림 6. 성능 비교 결과 (DRAM 캐시를 사용하지 않는 경우 정규화된 실행시간)

Fig. 6 Performance comparisons (normalized execution time to no DRAM cache configuration)

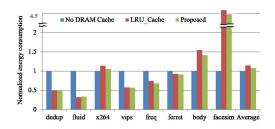

그림 7. 에너지 소모 비교 결과 (DRAM 캐시를 사용하지 않는 경우에 정규화 된 에너지 소모) Fig. 7 Energy consumption (normalized energy consumption to no DRAM cache configuration)

은 메모리 접근이 가장 많은 두 개의 응용으로 구성되어 있는 반면 그룹 4는 메모리 접근이 가장 적은 두 개의 응용으로 구성하였다. 그룹 2와 3은 그룹1과 4 사이의 메모리 접근 빈도를 가진다.

제안된 기법 ("Proposed"로 표현)의 성능 및 에너지 소모에 대해 DRAM 캐시를 사용하지 않고 PCM만을 메인 메모리로 사용하는 설정 ("No DRAM Cache"로 표현), 기존 LRU기반의 DRAM을 캐시로 설정 ("LRU Cache"로 표현)과 비교를 수행하였다. 모든 사용된 캐시의 쓰기 정책은 모두 지연쓰기 (Write back)를 적용하였다. 제안된 기법의 경우 임계값 (Th)은 1, 즉 동일 캐시세트 내에서 선반출 가능한 캐시라인의 수를 1로 설정하여 실험하였다.

## 3.2 실험결과 및 분석

그림 6은 제시된 3가지 설정에 대해 사용된 벤치마크의 응용별 성능을 비교한 결과 그래프이다. Y축은 응용별/설정별 실행시간을 나타내며 "No DRAM Cache"을 기준으로 정규화 (Normalized)하여 표현하였다. "LRU Cache"의 경우 실행시간은

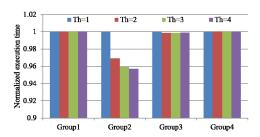

그림 8. 임계값 설정에 따른 성능 비교 (Th=1일 경우에 정규화 된 실행시간)

Fig. 8 Performance comparison according to the threshold (normalized execution time to Th=1)

최소 2%에서 최대 77%까지 향상을 보였으며, 제안된 선반출 기반 캐시관리정책까지 적용할 경우 최소 9% (facesim)에서 최대 84% (fluid)의 성능향상을 보였다. 이는 대부분의 응용에서 성능 지연의 주요 요인이 되는 포어그라운드 반출을 백그라운드 반출로 전환함으로써 얻어지는 성능향상으로 분석된다. 성능향상은 dedup과 x264을 제외하면 대체적으로 메모리 접근빈도가 높을수록 향상되는 결로 분석된다. 제안된 기법을 "LRU Cache"와 비교할경우에도 평균 23.9%의 향상을 보였다.

그림 7은 에너지 소모에 대해 비교한 결과이며 성능 그래프와 마찬가지로 "No DRAM Cache"를 기준으로 정규화하여 표현하였다. "LRU Cache"의 경우 DRAM에서 소모되는 에너지로 인해 일부 응용에 대해서는 "No DRAM Cache" 결과보다 많은에너지를 소모하는 것으로 나타난다. 이는 대부분의 응용에서 DRAM 캐시에서 소모되는 추가적인 에너지를 성능향상을 통해 상쇄되는 것으로 분석되지만, 성능향상이 충분치 않은 응용의 경우 오히려 전체에너지가 증가되는 현상을 보였다. 다만 제안된 기법을 "LRU Cache"와 비교해보면 에너지 소모는조금 증가/감소하는 경향을 보인 것으로 볼 때 에너지소모 측면에서는 선반출 동작이 에너지 소모를 크게 증가시키지 않는 것으로 분석할 수 있다.

마지막으로 그림 8은 임계값 설정에 따른 성능을 비교한 결과이다. 모든 결과 값은 임계값을 1 (Th=1)로 설정한 결과를 기준으로 정규화하여 표현하였다. 본 평가는 개별 응용을 실행하는 방법이 아닌 표 3에서 표현한 그룹별로 실행하여 상대적으로 높은 메모리 접근 빈도를 갖는 상태에서 평가하였다. 그림에서 보는 바와 같이 임계점에 따른 성능은 그룹 1,3 및 4 응용들에서는 임계값과 상관없이

거의 일정하게 나타났으며, 그룹 2는 임계값을 높일 경우 최대 4.4%의 추가적인 성능 향상을 보였다. 이는 임계값의 경우 메모리 접근 빈도 뿐 아니라 연속된 메모리 접근의 분포 (Distribution), 동일한 캐시세트로의 접근 분포 여부 등 다양한 원인이 복 합되어 나타난 결과로 분석 된다.

#### Ⅲ. 결 론

저비용 및 저전력이 가능한 상변화 메모리와 같 은 비휘발성 메모리에 대한 연구 개발이 활발해 지 면서 기존 DRAM기반 메인 메모리 시스템을 대체 할 메모리 기술로서 부각되고 있다. 그러나 상변화 메모리와 같은 일부 비휘발성 메모리들은 상대적으 로 낮은 쓰기 성능으로 인해 그 활용이 제한되고 있다. 이러한 점을 해결하기 위해 본 논문에서는 선 반출에 기반한 캐시 관리기법을 제안하였다. 제안된 기법은 PCM을 메인 메모리로 사용할 경우 낮은 쓰 기 성능으로 인해 캐시실패 시 발생할 수 있는 성 능 지연을 백그라운드로 수행하게 함으로서 캐시실 패에 따른 성능 지연을 효율적으로 감소할 수 있도 록 하였다. 메모리 트레이스에 기반한 시뮬레이션 평가 결과 제안된 기법은 LRU를 사용하는 기존 캐시 기법보다 평균 24%의 성능향상을, 6%의 에너 지 절감 효과를 보였다.

### References

- [1] R. F. Freitas, W. W. Wilcke, "Storage-class memory: the Next Storage System Technology," Journal of Research and Development, Vol. 52, No. 4/5, pp. 439-447, 2008.

- [2] T. Nirschl, J.B. Philipp, T.D. Happ, G.W. Burr, B. Rajendran, M. Lee, E. Joseph, "Write Strategies for 2 and 4-bit Multi-level Phase-change Memory," Proceedings of the IEEE International Electron Device Meeting, pp. 461-464, 2007.

- [3] M.K. Qureshi, M.M. Franceschini, J.P. Karidis, "Morphable Memory System: a Roust Architecture for Exploiting Multi-level Phase Change Memories," Proceedings of International Symposium on Computer Architecture, pp. 154–162, 2010.

- [4] B. Jung, J. Lee, "High Performance PCM&DRAM Hybrid Memory System," in IEMEK Journal of Embedded Systems and Applications, Vol. 11, No. 2, pp. 117~123, 2016 (in Korean).

- [5] G. Dhiman, R. Ayoub, T. Rosing, "PDRAM: a Hybrid PRAM and DRAM Main Memory System," Proceedings of the 46th Annual Design Automation Conference, pp. 464-469, 2009.

- [6] S. Lee, H. Banh, S. Noh, "CLOCK-DWF: A Write-History-Aware Page Replacement Algorithm for Hybrid PCM and DRAM Memory Architectures," IEEE Transactions on Computers, Vol. 63, No. 9, pp. 2187-2200, 2014.

- [7] X. Cai L. Jum M. Zhao, Z. Sun, Z. Jia, "A Novel Page Caching Policy for PCM and DRAM of Hybrid Memory Architecture," 13th International Conference on Embedded Software and Systems (ICESS), pp.67-73, 2016.

- [8] M. K. Qureshi, M. M. Franceschini, L. A. Lastras-montano, "Improving Read Performance of Phase Change Memories via Write Cancellation and Write Pausing," in International Symposium On High-Performance Computer Architecture, 2010.

- [9] M. K. Qureshi, V. Srinivasan, J. A. Rivers, "Scalable High Performance Main Memory System Using Phase-change Memory Technology," in International Symposium on Computer Architecture, 2009.

- [10] S. Baek, H. Lee, C. Nicopoulos, J. Kim, "Designing Hybrid DRAM/PCM Main Memory Systems Utilizing Dual-Phase Compression," ACM Transaction on Design Automation of Electronic Systems, Vol. 20, No. 1, 2014.

- [11] S. Raoux, G.W. Burr, M.J. Breitwisch, C.T.Rettner, Y.C. CHen, R.M. Shelby, C.H. Lam, "Phase-change Random Access Memory: a Scalable Technology," IBM Journal of Research and Development, Vol. 52, No. 4/5, pp. 465-479, 2008.

- [12] P.S. Magnsusson, M. Christensson, J.

# 252 낮은 쓰기 성능을 갖는 비휘발성 메인 메모리 시스템을 위한 성능 및 에너지 최적화 기법

- Eskilson, D. Forsgren, G. Hallberg, J. Hogberg, B. Werner, "Simics: a Full System Simulation Platform," Computer, Vol. 35, No. 2, pp. 50–58, 2002.

- [13] S. Kang W. Cho, B.H. Cho, K.J. Lee, C.S. Lee, H.R. Ohm Y.H. Ro, "A 0.1/spl mu/m 1.8V 256Mb 66MHz Synchronous Burst PRAM," in International Solid-State Circuits Conference, pp. 487 496, 2006.

- [14] A. P. Ferreira, B. Childers, R. Melhem, D. Mossee, M. Yousif, "Using PCM in Next-generation Embedded Space

#### Woo-Soon Jung (정 우 순)

Woo-Soon Jung received B.S and the M.S in Embedded System Engineering from Daegu University in 2015 and 2018, respectively. He is

currently a Ph.D. student in Daegu Uniersity. His research interests include low power system and artificial intelligence.

Email: jusemukengum@gmail.com

- Applications," IEEE Real-Time and Embedded Technology and Applications Symposium, 2010.

- [15] Samsung Electronics, "DDR2 registered SDRAM module, M393T5160QZA," Datasheet 저전력 시스템

- [16] C. Bienia, S.Kumar, J.P. Singh, K. Li, "The PARSEC Benchmark Suite: Characterization and Architecture Implications," Proceedings of the International Conference on Parallel Architectures and Compilation Technique, pp. 50–58, 2002.

#### Hyung-Gyu Lee (이 형 규)

Hyung-Gyu Lee received Ph.D. degree in Electrical and Computer Engineering from Seoul National University in 2007. He stayed in Samsung as a

senior research engineer. He stayed in Georgia Tech, USA as a Postdoctoral researcher. He is currently an associate professor of Information and Communication Engineering Department in Daegu University. His fields of interest include Low power system design, energy harvesting, low power memory.

Email: hglee@daegu.ac.kr