# 3 4H-SiC 기반으로 제작된▲ 쇼트키 다이오드의 계면 준위 분석

글\_**강홍전** 선임연구원 | 실리콘웍스 PDS팀 · **김형준** 명예교수 | 서울대학교 재료공학부

#### 1. 서론

4H-SiC는 고온, 고전압 안정성 및 높은 열전 도도로 인해 전력반도체 재료 시장에서 점유 율이 증가하고 있다. 또한 전기자동차 및 스마 트 그리드 시장의 증대와 맞물려 4H-SiC 전력 반도체 시장의 연평균 성장률과 규모는 2022 년에 각각 40%와 10억 달러가 될 것으로 예상 됐다[1].

기존의 실리콘에 비하여 4H-SiC는 밴드갭에 에너지 준위를 많이 포함하고 있으며 이종 접합 시계면 준위가 더 많이 발생한다. 계면 준위는 원자의 끊어진 결합(dangling bonds) 혹은 불순물 원자와 관련이 있으며 MOSFET 또는 IGBT의 sub-threshold swing과 쇼트키 다이오드의 장벽 높이에 영향을 준다. 소자를 제작할 때 진행하는 열처리 및 산화 과정이 계면 및단결정 내부에 에너지 준위를 발생시킬 수 있다. SiO₂/SiC의 계면 준위는 SiC가 산화되면서

SiO<sub>2(s)</sub>와 CO<sub>(g)</sub>를 생성하는데, 이때 산화막이 두 꺼워 지면서 C가 빠져나오지 못하고 계면에 남 아 에너지 준위를 형성하는 것으로 알려져 있 다 [2]. 남겨진 탄소 원자들로 생성된 에너지 준 위를 비 활성화시키기 위해 질화 처리가 이용 된 바 있으며 [3], 그 원인이 되는 산화과정을 감소시키기 위해 산화물을 증착한 뒤 NO gas 처리를 하여 계면 준위를 감소시킨 결과가 보 고됐다 [4]. 쇼트키 다이오드의 계면 역시 원자 의 끊어진 결합과 소자 제작 공정 동안 생성된 과잉 탄소가 계면 준위를 증가 시키며 이를 감 소시키기 위해 SiO<sub>2</sub>/SiC의 계면 준위를 감소시 키는 것과 비슷한 방법이 이용되기도 했다 [5]. 하지만, 지금까지의 연구 결과에서는 쇼트키 다이오드 계면 준위의 증감 정도는 알 수 있었 지만, 밴드갭 내에 존재하는 계면 준위의 에너 지 분포를 알기 어려웠다 [6].

본고에서는 Work function dependent barrier height 측정 방법과 깊은 준위 천이 검출기 (deep level transient spectroscopy; DLTS)를 이용한 계면 준위 측정 방법, 그리고 4H-SiC 쇼트키 다이오드의 계면이 산화 및 질화 처리 됐을때 발생하는 에너지 준위를 관찰 한 결과들을 소개한다.

# 2. 쇼트키 다이오드의 계면 준위의 검출

## 2.1 쇼트키 금속의 일함수에 의존하는 쇼트 키 장벽의 변화

연속적인 계면 준위 분포를 가정할 때, 쇼트 키 장벽 높이는 계면 준위 밀도 $(D_{tt})$  와 연관시킬 수 있다 [7].

$$\Phi_{Bn0} = C_2(\phi_m - \chi) + (1 - C_2) \left(\frac{E_g}{q} - \phi_0\right)$$

$$C_2 = \left(\frac{\epsilon_i}{\epsilon_i + q^2 \delta D_{it}}\right)$$

(1)

계면 준위 밀도 $(D_t)$ 가 높은 경우 식 (1)에서  $C_2$ 는 0에 가깝게 되고 장벽 높이는 우변 두 번째 항이 주도적으로 작용하여 밴드 갭과 중성 준위의 차이가 장벽 높이를 결정짓고 반대로  $D_t$ 가 낮으면  $C_2$ 가 1에 가까워져 우변 첫 번째 항이 주도적으로 작용하여 금속의 일함수와 전자 친화력(electron affinity)의 차이가 장벽 높이를 결정짓게 된다. 쇼트키 금속의 종류

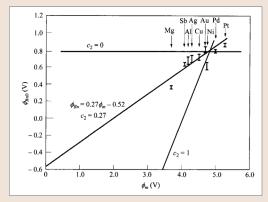

그림 1 ► Experimental barrier heights for different metals on N-type silicon.

를 변경하여 일함수를 조절하면 쇼트키 장벽의 높이가 변하게 된다 (그림 1). 그림 1의 쇼트키 다이오드의 C₂는 0.27 정도로 나타났으며수 Å의 계면 두께를 가정했을 때 계면 준위 밀도는 3e13/eV-cm²로 계산된다 [7]. 하지만 본방법으로 계면 준위를 측정하는 것은 금속을계속 바꾸어 주어야 하는 번거로움과 계면 준위의 분포를 확인하기 어려운 단점이 있다.

#### 2.2 DLTS의 원리와 계면 준위의 검출

쇼트키 혹은 pn 다이오드를 형성하고 역방 향 전압을 인가한 뒤 공핍 영역을 감소시키는 방향으로 전압 펄스를 넣어주면 밴드 갭 내부의 에너지 준위를 전하 나르개로 채워줄 수 있다. 펄스가 끝나면, 포획된 전하 나르개는 열적여기에 의해 에너지 준위에서 빠져나오게 된다. 이것은 소자의 정전용량 변화를 가져오며그 수가 지수함수형 감쇠(exponential decay)를하게 된다. 두 개의 특정 시간에 대한 정전 용량 변화를 온도의 그래프로 나타낸 것이 DLTS spectra가 된다. 이를 수학적으로 표현하면,

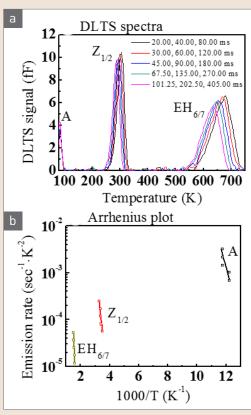

그림 2 ▶ (a) DLTS spectra with five rate windows and (b) its Arrhenius plot [6].

$$S(e_1) = \Delta C(e^{-e_1t_1} - e^{-e_1t_2}) \tag{2}$$

식 (2)의 e1에 대한 미분 방정식의 해는,

$$e_1 = (t_1 - t_2) / \ln(t_1/t_2) \tag{3}$$

즉 수학적 모델에서 DLTS의 peak 위치에서 방출 속도와 관찰 시간을 연관시킬 수 있다. 여러 개의 픽의 위치와 그때의 온도를 연결시킴으로써(그림 2(a)) Arrhenius plot을 얻을 수 있고(그림 2(b)) 이로부터 에너지 준위 ( $\Delta E$ )와 포획 반경 ( $\sigma$ )을 계산해 낼 수 있다.

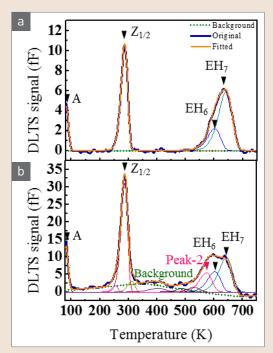

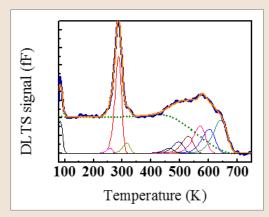

그림 3 ➤ DLTS spectra of (a) the bulk region and (b) interfaceincluded region of control sample. In the interfaceincluded region, background and peak-2 are additionally found [6].

$$e_1 = v_t N_c \sigma e^{\frac{-\Delta E}{kT}} = T^2 c e^{\frac{-\Delta E}{kT}} \tag{4}$$

실제 DLTS 측정에서는, noise를 감소시키기 위해 correlation function과 Lock-in amplifier가 도입이 되며 DLTS spectra와 방출 속도의 수학 적 표현들이 약간 더 복잡해진다 [8]. 이는 본고 의 주제를 벗어나기 때문에 더 자세히 다루지 않는다.

DLTS 측정 시 쇼트키 다이오드에 인가되는 펄스를 순방향 전위까지 높여주면, (p-type에 서는 전위를 낮춤) 계면 준위를 전하 나르개로

채워줄 수 있다. 하지만, 에너지 준위를 측정할 때 항상 reverse bias 및 전압 펄스가 인가되기 때문에, 계면 준위를 검출할 때 피치 못하게 단 결정 내부의 에너지 준위도 함께 검출된다. 따 라서 DLTS spectra를 분석할 때에는, 단결정 내 부와 계면의 에너지 준위 신호들을 구분해야 할 필요가 있다. 그림 3은 (a) 단결정 내부 신 호와 (b) 단결정 내부 및 계면 영역을 포함한 신호이며 각 peak들과 연속적인 계면 준위를 나타내는 background를 DLTS spectral fitting 을 통해 분리 한 것이다. DLTS peak의 모양은 Gaussian-Lorentzian 분포가 아니기 때문에 반 드시 DLTS spectra equation을 사용해야 한다 [6]. 쇼트키 다이오드의 계면 준위가 분포하는 두께 확인이 어려워 계면 준위 밀도에 대한 절 대 값을 구하기 어렵고 spectra의 intensity를 통 하여 상대적인 비교를 진행할 수 있다 [6].

# 3. 4H-SiC 쇼트키 다이오드의 계면 준위

### 3.1 산화 및 질화 처리가 계면 준위에 미치는 영향

쇼트키 다이오드 계면에 산소 또는 질소와 관련된 에너지 준위들을 좀 더 두드러지게 확 인하기 위해 계면을 고의로 산화시키거나 질 화시켜 관찰하기도 하였다 [6]. 그림 4는 4H-SiC의 표면을 1,200°C에서 산화시키고 산화막 을 제거한 뒤 제작한 쇼트키 다이오드의 계면

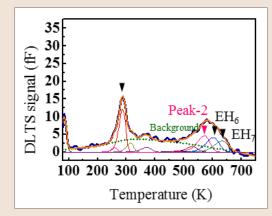

그림 4 ➤ DLTS spectra of interface-included regions of oxi dation at 1,200°Csample [6].

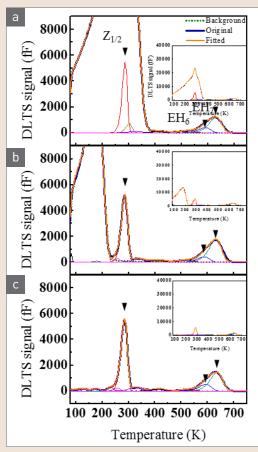

그림  $5 \triangleright$  DLTS spectra of (a) Ar 1,200°C, (b)  $N_2$  1,200°C, and (c) NH $_3$  1,200°Csamples, respectively [6].

영역이 포함된 DLTS spectra이다. 산화 처리된 표면의 계면 준위는 증가하며 반대로 단결정 내부 준위  $Z_{1/2}$ 와  $EH_{6/7}$ 이 감소하였다. 내부 준위의 감소는 과잉 탄소에 의한 것으로 추측된다 [9].

SiO<sub>2</sub>/SiC 계면의 경우 NO gas 분위기에서 열 처리 할 경우 에너지 준위 밀도를 낮출 수 있는 것으로 알려져 있으며 또한 NH<sub>3</sub> 처리로 계면 준위를 감소시킨 것이 보고됐다 [10], 그림 5는 SiC 표면을 1,200°C NH<sub>3</sub> gas 분위기에서 열처리한 뒤 제작된 쇼트키 다이오드의 DLTS spectra이다. SiO<sub>2</sub>/SiC계면에서 질화 처리가 계면 준위를 감소시키는 것과 달리 쇼트키 다이오드의 계면은 많은 에너지 준위가 생성되는 것으로 확인됐다. 이것은 아마도 SiO<sub>2</sub>/SiC 계면에는이미 많은 에너지 준위가 존재하지만, 쇼트키다이오드 계면에는 그 양이 상대적으로 적어오히려 질소와의 반응으로 계면의 무질서도가증가한 것으로 보인다. 또한 SiO<sub>2</sub>/SiC계면을 열처리 할 때는 SiO<sub>2</sub>가 완충 역할을 하는 반면, 쇼트키다이오드 제작 시 4H-SiC가 직접 NH<sub>3</sub>에노출됐기 때문일 수 있다.

#### 3.2 On-axis 기판의 계면 준위

4H-SiC 기판은 나선 전위와 관련된 결정 결 함을 줄이고자 결정학적 (0001) 방향에서 (11-20) 방향으로 4° off 된 substrate위에 epi-layer 를 성장시킨다. 하지만, basal plane dislocation 이 epi-layer와 함께 성장하여 표면에 이르게 되고 이것이 전력 반도체 소자의 성능을 크게 저하시키는 것으로 알려져 있다. 따라서 현재 on-axis 기판 위에 고품질 epi-layer를 성장시키 려는 시도가 진행되고 있다 [11]. 그림 6은 epilayer가 없는 on-axis기판을 이용하여 제작된 쇼트키 다이오드의 계면 영역이 포함된 DLTS spectra이다. 첫 번째 DLTS 측정에서 기판 내 부의 Z<sub>1/2</sub> 픽의 강도 보다 약 4배 큰 강도를 갖 는 background가 검출됐다. DLTS 측정 시 발 생하는 온도와 전계의 영향으로 픽의 변화가 관찰되는데 두 번째 DLTS 측정에서 계면 준위

그림 6 > DLTS spectra of interface included region on-axis substrate of (a) control, (b) second sweep, and (c) first sweep of Ar 1,500°C sample [6].

가 감소하면서 저온 쪽으로 background가 이동하였다. 또한 1,500°C 열처리 이후 계면 준위가 완전히 사라졌다. On-axis의 높은 계면 준위 밀도는 쇼트키 다이오드의 전류-전압 특성에서 이력현상이 나타나기도 하였다 [6].

#### 4. 맺음말

4H-SiC 표면을 고의로 산화시키거나 질화시켜 계면 준위를 부각시켜 관찰하였다. 질화 처리된 표면의 경우 계면 준위가 산화 처리된 쇼트키 다이오드의 계면 준위보다 더 크게 증가하였다. 질화 처리가 계면 준위 감소에 도움이된다는 기존의 연구들에서 벗어나는 결과처럼보이지만, 기존의 SiO<sub>2</sub>/SiC 계면에서는 SiO<sub>2</sub>가완충 역할을 하여 상대적으로 질화 정도가 더

약했을 것으로 생각되며 bare SiC로 제작된 쇼트키 다이오드의 경우 계면 준위가 현저하게 낮기 때문에 오히려 질화처리가 계면의 무질서 도를 높였을 수 있다. Epi-layer가 없는 on-axis기판을 이용하여 제작된 쇼트키 다이오드의 계면 영역이 포함된 DLTS spectra측정에서 기판 내부의 Z<sub>1/2</sub> 픽의 강도 보다 약 4배 큰 강도를 갖는 background가 검출됐으며 이러한 높은 밀도의 계면 준위는 전류-전압 곡선에 영향을 줄수 있다. ♣️

#### 참/고/문/헌

- [1] H. Lin, POWER SiC 2017: MATERIALS, DEVICES, MODULES, AND APPLICATIONS, https://www.systemplus.fr/wp-content/uploads/2018/07/YD18027\_Power\_SiC\_2018\_Materials\_Devices\_Applications\_July2018\_Yole\_Flyer.pdf (2018).

- [2] T. Akiyama, A. Ito, K. Nakamura, T. Ito, H. Kageshima, M. Uematsu, and K. Shiraishi, Surf Sci., 641, 174 (2015).

- [3] S. A. Correa, C. Radtke, G. V. Soares, L. Miotti, I. J. R. Baumvol, S. Dimitrijev, J. Han, L. Hold, F. Kong, and F. C. Stedile, *Appl. Phys. Lett.*, 94, 251909 (2009).

- [4] C. H. Kim, J. H. Moon, J. H. Yim, D. H. Lee, J. H. Lee, H. H. Lee, and H. J. Kim, *Appl. Phys. Lett.*, 100, 082112 (2012).

- [5] D. H. Lee, C. H. Kim, H. H. Lee, S. H. Lee, H. J. Kang, H. w. Kim, H. K. Park, J. Y. Heo, and H. J. Kim, IEEE ELECTRON DEVICE LETTERS, 35, 868 (2014).

- [6] H. J. Kang, Ph. D. Impurity-related Interface States of 4H-SiC Schottky Diode Observed by Deep Level Transient Spectroscopy, Seoul National University, Seoul (2018).

- [7] A. Cowley and S. Sze, J. Appl. Phys., 36, 3212 (1965).

- [8] C. Crowell and S. Alipanahi, Solid-State Electron., 24, 25 (1981).

- [9] K. Kawahara, J. Suda, and T. Kimoto, *J. Appl. Phys.*, 111, 053710 (2012).

- [10] C. H. Kim, S. H. Lee, J. H. Moon, J. R. Kim, H. H. Lee, H. J. Kang, H. W. Kim, J. Y. Heo, and H. J. Kim, ECS Solid State Lett., 4, N9 (2015).

- [11] H. W. Kim, H. H. Lee, Y. S. Kim, S. H. Lee, H. J. Kang, and J. Y. Heo, *Cryst. Eng. Comm.*, 19, 2359 (2017).

#### 저/자/약/력

| 성명 | 강홍전      |                            |

|----|----------|----------------------------|

| 학력 | 2011년    | 서울과학기술대학교 신소재공학과 공학사       |

|    | 2013년    | 2013년 서울과학기술대학교 재료공학과 공학석사 |

|    | 2018년    | 서울대학교 재료공학부 공학박사           |

| 경력 | 2018년-현재 | 실리콘웍스 PDS팀 선임연구원           |

성명 김형준 1976년 서울대학교 재료공학과 공학사 학력 한국과학기술원 재료공학과 공학석사 1978년 1985년 노스캐롤라이나 주립대학교 재료공학과 공학박사 경력 1978년-1981년 국방과학연구소 연구원 1986년-2018년 서울대학교 재료공학부 교수 2018년-현재 서울대학교 재료공학부 명예교수