http://dx.doi.org/10.17703/JCCT.2018.4.3.287

JCCT 2018-8-37

# 탄소나노튜브 방향성 수축 전송 방법이 CNTFET 기반 회로 성능에 미치는 영향에 관한 연구

# A Study on the Effect of Carbon Nanotube Directional Shrinking Transfer Method for the Performance of CNTFET-based Circuit

조근호\*

#### Geunho Cho\*

요 약 차세대 반도체 소자로 관심을 받고 있는 CNTFET은 소자의 소스와 드레인 사이에 CNT를 배치시켜, 기존 MOSFET보다 작은 전압으로 전자의 ballstic 혹은 near-ballastic 이동을 가능하게 만든 반도체 소자이다. CNTFET의 성능을 높이기 위해서는 많은 수의 CNT를 CNTFET 안에 높은 밀도로 배치해야 하기 때문에 CNT의 밀도를 증가시키기 위한 다양한 공정들이 개발되고 있다. 최근, 방향성 수축 전송 방법이 개발되어 CNTFET의 전류 밀도를 150uA/um까지 향상시켜줄 수 있음을 보이고 있어, CNTFET 기반 집적회로의 구현 가능성을 높이고 있다. 본 논문에서는, 방향성 수축 전송 방법으로 CNTFET 소자를 만들 경우, CNTFET 회로의 성능이 기존 MOSFET의 성능에 비해 얼마나 향상시킬 수 있는지 그 성능을 평가할 수 있는 방안을 논의하고자 한다.

주요어 : 방향성 수축 전송 방법, 탄소나노튜브 전계효과 트랜지스터, 탄소나노튜브, 공정편차, 선형 프로그래밍

Abstract The CNTFET, which is attracting attention as a next-generation semiconductor device, can obtain ballistic or near-ballistic transport at a lower voltage than that of conventional MOSFETs by depositing CNTs between the source and drain of the device. In order to increase the performance of the CNTFET, a large number of CNTs must be deposited at a high density in the CNTFET. Thus, various manufacturing processes to increase the density of the CNTs have been developed. Recently, the Directional Shrinking Transfer Method was developed and showed that the current density of the CNTFET device could be increased up to 150 uA/um. So, this method enhances the possibility of implementing a CNTFET-based integrated circuit. In this paper, we will discuss how to evaluate the performance of the CNTFET device compared to a MOSFET at the circuit level when the CNTFET is fabricated by the Directional Shrinkage Transfer Method.

Key words: Directional Shrinking Transfer Method, CNTFET, CNT, Process Variation, Linear Programming

\*정회원, 서경대학교 전자공학과 (교신저자) 접수일: 2018년 5월 6일, 수정완료일: 2018년 6월 2일 게재확정일: 2018년 7월 15일 Received: May 6, 2018 / Revised: June 2, 2018 Accepted: July 15, 2018 \*Corresponding Author: choroot@skuniv.ac.kr Dept. of Electronic Engineering, Seokyeong Univ, Korea

#### 1. 서 론

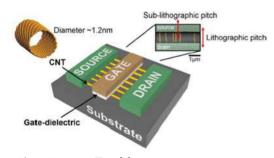

차세대 반도체로 각광받고 있는 CNTFET(Carbon NanoTube Field Effect Transistor)은 약 1um의 자유 이동경로(mean free path)를 갖는 CNT를 그림 1과 같 이 소자의 소스(Source)와 드레인(Drain) 사이에 배치 시켜 낮은 바이어스 전압으로 전자의 ballistic 혹은 near-ballistic 이동을 가능하게 만드는 구조로 되어 있 다. CNTFET 성능을 향상시키기 위해서는 CNTFET 안에 CNT가 동일한 그리고 좁은 간격으로 배치되어야 하나, 현재 공정 수준에서는 CNT의 밀도를 높이는데 부족함이 있어. CNTFET 기반의 집적회로를 구현하는 데 어려움을 겪고 있다. 더욱이, 정렬이 안 된(misaligned) CNT의 배치는 스크리닝 효과(screening effect)로 각 CNT에 흐르는 전류의 양을 변화시키고, CNTFET의 게이트 구조를 변경시켜, 게이트 커패시턴 스(gate capacitance)를 변화시킨다. 이와 같은, CNT-FET의 불규칙한 전류와 게이트 커패시턴스 변화는 안 정적인 CNTFET 회로를 구현하는데 걸림돌로 작용하 고 있다 [1]-[4].

그림 1. CNTFET 구조 [1] Figure 1. CNTFET Structure [1]

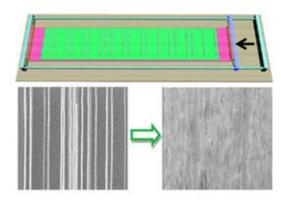

최근 개발된 방향성 수축 전송 방법(Directional Shrinking Transfer Method)은 그림 2와 같이 늘어난 탄성 필름(stretched elastic film) 위에 CNT를 배치시킨 후, 탄성 필름을 수축시키는 방법으로 CNT 배치밀도를 증가시키는 원리로 전류 밀도(current density)를 150 uA/um까지 향상시킴으로서, CNTFET 기반의 집적회로 구현에 대한 기대를 높이고 있다. 하지만, 그림 2와 같이, CNT 배치 밀도가 증가된 이후에도 여전히 CNT 사이의 거리가 불규칙하여, 앞서 언급한 정렬이되지 않은 CNT 배치효과에 의해 CNTFET 소자의 성능이 불규칙하게 변할 수 있다 [5].

그림 2. 탄소나노튜브 방향성 수축 전송 방법 [5] Figure 2. CNT Directional Shrinking Transfer Method [5]

CNTFET 소자 개발의 최종 목표가 CNTFET으로 구성된 집적 회로임을 감안할 때, 이러한 소자 성능의 변화가 회로에 미치는 영향을 분석하는 과정은 안정적인 CNTFET 기반 집적 회로를 성공적으로 구현하는데 필요한 중요한 요소라고 볼 수 있다. 따라서, 본 논문에서는 최근에 발표된 방향성 수축 전송 방법으로 CNTFET 제작 공정이 진행될 경우, 기존 MOSFET과 비교하여 어느 정도의 성능 향상 혹은 변화가 있는지 자세히 분석해 보고자 한다.

# Ⅱ. 본 론

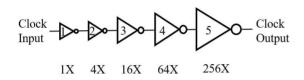

CNTFET 소자의 성능을 기존 MOSFET 소자와 함께 회로 레벨에서 비교하기 위해서, 본 논문에서는 디지털 회로 중 가장 기본이 되는 인버터(inverter)를 활용하여, 그림 3과 같이, 5단 FO4(Fan-Out Four) 인버터 체인(inverter chain)을 구성하여 그 성능을 비교해보고자 한다. 공정한 비교를 위해, 동일한 게이트 길이(gate length)를 구현하기 위한 32 nm MOSFET 그리고 32 nm CNTFET HSPICE 라이브러리 파일을 사용하였으며, 앞서 언급한 방향성 수축 전송 방법을 분석하여, 방향성 수축 전송 방법으로 CNTFET 소자를 만들 경우 나타나는 다양한 소자 특성을 CNTFET 회로성능 평가에 반영하였다.

일반적으로, MOSFET의 게이트 길이가 32 nm인 경우, MOSFET의 게이트 넓이(gate width)는, 그림 3과 같이, 게이트 길이의 배수(ex. 1배, 4배, 16배, 64배, 그리고 256배)로 설정하지만, CNTFET은 그림 1과 같이

CNT가 소스와 드레인 사이에 배치되므로, 게이트 넓이를 결정할 때, CNTFET 안에 배치되는 CNT의 수와 CNT 사이의 간격을 함께 결정해 주어야 한다. [5]에서 방향성 수축 전송 방법을 사용할 경우, 1.3 nm인 CNT를 최대 80 tubes/um로 배치시킬 수 있음을 보이고 있어, CNT 사이의 간격이 12.5 nm임을 알 수 있으며, 이경우, 게이트 넓이가 32 nm일 때, 약 3개의 CNT가 배치될 수 있음을 알 수 있다. 따라서, CNTFET의 게이트 넓이를 그림 3과 같은 배수로 설정할 때, 기본 게이트 넓이(32 nm)에 CNT를 3개씩 배치시키는 방식으로인버터 체인을 구성하였다.

그림 3. 인버터 체인 Figure 2. Inverter Chain

이와 같은 설정으로 MOSFET과 CNTFET의 회로 성능을 비교한 결과, 표 1과 같이, CNTFET은 MOSFET보다 지연(delay) 측면에서 약 3배 그리고 파워 (power) 측면에서 약 4배의 성능 향상이 있음을 알 수 있다. 이는 CNT의 높은 전도성으로 인해, 동일한 게이트 길이에 대해 더 많은 전류를 흘릴 수 있기 때문으로볼 수 있다. 추가로, [5]에서 사용한 CNT의 길이는 200 nm이므로, 실제적인 공정 상황을 반영하기 위해, MOSFET과 CNTFET의 길이를 200 nm로 늘려, 두 소자의 성능을 비교하였다. 그 결과, MOSFET의 지연은약 45배 증가하는 반면, CNTFET은약 15배 증가하는데 그친다.이는 앞서 언급하였듯이, CNT의 우수한 전도성으로인해, 게이트 길이 증가에 대한 지연 증가 정도가 상대적으로 적기 때문으로볼 수 있다.

이러한 CNT의 우수한 성능은, 하지만, CNT를 배치시키는 공정에서, 그림 2와 같이, 주어진 모든 공간에 CNT가 배치될 수 없으며, CNT 사이의 간격 역시 불규칙해 질 수 있어, CNTFET의 성능이 저하될 수 있음을 예상할 수 있다. 앞서 언급한 바와 같이, CNT 수의 감소는 소스와 드레인 사이에 흐르는 전류량을 감소시키고, CNT 사이의 불규칙한 거리 변화는 각 CNT에 흐르는 전류의 양을 변화시켜, 결국 CNTFET 전체의

전류 양을 감소시키고 불규칙하게 만든다. 동시에, 이러한 CNT의 변화는 CNTFET 소자의 게이트 구조를 변화시켜 게이트 커패시턴스 역시 변화 시킨다. 이러한 전류와 게이트 커패시턴스의 변화가 CNTFET 회로의성능을 얼마나 변화시키는지 알아보기 위해, CNTFET의 CNT의 수가 약 30% 감소했을 때(그림 2 참조), CNTFET회로의 성능 변화를 시뮬레이션 해 보았다. CNT 수 30% 감소는, 게이트 넒이 32 nm 기준으로, 3개의 CNT 중 1개가 배치되지 못한 상황을 의미한다.

표 1. MOSFET과 CNTFET 회로의 지연과 파워 Table 1. Delay and Power of MOSFET and CNTFET

| Table 1. Belay and 1 ewer of Meet Et and ettil Et |               |               |                |                |  |  |

|---------------------------------------------------|---------------|---------------|----------------|----------------|--|--|

|                                                   | Delay<br>(ps) | Power<br>(uW) | Delay<br>Ratio | Power<br>Ratio |  |  |

| MOSFET<br>32nm                                    | 15.140        | 27.600        | 0              | 0              |  |  |

| CNTFET<br>32nm                                    | 4.385         | 6.970         | 0              | 0              |  |  |

|                                                   |               |               |                |                |  |  |

| MOSFET<br>200nm                                   | 685.900       | 18.180        | 45.304         | 0.659          |  |  |

| CNTFET<br>200nm                                   | 14.890        | 139.500       | 3.396          | 20.014         |  |  |

표 2. 결함이 존재하는 CNTFET 회로의 지연과 파워 Table 1. Delay and Power of Defective CNTFET

|                                          | Delay<br>(ps) | Power (uW) | Delay<br>Diff.<br>(%) | Power<br>Diff.<br>(%) |

|------------------------------------------|---------------|------------|-----------------------|-----------------------|

| Evenly<br>Defective<br>CNTFET<br>200nm   | 15.430        | 102.000    | 3.627                 | -26.882               |

|                                          |               |            |                       |                       |

| Unevenly<br>Defective<br>CNTFET<br>200nm | 18.250        | 122.100    | 22.565                | -12.473               |

|                                          | 18.370        | 115.600    | 23.371                | -17.133               |

|                                          | 18.500        | 109.100    | 24.244                | -21.792               |

|                                          | 18.640        | 102.600    | 25.185                | -26.452               |

먼저, CNT 사이의 거리가 일정하게 유지되며, CNT의 수가 감소하는 경우, 즉, 균일한 결함이 존재하는 CNTFET(Evenly Defective CNTFET)의 경우, CNT-FET 회로의 성능을 시뮬레이션 하면(CNT의 길이는 200nm). 표 2와 같이, CNT의 수가 30% 정도 감소하였을 때, 결함이 없는 CNTFET과 비교하여 지연이

3.627% 증가하고, 파워는 26.882% 감소하는 것으로 나 타난다.

본 논문에서 언급한 최신 공정, 즉, 방향성 수축 전 송 방법을 사용한 경우라도, CNT의 수가 감소하였을 때, 그림 2와 같이 CNT 사이의 거리를 일정하게 만들 기는 아직 어렵다. 따라서, CNT 사이의 거리가 불규칙 한 경우, 즉, 불균일한 결함이 존재하는 CNTFET (Unevenly Defective CNTFET)에 대한 CNTFET 회로 성능 분석이 필요하지만, 현재까지 개발된 CNTFET HSPICE 라이브러리 파일은 CNT 사이의 거리가 일정 한 경우만 지원하기 때문에, CNT 사이의 거리가 불규 칙한 경우에 대한 회로 시뮬레이션은 불가능하다. 이러 한 불가능한 시뮬레이션을 가능하게 만들기 위해, 선형 프로그래밍(linear programming)을 활용한 시뮬레이션 방법이 과거 제시되었다. 방법은 불균일한 결함이 존재 하는 CNTFET의 전류와 게이트 커패시턴스를 먼저 계 산한 후, CNT 사이의 간격이 동일한 조건 하에, 같은 전류와 게이트 커패시턴스를 갖는 CNTFET 구조를 선 형 프로그래밍으로 찾는 방법이다 [6]-[8].

본 논문에서 분석 중인 불균일한 결함이 존재하는 CNTFET에 위에 언급한 선형 프로그램을 적용하면, 표 2와 같이, CNT가 30% 감소된 상황에서 CNT의 다양한 그리고 불규칙한 배치는 4개의 CNTFET 구조로 대표될 수 있음을 알 수 있다. 대표적인 4개의 CNTFET 구조를 통해, 불균일한 결함이 존재하는 CNTFET은 평균 23.842% 지연 증가와 함께 최대 25.185% 그리고 최소 22.565%의 지연 변화가 있음을 알 수 있다. 동시에, 평균 19.462% 파워를 감소시키며, 최대 26.452% 그리고 최소 12.473%의 파워 변화를 보이고 있다. 이러한 변화는 동일한 CNT수의 감소에 대해서도 그 위치에 따라 전류와 게이트 커패시턴스 양이 심하게 변할 수 있음을 보이고 있다. 따라서, 동일한 크기 그리고 동일한 수의 CNT를 갖는 CNTFET 소자라 할지라도 다양한 성능의 변화가 있음을 알 수 있다.

### V. 결 론

CNTFET의 우수한 성능에도 불구하고, CNT 배치기술의 미성숙은 CNTFET을 활용한 대규모 집적회로 구현을 어렵게 하고 있다. 본 논문에서는 이러한 어려움을 극복하기 위해 개발된 방향성 수축 전송 방법을

분석하여, 방향성 수축 방법을 통해 CNTFET 소자를 만들 경우, 기존 MOSFET에 비해 어느 정도의 성능 향상 그리고 변화가 일어날 수 있는지 그 정도를 회로 관점에서 분석해 보았다. 시뮬레이션 결과 CNT의 불규칙한 배열은 CNTFET의 지연을 평균 23.842% 파워를 평균 19.462% 각각 증가 그리고 감소시키고, 평균 지연 값과 파워 값을 각각 ±2% 와 ±7%의 변화시킴을 알 수 있었다.

## References

- [1] M. M. Shulaker et al., "Sensor-to-Digital Interface Built Entirely With Carbon Nanotube FETs," IEEE J. Solid-State Circuits, vol. 49, no. 1, pp. 190 201, 2014.

- [2] J. Deng, et al., "A Compact SPICE Model for Carbon-Nanotube Field-Effect Transistors Including Nonidealities and Its Application Part I: Model of the Intrinsic Channel Region," *IEEE Transactions on Electron Devices*, vol 54, pp. 3186–3194, Nov. 2007.

- [3] J. Deng, et al., "A compact SPICE model for carbon nanotube field effect transistors including non-idealities and its application—Part II: Full device model and circuit performance benchmarking," IEEE Transactions on Electron Devices, vol. 54, pp. 3195-3205, Nov. 2007.

- [4] N. Patil, J. Deng, A. Lin, H. S. P. Wong, and S. Mitra, "Design Methods for Misaligned and Mispositioned Carbon-Nanotube Immune Circuits," IEEE Trans. Comput. Des. Integr. Circuits Syst., vol. 27, no. 10, pp. 1725 1736, 2008.

- [5] J. Si et al., "Scalable Preparation of High Density Semiconducting Carbon Nanotube Arrays for High-Performance Field-Effect Transistors," ACS Nano, vol. 12, no. 1, pp. 627 - 634, Jan. 2018.

- [6] G. Cho and F. Lombardi, "Circuit-Level Simulation of a CNTFET With Unevenly Positioned CNTs by Linear Programming," IEEE Trans. Device Mater. Reliab., vol. 14, no. 1, pp. 234 244, 2014.

- [7] G. Cho, "A Study on the Process Variation Analysis for CNTFET-based Circuit Design," Journal of IKEEE, vol. 22, pp. 98–103, Mar. 2018.

- [8] G. Cho, "An Accuracy Improvement Method for the Analysis of Process Variation Effect on CNTFET-based Circuit Performance," Journal of IKEEE, vol. 22, pp. 420–426, Jun. 201.

- ※ 본 연구는 IDEC에서 EDA Tool를 지원받아 수행하였습니다.

- ※ 본 연구는 2018학년도 서경대학교 교내연 구비 지원에 의하여 이루어졌음.