# A Study on the Effective Downscaling Methodology for Design of a Micro Smart Grid Simulator

## Yun-Seok Ko<sup>†</sup>

**Abstract** – In this paper, a methodology was proposed to reduce the electrical level and spatial size of the smart grid with distributed generations (DGs) to a scale in which the electrical phenomena and control strategies for disturbances on the smart grid could be safely and freely experimented and observed. Based on the design methodology, a micro smart grid simulator with a substation transformer capacity of 190VA, voltage level of 19V, maximum breaking current of 20A and size of  $2 \times 2$  m² was designed by reducing the substation transformer capacity of 45MVA, voltage level of 23kV and area of  $2 \times 2$  km² of the smart grid to over one thousandth, and also reducing the maximum breaking current of 12kA of the smart grid to 1/600. It was verified that the proposed design methodology and designed micro smart grid simulator were very effective by identifying how all of the fault currents are limited to within the maximum breaking current of 20A, and by confirming that the maximum error between the fault currents obtained from the fault analysis method and the simulation method is within 1.8% through the EMTP-RV simulation results to the micro smart grid simulator model.

**Keywords**: Smart grid, Micro smart grid simulator, Distribution system, MEMS

#### 1. Introduction

Electrical phenomena and control methods on power grids have been studied for decades. As a result, various fault detection methods, service restoration methods [1-2] and feeder reconfiguration methods [3-4] have been proposed in order to improve the reliability of power supply and the efficiency of power grid operations. In particular, in references [5-7], some new distributed autonomous and adaptive control algorithms have been proposed for a smart grid. However, the proposed methodologies are rarely applied to actual distribution automation systems because of problems with reliability and stability. In addition, a smart grid with distributed generations (DGs) has a mixed structure in which a radial line and a loop line are mixed; this structure raises new problems such as protection coordination due to new electric phenomena arising from the new structure, making the existing problems more difficult to resolve [8-11].

In order for the proposed strategies to be successfully utilized, reliability and stability must be proved through application to a real distribution system. But, this is accompanied by a considerable number of uncertainties and risks because it is not possible to predict when a fault will occur; in the event of a real fault, it can cause severe outages due to inaccurate operation. Therefore, before applying the proposed algorithms to the real system, the

basic performance is typically verified using a demonstration test center. However, the configuration and size of a demonstration test center is very limited unlike the real smart grid, construction of which requires considerable economic costs and space cost of several km<sup>2</sup> or more. This makes it difficult to observe the electrical phenomena of other distribution lines (DLs) in large scale systems when a single fault occurs. This difficulty has become a major challenge in recent years. Also, it takes considerable time to prepare and is followed by great danger due to the fault current of maximum 12kA occurring from fault tests carried out at a substation transformer capacity of 45MVA and voltage level of 23kV. This problem, in reality, makes it difficult for engineers and researchers to gain experimental access, and renders it difficult to apply and evaluate the proposed algorithms. In order to overcome this issue, a new paradigm is required such that researchers can freely configure the smart grid in laboratories, observe the electric phenomena of the smart grid and evaluate the experiment results easily and safely. To meet these new requirements, a micro smart grid (SG) simulator that downscales the smart grid electrically and spatially is needed.

The development of the proposed micro SG simulator is planned in three stages, as it involves the design, making and application evaluation of each component as well as the micro SG simulator. The first stage is the design of the micro SG simulator's specifications. The second stage is the prototype making of the micro SG simulator with the bidirectional communication capability.

<sup>†</sup> Corresponding Author: Dept. of Electronic Engineering, Namseoul University, Korea. (ysko@nsu.ac.kr)

Received: October 17, 2017; Accepted: April 3, 2018

In the third stage, application studies including a sophisticated fault detection algorithm and a distributed, autonomous and adaptive control algorithm are performed. This paper presents the design of the micro SG simulator's specifications as the first step. So far, the miniaturization problem of systems and devices has been studied with MEMS technology in several fields [12-14]. However, no systematic method has been proposed to downscale the electrical level and size of the smart grid to the desired electrical level and space size.

Accordingly, in this paper, a methodology is proposed to reduce the electrical level and space size of the smart grid to a predetermined scale to design a micro SG simulator that can safely and freely experiment and observe the electrical phenomena and strategies to control disturbances on a smart grid with DGs. The maximum breaking current (MBC) of the protective devices (PDs) must be reduced as much as possible, since it plays an important role in downscaling the size of the power facilities such as PDs on the smart grid simulator. To solve this problem, in this paper, a fault current limiter (FCL) design method is proposed in which the target impedance value of the FCL is determined by simultaneously and repeatedly considering not only the impedance of FCLs but also the maximum voltage drop of the distribution line for the smart grid with FCL unlike the existing FCL application methods [15-17]. This will help to reduce the MBC values of PDs to the required level. Based on this FCL design methodology, an effective design methodology is developed to miniaturize the electrical level and space size of the smart grid, and then a micro SG simulator is designed using the design methodology. In order to verify the effectiveness of the proposed design methodology, it is checked whether the EMTP-RV fault simulation results for the micro SG simulator model are all within the predefined MBC of the PDs and the artificial fault generator (AFG). Also, the fault currents obtained from the fault analysis method are compared with those obtained from EMTP-RV simulation work for the micro SG simulator model.

## 2. FCL Design Methodology of Smart Grid

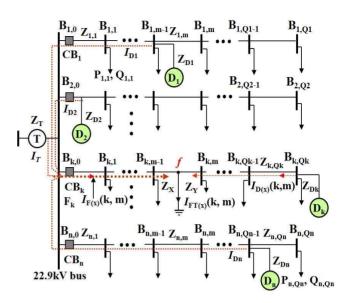

Generally, a smart grid consists of n DLs that receive electricity from one substation transformer, based on the configuration of the actual distribution system, and each DL comprises  $Q_n$  line sections, as shown in Fig. 1. Assume that the predetermined DG capacity, P[kVA] is allocated to each DL of the smart grid. At this time, r small capacity DGs with the same capacity (P/r)[kVA] and % impedance can be concentrated at one position or distributed at several positions of the DL. Because the former case has a greater

Fig. 1. The smart grid configuration with DGs

effect on the maximum fault current and minimum fault current of the DLs of the smart grid and simplifies the fault current calculation equation, it is appropriate to model the former case to determine the MBC values of PDs on the DLs. Accordingly, one large capacity DG is modeled as being connected to one DL as shown in Fig. 1. In Fig. 1, T and D<sub>i</sub> are the substation transformer and the ith DG, respectively, and  $I_T$  and  $I_{Di}$  are the secondary currents of T and the current of D<sub>i</sub>. Further, Z<sub>T</sub> and Z<sub>Di</sub> are % impedances of T and Di. Fi is the ith feeder, and CBi is the circuit breaker of  $F_i$ .  $B_{i,j}$  is the jth line bus of  $F_i$  and  $Z_{i,j}$  is the % impedance of the jth line section of F<sub>i</sub>. P<sub>i,i</sub> and Q<sub>i,i</sub> are the active power and reactive power of the jth line section of F<sub>i</sub>, respectively. If an arbitrary fault occurs at point f of the mth section of the kth line (F<sub>k</sub>) then the configuration of the fault impedance is determined by the location of the DG, as shown by the dashed line in Fig. 1.

The dashed line represents the current that flows from the substation transformer and DGs to the fault point f. In particular,  $I_{F(x)}(k, m)$  and  $I_{D(x)}(k, m)$  are the fault currents flowing from  $CB_k$  and  $D_k$  to f, respectively, and  $I_{FT(x)}(k, m)$ is the total fault current flowing into f, which is equal to the sum of  $I_{F(x)}(k, m)$  and  $I_{D(x)}(k, m)$ . Here, the subscript x is expressed as s for a three phase short circuit fault and g for a single phase ground fault. The paths from DGs connected to lines except  $F_k$  and substation transformer T to the 23kV bus, consist of parallel circuits. On the other hand, the fault circuit on the path from the 23kV bus to the faulty feeder depends on the location of the DG. In particular, the fault impedance is composed differently depending on whether DG is on an upstream position or on downstream position from f. Finally it can be represented as a variable resistor that has different impedance values according to the location of DG. In this paper, FCLs are introduced to reduce the fault current in the smart grid with DGs as

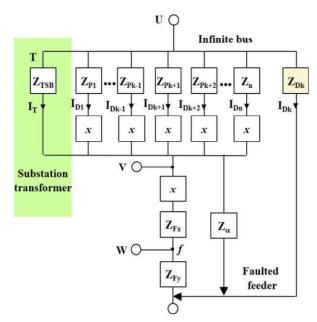

Fig. 2. Total impedance map of the smart grid

**Fig. 3.** Equivalent circuit for the total fault impedance circuit of the smart grid

shown in Fig. 1. FCLs play a major role in reducing the maximum fault current and the MBC of the PDs on a micro SG simulator within a target level. When applying the concept of infinite bus method in [18-19, 24] to a smart grid with n DLs, n FCLs and n DGs, the total impedance map of the smart grid can be represented as shown in Fig. 2.

In Fig. 2,  $Z_{TSB}$  is the path % impedance from power grid to secondary bus of T,  $Z_{Pi}$  is the path % impedance from  $D_i$  to secondary bus of T, and f is the fault location on the faulty feeder.  $Z_{Fx}$  and  $Z_{Fy}$  are upstream % line impedance and downstream % line impedance from f on the faulty feeder, respectively.  $Z_{\alpha}$  is the % line impedance from the 23 kV bus to the position of  $D_k$  on the faulty line  $F_k$ , and x is % impedance of FCL.

## 2.1 Computation of fault currents

The fault currents for a smart grid can be obtained by applying a symmetric coordinate method [18] to the total fault impedance circuit of Fig. 2. In Fig. 1,  $D_k$  is on the downstream line of the fault point f, but may be on the fault point or on the upstream line of fault point. Fig. 3 shows the equivalent circuit for the fault impedance circuit of a smart grid. In Fig. 3, (a) shows the equivalent circuit when DG is on the upstream line of the fault point f, (b) shows the equivalent circuit when DG is on the fault point f, and (c) shows the equivalent circuit when DG is on the downstream line of the fault point f, respectively. Here,  $Z_{\chi}$  is  $Z_{\alpha}$  minus  $Z_{Fx}$ .

Initially, the fault impedance  $Z_{UV}$  [%] obtained by the paths from DGs of adjacent feeders and the substation transformer T to the bus bar can be represented as Eq. (1).

$$Z_{UV} = \frac{1}{\sum_{i=1, i \neq k}^{n} \frac{1}{Z_{Pi} + x} + \frac{1}{Z_{TSB}}}$$

(1)

The total impedance of the fault impedance circuit,  $Z_{\rm UW}$  [%] can be represented as Eq. (2). In Eq. (2),  $\beta$  has a different value depending on whether the fault location f is an upstream location or a downstream location with respect to the DG on the DL experiencing the fault. If  $Z_{\alpha}$  is less than or equal to  $Z_{\rm Fx}$ , then  $\beta$  is 0; otherwise  $\beta$  is 1.

$$Z_{UW} = \frac{(Z_{UV} + x + Z_{\alpha} - \beta Z_{\chi})(Z_{Dk} + \beta Z_{\chi})}{Z_{UV} + x + Z_{\alpha} + Z_{Dk}} + (\beta - 1)Z_{\chi}$$

(2)

$I_{UV}$  can be represented as Eq. (3). In Eq. (3),  $I_{UV}$  is the fault current flowing from  $CB_k$  to fault location f.

$$I_{UV} = \frac{(Z_{Dk} + \beta \gamma)}{Z_{UV} + x + Z_{\alpha} + Z_{Dk}} \times I_{UW}$$

(3)

$I_{Dk}$  can be represented as Eq. (4). In Eq. (4),  $I_{Dk}$  is the fault current flowing from  $D_k$  to fault location f.

$$I_{Dk} = \frac{Z_{UV} + x + Z_{\alpha} - \beta \gamma}{Z_{UV} + x + Z_{\alpha} + Z_{Dk}} \times I_{UW}$$

$$\tag{4}$$

And,  $I_{UW}$  is the total fault current  $I_{FTk}$  flowing into the fault location f which is the sum of  $I_{UV}$  and  $I_{Dk}$ .  $I_{Di}$  (except for  $I_{Dk}$ ) and  $I_T$  can be computed through Eq. (5) and (6), respectively.

$$I_{Di(i \neq k)} = [Z_{IIV} / (Z_{Pi} + x)] \times I_{IIV}$$

(5)

$$I_T = \left(Z_{UV} / Z_{TSB}\right) \times I_{UV} \tag{6}$$

In the case of a three phase short circuit fault,  $Z_{Pi}$ ,  $Z_{TSB}$ ,  $Z_{UV}$ ,  $Z_{\alpha}$ ,  $Z_{Dk}$ ,  $Z_{UW}$ ,  $I_{UW}$ ,  $I_{UV}$  and  $I_{Dk}$  of Eq. (1)-(6) should be represented as  $Z_{Pi1}$ ,  $Z_{TSB1}$ ,  $Z_{UV1}$ ,  $Z_{\alpha 1}$ ,  $Z_{Dk1}$ ,  $Z_{UW1}$ ,  $I_{UW1}$ ,  $I_{UV1}$  and  $I_{Dk1}$ , which are the % positive sequence impedances and the % positive sequence currents respectively. At this time,  $I_{UV1}$ ,  $I_{Dk1}$  and  $I_{UW1}$  are  $I_{F(s)}(k, m)$  and  $I_{D(s)}(k, m)$   $I_{FT(s)}(k, m)$ , respectively. In Eq. (5)-(6),  $I_{Di(i\neq k)}$  and  $I_{T}$  should be represented as  $I_{Di1(i\neq k)}$  and  $I_{T1}$ , which are the corresponding positive sequence currents. Further,  $I_{UW1}$  becomes the three phase short fault current  $I_{s}$ , which is computed using Eq. (7) based on the symmetrical coordinate method.

$$I_s = \frac{100}{Z_{UW1}} \times \frac{P}{\sqrt{3} V} \tag{7}$$

In Eq. (7), V is base voltage [kV] and P is base capacity [MVA]. The currents in the substation transformer T and each  $D_i$  in case of the three phase short circuit fault are  $I_{T1}$ ,  $I_{Dk1}$  and  $I_{Di1(i\neq k)}$ .

In the case of a single phase ground fault,  $Z_{Pi}$ ,  $Z_{TSB}$ ,  $Z_{UV}$ ,  $Z_{\alpha}$ ,  $Z_{Dk}$ ,  $Z_{UW}$ ,  $I_{UW}$ ,  $I_{UV}$  and  $I_{Dk}$  of Eq. (1) - (6) should be represented as  $Z_{Pi0}$ ,  $Z_{TSB0}$ ,  $Z_{UV0}$ ,  $Z_{\alpha0}$ ,  $Z_{Dk0}$ ,  $Z_{UW0}$ ,  $I_{UW0}$ ,  $I_{UW0}$  and  $I_{Dk0}$  which are the corresponding % zero sequence impedances and zero sequence currents, respectively. If the % neutral ground resistance  $Z_{NGR}$  exists,  $Z_{TSB0}$  is  $Z_{TSB} + 3Z_{NGR}$ . In Eq. (5)-(6),  $I_{Di\ (i\neq k)}$  and  $I_{TSE0}$  should be represented as  $I_{Di0\ (i\neq k)}$  and  $I_{T0}$ , which are the corresponding zero sequence currents.  $I_{UW0}$  becomes the single phase ground fault current  $I_{g}$ , which is computed using Eq. (8) based on the symmetrical coordinate method.

$$I_g = \frac{3 \times 100}{Z_{UW0} + Z_{UW1} + Z_{UW2}} \frac{P}{\sqrt{3}V}$$

(8)

In Eq. (8),  $Z_{UW2}$  represents the % negative sequence impedance of  $Z_{UW}$ . The currents in the substation transformer T and each  $D_i$  in the single phase ground fault are obtained by Eq. (9), (10) and (11). Here,  $I_{UVg}$ ,  $I_{Dkg}$  and  $I_{UW0}$  become  $I_{F(g)}(k, m)$ ,  $I_{D(g)}(k, m)$  and  $I_{FT(g)}(k, m)$  for the single phase ground fault, respectively.

$$I_{UVg} = I_{UV0} + 2 \times I_{UV1} \tag{9}$$

$$I_{T_{\sigma}} = I_{T_0} + 2 \times I_{T_1} \tag{10}$$

$$I_{Dig} = I_{Di0} + 2 \times I_{Di1} \tag{11}$$

## 2.2 Determination of FCL

When a three phase short fault occurs at point f in the jth line section of the ith distribution line, the fault currents  $I_{F(s)}(i, j)$ ,  $I_{D(s)}(i, i)$  and  $I_{FT(s)}(i, j)$  are obtained

from Eq. (3), (4), and (7), respectively. On the other hand, when a single phase ground fault occurs at point f in the jth line section of the ith distribution line, the fault currents  $I_{F(g)}(i, j)$ ,  $I_{D(g)}(i, j)$  and  $I_{FT(g)}(i, j)$  are obtained from Eq. (9), (11) and (8), respectively. Therefore, FCL design is a matter of determining x such that the maximum value  $\times \lambda$  of fault currents  $I_{F(s)}(i, j)$  and  $I_{F(g)}(i, j)$ j) obtained from fault cases of all line buses B<sub>i,j</sub> is less than  $I_{Pmbc}$  and the minimum value of fault currents  $I_{F(s)}(i,$ j) and  $I_{F(g)}(i, j)$  obtained from fault cases of all line buses  $B_{i,i}$  are equal to or greater than  $\delta \times I_{Pmoc}$  for  $i \in U$ ,  $j \in V_i$ . Here, I<sub>Pmbc</sub> is the predefined maximum breaking current (MBC) of PDs of DLs, I<sub>Pmoc</sub> is the predefined minimum operating current (MOC) of PDs of DLs, U is the set of all DLs of smart grid and V<sub>i</sub> is the set of all line buses of the ith DL. V<sub>i</sub> is defined as a set of all line buses because the fault point must be a line bus instead of a line section in order to obtain more accurate the maximum fault current value and minimum fault current value. Also, the maximum value I<sub>dmax</sub>, and minimum value I<sub>dmin</sub> of fault currents  $I_{D(s)}(i, j)$  and  $I_{D(g)}(i, j)$  obtained from fault cases of all line buses  $B_{i,j}$  for  $i \in U$ ,  $j \in V_i$  are utilized to determine I<sub>Dmbc</sub> and I<sub>Dmoc</sub> of DGs in Fig. 5. Here, I<sub>Dmbc</sub> is the predefined maximum breaking current (MBC) of PDs of DGs, I<sub>Dmoc</sub> is the predefined minimum operating current (MOC) of PDs of DGs,  $\lambda$  is the safety factor that is considered to ensure so that PDs have sufficient fault current blocking capability, and  $\delta$  is safety factor that is introduced in order for the PD to work clearly.

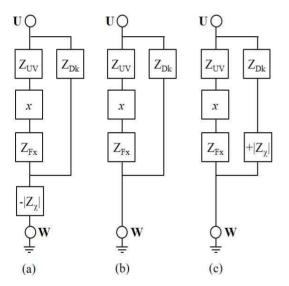

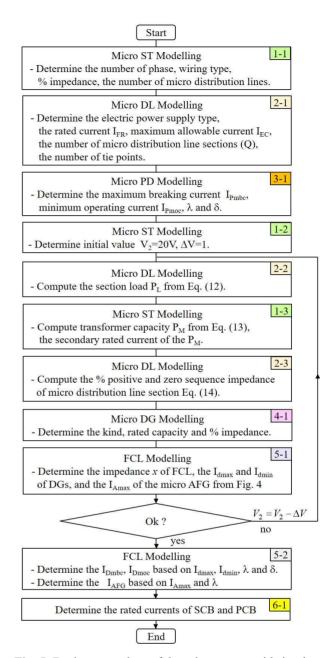

Unfortunately, since  $Z_{UV}$  is the nth order equation for x as shown in Eq. (1), it is impossible to obtain an equation for directly determining x from Eq. (3). Accordingly, it is necessary to determine x according to the following design procedure. The overall design procedure of FCL is shown in Fig. 4.

**Step 1** Determine the  $I_{Pmbc}$  and  $I_{Pmoc}$  of PD for the DLs on the smart grid. Where,  $I_{Pmoc}$  is  $\tau$  times the rated current of the distribution line, generally  $\tau$  is 2.

Step 2 Set the initial value of x, which is the impedance value of FCL, to 0, the value of  $\Delta$  to 0.1, and the value of DM to 0. Here DM stands for design mode. If DM is 0, it is a FCL design mode based on the change of x, whereas if DM is 1, it is a DL design mode that solves the problem based on the change of  $V_{MVD}$  when problem-solving is difficult with x only. Here,  $V_{MVD}$  is the maximum allowable voltage drop which is the management goal for voltage drop of DL in an electric power company.

**Step 3** Compute  $\{I_{FT(s)}(i, j)\}$  by applying Eq. (7) and then  $\{I_{F(s)}(i, j)\}$  and  $\{I_{D(s)}(i, j)\}$  by applying Eq. (3) and Eq. (4) to fault cases of  $B_{i,j}$  for  $i \in U, j \in V_i$ . Go to step 4.

Fig. 4. The design procedure of FCL

**Step 5** Compute  $\{I_{FT(g)}(i, j)\}$  by applying Eq. (8) and then  $\{I_{F(g)}(i, j)\}$  and  $\{I_{D(g)}(i, j)\}$  by applying Eq. (9) and Eq. (11) to the fault cases of line bus  $B_{i,j}$  for  $i \in U$ ,  $j \in V_i$ . And then go to step 6

**Step 6** Determine  $w_0 = \max\{I_{FT(g)}(i, j)\}, w_1 = \max\{I_{F(g)}(i, j)\}$ j)},  $w_2 = \min\{I_{F(g)}(i, j)\}, w_3 = \max\{I_{D(g)}(i, j)\}, w_4 = \min\{I_{D(g)}(i, j)\}, w_5 = \min\{I_{D(g$ (i, j). Go to step 7.

**Step 7** Set max  $\{v_0, w_0\}$  to  $I_{Amax}$ , max  $\{v_3, w_3\}$  to  $I_{dmax}$ and min  $\{v_4, w_4\}$  to  $I_{dmin}$ . Here,  $I_{Amax}$  is introduced in Fig. 5 to determine I<sub>AFG</sub> which is the maximum allowable current (MAC) of the AFG.

$\textit{Step 8} \;\; \text{Update max} \;\; \{I_{Amax}, \; {I_{Amax}}^*\}, \;\; \text{max} \;\; \{I_{dmax}, \; {I_{dmax}}^*\}$ and min  $\{I_{dmin},\,{I_{dmin}}^*\}$  as new  $I_{Amax},\,I_{dmax}$  and  $I_{dmin},\,$  and then go to step 9. Here, \* means the previous values.

Step 9 If DM is 0, go to step 10 to solve the problem in FCL design mode, otherwise go to step 12 to solve the problem in DL design mode.

Step 10 If x is less than the maximum allowable value 2.0, go to step 11, otherwise output Fail.

Step 11 If max  $\{v_1, w_1\} \times \lambda$  is less than  $I_{Pmbc}$ , then go to step 13, otherwise  $x=x+\Delta$  and go to step 3.

**Step 12** If max  $\{v_1, w_1\} \times \lambda$  is less than  $I_{Pmbc}$ , then go to step 13, otherwise output Fail.

Step 13 If min  $\{v_2, w_2\}$  is greater than  $I_{Pmoc} \times \delta$  then go to Step 14, otherwise set  $V_{MVD}$  to  $V_{MVD}$ - $\Delta_V$ , update the % impedance of distribution line sections to the newly calculated impedance value using Eq. (14), set BR to 1, and go to step 3. Here, the value of  $\Delta_V$  is 0.1.

Step 14 Determine x as the design value of FCL,  $V_{MVD}$ as new  $V_{MVD}$ , and output  $I_{dmax}$ ,  $I_{dmin}$ , and  $I_{Amax}$  to determine  $I_{Dmbc}$  and  $I_{Dmoc}$  of DGs and  $I_{AFG}$  of AFG in Fig. 5, and then output Ok.

### 3. Design of Micro Smart Grid Simulator

Here, a methodology for designing a micro SG simulator is developed based on the configuration of the real smart grid, the empirical knowledge obtained from the design experts of the power distribution system and the operating experts of automated distribution system, and [20].

## 3.1 Modelling of the micro ST

Generally, the substation transformer (ST) is a three phase three-winding transformer, and uses the wiring method of  $Y_g$ -  $Y_g$ - $\Delta$  or Y- $Y_g$ - $\Delta$  depending on whether the primary side is grounded or not. However, the threewinding transformer is costly, and difficult to construct and downsize because of its complicated structure. Therefore, through the fault impedance analysis, an easyto-build two-winding transformer is adopted for this study. Table 1 shows the equivalent impedance circuit of the power grid viewed from secondary bus of the substation transformer by wiring method. In Table 1, Z<sub>G1</sub> and Z<sub>G0</sub> are the % positive sequence impedance and the % zero sequence impedance of the source power grid, respectively. Z<sub>P</sub>, Z<sub>S</sub> and Z<sub>T</sub> represent the % impedance of the primary winding, the % impedances of the secondary winding and the tertiary winding respectively. Also, Z<sub>G0P</sub> is the sum of  $Z_{G0}$  and  $Z_{P}$ , and  $Z_{G0P}//Z_{T}$  is the parallel impedance of  $Z_{GOP}$  and  $Z_T$ .

Table 1. Equivalent impedance circuit by wiring method

| Sym.              | Primary | Equivalent impedance circuit                                            |                                                                                        |  |  |

|-------------------|---------|-------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--|--|

| circuit           | ground  | $Y_g$ - $Y_g$ - $\Delta$                                                | $\Delta$ - $Y_g$                                                                       |  |  |

| Positive sequence | yes/no  | $\bigcirc Z_{G1}$ $\bigcirc Z_{P}$ $\bigcirc Z_{S}$ $\bigcirc \bigcirc$ | $\circ$ $Z_{G1}$ $Z_P$ $Z_S$ $\circ$                                                   |  |  |

| Zero<br>sequence  | No      | $O-Z_T-Z_S-3Z_{NGR}-O$                                                  | $O-Z_T-Z_S-3Z_{NGR}-O$                                                                 |  |  |

|                   | Yes     | $O \begin{bmatrix} Z_{GOP} \\ Z_T \end{bmatrix} Z_S 3 Z_{NGR} O$        | $\bigcirc Z_{T} - Z_{S} - \begin{bmatrix} 3Z_{NGR} \\ 3Z_{COM} \end{bmatrix} \bigcirc$ |  |  |

In Table 1, although the zero sequence component of the equivalent impedance circuit of  $Y_g\text{-}Y_g\text{-}\Delta$  wiring is different from that of  $\Delta\text{-}Y_g$  wiring, it can be compensated for by introducing  $Z_{COM}$  in parallel to  $Z_{NGR}.$  However,  $Z_{COM}$  is not considered in this paper. It is because it offers more severe test conditions by reducing the ground fault current.

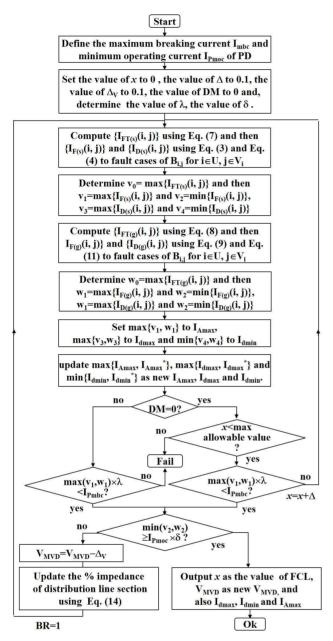

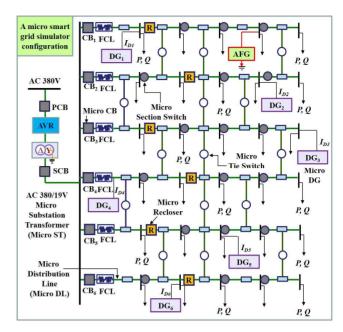

Accordingly,  $\Delta$ -Y<sub>g</sub> wiring is adopted which is the three phase, two-winding transformer. The secondary rated voltage V<sub>2</sub> of the micro substation transformer is determined to be 19V, based on the iterative design results of micro SG simulator shown in Fig. 5. This is intended to achieve the target MBC in the range of 20 to 15V. In general, a substation transformer supplies electric power to six DLs. Based on this configuration of the smart grid, six micro DLs supplied by one micro substation transformer are designed on the micro SG simulator.

#### 3.2 Modelling of the micro DL

The micro DL adopted an electric supply method of the 3-phase 4-wire type, which is the standard electric supply method of overhead lines on a smart grid. In particular, it is designed such that all micro DLs are made up of 5 line sections and 3 tie connections equally, based on the distribution system design standard. First of all, the rated current  $I_{FR}$  of the micro DL is designed to be safe enough to handle. Here, the  $I_{FR}$  is designed to be 0.76A. The maximum allowable current  $I_{EC}$  of micro DL can be set as 1A which is 1.4 times the rated current  $I_{FR}$  of the micro DL. If the loads of all line sections of all micro DLs are designed equally, based on  $V_2$  and  $I_{FR}$ , each section load  $P_L$  can be set at 4.75W+j1.56VAR by Eq. (12) with the load factor 0.95, which is the management goal of power factor in an electric power company.

$$P_L = \frac{1}{Q}\sqrt{3}V_2I_{FR} \tag{12}$$

In Eq. (12), Q is the number of line sections. The

Fig. 5. Design procedure of the micro smart grid simulator

capacity  $P_M$  of the micro substation transformer is designed as 190VA by Eq. (13). In Eq. (13), n is the number of micro DLs and  $\alpha$  is the safety factor of micro substation transformer. The  $\alpha$  value of the smart grid is about 1.3, but the  $\alpha$  value of the micro SG simulator is defined as 1.25. This is because the maximum load of a micro substation transformer is constant unlike that of the smart grid.

$$P_M = n\sqrt{3}V_2I_{FR} \times \alpha \tag{13}$$

If the positive sequence impedance  $Z_{LS1}$  of all line sections are designed to be the same, it can be computed by Eq. (14).

$$Z_{LSI} = V_{MVD} / \left( \frac{P_L}{\sqrt{3}V_2} \sum_{k=1}^{Q} Q - k + I \right)$$

(14)

In Eq. (14), because  $V_{\text{MVD}}$  is designed as 3%, the % impedance of Z<sub>LS1</sub> based on 190VA is determined as 5.06 + j10.11. The zero sequence impedance values  $Z_{LS0}$  of all line sections are designed to be the same as  $Z_{LS1}$ .

## 3.3 Modelling of the micro DG

Based on [8, 21-25], the fault current of PV inverter system connected to the power system is limited to 1.5 times the rated current of the PV system. The PV inverter system will be disconnected from the grid within half a cycle to protect the inverter components if a fault causes flow of more than 1.5 times the rated current. On the other hand, in the case of a wind turbine generator with a synchronous generator, a fault current of 5 to 8 times the rated current flows due to the effect of transient reactance. Therefore, the wind turbine system is selected as a micro DG since the wind turbine system has a greater influence on determining the MBC and total fault current of the PD. The capacity of the micro DG is determined to be 7.5VA, which is 30% of the micro DL capacity 0.76A as a power company aims to reach 30% of the line capacity in order to increase the efficiency of power utilization. Because the purpose of this paper is to determine the MBC of DGs rather than to observe the transient characteristics, the wind turbine generators are modeled with the % impedance. In particular, in order to obtain the maximum fault current at 8 times the rated current as shown in [21], the 7.5VA based % impedance  $Z_1(Z_0)$  is determined as j12.5 by 100/8. Here,  $Z_1$  and  $Z_0$  are the % positive sequence impedance and % zero sequence impedance, respectively.

#### 3.4 Modelling of the micro PD

PDs in the smart grid include CBs, reclosers, a section switch and a tie switch. In designing and making these PDs, the determination of the MBC is very important in determining the electrical level and size of the micro SG simulator. The I<sub>Pmbc</sub> of PDs on the micro SG simulator is designed to be 20A to reduce the size of the PDs to 13x13cm<sup>2</sup> by applying the relay as a switching device. This way, the system can be tested safely and freely in the laboratory, and it also reduces the space size of the smart grid to 4x4m<sup>2</sup>. Further, I<sub>Pmoc</sub> of the micro PDs on the micro DL is designed as 1.5A which is 2 times the rated current I<sub>FR</sub>, 1.5 times the maximum allowable current I<sub>EC</sub>. and sufficiently smaller than the MBC target value. Accordingly, the micro PDs should be able to operate at 1.5A and break the maximum current 20A when an artificial fault is generated on the micro SG simulator.

Furthermore, the values of  $\lambda$  and  $\delta$  are both set to 1.5 to ensure that PDs have sufficient fault current breaking capability and at the same time allow those PDs to work efficiently. Fig. 5 shows the overall design procedure of the micro SG simulator.

#### 3.5 Determination of FCL

The maximum fault current of the micro DLs on a micro SG simulator is hundreds of A. The FCLs are designed to make this fault current smaller than I<sub>Pmax</sub> and greater than  $\delta$  times  $I_{Popc}$  of the PDs mentioned above. The design procedure shown in Fig. 5 is implemented as an Excel program. Further, using the Excel program, the FCLs are designed as 0.  $9\Omega$ , and the  $I_{Dmbc}$  and  $I_{Dmoc}$  of DGs are designed as 5A and 0.5A, respectively. Also, the maximum allowed current IAFG of AFG is designed as 30A. Here,  $I_{\text{Dmbc}},\,I_{\text{Dmoc}}$  and  $I_{\text{AFG}}$  are designed with the same

**Table 2.** Specifications of the micro smart grid simulator

| Power facility |                                 | 0 1                                | Micro smart grid |                          |  |

|----------------|---------------------------------|------------------------------------|------------------|--------------------------|--|

| Ob.            | Attributes                      | Smart grid                         | simulator        |                          |  |

|                | Num. of phases                  | 3 phase                            | 3 phase          |                          |  |

|                | Wiring method                   | $Y-Y_g-\Delta$<br>$Y_g-Y_g-\Delta$ | Δ-Y <sub>g</sub> |                          |  |

|                | Capacity                        | 45 MVA                             | 190VA            | 20x20<br>cm <sup>2</sup> |  |

| ST             | % impedance                     | j15.9                              | j2               |                          |  |

|                | $\Omega$ based $Z_{\text{NGR}}$ | j0.6Ω                              | j0.05Ω           |                          |  |

|                | Rated voltage                   | 22.9 kV                            | 19V              |                          |  |

|                | Rated current                   | 1,512 A                            | 5.77A            |                          |  |

|                | Num. of feeders                 | 6                                  | 6                |                          |  |

|                | Supply type                     | 3p 4w                              | 3p 4v            | W                        |  |

|                | Rated current                   | 252A                               | 0.76A            |                          |  |

|                | Max current                     | 352.8A                             | 1A               |                          |  |

|                | Num.of sections                 | 5                                  | 5                |                          |  |

| DL             | Num. of ties                    | ≥3                                 | 3~6              |                          |  |

|                | Section load                    | 0.316MVA                           | 5VA              | 13x5cm <sup>2</sup>      |  |

|                | Section% imp.                   | 6.95+j14.92                        | 5.06+j10.11      | 13x5cm <sup>2</sup>      |  |

|                | V <sub>MVD</sub> (%)            | ≤ 5%                               | 3 %              |                          |  |

|                | Power factor                    | 0.95                               | 0.95             |                          |  |

|                | Rated capacity                  | 1MVA                               | 7.5VA            |                          |  |

|                | Rated current                   | 75.6A                              | 19V 0.228A       |                          |  |

| DG             | % impedance                     | -                                  | j12.5            | 13x20<br>cm <sup>2</sup> |  |

|                | MBC (I <sub>Dmbc</sub> )        |                                    | 19V 5A           | <b>V</b>                 |  |

|                | MOC (I <sub>Dmoc</sub> )        |                                    | 19V 0.5A         |                          |  |

| PD             | MBC (I <sub>Pmbc</sub> )        | 2,521A                             | 19V 20A          | 13x13                    |  |

|                | MOC (I <sub>Pmoc</sub> )        | 500A                               | 19V 1.5A         | cm <sup>2</sup>          |  |

| FCL            | $\Omega$ based $x$              | =                                  | j0.9Ω            | 13x5cm <sup>2</sup>      |  |

| AFG            | MAC (I <sub>AFG</sub> )         | -                                  | 19V 30A          | 8x8cm <sup>2</sup>       |  |

| SCB            | MOC (I <sub>SCB</sub> )         | -                                  | 19V 30A          | 8x8cm <sup>2</sup>       |  |

| PCB            | MOC (I <sub>PCB</sub> )         | -                                  | 380V 10A         | 8x8cm <sup>2</sup>       |  |

|                | Space size                      | 2x2km <sup>2</sup>                 |                  | 2x2m <sup>2</sup>        |  |

$\lambda$  and  $\delta$  values as in the PD design. The AFG is introduced to generate fault on the micro SG simulator. Table 2 shows the specifications of the micro SG simulator. The facilities attributes of the smart grid are obtained by [11].

## 3.6 Modeling of the power source

The fault current of the micro SG simulator does not affect the smart grid at all because it is very small compared to the load current of smart grid. On the other hand, the load current of smart grid on the power supply circuit will have an impact on the fault current of a micro SG simulator without an automatic voltage regulator. For a micro SG simulator without the automatic voltage regulator, as the line load of the smart grid is heavier and the installation location of the micro SG simulator is closer to the end of the line of the smart grid, the voltage drop of the smart grid will have more impact on the fault current of the micro SG simulator. Therefore, an automatic voltage regulator (AVR) is designed in front of the power source of the micro SG so that the fault test can be independently performed without being influenced by the voltage drop of the smart grid.

#### 3.7 Determination of SCB and PCB

In order to protect the micro SG simulator and engineer when an artificial fault is generated by AFG, a secondary circuit breaker (SCB) with I<sub>SCB</sub> of 30A is installed on the secondary side of the micro substation transformer. Here, I<sub>SCB</sub> is a minimum operating current (MOC) of SCB.

In a normal state, when an artificial fault is generated on the micro SG simulator, SCB with MOC of 30A is not activated since the fault current is limited within the I<sub>Pmax</sub> 20A of micro PD. On the other hand, because micro PDs are operated to protect the micro SG simulator, it is possible to observe the fault phenomenon and test the control strategy using these micro PDs. However, if the fault current exceeds 20A due to a physical fault on the micro SG simulator, micro PDs may be damaged or the operator injured. If the fault cannot be completely eliminated due to this problem, it can lead to a very dangerous situation, in which the in-built SCB protects the micro SG simulator and the operator. Also, a PCB with I<sub>PCB</sub> of 10A is designed on the primary side of the micro substation transformer to protect the circuit when the SCB does not work or when a fault occurs in a micro substation transformer. Here, IPCB is a minimum operating current (MOC) of PCB. Fig. 6 shows the overall configuration of the micro SG simulator designed by specifications shown in Table 2.

Fig. 6. Configuration of the micro smart grid simulator

#### 4. Validation of the Design Methodology

The validity of the proposed design methodology can be verified by confirming the effectiveness of the designed micro SG simulator model using it. For this purpose, the micro SG simulator model based on Table 2 and Fig. 2 is developed as an EMTP model [26], and the fault currents from the EMTP-RV simulation work are compared with the fault currents obtained from the design methodology.

## 4.1 Effectiveness of the micro SG simulator model

The effectiveness of the micro SG simulator can be verified by generating faults in all buses on the micro SG simulator model and then checking whether the fault currents met the design conditions of the micro PD, the design conditions of the micro DGs, and the design conditions of the AFG. First, the micro PDs were designed with  $I_{Pmbc}$  of 20A and  $I_{Pmoc}$  of 1.5A.

The effectiveness of the micro SG simulator can be verified by simulating faults in all buses Bii of the micro SG simulator and confirming that 1.5 times of fault currents  $I_{F(x)}(i, j)$  are less than 20A and that  $I_{F(x)}(i, j)$  are equal to or greater than 1.5 times 1.5A. In Table 3, for all cases, 1.5 times  $I_{F(x)}(i, j)$  is less than 20A and  $I_{F(x)}(i, j)$  is greater than 2.25A. From these results, the validity of the proposed design methodology can be verified.

Second, the PDs of the micro DGs have the I<sub>Dmbc</sub> of 5A and I<sub>Dmoc</sub> of 0.5A. The effectiveness of the micro SG simulator can be verified by simulating faults in all buses B<sub>i,i</sub> of the micro SG simulator and confirming that 1.5 times of fault currents  $I_{D(x)}(i, j)$  are less than 5A and that

**Table 3.** The fault currents  $I_{F(x)}(i, j)$

| i | Х | $I_{F(x)}(i,j)$ |           |           |           |           |           |

|---|---|-----------------|-----------|-----------|-----------|-----------|-----------|

| 1 |   | $B_{i,0}$       | $B_{i,1}$ | $B_{i,2}$ | $B_{i,3}$ | $B_{i,4}$ | $B_{i,5}$ |

| 1 | S | 11.73           | 9.65      | 7.96      | 6.76      | 5.89      | 5.22      |

| 2 | S | 11.72           | 9.64      | 8.18      | 7.09      | 6.27      | 5.47      |

| 3 | S | 11.68           | 9.64      | 8.18      | 7.09      | 6.26      | 5.62      |

| 4 | s | 11.69           | 9.39      | 7.81      | 6.68      | 5.84      | 5.19      |

| 5 | S | 11.68           | 9.64      | 8.18      | 7.10      | 6.10      | 5.35      |

| 6 | S | 11.68           | 9.64      | 8.18      | 6.91      | 5.97      | 5.27      |

| 1 | g | 11.30           | 9.39      | 7.78      | 6.64      | 5.78      | 5.13      |

| 2 | g | 11.31           | 9.39      | 8.00      | 6.97      | 6.17      | 5.39      |

| 3 | g | 11.29           | 9.39      | 8.00      | 6.97      | 6.17      | 5.54      |

| 4 | g | 11.30           | 9.13      | 7.63      | 6.55      | 5.74      | 5.11      |

| 5 | g | 11.30           | 9.39      | 8.00      | 6.96      | 6.00      | 5.27      |

| 6 | g | 11.30           | 9.39      | 8.00      | 6.77      | 5.87      | 5.19      |

**Table 4.** The fault currents  $I_{D(x)}(i, j)$

| i | x | $I_{D(x)}(i,j)$ |           |                  |                  |           |                  |

|---|---|-----------------|-----------|------------------|------------------|-----------|------------------|

| 1 |   | $B_{i,0}$       | $B_{i,1}$ | B <sub>i,2</sub> | B <sub>i,3</sub> | $B_{i,4}$ | B <sub>i,5</sub> |

| 1 | S | 1.77            | 1.82      | 1.51             | 1.28             | 1.12      | 0.99             |

| 2 | s | 1.61            | 1.65      | 1.71             | 1.76             | 1.83      | 1.58             |

| 3 | s | 1.57            | 1.60      | 1.65             | 1.71             | 1.76      | 1.83             |

| 4 | s | 1.82            | 1.47      | 1.22             | 1.05             | 0.92      | 0.82             |

| 5 | s | 1.66            | 1.71      | 1.76             | 1.83             | 1.56      | 1.37             |

| 6 | S | 1.71            | 1.76      | 1.82             | 1.53             | 1.33      | 1.17             |

| 1 | g | 1.77            | 1.82      | 1.52             | 1.29             | 1.13      | 1.00             |

| 2 | g | 1.62            | 1.66      | 1.71             | 1.76             | 1.83      | 1.59             |

| 3 | g | 1.57            | 1.62      | 1.66             | 1.71             | 1.76      | 1.82             |

| 4 | g | 1.82            | 1.48      | 1.24             | 1.06             | 0.93      | 0.83             |

| 5 | g | 1.67            | 1.71      | 1.77             | 1.82             | 1.57      | 1.37             |

| 6 | g | 1.71            | 1.77      | 1.82             | 1.54             | 1.34      | 1.18             |

**Table 5.** The total fault currents  $I_{FT(x)}(i, j)$

| i | X | $I_{FT(x)}(i,j)$            |           |                  |           |                  |           |

|---|---|-----------------------------|-----------|------------------|-----------|------------------|-----------|

| 1 |   | $\mathrm{B}_{\mathrm{i},0}$ | $B_{i,1}$ | B <sub>i,2</sub> | $B_{i,3}$ | B <sub>i,4</sub> | $B_{i,5}$ |

| 1 | S | 13.48                       | 11.50     | 9.46             | 8.05      | 6.97             | 6.11      |

| 2 | S | 13.31                       | 11.31     | 9.89             | 8.79      | 8.04             | 6.93      |

| 3 | S | 13.21                       | 11.27     | 9.84             | 8.78      | 7.98             | 7.33      |

| 4 | S | 13.52                       | 10.89     | 9.05             | 7.72      | 6.72             | 5.92      |

| 5 | S | 13.31                       | 11.36     | 9.94             | 8.91      | 7.59             | 6.60      |

| 6 | S | 13.37                       | 11.42     | 10.02            | 8.42      | 7.25             | 6.33      |

| 1 | g | 13.05                       | 11.16     | 9.24             | 7.84      | 6.79             | 5.97      |

| 2 | g | 12.87                       | 10.99     | 9.64             | 8.63      | 7.85             | 6.80      |

| 3 | g | 12.83                       | 10.95     | 9.59             | 8.58      | 7.80             | 7.19      |

| 4 | g | 13.11                       | 10.58     | 8.81             | 7.52      | 6.52             | 5.78      |

| 5 | g | 12.92                       | 11.05     | 9.70             | 8.69      | 7.43             | 6.47      |

| 6 | g | 12.98                       | 11.11     | 9.76             | 8.23      | 7.08             | 6.20      |

$I_{D(x)}(i, j)$  are equal to or greater than 1.5 times 0.5A. In Table 4, for all cases, 1.5 times  $I_{D(x)}(i, j)$  is less than 5A and the  $I_{D(x)}(i, j)$  is greater than 0.75A. Also, all fault currents from the DGs are in the range of 3.5 to 8 times the rated currents of the DGs.

Third, a micro AFG with IAFG of 30A was designed to generate an artificial fault on the micro SG simulator.

Its validity can be verified that 1.5 times of total fault currents  $I_{FT(x)}(i, j)$  obtained from the fault simulations in all line buses B<sub>i,i</sub> of the micro SG simulator, are less than the predefined I<sub>AFG</sub> of 30A. In Table 5, for all cases, it can be seen that the 1.5 times of max  $\{I_{FT(x)}(i, j)\}\$  is 20.22A and less than 30A. These results further verify the validity of the proposed design methodology.

#### 4.2 Effectiveness of the fault analysis method

The micro SG simulator design requires repetitive fault current computations to determine specifications that meet the design conditions of micro PDs and to get the fault current information. This is necessary to determine the specifications of micro AFG and PDs of micro DGs. Only  $I_{F(x)}(i,\ j),\ I_{D(x)}(i,\ j)$  and  $I_{FT(x)}(i,\ j)$  among the fault currents are directly utilized in the design procedure. Therefore, the effectiveness of the fault analysis method can be verified by comparing  $I_{F(x)}(i, j)$ ,  $I_{D(x)}(i, j)$  and  $I_{FT(x)}(i, j)$  obtained by applying the fault analysis method and EMTP-RV to the micro smart grid simulator model shown in Table 2.

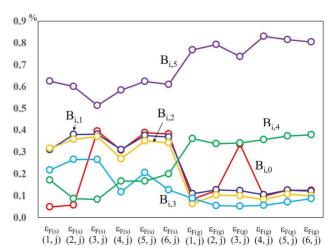

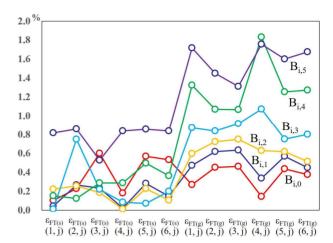

Fig. 7 shows the percent values  $\varepsilon$  of the differences between the fault current values obtained by the fault analysis method and the fault current values obtained by EMTP-RV simulation in the cases of a three phase short fault and a single phase ground fault at fault location Bii on the micro SG simulator model. In Fig. 7,  $\varepsilon_{F(s)}(i, j)$  and  $\varepsilon_{F(g)}(i, j)$  indicate the  $\varepsilon$  values obtained from the three phase short fault and the single phase ground fault for the line bus B<sub>i,i</sub>, respectively. The EMTP-RV simulation results are already given in Table 3. The ε value is represented in Eq. (15). In Eq. (15),  $I_{EMTP}$  and  $I_{FAM}$ represent the fault current value obtained by the EMTP-RV simulation, and the fault current value obtained by the fault analysis method, respectively.

**Fig. 7.** The  $\varepsilon_{F(x)}(i, j)$  values obtained from the fault analysis method and EMTP-RV simulation

**Fig. 8.** The  $\varepsilon_{D(x)}(i,j)$  values obtained from the fault analysis method and the EMTP-RV simulation

$$\varepsilon = \frac{I_{EMTP} - I_{FAM}}{I_{EMTP}} \times 100 \tag{15}$$

The most important point in the micro SG simulator design process is to determine the MBC of the PDs that plays the most crucial role in downsizing the micro SG simulator. That is, the accuracy of the  $I_{F(x)}(i, j)$  among the fault currents is very important. From Table 6, it is proved that the  $I_{F(x)}(i, j)$  values by the fault analysis method can be accurately calculated since  $\epsilon$  values are all within 1%.

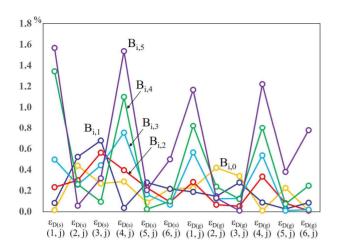

Fig. 8 shows the percent values  $\epsilon$  of the differences between the  $I_{D(x)}(i,j)$  obtained by the fault analysis method and the fault current obtained by EMTP-RV simulation, in cases of a three phase short fault, and a single phase ground fault at fault location  $B_{i,j}$ , on the micro SG simulator model.

In Fig. 8,  $\epsilon_{D(s)}(i, j)$  and  $\epsilon_{D(g)}(i, j)$  indicate the  $\epsilon$  values between  $I_{D(s)}(i, j)$  for the three phase short fault, and between  $I_{D(g)}(i, j)$  the single phase ground fault on the fault location  $B_{i,j}$ , respectively. The EMTP-RV simulation results are already presented in Table 4. When the DG is located near the CB and a fault occurs at the end of the line (bus  $B_{i,5}$ ),  $\epsilon$  for the  $I_{D(x)}(i,j)$  increases but it remains within 1.6% and the  $\delta$  value of  $I_{Dopc}$  of DGs is 2, which has no effect on the design results. This proves that the proposed fault analysis method is very effective for the fault analysis of the micro smart grid simulator model.

Fig. 9 shows the % values  $\epsilon$  of the differences between the  $I_{FT(x)}(i,j)$  obtained by the fault analysis method and the  $I_{FT(x)}(i,j)$  obtained by EMTP-RV simulation in the case of a three phase short fault, and in the case of a single phase ground fault of fault location  $B_{i,j}$  on the micro SG simulator. In Fig. 9,  $\epsilon_{FT(s)}(i,j)$  and  $\epsilon_{FT(g)}(i,j)$  indicate the  $\epsilon$  values between  $I_{FT(x)}(i,j)$  for the three phase short fault, and for the single phase ground fault on the ith micro DL, respectively. The EMTP-RV simulation results are already

**Fig. 9.** The  $\varepsilon_{FT(x)}(i, j)$  values obtained from the fault analysis method and EMTP-RV simulation

presented in Table 5. It can be seen that, as in the first micro DL  $F_1$  and the fourth micro DL  $F_4$ , when the DG is on the starting location of the line and the fault occurs at the end of the DL, the error  $\varepsilon$  can be slightly higher compared to other cases. This is because the  $I_{FT(x)}(i, j)$  obtained from EMTP-RV can be smaller than that calculated by the fault analysis method due to currents flowing into the load from the  $I_{F(x)}(i, j)$ .

However, fault current values calculated from the fault analysis method are greater than those of EMTP-RV for all fault cases and the  $\epsilon$  values are less than 1.8%, which has no effect on the design result of the  $I_{AFG}$  of micro AFG.

#### 5. Conclusions

In this study, a methodology was proposed to reduce the electrical level and space size of the smart grid to a predetermined scale, and based on the design methodology a miniaturized micro SG simulator that can safely and freely observe the electrical phenomena was designed. This new design can aid to test control strategies for disturbances on the smart grid under safe electrical levels with minimum economic and spatial costs. The micro SG simulator has the same configuration as the actual smart grid except that a substation transformer has the wiring of  $\Delta$ -Y<sub>g</sub> instead the wiring of Y<sub>g</sub>-Y<sub>g</sub>- $\Delta$  and has a substation transformer capacity of 190VA, voltage level of 19V, area of 4m<sup>2</sup> and I<sub>Pmbc</sub> of 20A, which are obtained by downscaling the substation transformer capacity of 45MVA, voltage level of 23kV and area of several km<sup>2</sup>. Thus it was possible to downsize the smart grid to over one thousandth and also reduced the 12kA MBC of the smart grid to 1/600 based on the design methodology proposed in this paper. Through the EMTP-RV simulation verification process, the effectiveness of the proposed design methodology and the micro SG simulator developed using the proposed design methodology was verified by showing that the all fault currents were within I<sub>Pmbc</sub> (20A) of the micro PD, I<sub>Dmbc</sub> (5A) of the micro DG and I<sub>AFG</sub> (30A) of the micro AFG, and by identifying error between the fault analysis results and EMTP-RV simulation results were within the maximum 1.8% for all fault cases on the micro SG simulator.

As mentioned above, the purpose of this paper is to design the specifications of the micro smart grid simulator. Therefore, additional research on designing and manufacturing micro power facilities such as a micro ST, micro PDs, micro DLs and micro DGs will continue based on the design specifications obtained in this paper.

#### Acknowledgments

This work was supported by the National Research Foundation of Korea Grant funded by the Korean Government (NRF-2016R1D1A1B01013749).

#### Nomenclature

| Variable         | Definition                                                                                     |

|------------------|------------------------------------------------------------------------------------------------|

| $Z_{\rm T}$      | The % impedance of substation transformer T                                                    |

| $F_{i}$          | The ith distribution line of smart grid                                                        |

| $CB_i$           | Circuit breaker of distribution line F <sub>i</sub>                                            |

| $B_{i,j}$        | The ith line bus of distribution line F <sub>i</sub>                                           |

| $Z_{i,j}$        | The % impedance of the jth line section of F <sub>i</sub>                                      |

| $D_{i}$          | The ith distributed generation, which is                                                       |

|                  | connected to F <sub>i</sub>                                                                    |

| $Z_{Di}$         | The % impedance of D <sub>i</sub>                                                              |

| (x)              | (s): three phase short circuit fault or                                                        |

|                  | (g) : single phase ground fault                                                                |

| f                | Fault location on the faulty distribution line                                                 |

| $I_T$            | Fault current flowing from T to f                                                              |

| $I_{Di}$         | Fault current flowing from $D_i$ to $f$                                                        |

| $I_{F(x)}(i,j)$  | Fault current flowing from CB <sub>i</sub> to f when any                                       |

|                  | fault with fault type x occurs at the jth line                                                 |

| T (::)           | section of F <sub>i</sub>                                                                      |

| $I_{D(x)}(1, J)$ | Fault current flowing from D <sub>i</sub> to f when any fault                                  |

|                  | with fault type x occurs at the jth line section of                                            |

| I (::)           | F <sub>i</sub>                                                                                 |

| $I_{FT(x)}(1,J)$ | Total fault current when any fault with fault type $x$ occurs at the jth line section of $F_i$ |

| $Z_{TSB}$        | The % impedance of power grid viewed from the                                                  |

| ZISB             | secondary bus of T                                                                             |

| $r_i$            | The number of line sections from D <sub>i</sub> to the                                         |

| J                | secondary bus of T                                                                             |

| $Z_{pi}$         | Path % impedance from D <sub>i</sub> to secondary bus of T                                     |

|                  | $Z_{Pi} = \sum_{j=1}^{r_i} Z_{i,j} + Z_{Di}$                                                   |

| $Z_{Fx}$                  | The % line impedance from the secondary bus of   |

|---------------------------|--------------------------------------------------|

|                           | T to f on the faulty distribution line           |

| $Z_{Fy}$                  | The % line impedance from $f$ to DG connected to |

| ,                         | the faulty distribution line                     |

| $Z_{\alpha}$              | The % line impedance from the secondary bus of   |

|                           | T to the position of $D_k$                       |

| x                         | The % impedance of fault current limiter         |

| $Z_{\chi}$                | $Z_{\alpha}$ minus $Z_{Fx}$ .                    |

| $Z_{\mathrm{UV}}^{}$      | Total % impedance considering the power grid,    |

|                           | and all distributed generations except Dk viewed |

|                           | at the secondary bus of T                        |

| $Z_{\mathrm{UW}}$         | Total % fault impedance                          |

| $I_s$                     | Three phase short circuit fault current          |

| $I_g$                     | Single phase ground fault current                |

| $\dot{V}_{MVD}$           | Maximum allowable voltage drop                   |

| $I_{FR}$                  | Rated current of distribution line               |

| $I_{EC}$                  | Maximum allowable current of distribution line   |

| $\mathbf{P}_{\mathrm{L}}$ | Line section load                                |

| $P_{M}$                   | Substation transformer capacity                  |

| $Z_{LS1}$                 | The % positive sequence impedance of line        |

|                           | section                                          |

$I_{Pmbc} \\$ Minimum operating current of protective device  $I_{Pmoc}$

breaking current of distributed Maximum  $I_{Dmbc}$ generation

Maximum breaking current of protective device

$I_{D\text{moc}}$ Minimum operating current of distributed generation

Maximum allowable current of artificial fault  $I_{AFG}$ generator

Safety factor that protective devices have λ sufficient fault current blocking capability

Safety factor that is introduced in order for the δ protective devices to work clearly.

$\varepsilon_{F(x)}(i,j)$  Error rate ( $\varepsilon$ ) value between  $I_{F(x)}(i,j)$ s obtained from fault analysis and EMTP-RV simulation when a fault with fault type x occurs on the line

$\varepsilon_{D(x)}(i, j)$  Error rate ( $\varepsilon$ ) value between  $I_{D(x)}(i, j)$ s obtained from fault analysis and EMTP-RV simulation when a fault with fault type x occurs on the line bus B<sub>i,j</sub>.

$\varepsilon_{FT(x)}(i,j)$  Error rate ( $\varepsilon$ ) value between  $I_{FT(x)}(i,j)$ s obtained from fault analysis and EMTP-RV simulation when a fault with fault type x occurs on the line bus B<sub>i,j</sub>.

## References

- [1] C.-C. Liu, S.-J. Lee, S. S. Venkata, "An expert system operation aid for restoration and loss reduction of distribution systems," IEEE Trans. Power Delivery, vol. 3, no. 2, pp 619-626, May 1988.

- [2] J. Liu, H. Cheng, X. Shi and J. Xu, "A Tabu search algorithm for fast restoration of large area breakdown

- in distribution systems," Energy and Power Engineering, vol. 2, no. 1, pp. 1-5, Feb. 2010.

- T. Taylor and D. Lubkeman, "Implementation of [3] heuristic search strategies for distribution feeder reconfiguration," IEEE Trans. Power Delivery, vol. 5, no. 2, pp 239-246, Apr. 1990.

- J. C. Wang, H. D. Chiang and G. R. Daring, "An efficient algorithm for real time network reconfigureation in large scale unbalanced distribution systems," IEEE Trans. Power Systems, vol. 11, no 1., pp. 511-517, Feb. 1996.

- Y.-S. Ko, "A self-isolation method for the HIF zone under the network-based distribution system." IEEE Trans. Power Delivery, vol. 24, no. 2, pp. 884-891, Apr. 2009.

- IEC, "Communication networks and systems in [6] Substations," IEC, Geneva, Switzerland, IEC 61850 First edition, 2003.

- R. Belkacemi, A. Babalola, F. Ariyo and A. Feliachi, [7] "Restoration of smart grid distribution system using two-way communication capability," 2013 North American Power Symposium, Manhattan, KS, USA, Sep. 2013.

- C.-H. Shin, G.-G. Yun, S.-S. Jo, W.-O. Jeong, D.-Y. Shin, et. al., "A study on the actual examination of bidirectional protection for interconnecting distributed resources with distribution system," Korea Electric Power Research Institute, Daejeon, South Korea, Tech. Rep. TR-H02. S2009.0998, Feb. 2009.

- Y.-S. Ko, T.-K. Kang, H.-Y. Park, H.-Y. Kim and H.-S. Nam, "FRTU-based fault zone isolation method in the distribution systems," IEEE Trans. Power Delivery, vol. 25, no. 2, pp. 1001-1009, Apr. 2010.

- [10] A. N. Milioudis, G. T. Andreou and D. P. Labridis, "Enhanced protection scheme for smart grids using power line communications techniques — Part II: location of high impedance fault Position," IEEE Trans. Smart Grid, vol. 3, no. 4, pp.1621-1630, 2012.

- [11] Y.-S. Ko, "A study on the agent (protective device)based fault determination and separation methodology for smart grid distribution system," J. Electr. Eng. Technol., vol. 10, no. 1, pp. 102-108, Jan. 2015.

- [12] T. Galchev, H. Kim and K. Najafi, "Micro power generator for harvesting low-frequency and nonperiodic vibrations," Journal of Microelectromechanical Systems, vol. 20, no. 4, pp. 852-866, Aug. 2011.

- [13] M. A. Burns, B. N. Johnson, S. N. Brahmasa ndra, K. Handique, J. R. Webster, et. al., "An Integrated Nanoliter DNA Analysis Device," Science, vol. 282, no. 5388, pp. 484-487, Oct.1998.

- [14] C. Lee and J. A. Yeh, "Development and evolution of MOEMS technology in variable optical attenuators," Journal of Micro/Nano Lithography, MEMS, and MOMES, vol. 7, no. 2, 021003, Apr. 2008.

- [15] K. Hongesombut, Y. Mitani, and K. Tsuji, "Optimal location assignment and design of superconducting fault current limiters applied to loop power system,' IEEE Trans. Applied Superconductivity, vol. 13, no. 2, pp. 1828-1831, Jun. 2003.

- [16] T. Sato, M. Yamaguchi, T. Terashimam S. Fukui, J. Ogawa and H.Shimizu, "Study on the effect of fault current limiter in power system with dispersed generators," IEEE Trans. Applied Superconductivity, vol. 17, no. 2, pp. 2331-2334, Jun. 2007.

- [17] Y. Zhang and R. A. Dougal," Novel dual-FCL connection for adding distributed generation to a power distribution utility." IEEE Trans. Applied Superconductivity, vol. 21, no, 3, pp. 2179-2183, Jun.

- [18] S. Marx and D. Bender, "An Introduction to symmetrical components, system modelling and fault calculation," in 30th Annual Hands-On Relay School, Washington State University, Washington, USA, Mar.

- [19] R. E. Fehr, III, "A novel approach for understanding symmetrical Components and Sequence networks of three-phase power systems," IEEE PES, New York, USA, TE-2006-000213, 2006.

- [20] KEPCO Academy, "Distribution system practice I, II, and III," Naju, Jeollanam-do, South Korea: KEPCO, 2002.

- [21] W.-W. Jung, H.-J. Lee, S.-C. Kwon and W.-K. Chae, "Application of directional over current protection schemes considering the fault characteristics in the distribution system with dispersed generation," J. of the Korean Institute of Illuminating and Electrical Installation Engineers, vol. 24, no. 9, pp. 97-107, Sep. 2010.

- [22] J.-H. Cha, K.-W. Park, H.-S. Ahn, K.-M. Kwon, J.-H. Oh, P. Mahirane and J.-E. Kim, "Overvoltage protection controller design of distributed generation," J. Electr. Eng. Technol., vol. 13, no. 2, pp. 599-607, Mar. 2018.

- [23] J.-H. Mun, H.-G. Kim and I.-L. Rho, "The technical standard of grid-connected distributed generation," Korea Electric Power Company, Naju, Jeollanamdo, South Korea, KEPCO-H0-Distribution-Standard-0015, Apr. 2017.

- [24] B.-T. Lee, C.-H. Kim, D.-S. Rho, Y.-P. Wang, Y.-G. Jang and S.-S. Seo, "Analysis of bi-directional protection problem for new energy power sources in distribution systems," in Proc. KIEE, 2009, pp. 515-516.

- [25] IEC, "Grid integration of large-capacity renewable energy sources and use of large-capacity electrical energy storage," White Paper IEC-WP RE-EES: 2012-10, Geneva, Switzerland, 2012.

- [26] J. Mahseredjian and C. Dewhurst, "EMTP-RV user manual ver. 3.0," Powersys, France, 2010.

Yun-Seok Ko He received his B.S., M.S., and Ph.D. degrees in Electrical Engineering from Kwangwoon University, Seoul, Korea in 1984, 1986, and 1996, respectively. He worked at KERI (Korea Electric Research Institute) from 1986 to 1996, and then POSRI (POSCO Research Institute) from 1996

to 1997. He also was a visiting professor at University of Utah from 2012 to 2013. Currently, he is a Professor at the Department of Electronic Engineering, Nam Seoul University, Korea. His research interests are distribution automation, substation automation, expert system application to power systems, Smart Grid and IED (Intelligent Electronic Devices).