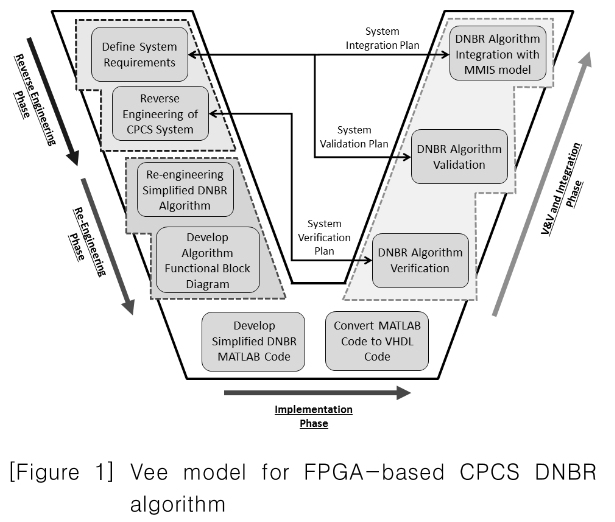

[Figure 1] Vee model for FPGA-based CPCS DNBR algorithm

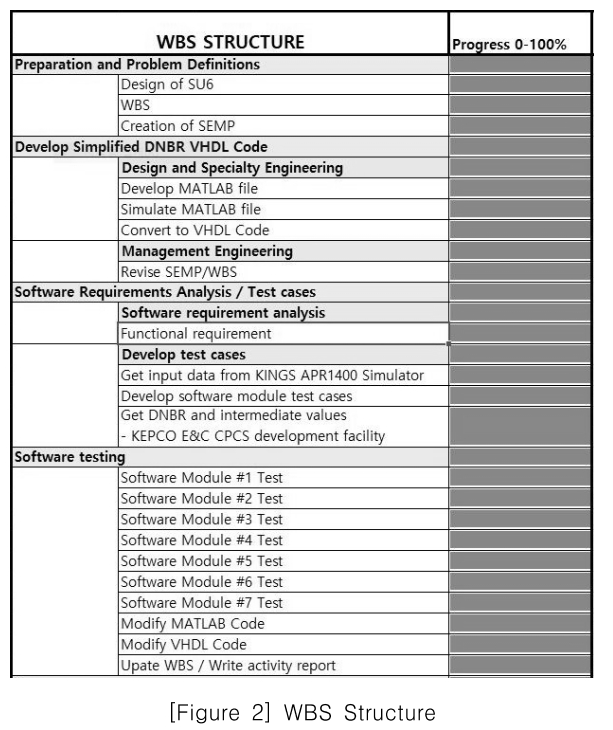

[Figure 2] WBS Structure

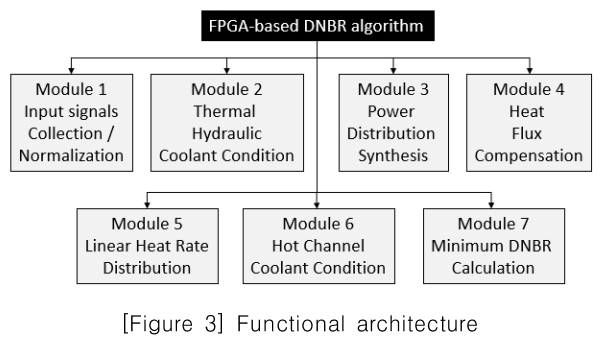

[Figure 3] Functional architecture

[Figure 4] EFFBD of Module 4

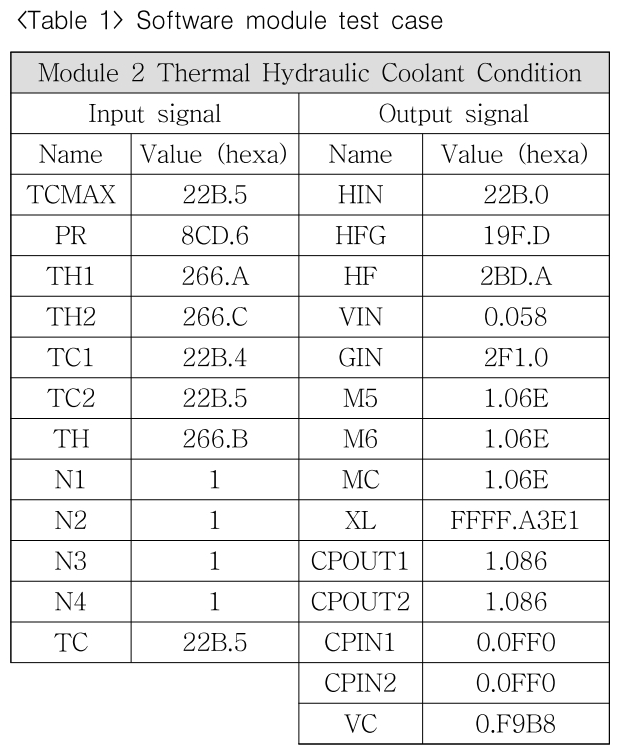

Software module test case

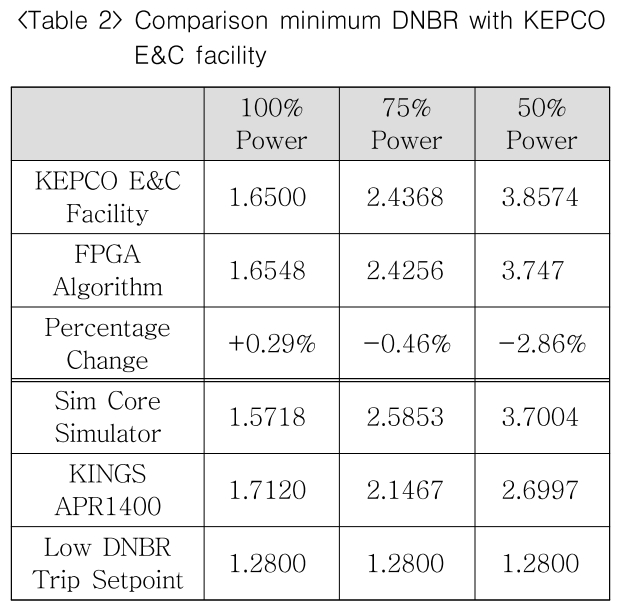

Comparison minimum DNBR with KEPCO E&C facility

References

-

NPP Systems - Core Protection Calculator System, Text Book for BNPP NPP, Revision 2, p.1

-

IAEA Nuclear Energy Series NP-T-3.17 Application of Field Programmable Gate Arrays in Instrumentation and Control Systems of Nuclear Power Plants, p.3-43

-

Systems Engineering Principles and Practice, Alexander Kossiakoff, Second edition, p36-37, 355-407

-

INCOSE Systems Engineering Handbook Fourth edition, p106-108

-

Elliot J. Chikofsky, James H. Cross II, Reverse Engineering and Design Recovery: A Taxonomy, IEEE, January 1990, p.15-16

-

KEPCO & KHNP, Functional Design Requirements for a Core Protection Calculator System for APR1400, Revision 0, 2014

-

Vitech corporation homepage, http://www.vitechcorp.com/resources/core/onlinehelp/desktop/Views/Enhanced_Function_Flow_Block_Diagram_(EFBD)

-

IEEE 1012, IEEE standard for system and software verification and validation, 2012

-

Donghwi Jeon, Jaecheon Jung, Design architecture of simplified core protection calculator system algorithm, Nuclear Engineering and Design, 2017

-

Restu Maerani, Software verification process and methodology for the development of FPGA-based engineered safety features system, Nuclear Engineering and Design, 2017

-

IAEA Nuclear Energy Series No. NP-T-1.5, Protecting against Common Cause Failures in Digital I&C Systems of Nuclear Power Plants

-

Peter L. Hung, Core Protection Calculator System: Past, Present, and Future, ICONE18-29001

-

Hyen-Jeong Kim, Field Programmable Gate Array-based I&C Safety System, ISOFIC/ISSNP 2014

-

IEC 62566, Nuclear power plants - Instrumentation and control important to safety - Development of HDL-programmed integrated circuits for systems performing category A functions, 2012

-

NUREG/CR-7006, Review Guidelines for Field-Programmable gate Arrays in Nuclear Power Plant Safety Systems, 2009

-

본 웹사이트에 게시된 이메일 주소가 전자우편 수집 프로그램이나

그 밖의 기술적 장치를 이용하여 무단으로 수집되는 것을 거부하며,

이를 위반시 정보통신망법에 의해 형사 처벌됨을 유념하시기 바랍니다.

-

[게시일 2004년 10월 1일]

-

제 1 장 총칙

-

제 1 조 (목적)

이 이용약관은 KoreaScience 홈페이지(이하 “당 사이트”)에서 제공하는 인터넷 서비스(이하 '서비스')의 가입조건 및 이용에 관한 제반 사항과 기타 필요한 사항을 구체적으로 규정함을 목적으로 합니다.

-

제 2 조 (용어의 정의)

① "이용자"라 함은 당 사이트에 접속하여 이 약관에 따라 당 사이트가 제공하는 서비스를 받는 회원 및 비회원을

말합니다.

② "회원"이라 함은 서비스를 이용하기 위하여 당 사이트에 개인정보를 제공하여 아이디(ID)와 비밀번호를 부여

받은 자를 말합니다.

③ "회원 아이디(ID)"라 함은 회원의 식별 및 서비스 이용을 위하여 자신이 선정한 문자 및 숫자의 조합을

말합니다.

④ "비밀번호(패스워드)"라 함은 회원이 자신의 비밀보호를 위하여 선정한 문자 및 숫자의 조합을 말합니다.

-

제 3 조 (이용약관의 효력 및 변경)

① 이 약관은 당 사이트에 게시하거나 기타의 방법으로 회원에게 공지함으로써 효력이 발생합니다.

② 당 사이트는 이 약관을 개정할 경우에 적용일자 및 개정사유를 명시하여 현행 약관과 함께 당 사이트의

초기화면에 그 적용일자 7일 이전부터 적용일자 전일까지 공지합니다. 다만, 회원에게 불리하게 약관내용을

변경하는 경우에는 최소한 30일 이상의 사전 유예기간을 두고 공지합니다. 이 경우 당 사이트는 개정 전

내용과 개정 후 내용을 명확하게 비교하여 이용자가 알기 쉽도록 표시합니다.

-

제 4 조(약관 외 준칙)

① 이 약관은 당 사이트가 제공하는 서비스에 관한 이용안내와 함께 적용됩니다.

② 이 약관에 명시되지 아니한 사항은 관계법령의 규정이 적용됩니다.

-

제 2 장 이용계약의 체결

-

제 5 조 (이용계약의 성립 등)

① 이용계약은 이용고객이 당 사이트가 정한 약관에 「동의합니다」를 선택하고, 당 사이트가 정한

온라인신청양식을 작성하여 서비스 이용을 신청한 후, 당 사이트가 이를 승낙함으로써 성립합니다.

② 제1항의 승낙은 당 사이트가 제공하는 과학기술정보검색, 맞춤정보, 서지정보 등 다른 서비스의 이용승낙을

포함합니다.

-

제 6 조 (회원가입)

서비스를 이용하고자 하는 고객은 당 사이트에서 정한 회원가입양식에 개인정보를 기재하여 가입을 하여야 합니다.

-

제 7 조 (개인정보의 보호 및 사용)

당 사이트는 관계법령이 정하는 바에 따라 회원 등록정보를 포함한 회원의 개인정보를 보호하기 위해 노력합니다. 회원 개인정보의 보호 및 사용에 대해서는 관련법령 및 당 사이트의 개인정보 보호정책이 적용됩니다.

-

제 8 조 (이용 신청의 승낙과 제한)

① 당 사이트는 제6조의 규정에 의한 이용신청고객에 대하여 서비스 이용을 승낙합니다.

② 당 사이트는 아래사항에 해당하는 경우에 대해서 승낙하지 아니 합니다.

- 이용계약 신청서의 내용을 허위로 기재한 경우

- 기타 규정한 제반사항을 위반하며 신청하는 경우

-

제 9 조 (회원 ID 부여 및 변경 등)

① 당 사이트는 이용고객에 대하여 약관에 정하는 바에 따라 자신이 선정한 회원 ID를 부여합니다.

② 회원 ID는 원칙적으로 변경이 불가하며 부득이한 사유로 인하여 변경 하고자 하는 경우에는 해당 ID를

해지하고 재가입해야 합니다.

③ 기타 회원 개인정보 관리 및 변경 등에 관한 사항은 서비스별 안내에 정하는 바에 의합니다.

-

제 3 장 계약 당사자의 의무

-

제 10 조 (KISTI의 의무)

① 당 사이트는 이용고객이 희망한 서비스 제공 개시일에 특별한 사정이 없는 한 서비스를 이용할 수 있도록

하여야 합니다.

② 당 사이트는 개인정보 보호를 위해 보안시스템을 구축하며 개인정보 보호정책을 공시하고 준수합니다.

③ 당 사이트는 회원으로부터 제기되는 의견이나 불만이 정당하다고 객관적으로 인정될 경우에는 적절한 절차를

거쳐 즉시 처리하여야 합니다. 다만, 즉시 처리가 곤란한 경우는 회원에게 그 사유와 처리일정을 통보하여야

합니다.

-

제 11 조 (회원의 의무)

① 이용자는 회원가입 신청 또는 회원정보 변경 시 실명으로 모든 사항을 사실에 근거하여 작성하여야 하며,

허위 또는 타인의 정보를 등록할 경우 일체의 권리를 주장할 수 없습니다.

② 당 사이트가 관계법령 및 개인정보 보호정책에 의거하여 그 책임을 지는 경우를 제외하고 회원에게 부여된

ID의 비밀번호 관리소홀, 부정사용에 의하여 발생하는 모든 결과에 대한 책임은 회원에게 있습니다.

③ 회원은 당 사이트 및 제 3자의 지적 재산권을 침해해서는 안 됩니다.

-

제 4 장 서비스의 이용

-

제 12 조 (서비스 이용 시간)

① 서비스 이용은 당 사이트의 업무상 또는 기술상 특별한 지장이 없는 한 연중무휴, 1일 24시간 운영을

원칙으로 합니다. 단, 당 사이트는 시스템 정기점검, 증설 및 교체를 위해 당 사이트가 정한 날이나 시간에

서비스를 일시 중단할 수 있으며, 예정되어 있는 작업으로 인한 서비스 일시중단은 당 사이트 홈페이지를

통해 사전에 공지합니다.

② 당 사이트는 서비스를 특정범위로 분할하여 각 범위별로 이용가능시간을 별도로 지정할 수 있습니다. 다만

이 경우 그 내용을 공지합니다.

-

제 13 조 (홈페이지 저작권)

① NDSL에서 제공하는 모든 저작물의 저작권은 원저작자에게 있으며, KISTI는 복제/배포/전송권을 확보하고

있습니다.

② NDSL에서 제공하는 콘텐츠를 상업적 및 기타 영리목적으로 복제/배포/전송할 경우 사전에 KISTI의 허락을

받아야 합니다.

③ NDSL에서 제공하는 콘텐츠를 보도, 비평, 교육, 연구 등을 위하여 정당한 범위 안에서 공정한 관행에

합치되게 인용할 수 있습니다.

④ NDSL에서 제공하는 콘텐츠를 무단 복제, 전송, 배포 기타 저작권법에 위반되는 방법으로 이용할 경우

저작권법 제136조에 따라 5년 이하의 징역 또는 5천만 원 이하의 벌금에 처해질 수 있습니다.

-

제 14 조 (유료서비스)

① 당 사이트 및 협력기관이 정한 유료서비스(원문복사 등)는 별도로 정해진 바에 따르며, 변경사항은 시행 전에

당 사이트 홈페이지를 통하여 회원에게 공지합니다.

② 유료서비스를 이용하려는 회원은 정해진 요금체계에 따라 요금을 납부해야 합니다.

-

제 5 장 계약 해지 및 이용 제한

-

제 15 조 (계약 해지)

회원이 이용계약을 해지하고자 하는 때에는 [가입해지] 메뉴를 이용해 직접 해지해야 합니다.

-

제 16 조 (서비스 이용제한)

① 당 사이트는 회원이 서비스 이용내용에 있어서 본 약관 제 11조 내용을 위반하거나, 다음 각 호에 해당하는

경우 서비스 이용을 제한할 수 있습니다.

- 2년 이상 서비스를 이용한 적이 없는 경우

- 기타 정상적인 서비스 운영에 방해가 될 경우

② 상기 이용제한 규정에 따라 서비스를 이용하는 회원에게 서비스 이용에 대하여 별도 공지 없이 서비스 이용의

일시정지, 이용계약 해지 할 수 있습니다.

-

제 17 조 (전자우편주소 수집 금지)

회원은 전자우편주소 추출기 등을 이용하여 전자우편주소를 수집 또는 제3자에게 제공할 수 없습니다.

-

제 6 장 손해배상 및 기타사항

-

제 18 조 (손해배상)

당 사이트는 무료로 제공되는 서비스와 관련하여 회원에게 어떠한 손해가 발생하더라도 당 사이트가 고의 또는 과실로 인한 손해발생을 제외하고는 이에 대하여 책임을 부담하지 아니합니다.

-

제 19 조 (관할 법원)

서비스 이용으로 발생한 분쟁에 대해 소송이 제기되는 경우 민사 소송법상의 관할 법원에 제기합니다.

-

[부 칙]

1. (시행일) 이 약관은 2016년 9월 5일부터 적용되며, 종전 약관은 본 약관으로 대체되며, 개정된 약관의 적용일 이전 가입자도 개정된 약관의 적용을 받습니다.