# Journal of the Korea Institute of Information and Communication Engineering

한국정보통신학회논문지 Vol. 22, No. 2: 369~374, Feb. 2018

# HDB3 Codec의 로직구현

엄준<sup>1</sup> · 김영길<sup>2\*</sup>

# **Logic Implementation of HDB3 Codec**

## Joon Eom<sup>1</sup> · Young-Kil Kim<sup>2\*</sup>

<sup>1</sup>Hanwha Systems, Pangyo 13524, Korea

#### 요 약

Line Code는 데이터 전송을 위해 사용하는 Code로 송수신기 간 데이터의 손실을 방지하기 위해 사용되는 데이터의 부호방식이다. Line Code의 종류는 B3ZS, HDB3, B8ZS 등 다양한 방식이 있으며 우리나라 군 전술통신망에서는 HDB3 Code를 사용하고 있다.

본 논문에서는 군 전술통신망에서 사용되는 HDB3 Codec을 로직으로 구현하여 단종에 대한 위험요소를 제거하고, 개발기간의 단축과 신뢰성 보장이 가능하도록 한다. 또한 최소한의 로직을 사용하여 HDB3 Codec 구현함으로서 FPGA를 사용하여 개발이 가능함을 확인하고 시뮬레이션을 통해 구현된 HDB3 Codec과 상용의 HDB3 Codec IC의 비교를 통해 하여 성능을 입증한다.

#### **ABSTRACT**

The Line Code is a code used for data transmission and is a coding method used to prevent loss of data between transmitter and receiver. There are various kinds of line code such as B3ZS, HDB3, B8ZS, and HDB3 code is used in the tactical communication networks of Korea.

In this paper, we implement the HDB3 Codec that is used in tactical communication networks in order to eliminate the risk factors for component discontinuance and to shorten development period and ensure reliability. Also it is confirmed that it can be implement by minimizing the amount of logic usage so that it can be used unrestrictedly in systems using FPGA and the implemented HDB3 Codec is simulated to confirm that it is equivalent to the performance of HDB3 Codec IC.)

**키워드**: FPGA, HDB3, 라인코덱, 로직

Key word: FPGA, HDB3, Line Code, Logic

Received 4 August 2017, Revised 24 November 2017, Accepted 3 February 2018

\* Corresponding Author Young-Kil Kim(E-mail: ykkim@ajou.ac.kr, Tel:+82-31-219-2364) Division of Electrical and Computer Engineering, Ajou University, Suwon 16499, Korea

Open Access http://doi.org/10.6109/jkiice.2018.22.2.369

pISSN:2234-4772

©This is an Open Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License(http://creativecommons.org/li-censes/by-nc/3.0/) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

Copyright © The Korea Institute of Information and Communication Engineering.

<sup>&</sup>lt;sup>2\*</sup>Division of Electrical and Computer Engineering, Ajou University, Suwon 16499, Korea

#### Ⅰ. 서 론

Line Code는 전송선로 상에 디지털 데이터를 전송하기 위해 사용되는 방식으로 통신선로상의 신호의 진폭 손실을 방지하고, 수신기에서 수신되는 신호로부터 클 럭 복원을 통해 송신기와 수신기간의 신호의 동기를 유 지하여 데이터의 손실을 방지하기 위해 사용된다.

이를 위해 요구되는 Line Code의 특성은 DC 성분이 적고 신호로부터 타이밍 정보의 추출이 가능해야 하며, 전송로의 대역폭에 적합한 스펙트럼을 가져야 하는 특 성이 요구된다.[1]

대표적인 Line Code로는 B3ZS, B6ZS, B8ZS, CMI, HDB3 등 여러 종류가 있으며, ITU-T Recommendation G.703에 각 Line Code 방식에 대한 물리적/전기적 특성을 규정하고 있다.[2]

우리나라 군 전술통신망에서는 HDB3(High Density Bipolar 3 Code) Line Code 방식을 채택하여 사용하고 있으며, 이 방식은 송신기에서 송신할 데이터에 4개 이상의 연속적인 "0" 데이터가 발생하는 경우 마지막 데이터 비트에 Bipolar Violation을 발생시켜 채널을 통해 송신함으로서 신호를 수신하는 수신기에서 신호의 타이밍 복원을 가능하게 하는 방식이다.

이러한 기능을 처리하기 위해 군에서 운용되는 통신 장비는 상용의 HDB3 Codec IC를 사용하여 왔다. 그러 나 군 장비는 개발부터 전력화, 폐기 될 때까지 수명주 기가 10년 이상으로 장기간 운용되기 때문에 유지보수 가 중요한 관심사이다. 따라서 장비 개발 시 사용하는 상용부품의 Life Cycle에 대한 고려가 필요하다. 반면에 부품 단종을 예상하여 미리 부품을 구매하여 재고를 확 보하는 것은 재고관리 등 비용 손실을 초래한다.

HDB3 Codec 구현에 사용된 자원은 이전의 연구에서는 State machine을 사용하여 HDB3 Encoder를 구현하거나[3], Arithmetic Logic Unit(ALU), Adder, Multiplier, Shifter 및 Digital signal processor 등을 사용하여 HDB3 Decoder를 구현하였으며[4], 또는 HDB3 Encoder 구현시 Combinational logic 28개, Register 16개, HDB3 Decoder를 Combinational logic 31개, Register 15개를 사용하여 구현하였다.[5]

본 논문에서는 위에 언급한 문제의 해결방안으로 HDB3 Codec을 최소한의 자원을 사용하여 구현하였고 FPGA로 구현하여 상용의 HDB3 Codec IC의 대체가 가능함을 확인하였으며, 상용 HDB3 Codec IC와 성능과 비교하여 동등함을 입증하고 실 장비 개발에 적용가능성을 확인하였다.

### Ⅱ. 본 론

#### 2.1. HDB3 Codec 설계

HDB3 code는 Alternate Mark Inversion(AMI) code 를 기반으로 하는 방식으로 연속적인 4개의 '0' 데이터 가 전송될 때 마지막 bit에 Violation 신호를 삽입하여 전송하는 방식이다.

HDB3 Encoding 방식은 4개의 연속적인 '0' 데이터가 전송될 때 이전에 전송된 Pulse의 극성이 '-' 이고 마지막 치환 이후 Bipolar pulse의 개수가 짝수개일 경우 4개의 연속적인 '0' 데이터를 "+00+"로 치환하고, 홀수개일 경우 4개의 연속적인 '0' 데이터를 "000-"로 치환하며, 이전 전송된 Pulse의 극성이 '+' 이고 마지막으로 치환된 이후 Bipolar pulse의 개수가 짝수개일 경우 4개의 연속적인 '0' 데이터를 "-00-"로 치환하고, 홀수개일 경우 4개의 연속적인 '0' 데이터를 "000+"로 치환한다.

표 1 에 HDB3 Code의 치환규칙을 나타낸다.[6]

Table. 1 HDB3 Substitution Rules

| Polarity of<br>Preceding Pulse | Number of Bipolar Pulse(ones) Since Last Substitution |      |  |

|--------------------------------|-------------------------------------------------------|------|--|

|                                | Odd                                                   | Even |  |

| -                              | 000-                                                  | +00+ |  |

| +                              | 000+                                                  | -00- |  |

※ '+'는 양의 pulse, '-'는 음의 pulse

그림 1은 NRZ 데이터를 HDB3 Code로 변환하는 예로 첫 번째 연속적인 4개의 '0' 데이터는 HDB3 Code 치환규칙에 따라 "000-"로 치환되고 두 번째 연속적인 4개의 '0'데이터는 "+00+"로 치환되다.

Fig. 1 HDB3 Encoding Example(B :Bipolar V : Violation)

본 논문에서는 HDB3 Encoder와 HDB3 Decoder를 로직으로 구현하고 시뮬레이션을 통해 상용의 HDB3 Codec IC의 성능과 동일함을 검증하였으며, 로직 구현 에 사용된 FPGA의 로직 소요량을 분석하여 최소한의 자원으로 구현이 가능함을 확인하였다.

로직 구현 및 검증을 위한 도구는 Altera 社의 Quartus II Tool을 이용하였고, Cyclone EP1C3T100C6 Chip을 사용하였다. [7]

#### 2.2. HDB3 Encoder 설계

HDB3 Encoder는 NRZ 데이터의 송신을 위해 HDB3 Code로 변화한다.

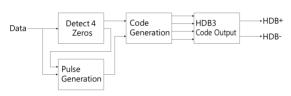

Fig. 2 HDB3 Encoder Structure

그림 2에서와 같이 HDB3 Encoder의 구조는 연속해서 입력되는 4개의 '0'의 데이터를 검출하기 위한 Detect 4 Zeros 블록과 입력 데이터와 Detect 4 Zeros블록의 출력을 조합하여 Bipolar 신호와 Violation 신호를 생성하는 Pulse Generation블록, 그리고 Detect 4 Zeros블록과 Pulse Generation 블록에서 출력되는 펄스를 조합하여 입력 데이터 '1'일 때 펄스, Bipolar 펄스 및 Violation 펄스를 발생하는 Code Generation 블록과 HDB+ 및 HDB- 의 Bipolar 신호를 출력하는 HDB3 Code Output 블록으로 구성된다.

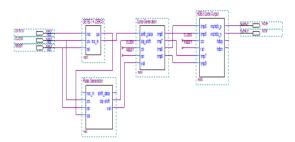

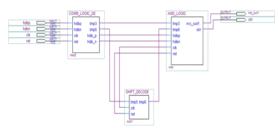

그림 3은 FPGA로 구현된 HDB3 Encoder로직으로 Detect 4 Zeros 로직은 4개의 연속된 '0' 데이터가 입력될 경우 하나의 펄스를 생성하여 출력하는 로직으로 연속된 4개의 '0' 데이터를 카운트 하기 위해 3개의 플립플롭과 조합논리회로로 구성되며, 4개의 마지막 '0' 데이터에서 하나의 펄스를 출력한다. Pulse Generation 로직은 Detect 4 Zeros 로직에서 출력된 펄스 신호를 이용하여 4 클럭 지연된 Bipolar 신호와 Violation 신호를생성한다. Code Generation 로직은 Pulse Generation 로직에서 출력된 신호를 이용하여 데이터 '1'에 대한 펄스와 Bipolar 펄스 및 Violation 펄스를 생성한다. 마지막으로

HDB3 Code Output 로직은 Code Generation 로직에서 출력되는 신호를 조합하여 HDB3 부호의 치환규칙에 따라 Violation 펄스와 Biolar 펄스의 극성을 결정하는 조합논리회로로 '+' 펄스와 '-' 펄스로 구분하여 신호를 출력한다.

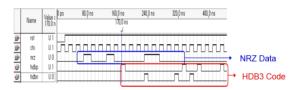

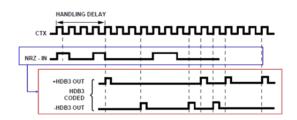

그림 4는 구현된 HDB3 Encoder에 NRZ 데이터 "10010000110000"가 입력될 때 HDB3 Code로 치환되어 출력되는 시뮬레이션 결과로 그림 1에서 HDB3 Code로 치환된 결과와 동일한 결과를 확인 할 수 있다.

Fig. 3 HDB3 Encoder Logic

Fig. 4 HDB3 Encoder Simulation Result

#### 2.3. HDB3 Decoder 설계

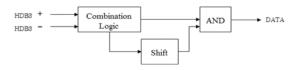

HDB3 Decoder는 HDB3 Code로 치환된 부호를 복호화 하여 원래의 NRZ 데이터로 변화하는 로직이다.

Fig. 5 HDB3 Decoder Structure

HDB3 Decoder는 Encoder보다 간단히 구현된다. 그 림 5 에서와 같이 입력되는 HDB3 Code는 Combination Logic블록과 Shift 블록에서 출력되는 신호를 AND 블록에서 조합하여 최종 NRZ 데이터로 Decoding 한다.

그림 6은 로직으로 구현된 HDB3 Decoder 블록으로, COMB LOGIC DE 로직에서 데이터 "1"에 해당하는 신호와 violation 신호를 구분하여 출력하고, Shift\_Decoder 로직에서 데이터 '1'에 해당하는 신호를 타이 밍 조절을 위해 3 Clock 지연시킨 후 출력한다. AND\_LOGIC 로직에서는 Shift된 신호와 COMB LOGIC DE 로직에서 출력되는 신호를 조합하여 최종 NRZ 데이터로 Decoding 한다.

그림 7은 입력되는 HDB3 Code가 NRZ 데이터로 복호화되어 출력되는 시뮬레이션 결과로 "+00-000+++00-"의 HDB3 Code가 입력될 경우 "1001000011 0000"의 NRZ 데이터가 출력되는 것을 알 수 있다. 이것은 그림 4의 HDB3 Encoder에서 Encoding되기 전의 NRZ 데이터와 동일하게 Decoding되는 것을 확인할 수 있다. [8]

Fig. 6 HDB3 Decoder Logic

Fig. 7 HDB3 Decoder Simulation Result

### 2.4. HDB3 Codec 실험

그림 8은 Quartus II Tool을 사용하여 HDB3 Encoder 출력을 HDB3 Decoder 입력으로 하여 수행한 시뮬레이 션 결과이다. NRZ 데이터 "10010000110000"이 HDB3 Encoder에 입력되어 HDB3 Code "+00-000-+-+00+"로 출력되고, 출력된 HDB3 Code를 HDB3 Decoder 입력 으로 하여 NRZ데이터로 복호화되어 HDB3 Encoder의 입력인 "10010000110000"이 출력되는 것을 알 수 있 다.

Fig. 8 HDB3 Codec Simulation Result

로직으로 구현된 HDB3 Encoder와 HDB3 Decoder를 시뮬레이션을 통해 이진 NRZ 데이터를 HDB3 Code로 Encoding한 후 치환된 HDB3 Code를 Decoding 했을 때 동일한 이진 NRZ 데이터로 복원됨을 확인하였다.

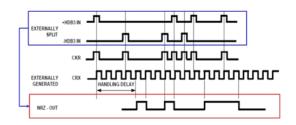

본 논문에서는 객관적인 성능검증을 위해 구현된 HDB3 Codec과 군 전술통신장비에 사용하고 있는 상용의 HDB3 Codec IC와 성능을 비교하였다.

그림 9와 그림 10은 Intersil 사의 HDB3 Codec IC의 Encoding 및 Decoding 타이밍도이다.[9] 그림 4의 시뮬레이션 결과와 비교하였을 때 Encoder 성능이 동등함을 알 수 있으며, 그림 7의 시뮬레이션 결과와 비교하였을 때 Decoder 성능이 동등함을 알 수 있다.

Fig. 9 HDB3 Encoder Timing Diagram of CD22103A

Fig. 10 HDB3 Dencoder Timing Diagram of CD22103A

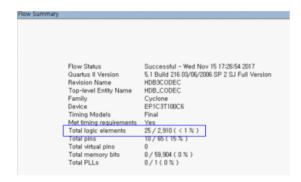

본 논문에서 구현된 HDB3 Codec은 표 2와 같이 2개의 Combinational logic, 11개의 Register 그리고 12개의 Combinational with register로 간단히 구현된다.

HDB3 Codec 구현에 사용된 로직량은 Altera社의 Cyclone EP1C3T100C6 FPGA Chip을 사용했을 때 그림 11 에서와 같이 정체 리소스 중 1% 이하의 로직으로

구현된다. 대부분의 장비는 FPGA를 사용하여 장비의 기능을 구현하고 있기 때문에 HDB3 Codec을 로직으로 구현하여 하나의 FPGA에 통합 한다면 별도의 부품을 사용하는 비용을 절감할 수 있으며, 부품의 단종위험에도 자유로워 질 수 있다.

Fig. 11 Total Logic element of HDB3 Codec

**Table. 2** HDB3 Code Logic Requirement (EP1C3T100C6(Altera社))

|                 | Logic Requirement |          |                              |  |

|-----------------|-------------------|----------|------------------------------|--|

| Item            | Combinationa 1    | Register | Combinationa l with register |  |

| HDB3<br>Encoder | 2                 | 7        | 9                            |  |

| HDB3<br>Decoder | 1                 | 4        | 3                            |  |

| HDB3<br>Codec   | 2                 | 11       | 12                           |  |

#### Ⅲ. 결 론

HDB3 Code는 군 전술통신망에서 디지털 데이터를 전송하기 위해 사용되는 Line Code이다. 이러한 HDB3 Codec을 로직으로 구현함으로써 상용품의 단종에 따른 장비의 운용공백을 최소화하고 상용의 HDB3 Codec IC를 하나의 FPGA에 통합하여 구현함으로써 유지보수 비용을 절감하여 정비성을 향상시킬 수 있다. 또한 장비 개발 시 부품의 수급에 따른 일정 단축이 가능하고 부품제거로 인한 비용절감 등의 이점이 있다.

현재 로직으로 구현된 HDB3 Codec은 군 전술통신 장비인 고속무선전송장비(HRT), 다중집선기세트(ERSC), MUX 등의 장비에 사용되고 있다. 본 논문에서는 HDB3 Codec을 FPGA를 이용하여 최소의 로직을 사용하여 구현하고, 시뮬레이션을 통해 상용 HDB3 Codec IC와 성능이 동등함을 검증하였다.

또한 Life Cycle이 10년 이상인 군용 장비에 적용함으로써 장비의 운용성 및 유지보수성 등의 향상이 가능함을 보였으며, 시뮬레이션을 통해 상용 HDB3 Codec IC와 성능이 동등함을 검증하였다.

신규로 개발되는 군 전술통신장비는 구현된 HDB3 Codec 로직을 사용하여 개발되고 있으며, 앞으로 장비 의 유지보수 측면에 많은 도움이 될 것으로 사료되다.

#### **REFERENCES**

- B. S. You, Analog and Digital Communication System, 1st ed. Seoul, Yang Seo Gak, Aug. 1999.

- [2] Recommendation G.703, Physical/electrical characteristics of hierarchical digital interfaces, ITU-T, Geneva, Apr. 2016.

- [3] S. Sathasivam, S. K. Rahamathulla, "Implementation of HDB3 Encoder Chip Design," *Indian Journal of Science and Technology*, vol. 9 no. 5, pp. 1-4, Feb. 2016, DOI; '10.17485/ijst/2016/v9i5/87170.

- [4] I. Ali, A. Ahmed , "An Efficient FPGA Based HDB3 Decoding system Using Direct Digital Synthesis," *Internationa of Future Computer and Communication*, vol.2, No. 6, pp. 576-580, Dec. 2013.

- [5] M. V. Bhimrao, T Ramesh, "ASIC Implementation of HDB3 Codec," *International Journal of Innovative Technology and Exploring Engineering(IJITEE)*, vol. 1, no. 3, pp. 779-779, Aug. 2012.

- [6] J. C. Bellamy, *Digital Telephony*, 3rd ed. New Jersey, NJ:A Wiley-Blackwell, Feb. 2000.

- [7] Altera Corporation, *Quick Start Guide for Quartus II Software*, San Jose, CA:ALTERA, 2007.

- [8] H. Y. Whang, Digital Logic and Computer Design, 5th ed, Seoul, Dong-Il Publication, Feb. 2016.

- [9] Intersil, CD22103A, File No. 1310.3, Milpitas, CA:Intersil, Jan. 1997.

# 엄준(Joon Eom)

1998, 금오공과대학교 전자제어공학과 학사 2018, 이주대 IT융합대학원 IT융합공학과 석사 1998, ~ 현재 한화시스템 수석연구원 ※ 관심분야: Embedded system, 정보통신

### 김영길(Young-kil Kim)

1978, 고려대학교 전자공학과 공학학사 1980, 한국과학기술원 산업전자공학과 공학석사 1984, ENST(프랑스) 공학박사 1984. ~ 현재 아주대학교 전자공학과 정교수 ※ 관심분야: 마이크로파 공학, 의료공학, embedded system