# 3-Level T-type Inverter Operation Method Using Level Change

# Tae-Hun Kim\* and Woo-Cheol Lee<sup>†</sup>

**Abstract** – In this study, a selective inverter operation between a 2-level voltage source converter (VSC) and a 3-level T-type VSC (3LT VSC) is proposed to improve the efficiency of a 3LT VSC. The 3LT VSC topology, except for its neutral-point switches, has similar operations as that of the 2-level VSC. If an operation mode is changed according to efficiency, the efficiency can be improved because efficiencies of each methods are depending on current and MI (Modulation Index). The proposed method calculates the power losses of the two topologies and operates as the having lower losses. To calculate the losses, the switching and conduction losses based on the operation mode of each topology were analyzed. The controller determined the operation mode of the 2- or 3-level VSC based on the power loss calculated during every cycle. The validity of the proposed control scheme was investigated through simulation and experiments. The waveform and average efficiency of each method were compared.

**Keywords**: T-type, inverter, 3-level, Loss, Efficiency

### 1. Introduction

A 2-level voltage source converter (VSC) is used for many systems because of its simple configuration and the ensured reliability [1]. However, the 2-level VSC has limit to improve the efficiency and performance. Recently, multilevel inverters are being researched to overcome the limitations of the 2-level VSC.

Multilevel inverters have several advantages as compared to 2-level VSC. Both reduce switching and harmonic losses and generate high quality output voltage because the switching voltage of the switch is half the DClink voltage [2, 3]. Multilevel inverters such as the neutralpoint-clamped (NPC), active NPC (ANPC) and H-bridge have advantages in terms of medium voltage [4-6]. However, these topologies have the disadvantage of high conduction losses because of their increased number of semiconductors. Thus, they are not ideal for low voltage applications. Therefore, a 3-level T-type VSC (3LT VSC) has been proposed to apply the conventional 3-level inverter to a low-voltage application [7]. The 3LT VSC has the advantage of low conduction losses as a result of a decrease in the number of switches and isolated gate drivers compared to conventional multilevel topologies such as NPC. The multi-level inverter has a disadvantage of increasing the number of devices, and various studies have been carried out to overcome this disadvantage. Studies to improve the efficiency of the T-type VSC include research on new devices, efficient PWM and operating methods, optimization designs, and so on [8-10].

Received: March 8, 2017; Accepted: September 26, 2017

Previous studies have shown that the 3LT VSC has low switching loss characteristics and achieves high efficiency compared to the 2-level VSC in low voltage conditions and when the switching frequency is higher than 10 kHz [10, 11].

The 3LT VSC has characteristics analogous to the conventional 2-level VSC. The 3LT VSC is composed of the same circuit as the 2-level VSC with an additional two neutral point switches. Therefore, the 3LT VSC can operate in the same manner as a 2-level VSC depending on the situation. The 3LT VSC efficiency depends on the amplitude modulation index (MI) if the switching frequency and DC-link voltage are the same. If the MI is small (i.e., close to zero), the efficiency of the 3LT VSC decreases as a result of the increase in conduction losses. Specifically, conduction losses depend on the turn-on ratio of the neutral point switches and on the MI. However, as previously mentioned, the 2-level VSC does not have neutral-point switches. Therefore, the 2-level VSC has higher efficiency than the 3LT VSC at a low MI. If the 3LT VSC operation mode is changed to that of a 2-level VSC at a low MI, the efficiency of the 3LT VSC will be the same as that of the 2-level VSC. By contrast, the 3LT VSC will have higher efficiency than that of the 2-level VSC at a high MI. If the average loss in a 60 Hz period is calculated and compared, the operation mode can be changed to another more efficient operation mode. Therefore, the system can achieve the efficiency of a 2-level or a 3LT VSC [12, 13].

In this study, a mode transition scheme for optimal efficiency is proposed. If operation mode is changed according to efficiency, the efficiency can be improved because efficiencies of each method are depending on current and MI. The proposed method calculates the power losses of the two topologies and operates as the having

<sup>†</sup> Corresponding Author: Dept. of Electrical, Electronic and Control Engineering, Hankyong National University, Korea. Institute for information technology convergence (woocheol@hknu.ac.kr)

Dept. of Electrical, Electronic and Control Engineering, Hankyong National University, Korea. (light411@naver.com)

lower losses. The controller performs a loss calculation and a comparison at each control period 10 and 15 kHz. If the loss calculation of the 3LT VSC result in a lower value than that of the 2-level VSC, the 3LT VSC operation is selected; otherwise, the 2-level VSC operation is selected. Therefore, in a 60 Hz period, the 3LT and 2-level VSC operation regions exist, and the average efficiency will be higher than that of the individual operation method. The proposed method is verified by means of a power sim (PSIM) simulation and experiments. The waveform and average efficiency of each method were compared.

# 2. Operation Characteristics and Power Loss

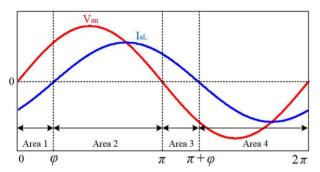

The switching and conduction losses can be derived from the DC-link voltage  $(V_{dc})$ , output voltage  $(V_{xn})$ , and inductor current  $(i_{xL})$ . The operation period is divided into four areas, as shown in Fig. 1. In each area, the operation modes and the switching and conduction losses are analyzed.

#### 2.1 2-level VSC

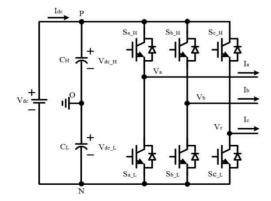

A 2-level VSC circuit is shown in Fig. 2 [14, 15]. In all areas, the switch  $S_{x H}$  operates as the complementary switch to the  $S_{x L}$  switch shown in Fig. 2. In areas 1 and 4, the switching loss in one switching cycle includes the turn-

Fig. 1. Operation areas based on phase angle of output voltage and inductor current in A-phase

Fig. 2. 3-phase 2-level VSC circuit

on loss  $(P_{xon2})$  and turn-off loss  $(P_{xoff2})$  of  $S_{x_{L}H}$ . A diode reverse-recovery loss  $(P_{xrr2})$  of  $S_{xL}$  also occurred. The switching losses can be expressed as:

$$P_{xon2} = \frac{V_{dc}}{V_{data}} A |i_{xL}| \tag{1}$$

$$P_{xoff 2} = \frac{V_{dc}}{V_{data}} B |i_{xL}| \tag{2}$$

$$P_{xrr2} = \frac{V_{dc}}{V_{data}} C |i_{xL}| \tag{3}$$

where the inductor instantaneous current  $i_{xL}$  is:

$$i_{xL} = I_{xL}\sin(\omega t + \varphi) \tag{4}$$

where  $V_{dc}$  is the DC-link voltage and  $V_{data}$  is the reference switching voltage in the datasheet. The switching voltage in the 2-level VSC is the same as  $V_{dc}$ . A and B are the constants obtained from the insulated gate bipolar mode transistor (IGBT) switching energy losses as functions of the collector current, and C is the constant obtained from the diode reverse-recovery energy losses as a function of the collector current in the datasheet. In addition,  $\varphi$  is the phase delay between the output voltage  $V_{xn}$  and inductor current  $i_{xL}$ .

The diode conduction loss  $(P_{xd})$  of the IGBT and the transistor conduction loss  $(P_{xtr})$  of the IGBT are expressed

$$P_{xtr} = (V_{c0} + R_s | i_{xL} |) |i_{xL}|$$

(5)

$$P_{xd} = (V_{d0} + R_d |i_{xL}|)|i_{xL}|$$

(6)

where  $V_{tr0}$  and  $V_{d0}$  are the on-state saturation voltage between the collector and emitter of the IGBT when the IGBT is turned on but when no current exists.  $R_{tr}$  and  $R_d$ are the on-state resistances, which are obtained from the  $I_c$ - $V_{ce}$  characteristics of the IGBT and antiparallel diode in the datasheet.

The conduction loss in one control period is changed depending on the duty ratio. In area 1, if  $S_{x H}$  is in the onstate, the current  $i_{xL}$  flows through the diode of  $S_{xH}$  and diode conduction loss occurred based on the turn-on ratio. Reverse- recovery energy loss occurred during switching times. The turn-on ratio of  $S_{x H}$  is the duty ratio expressed as:

$$D_2 = \frac{1}{2} + \frac{|V_{xn}\sin(\omega t)|}{2V_{dc}}$$

(7)

Therefore, the turn-on ratio varies depending on the output voltage. When conduction losses are calculated, the turn-on ratio of each switch must be considered. When  $S_{a\ H}$ is turned off and  $S_{aL}$  is in the on-state, the current  $i_{aL}$  will flow through the transistor of  $S_{a_{\underline{L}}L}$ . During switching time,

**Table 1.** 2-level VSC switching and conduction losses

| Area | Loss        | Switches                | Loss equation                                            |

|------|-------------|-------------------------|----------------------------------------------------------|

| 1    | $P_{xsw2}$  | $D_{a\_H}$ , $S_{a\_L}$ | $P_{xrr2} + P_{xon2} + P_{xoff2}$                        |

|      | $P_{xcon2}$ | $D_{a\_H}$ , $S_{a\_L}$ | $D_2 P_{xd} + (1-D_2) P_{xtr} + (d/2)(P_{xd} - P_{xtr})$ |

| 2    | $P_{xsw2}$  | $S_{a\_H}$ , $D_{a\_L}$ | $P_{xon2} + P_{xoff2} + P_{xrr2}$                        |

|      | $P_{xcon2}$ | $S_{a\_H}$ , $D_{a\_L}$ | $D_2 P_{xtr} + (1-D_2) P_{xd} + (d/2)(P_{xd} - P_{xtr})$ |

| 3    | $P_{xsw2}$  | $S_{a\_H}$ , $D_{a\_L}$ | $P_{xon2} + P_{xoff2} + P_{xrr2}$                        |

|      | $P_{xcon2}$ | $S_{a\_H}$ , $D_{a\_L}$ | $(1-D_2) P_{xtr} + D_2 P_{xd} + (d/2)(P_{xd} - P_{xtr})$ |

| 4    | $P_{xsw2}$  | $D_{a\_H}$ , $S_{a\_L}$ | $P_{xrr2} + P_{xon2} + P_{xoff2}$                        |

|      | $P_{xcon2}$ | $D_{a\_H}$ , $S_{a\_L}$ | $(1-D_2) P_{xd} + D_2 P_{xtr} + (d/2)(P_{xd} - P_{xtr})$ |

Fig. 3. 3LT VSC circuit

turn-on and turn-off losses  $(P_{xon2}, P_{xoff2})$  occurred in  $S_{x\_L}$ . The turn-on ratio of  $S_{aL}$  will be  $(I - D_2)$ .

The operating switches and loss equations for all areas are listed in Table 1.

In Table 1,  $P_{xxw2}$  denotes the switching loss and  $P_{xcon2}$ denotes the conduction loss of a 2-level VSC.  $P_{xxw2}$ employs the same equation for each area because the current flows through one IGBT transistor and one IGBT antiparallel diode. However,  $P_{xcon2}$  uses a different equation for each area because the conduction loss must consider the turn-on ratio. The 2-level VSC total loss is expressed as:

$$P_{x2} = P_{xsw2} + P_{xcon2} \tag{8}$$

# 2.2 3-level T-type VSC

The 3LT VSC is shown in Fig. 3.  $S_{x H}$  and  $S_{x N2}$ , as well as  $S_{x NI}$  and  $S_{x L}$ , perform complementary switching operations. In single cycle, the output voltage of the 3LT VSC ranges from zero to  $V_{dc}/2$  or from -  $V_{dc}/2$  to zero. Because of the decrease in the turn on/off voltage of the switch, the switching losses and harmonics are reduced. Therefore, the 3LT VSC IGBT turn-on and turn-off loss  $(P_{xon2}, P_{xoff2})$ , as well as the diode reverse recovery loss  $(P_{xrr3})$ , are expressed, respectively, as:

$$P_{xon3} = \frac{V_{dc}/2}{V_{data}} A |i_{xL}| \tag{9}$$

**Table 2.** 3LT VSC switching and conduction losses

| Area | Loss               | Switches                    | Loss equation                                        |

|------|--------------------|-----------------------------|------------------------------------------------------|

| 1    | $P_{xsw3}$         | $D_{x\_H}$ , $S_{x\_N2}$    | $P_{xrr3} + P_{xon3} + P_{xoff3}$                    |

|      | $P_{xcon3}$        | $D_{x\_H}$ , $D_{x\_NI}$ ,  | $D_3P_{xd} + (1 - D_3)P_{xd} + (1 - D_3)P_{xtr}$     |

|      |                    | $S_{x N2}$                  | $+ (d/2)(P_{xd} - P_{xtr})$                          |

|      | $P_{xsw3}$         | $S_{x\_H}$ , $D_{x\_N2}$    | $P_{xon3} + P_{xoff3} + P_{xrr3}$                    |

| 2    | P <sub>xcon3</sub> | $S_{x\_H}$ , $S_{x\_NI}$ ,  | $D_3 P_{xtr} + (1 - D_3) P_{xtr} + (1 - D_3) P_{xd}$ |

|      |                    | $D_{x\_N2}$                 | $+ (d/2)(P_{xd} - P_{xtr})$                          |

| 3    | $P_{xsw3}$         | $S_{x\_NI}, D_{x\_L}$       | $P_{xon3} + P_{xoff3} + P_{xrr3}$                    |

|      | $P_{xcon3}$        | $S_{x\_N1}$ , $D_{x\_N2}$ , | $(1 - D_3) P_{xtr} + (1 - D_3) P_{xd} + D_3 P_{xd}$  |

|      |                    | $D_{x\_L}$                  | $+ (d/2)(P_{xd} - P_{xtr})$                          |

| 4    | $P_{xsw3}$         | $D_{x\_NI}$ , $S_{x\_L}$    | $P_{xrr3} + P_{xon3} + P_{xoff3}$                    |

|      | P <sub>xcon3</sub> | $D_{x\_N1}$ , $S_{x\_N2}$ , | $(1 - D_3) P_{xd} + (1-D_3) P_{xtr} + D_3 P_{xtr}$   |

|      |                    | $S_{x\_L}$                  | $+ (d/2)(P_{xd}-P_{xtr})$                            |

$$P_{xoff3} = \frac{V_{dc}/2}{V_{data}} B |i_{xL}| \tag{10}$$

$$P_{xrr3} = \frac{V_{dc}/2}{V_{data}}C|i_{xL}| \tag{11}$$

where  $V_{dc}/2$  is the same as the switching voltage of the 3LT VSC.

When the current flows through the neutral point of the IGBT  $(S_{x NI}, S_{x N2})$ , the conduction losses will increase to twice that of the 2-level VSC because both transistor and diode conduction losses occur. Therefore, if the turn-on ratio of the  $S_{x\ NI}$  and  $S_{x\ N2}$  is sufficiently high, the 3LT VSC conduction loss will be higher than that of the 2-level VSC.

The 3LT VSC operation is divided based on the areas shown in Fig. 1. In areas 1 and 3,  $S_{a NI}$  is in the on-state and  $S_{a L}$  is in the off-state, and  $S_{a H}$  and  $S_{a N2}$  perform a complementary switching operation. In area 1 and in the  $S_{a,H}$  on-state, the current flows through the  $S_{a,H}$  diode and diode conduction loss occurred. In addition, at  $S_{a H}$ switching time, a diode reverse-recovery loss occurred. In the  $S_{a L}$  on-state, the current flows through the  $S_{a L}$ transistor. Thus, a transistor conduction loss occurred. During switching time,  $S_{x L}$  turn-on and turn-off loss occurred. The duty ratio is expressed as:

$$D_3 = \frac{|V_{xn}\sin(\omega t)|}{V_{dc}/2} \tag{12}$$

In the Area 1, 2, The  $D_3$  becomes the duty of  $D_{xH}$  and in other area The  $D_3$  becomes the duty of  $D_{xL}$  [16]. The operating switches and loss equations for all areas are listed in Table 2. As shown in Table 2, the 3LT VSC switching loss  $(P_{xsw3})$  employs the same equation for each area because the current flows through one IGBT transistor and one IGBT antiparallel diode. The 3LT VSC conduction loss  $(P_{xcon3})$  is the sum of three terms because two switches are present in the neutral point. Conduction losses are different based on the turn-on ratio of each switch. The 3LT VSC total loss is expressed as:

$$P_{x3} = P_{xsw3} + P_{xcon3} (13)$$

### 3. Proposed Method

A mode transition scheme between the 2-level and 3LT VSC is proposed for optimal efficiency. Loss calculation results of (8) and (12) are compared to determine whether an inverter immediately yields high efficiency. Parameters that influence loss calculation results are the duty ratio (DC-link voltage, output voltage) and the inductor current. The proposed method achieves high efficiency compared with the 2-level or 3LT VSC.

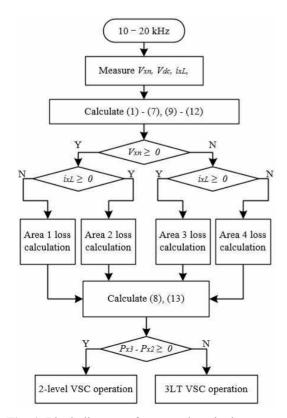

### 3.1 Proposed method sequence

Fig. 4 is a block diagram of the proposed method sequence. The sequence is performed during every cycle from 10 to 15 kHz. After the parameter values  $(V_{xn}, V_{dc})$ and  $i_{xL}$ ) are measured, the operation area is divided according to  $V_{xn}$  and  $i_{xL}$ . The switching and conduction losses ( $P_{xsw2}$ ,  $P_{xcon2}$ ,  $P_{xsw3}$ , and  $P_{xcon3}$ ) are calculated based on the loss equations given in Table 1 and Table 2. Then,  $P_{x2}$  and  $P_{x3}$  are compared. If the  $P_{x3}$  is less than  $P_{x2}$ , the 3LT VSC operation mode selected; otherwise, the 2-level VSC operation mode is selected.

#### 3.2 Simulation results

To verify the proposed method, a PSIM simulation was performed. The calculation and inverter operation were performed using a dynamic linking library (DLL) function.

Fig. 4. Block diagram of proposed method sequence

The thermal module of the PSIM was used to confirm the results of the calculation. The parameters used in the simulation and experiment are shown in Table 3.

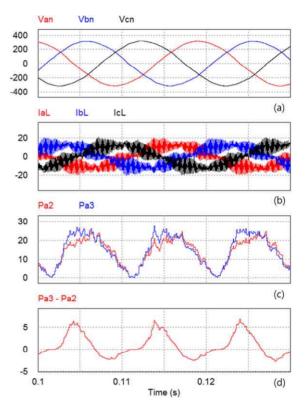

The PSIM simulation results are shown in Fig. 5.  $P_{x2}$  and  $P_{x3}$  are calculation results from (8) and (12). When  $(P_{x3} P_{x2}$ )  $\geq 0$ , the inverter operates as a 2-level VSC. When  $(P_{x3})$  $-P_{x2}$ ) < 0, the inverter operates as a 3LT VSC.

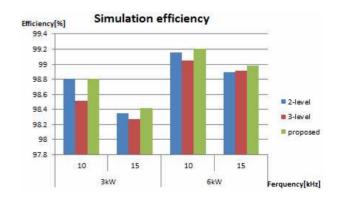

Fig. 6 shows the simulation results based on the conditions that DC-link voltage 700 V, output voltage 380 V, 6 kW resistor load. The proposed method achieved higher efficiency than did the individual operation methods.

**Fig. 5.** Simulation waveform ( $f_s = 10 \text{ kHz}$ ,  $R_{load} = 48 \Omega$ ): (a) output phase voltage  $V_{an}$ ,  $V_{bn}$ , and  $V_{cn}$ , (b) inductor current  $i_{aL}$ ,  $i_{bL}$ , and  $i_{cL}$ , (c) 2-level A-phase loss calculation  $P_{a2}$  and 3-level A-phase loss calculation  $P_{a3}$ , (d)  $P_{a3}$  -  $P_{a2}$

Fig. 6. Simulation efficiency with R load (3 kW, 6 kW)

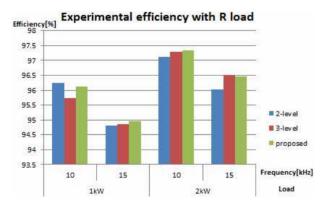

The efficiency increased approximately 0.3% with the 10 kHz frequency and 1 kW resistor load.

## 4. Experimental results

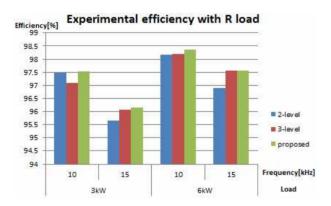

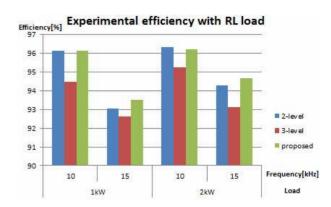

Experimental conditions were the same as those listed in Table 3. To verify the proposed method the experiment was performed on some other conditions. First, the DC-link voltage is 700 V, output voltage is 380 V and R load.

Second, the DC-link voltage is 500 V, output voltage is 220 V and R load. Third, the DC-link voltage is 500 V, output voltage is 220 V and RL load that PF is 0.8. The prototype 3LT VSC consisted of a Vincotech 70-W212NMA300SC-M208P IGBT (1200V, 300A). A digital signal processor TMS320F28335 was used to implement the proposed control method.

### 4.1 Waveform comparison

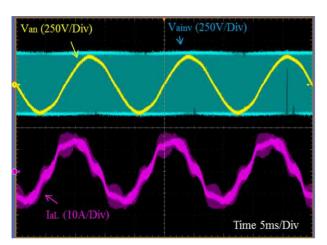

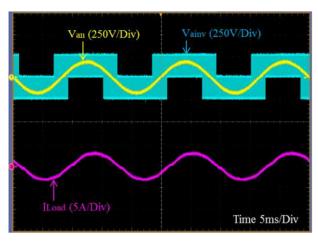

Figs. 7 to 9 show experimental results. The DC-link voltage is 700 V, output voltage is 380 V. The control period was 10 kHz and the resistor load was 3 kW. Fig. 7 shows the 2-level VSC waveform. The inverter voltage fluctuation was equal to the DC-link voltage. In 2-level operating mode, the ripple current of the inductor is larger than in other operating modes. Fig. 8 shows the 3LT VSC waveform. The inverter voltage fluctuation was equal to

Table 3. System parameter

| Parameter                          | Value        |

|------------------------------------|--------------|

| DC-link voltage (V <sub>dc</sub> ) | 700, 500 [V] |

| Output voltage $(V_{xl})$          | 380, 220 [V] |

| Switching frequency $(f_s)$        | 10, 15 [kHz] |

| Resistor load ( $R_{load}$ )       | 24, 48 [Ω]   |

| Inductor load $(L_{load})$         | 48, 77 [mH]  |

| Filter inductor $(L_f)$            | 1 [mH]       |

| Filter capacitor $(C_f)$           | 100 [μF]     |

Fig. 7. 2-level operation mode waveform: Ch1 output voltage,  $V_{an}$  (250 V/div), Ch2 inverter voltage,  $V_{ainv}$ (250 V/div), Ch3 inductor current,  $i_{aL}$  (10 A/div)

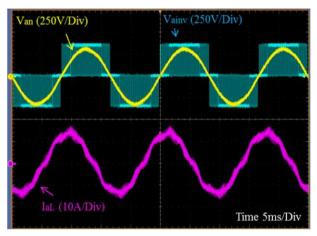

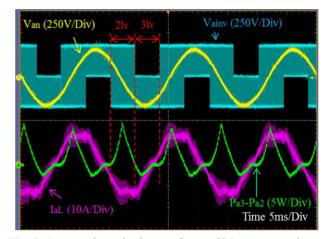

half the DC-link voltage. In addition, Fig. 8 shows that the 3LT VSC current fluctuation was lower than that of the 2-level VSC. Fig. 9 shows the proposed method's operation waveform. The area marked with 2lv is 2-level operating area and 3lv is 3-level operating area. The operation area can be noticed by the inverter voltage waveform. An additional waveform,  $P_{a3}$ - $P_{a2}$ , also exists. When  $(P_{a3}-P_{a2}) \ge 0$ , the inverter operated as a 2-level VSC. When  $(P_{a3}-P_{a2}) < 0$ , the inverter operated as a 3LT VSC. Therefore, the 2-level VSC operation was performed at phase angles of approximately "0" and " $\pi$ ". Fig. 10 shows the experimental waveforms on condition of DC-link voltage 500 V, output voltage 220 V with 1 kW RL load. In conditions of 1 kW and 2 kW, the PF is close to 0.8.

### 4.1 Efficiency comparison

A HIOKI PW6001 power analyzer with a basic power

Fig. 8. 3-level operation mode waveform: Ch1 output voltage, V<sub>an</sub> (250 V/div), Ch2 inverter voltage, V<sub>ainv</sub> (250 V/div), Ch3 inductor current,  $i_{aL}$  (10 A/div)

Fig. 9. Proposed method waveform: Ch1 output voltage,  $V_{an}$  (250 V/div), Ch2 inverter voltage,  $V_{ainv}$  (250 V/div), Ch3 inductor current, i<sub>aL</sub> (10 A/div), Ch4  $P_{a3} - P_{a2}$  value (5 W/div)

Fig. 10. Proposed method waveform with RL load: Ch1 output voltage,  $V_{an}$  (250 V/div), Ch2 inverter voltage,  $V_{ainv}$  (250 V/div), Ch3 load current,  $i_{Load}$ (10 A/div)

Fig. 11. Experiment efficiency with R load (3 kW, 6 kW)

Fig. 12. Experiment efficiency with R load (1 kW, 2 kW)

accuracy of 0.02 % was used to measure the efficiency. Fig. 11 shows the experimental results on the first conditions as mentioned before same with Figs.7-9. Fig. 12 shows the experimental results on the second conditions. Comparing the 2-level and 3-level operating mode in terms of efficiency, the 3-level operation mode is more effective than the 2-level as the capacity and frequency increase.

Fig. 13. Experiment efficiency with RL load (1 kW, 2 kW)

Because the switching losses are increased as the switching voltage and frequency are increase. Fig. 13 shows the experimental results on the conditions same with Fig. 10. It can be seen that the efficiency of each operation mode can be different depending on the phase on same condition. In Fig. 13, efficiency of 2-level is greater than 3-level.

The efficiency of proposed method is almost same or higher with an operation mode that has better efficiency. On condition of a 15 kHz frequency and a 2 kW RL load the efficiency was increased approximately 1.53 % than the 3-level, and 0.37 % than 2-level. On condition of a 15 kHz frequency and a 1 kW RL load the efficiency of proposed method was increased 0.91 % than 3-level and 0.46 % than 2-level. In these two cases the efficiency of 2, 3-level are worst but the increase rate of proposed method efficiency is best.

# 5. Conclusion

The 3LT VSC had the advantage of low switching loss because the switching voltage was the half the DC-link voltage. 3LT VSC has a disadvantage of large conduction loss due to two neutral switches. At a low output voltage, the 2-level mode is more advantageous in terms of efficiency than that of the 3-level mode. In this study, a mode transition scheme between a 2-level and a 3-level operation mode was proposed for optimal efficiency for 3LT VSC. In each control period, the proposed method performs calculation of losses and selects a better operation mode. The proposed mode transition scheme is more efficient when operating only in 3-level or 2-level under most conditions.

# Acknowledgements

"This research was supported by Basic Science Research Program through the National Research Foundation of Korea(NRF) funded by the Ministry of Education(No. NRF-2017R1D1A1B03031532)"

### References

- [1] P. Cortes, G. Ortiz, J. I. Yuz, J. Rodriguez, S. Vazquez, and L. G. Franquelo, "Model predictive control of an inverter with output lc filter for ups applications," Industrial Electronics, IEEE Transactions on, vol. 56, no. 6, pp. 1875-1883, 2009.

- [2] L. G. Franquelo et al., "The age of multilevel converters arrives," IEEE Ind. Electron. Mag., vol. 2, no. 2, pp. 28-39, Jun. 2008.

- J. Rodriguez, S. Bernet, B. Wu, J. O. Pontt, and S. Kouro, "Multilevel Voltage-source-converter Topologies for Industrial Medium-voltage Drives," IEEE Trans. Ind. Electron., vol. 54, no. 6, pp. 2930-2945, Dec.

- H. Abu-Rub, J. Holtz, J. Rodriguez, and G. Baoming, [4] "Medium voltage multilevel converters — State of the art, challenges and requirements in industrial applications," IEEE Trans. Ind. Electron, vol. 57, no. 8, pp. 2581-2596, Aug. 2010.

- [5] T. Bruckner, S. Bernet, and H. Guldner, "The active NPC converter and its loss-balancing control," IEEE Trans. Ind. Electron., vol. 52, no. 3, pp. 855-868, Jun. 2005.

- [6] F. Khoucha, M. S. Lagoun, A. Kheloui, and M. El Hachemi Benbouzid, "A comparison of symmetrical and asymmetrical three-phase H-bridge multilevel inverter for DTC induction motor drives," IEEE Trans. Energy Convers., vol. 26, no. 1, pp. 64-72, Mar. 2011.

- M. Schweizer and J. W. Kolar, "Design and implementation of a highly ef- ficient 3-level T-type converter for low-voltage applications," IEEE Trans. Power Electron., vol. 28, no. 2, pp. 889-907, Feb. 2013.

- Y. Kashihara and J. Itoh, "The performance of the multilevel converter topologies for PV inverter," in Proc. CIPS, Beijing, China, pp. 1-6, Mar. 2012,

- [9] K. Komatsu, "New IGBT modules for advanced neutral-point-clamped 3-level power converters" International Power Electronics Conference (IPEC), pp. 523-527, 2010.

- [10] S-M. Shin, J-H. Ahn, and B-K. Lee, "Maximum Efficiency Operation of Three-Level T-type Inverter for Low-Voltage and Low-Power Home Appliances," Journal of Electrical Engineering & Technology, vol. 10, no. 2, pp. 586-594, 2015.

- [11] J. W. Kolar, "High efficiency drive system with 3level T-type inverter," Proc. EPE Appl., pp. 1-10, Aug. 2011.

- [12] R. Teichmann and S. Bernet, "A comparison of threelevel converters versus two-level converters for lowvoltage drives, traction, and utility applications," IEEE Trans. Ind. Appl., vol. 41, pp. 855-865, May-June 2005.

- [13] Alemi, Payam, and Dong-Choon Lee. "A Generalized Loss Analysis Algorithm of Power Semiconductor

- Devices in Multilevel NPC Inverters," Journal of Electrical Engineering and Technology, vol.9, no.6, pp. 2168-2180, 2014.

- [14] K. Zhang, Y. Kang, J. Xiong, and J. Chen, "Direct repetitive control of SPWM inverters for UPS purpose," IEEE Trans. Power Electron., vol. 18, no. 3, pp. 784-792, May 2003.

- [15] Bai Baodong, Chen Dezhi, "Inverter IGBT Loss Analysis and Calculation," Industrial Technology (ICIT), 2013 IEEE International Conference on. *IEEE*, pp 563-569, 2013.

- [16] W. Srirattanawichaikul, S. Premrudeepreechacharn, Y. Kumsuwan, "Modified Unipolar Carrier-Based PWM Strategy for Three-level Neutral-Point-Clamped Voltage Source Inverters," Journal of Electrical Engineering & Technology, vol. 9, no. 2, pp. 489-500, March 2014.

Tae-Hun Kim He received the B.S. and M.S. degrees in electrical engineering from Hankyong National University, Ansung, Korea, in 2014, 2016, respecttively. He is currently a Ph.D course student in the School of Electrical, Electronic and Control Engineering at Hankyong National University. His

research interests are in the areas of power converter, PFC, inverter, and electrical drives.

Woo-Cheol Lee He received the B.S. and M.S. and Ph.D. degrees in electrical engineering from Hanyang University, Seoul, Korea, in 1987, 1989, 2001, respectively. From 1988 to 1998, he was with the R&D Institute, Hyosung Industries Company Ltd., as a Senior Researcher, Seoul, Korea. He

was a Visiting Professor in the department of Electrical Engineering at Virginia Polytechnic Institute and State University, Virginia, USA from 2007 to 2009. Since 2002, he has been with Hankyong National University, Ansung, Korea, where he is a Professor with the Department of Electrical, Electronic and Control Engineering. His research interests are in the areas of power converter, APF, UPS, and electrical drives.