ISSN: 1226-7244 (Print) ISSN: 2288-243X (Online) 논문번호 18-04-03

16

# 영상의 휘도 분포를 이용한 LDR 영상의 실시간 HDR 변환 하드웨어 구현 Real-Time LDR to HDR Conversion Hardware

이 승 민\*, 강 봉 순\* \*

Implementation using Luminance Distribution

Seung-min Lee\*, Bong-soon Kang\*

#### **Abstract**

Due to the development of display technologies for images, the resolution and quality of images are increasing day by day. In accordance with the development of the display technology, researches have been actively conducted on technologies for converting and displaying existing images to higher resolution and quality. Since the results of theses studies are included in the image signal processor, hardware implementation is indispensable. In this paper, we propose a real-time HDR(High Dynamic Range) conversion hardware implementation of LDR(Low Dynamic Range) image using luminance distribution. The proposed method extracts the features of the image using the histogram of the luminance distribution, and extends the luminance and color based on the extracted features. In addition, when the proposed method is designed by hardware IP(Intellectual Property) and its performance is verified, 4K DCI(Digital Cinema Image) can be handled at a rate of 30fps at 265.46MHz.

### 요 약

영상을 출력하는 디스플레이 기술의 발달로 인하여 영상의 해상도와 품질이 나날이 증가하고 있다. 이러한 디스플레이 기술의 발달에 맞추어, 기존의 영상들을 더 높은 해상도와 품질로 변환하여 디스플레이 할 수 있는 기술에 대한 연구가 활발하게 이루어지고 있다. 이러한 연구 결과는 이미지 신호 처리 장치에 포함되기 때문에 하드웨어 구현이 필수적으로 요구된다. 본 논문에서는, 영상의 휘도 분포를 이용한 LDR(Low Dynamic Range) 영상의 실시간 HDR(High Dynamic Range) 변환 하드웨어 구현을 제안한다. 제안하는 방법은 휘도 분포의 히스토그램을 이용하여 영상의 특징을 추출하고, 이를 바탕으로 하여 휘도와 색상을 확장한다. 또한, 제안한 알고리즘을 하드웨어 IP(Intellectual Property)로 설계하여 그 성능을 검증하였을 때, 최대 동작 주파수 265.46MHz로 4K DCI(Digital Cinema Image) 영상에 대하여 30fps로 동작하여 4K 표준에 대응할 수 있음을 확인하였다.

Key words: LDR, HDR, dynamic range conversion, hardware implementation, FPGA

Dept. of Electronic Engineering, Dong-A University

Corresponding author

E-mail: bongsoon@dua.ac.kr, Tel: +82-51-200-7703

Acknowledgment

This paper was supported by research funds from Dong-A University.

Manuscript received Dec. 7, 2018; revised Dec. 21, 2018; accepted Dec. 22, 2018

This is an Open-Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License (http://creativecommons.org/licenses/by-nc/3.0) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

# I . 서론

디스플레이 기술의 발달로 인하여 고화질, 고품질 의 영상들의 표현이 가능해지게 되었고, 이는 다양 한 영상 표준들이 등장하는 계기가 되었다[1]-[3]. 이러한 표준에 맞추어 영상의 해상도 및 품질 또한 기존보다 더 높은 해상도, 더 높은 색 표현 체계가 채택되고 실용화가 되고 있다[1]-[3]. 이에 맞추어 새로이 획득 되는 영상의 해상도나 품질은 새로운 표준에 맞추어 촬영되고 있으나, 기존에 촬영되어 있던 영상들은 이러한 표준에 대응하지 못하고 있다. 이러한 영상들을 위하여 다양한 방법의 LDR(Low Dynamic Range) 영상의 HDR(High Dynamic Range) 변환 알고리즘들이 활발하게 연구 되고 있다[4]-[13]. 이러한 기술을 동적 영역 변환이라고 하며, 동적 영 역 변환 기술은 디스플레이 장치에 포함되는 영상 신호 처리 장치(Image Signal Processor)에 필수적 으로 포함이 되어야 하는 기술이기 때문에 전용 하 드웨어의 구현이 필수적인 장치이다. 최근 4K 및 8K영상 표준이 실용화 되면서 동적 영역 확장 기 술 및 하드웨어 구현에 관한 연구들이 더욱 더 활 발하게 진행되고 있다[4]-[7].

본 과제에서는 영상 신호 처리 장치에 탑재하기 위한 동적 영역 변환 하드웨어를 제안한다. 제안하는 방법은 입력되는 영상의 휘도 분포를 이용하여 영상의 특징을 추출하고, 이를 바탕으로 하여 휘도 및 색상을 확장한다. 설계된 하드웨어는 FPGA(Field Programmable Gate Array)를 이용하여 실시간으로 4K DCI(Digital Cinema Image) 표준에 대응 할수 있도록 한다.

본 논문의 구성은 다음과 같다. 2장에서는 동적 영역 확장 방법에 대하여 간략하게 설명하고 3장에서는 제안하는 하드웨어의 구조에 대하여 설명한다. 4장에서는 제안하는 하드웨어의 성능평가를 수행하며, 5장에서는 제안하는 하드웨어를 IP(Intellectual Property)로 구현하고 그 성능을 평가한다. 6장에서는 결론을 맺는다.

#### II. LDR 영상의 HDR 변환 알고리즘

본 논문에서 사용하고자 하는 LDR 영상의 HDR 변환 방법은 기존의 연구 되었던 저조도 영상의 화 질 개선 알고리즘을 바탕으로 한다[11]. 제안하는

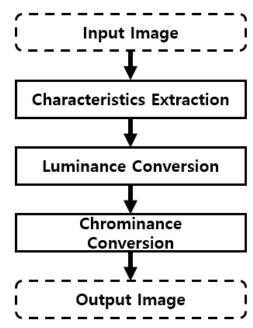

Fig. 1. Flowchart of LDR to HDR conversion. 그림 1. 동적 영역 변환 흐름도

방법의 흐름은 그림 1과 같다.

입력 영상에 대하여 영상의 특성을 추출 (Characteristics Extraction) 후, 특성에 따라 입력 영상의 휘도를 변환(Luminance Conversion)한다. 휘도의 변환이 완료되면 휘도의 변환비율에 따라 색상을 변환(Chrominance Conversion)하여 출력으로 내보낸다.

영상의 동적 영역을 변환하는 과정에서 수식 (1)에서 수식 (6)이 사용된다. 영상의 특징 추출은 입력 영상의 평균 휘도 값을 연산하면서 휘도의 히스토그램을 생성한다. 생성된 휘도 히스토그램은 휘도의 누적 분포 함수로 변환된다. 휘도의 누적 분포 함수의 10%, 20%, 30%, 40%에 해당하는 휘도를 추출하고, 수식 (1)을 이용하여 영상에 분포하고 있는 휘도간의 거리( $pixel_{dis}$ )를 측정한다.

$$pixel_{dis} = \sum_{n=2}^{4} \frac{CDF_n - CDF_1}{3} \times \frac{1}{mean_{vol} - CDF_1}$$

(1)

$mean_{val}$ 은 영상의 평균 휘도이다. 휘도 변환은 수식 (2)의 형태로 이루어진다.

$$L_{out} = L_{in} + LG(L_{in}) \times LW(L_{in})$$

(2)

$L_{out}$ 변환 된 휘도이며,  $L_{in}$ 은 입력 휘도이다.  $LG(L_{in})$ 는 입력 휘도에 대한 휘도 이득이며  $LW(L_{in})$

는 입력 휘도에 대한 휘도 가중치이다. 휘도 이득과 휘도 가중치는 각각 수식 (3)과 수식 (4)에 의하여 결정된다.

$$LG(L_{in}) = \frac{L_{in}}{255} + (\frac{255 - mean_{val}}{255})$$

(3)

$$LW(L_{in}) = \frac{(255 - L_{in})^{\alpha}}{255} \times (255 - L_{in})$$

(4)

α는 휘도 가중치를 결정하면 파라미터이며 수식 (5)에 의하여 결정된다. 휘도 변환이 완료 되면 색상 변환을 수행한다. 색상 변환은 수식 (6)을 사용한다.

$$\alpha = (1 - pixel_{dis}) \times \frac{255 - mean_{val}}{255}$$

(5)

$$C_{out} = C_{in} \times \frac{L_{out}}{L_{in}} \tag{6}$$

그림 2는 본 논문에서 사용하는 LDR 영상의 HDR 변환 예시를 보여준다. 그림 2(a)는 입력 영상이며 그림 2(b)는 출력 영상을 나타낸다. 휘도 및 색상 변환으로 동적 영역이 확장되었다.

Fig. 2. Result image of proposed LDR to HDR Conversion:

(a) LDR image, (b) HDR image.

그림 2. 제안하는 동적 영역 확장 방법의 결과: (a) LDR 영상, (b) 변환된 HDR 영상

#### Ⅲ. LDR 영상의 HDR 변환 하드웨어

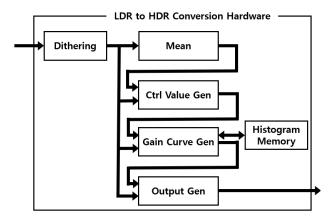

그림 3은 본 논문에서 제안하고자 하는 영상의 휘도 분포를 이용한 LDR 영상의 실시간 HDR 변환 하드웨어의 블록도이다. 제안하는 하드웨어는 디더링(Dithering), 평균기(Mean), 제어 변수 생성기(Ctrl Value Gen), 이득 곡선 생성기(Gain Curve

Gen), 출력 생성기(Output Gen), 히스토그램 메모리(Histogram Memory)를 포함한다.

Fig. 3. Block diagram of proposed hardware. 그림 3. 제안하는 방법의 하드웨어 블록도

LDR 영상은 좁은 동적 범위로 인하여 표현 할수 있는 정보의 양이 제한적이다. 이로 인한 부작용을 방지하기 위하여 입력되는 LDR 영상에 디더링을 수행한다. 이는 입력되는 LDR 영상에서 인접한 픽셀의 정보가 동일하더라도 출력에서는 인접한 픽셀의 결과 값이 동일하지 않고 유사한 값을 가지게 하여 보다 더 자연스러운 영상으로 만들어준다.

평균기는 입력되는 LDR 영상의 휘도 평균을 추출한다. 실시간으로 입력되는 영상에서 휘도 평균을 찾는 것은 매우 어려운 일이다. 영상의 휘도 평균을 찾고, 이를 해당 영상에 적용하기 위해서는 프레임 메모리가 필수적으로 동반되어야 한다. 그러나 본 논문에서는, 메모리의 사용량을 줄이기 위하여 추출한 휘도 평균을 다음 영상에 적용한다. 동영상의 경우 이어지는 각각의 영상은 높은 상관관계(Correlation)를 가지기 때문에 이와 같은 방법으로 메모리 사용량 및 처리 속도를 향상할 수있다.

제어 변수 생성기는 사용자가 입력하는 컨트롤 레지스터의 값과 영상의 휘도 평균을 이용하여 내 부에서 하드웨어를 제어하는 변수를 생성한다. 이 변수들은 이득 곡선 생성기에서 활용된다.

이득 곡선 생성기는 LDR 영상을 HDR 영상으로 변환하기 위한 이득 곡선을 생성한다. 제어 변수 생성기에서 생성한 변수와 히스토그램의 분포에 따라 이득 곡선이 결정된다.

## Ⅳ. 제안하는 하드웨어의 성능평가

Fig. 4. Histogram of LDR and HDR image: (a) histogram of LDR image, (b) histogram of HDR image. 그림 4. LDR 영상과 HDR영상의 히스토그램: (a) LDR 영상의

히스토그램, (b) HDR 영상의 히스토그램

제안하는 하드웨어의 성능을 평가하기 위하여 그림 2(a)의 입력 영상을 이용하여 휘도의 히스토그램을 측정하였다. 그림 4(a)는 LDR영상의 휘도 히스토그램 분포이며, 그림 4(b)는 HDR영상으로 변환된 결과의 휘도 히스토그램 분포이다. 각 히스토그램의 x축은 픽셀의 휘도, y축은 빈도를 나타낸다. 그림 4(a)는 휘도가 256개의 준위로 표현되지만, 그림 4(b)는 4096개의 준위를 가질 수 있다. 따라서 더욱 세부적인 표현이 가능하며, LDR 영상에서는 밀집 되어 있던 휘도의 준위가 HDR 영상에서는 무변으로 분산되어 더욱 세밀한 휘도의 분포를 나타낸다.

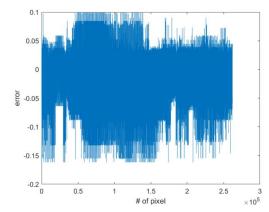

그림 5는 그림 2(a)의 영상을 제안하는 하드웨어로 구현하였을 때 발생하는 절단 오차의 범위를 나타낸다. x축이 영상의 각 화소를 의미하며, y축이

각각의 화소의 오차를 의미한다. 최대 오차가 256 준위 기준  $\pm 0.2$  미만으로 높은 정밀도를 가진다.

Fig. 5. Error bound of proposed method. 그림 5. 제안하는 방법의 오차 범위

#### V. IP 구현 및 평가

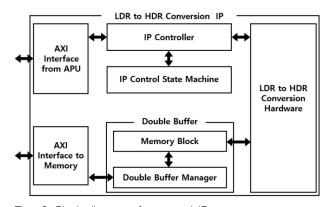

Fig. 6. Block diagram of proposed IP. 그림 6. 제안하는 방법의 IP 내부 블록도

본 논문에서 제안하는 하드웨어의 실시간 검증 및 성능 평가를 위하여 그림 6의 형태를 가지는 IP를 구현하였다. LDR to HDR Conversion IP는 본 논문에서 제안하는 방법을 하드웨어로 설계한 LDR to HDR Conversion Hardware와 AXI(Advanced eXtensible Interface) 인터페이스, IP의 내부 동작을 총괄하는 컨트롤러(IP Controller), 내부 동작에 따른 IP의 상태머신(IP Control State Machine), 메모리(Memory Block), 메모리 컨트롤러(Double Buffer Manager)로 구성된다. AXI 인터페이스는 APU가 IP를 제어하기 위한 용도로는 슬레이브 모드의 인터페이스를, 메모리에 접근하여 데이터 교환을 하기 위한 용도로는 마스터 모드의 인터페이스를 사

용하였다[14]. 더블 버퍼(Double Buffer) 구조를 사용하여 메모리에서 영상을 가져 오면서 하드웨어로 영상을 동시에 전송 할 수 있다.

표 1은 그림 6의 IP를 XILINX 합성 툴을 이용하여 합성한 결과이다. 레지스터(Slice Registers)는 총 1,452개를 소모하여 가용 면적의 0.3%를 사용하였으며, LUTs(Look Up Tables)는 가용 면적의 1%를 사용하였으며 최대 동작 주파수는 265.463MHz로 측정되었다. 측정된 최대 동작 주파수는 DCI 4K 영상을 초당 30장 처리 할 수 있는 속도로, 국제 4K 표준 25.6장 이상을 만족한다[2].

Table 1. XILINX Synthetic Result. 표 1. 자일링스 합성 툴을 이용한 합성 결과

| XILINX Design Analyzer  |                  |       |             |

|-------------------------|------------------|-------|-------------|

| Device                  | ZC7Z045-FFG900-2 |       |             |

| Slice Logic Utilization | Available        | Used  | Utilization |

| Slice Registers (#)     | 437,200          | 1,452 | 0.3%        |

| Slice LUTs (#)          | 218,600          | 2,388 | 1%          |

| Minimum period          | 3.767 ns         |       |             |

| Maximum Frequency       | 265.463 MHz      |       |             |

<sup>\*</sup> The EDA software was provided by IDEC, Korea.

#### VI. 결론

본 논문에서는 LDR영상을 실시간으로 HDR영상으로 변환 할 수 있는 하드웨어를 제안하고 이를 IP로 구현하여 그 성능을 평가하였다. IP 구현 결과 1,452개의 레지스터와 2,388개의 LUT를 사용하여 각각 0.3%, 1%의 사용 가능한 리소스를 사용하였다. 이는 전용 하드웨어의 면적이 적음을 의미하여, 영상 신호 처리 장치에 탑재하기에 용이함을 의미한다. 최대 동작 주파수는 265.463MHz로 4,096x 2,160 크기의 4K DCI 영상을 초당 30장 처리 할 수 있으므로, 국제 표준을 만족하는 성능을 가짐을 확인하였다.

#### References

- [1] ITU-R standard, Rec. ITU-R BT.2020, *ITU-R*, 2014.

- [2] ITU-R standard, Rec. ITU-R BT.2100, ITU-R, 2016.

- [3] SMPTE standard, SMPTE 2036-1, *SMPTE*, 2009.

- [4] R. Saha, P. P. Banik, and K. D. Kim, "Conversion of LDR image to HDR-like image through high-level synthesis tool for FPGA implementation," 2018 IEEE International Conference on Consumer Electronics (ICCE2018), pp.1–2, 2018. DOI:10.1109/ICCE.2018.8326111

- [5] G. D. Licciardo, C. Cappetta, and L. D. Benedetto, "Design and FPGA implementation of a real-time processor for the HDR conversion of images and videos," 2018 8<sup>th</sup> Computer Science and Electronic Engineering (CEEC2016), pp. 192–197, 2016. DOI:10.1109/CEEC.2016.7835912

- [6] C. Cappetta, G. D. Licciardo, and L. D. Benedetto, "An FPGA oprimization of a multiple resolution architecture for LDR to HDR image conversion," *International Symposium on Signals, Circuits and Systems (ISSCS2017)*, pp.1–4, 2017. DOI:10.1109/ISSCS.2017.8034902

- [7] T. Ai, M. A. Ali, G. Steffan, K. Ovtcharov, S. Zulfiqar, and S. Mann, "Real-time HDR video imaging on FPGA with compressed comparametric lookup tables," 2014 IEEE 27th Canadian Conference on Electrical and Computer Engineering (CCECE2014), pp.1-6, 2014.

DOI:10.1109/CCECE.2014.6901124

[8] G. Fu, L. Shen, H. Yang, X. Hu, and P. An, "Fast Intra Coding of High Dynamic Range Videos in SHVC," *IEEE Signal Processing Letters*, vol.25, no.11, pp.1665–1669, 2018.

DOI:10.1109/LSP.2018.2867895

[9] S. Park, S. Yu, M. Kim, K. Park, and J. Paik, "Dual Autoencoder Network for Retinex-Based Low-Light Image Enhancement," *IEEE Access*, vol.6, pp.22084–22093, 2018.

DOI:10.1109/ACCESS.2018.2812809

[10] S. Mandal, X. L. Dean-Ben, and D. Razansky, "Visual Quality Enhancement in Optoacoustic Tomography Using Active Contour Segmentation Priors," *IEEE Transactions on Medical Imaging*, vol.35, no.10, pp.2209–2217, 2016.

DOI:10.1109/TMI.2016.2553156

[11] H. Cho, G. J. Kim, K. Jang, S. L, and B. Kang, "Color Image Enhancement Based on Adaptive Nonlineer Curves of Luminance Features," *Journal of Semiconductor Technology and Science*, vol.15, no.1, pp.60–67, 2015.

DOI:10.5573/JSTS.2015.15.1.060

[12] S. Lee, D. Kim, and C. Kim, "Ramp Distribution—Based Image Enhancement Techniques for Infrared Images," *IEEE Signal Processing Letters*, vol.25, no.7, pp.931–935, 2018. DOI:10.1109/LSP.2018.2834429 [13] K. Park, S. Yu, S. Park, S. Lee, and J. Paik, "An Optimal Low Dynamic Range Image Generation Method Using a Neural Network," *IEEE Transactions on Consumer Electronics*, vol.64, no.1, pp.69–76, 2018. DOI:10.1109/TCE.2018.2811257 [14] XILINX, "AMBA AXI4 Interface Protoceol,"

https://www.xilinx.com/products/intellectual-prop

# BIOGRAPHY

# Seungmin Lee (Member)

erty/axi.html

2016: BS degree in Electronic Engineering, Dong-A University. 2018: MS degree in Electronic Engineering, Dong-A University 2018~: Ph.D Candidate in Electronic Engineering, Dong-A University

#### Bongsoon Kang (Member)

1985: BS degree in Electronic Engineering, Yonsei University. 1987: MS degree in Electrical Engineering, University of Pennsylvania.

1990: PhD degree in Electrical Engineering, Drexel University.

$1989\!\sim\!1999$  : Senior Staff Researcher, Samsung Electronics.  $1999\!\sim$  : Prof. of Dept. of Electronic Engineering, Dong-A University.