# 위상이 다른 4개의 클럭을 이용한 시추공 레이다 수신기용 ETS 샘플러 설계

유영재, 오재곤<sup>\*</sup> 한국산업기술대학교 전자공학부

# ETS Sampler design for borehole radar receiver using 4 different clock phases

Young-jae Yoo, Chaegon Oh\*

Division of Electronics, Korea Polytechnic University

요 약 시추공 레이다는 지하자원 및 지질탐사 목적으로 사용되는 레이다로서 수 ns의 펄스폭을 갖는 전자파를 송신하고 탐사 대상으로부터 반사되어 입력되는 수십에서 수백MHz의 반사파를 수신하기 위하여 고속 샘플러가 반드시 필요하다. 수십MHz의 샘플링 클럭 주파수로도 수GHz급의 샘플링 성능을 낼 수 있는 ETS(Equivalent-Time Sampling)는 시추공 레이다용 수신기의 샘플러로 사용이 적합하다. ETS 샘플러 설계에 있어 가장 중요한 요소인 샘플링 클럭 지연을 제어하는 방법으로 본 연구에서는 하나의 클럭 소스에 대해 각 90°씩 위상 차이를 가지는 4개의 클럭을 이용한 방법을 제시하였다. 제안하는 방법은 기존의 지연 발생기를 이용하는 방법보다 설정한 구간 내에서 데이터를 획득하는 시간이 1/23로 단축 가능하다. 구현된 샘플러를 기존 시추공 레이다의 수신기에 적용하면 단축된 샘플링 시간으로 인해 추가로 64회 누적이 가능해져 지하 터널탐사를 위한 수신신호 품질 개선 효과를 얻을 수 있다. 또한, 목표 샘플링 범위를 만족하기 위해서 여러 개의 샘플링 클럭지연제어 로직을 사용하는 기존 방식에 비하여 하나의 지연제어 로직을 사용함으로써 그간 반드시 필요하였던 보정 과정의생략이 가능하다. 그 결과 시스템의 구조를 단순화할 수 있었으며 균일한 샘플러의 구현이 가능하였다.

**Abstract** Borehole radar is a radar used for underground resources and geological exploration purposes. It needs a high-speed sampler to transmit electromagnetic waves with a pulse width of several ns and to receive reflected waves of several tens to several hundreds of MHz reflected from the object to be surveyed. ETS (Equivalent-Time Sampling), which can achieve sampling performance of several GHz with a sampling frequency of several tens of MHz, is suitable for use as a sampler of a borehole radar receiver.

In this paper, we propose a method to control the sampling clock delay, which is the most important factor in ETS sampler design, using four clocks with phase difference of 90° for one clock source.

The proposed method can reduce the time required to acquire the data within the set interval by 1/25 than the conventional method using the delay generator. When the implemented sampler is applied to the receiver of existing borehole radar, it is possible to accumulate 58 additional times due to the shortened sampling time.

In addition, by using one delay control logic compared with the conventional method using several sampling clock delay control logic in order to satisfy the target sampling range, it is possible to omit the correction process which was necessary in the past. As a result, the structure of the system can be simplified and a uniform sampler can be realized.

Keywords: Borehole radar, Delay generator, ETS, Geological exploration, High resolution sampler

\*Corresponding Author : Chaegon Oh(Korea Polytechnic Univ.)

Tel: +82-31-8040-0475 email: cgoh@kpu.ac.kr

Received December 14, 2017 Revised January 4, 2018 Accepted January 5, 2018 Published January 31, 2018

#### 1. 서론

GPR(Ground Penetrating Radar) 시스템은 전자기파를 사용하여 지하 매질을 통과할 때 발생하는 반사, 산란, 지연, 감쇄 등의 신호 변화를 분석함으로써 지하 구조 및 지층에 대한 정보를 얻는데 사용된다[1-3]. GPR 시스템은 크게 지표면에서 운용하는 표면형 레이다 시스템과 시추공에서 운용하는 시추공 레이다 시스템으로 나눌 수 있다. 전자기파는 지하 매질을 거치면서 매질의 전기적인 특성으로 인하여 많은 양이 감쇄된다. 따라서 표면형 레이다는 상대적으로 깊은 위치에 있는 목표물을 탐지하는데 어려움이 있어 시추공 레이다를 사용하고 있다. 시추공 레이다는 운용 방법에 따라 하나의 시추공에 송·수신기를 같이 투입하여 목표물에 반사되는 신호를 분석하는 반사형 시스템과 송·수신기를 각각의 시추공에 별도로 투입하여 목표물을 통과하는 신호를 분석하는 투과형 시스템으로 구분된다[4-5].

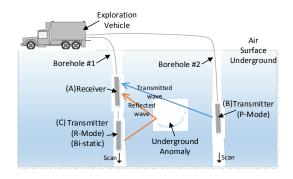

반사형 시스템과 투과형 시스템은 각각 장·단점이 있어 실제 운용에는 두 가지 방법을 복합적으로 사용하기도 한다. 이를 Fig. 1에 나타내었다. Fig. 1의 (A)와 (B)의 조합은 투과형 시스템을, (A)와 (C)의 조합은 반사형시스템의 구성이다.

Fig. 1. Borehole radar for underground cavity detection

본 논문에서는 시추공 레이다 시스템의 수신기에 필수적으로 필요한 고속 샘플러의 설계 요건을 알아보고수십MHz 단위의 저속 ADC(Analog Digital Converter)로 GHz급의 샘플링 해상도를 갖는 ETS(Equivalent-Time Sampling) 샘플러를 위상이 다른 4개의 클럭을 사용하여 구현하였다. 그리고 이를 지하터널 탐사용 시추공 레이다에 적용하여 그 성능을 확인하였다.

#### 2. 본론

# 2.1 GPR 시스템 수신기용 고속 샘플러 2.1.1 샘플링 해상도

GPR 시스템은 탐사 대상을 식별하기 위한 탐사 주파수를 선정하여 임펄스 형태의 전자파를 발생시켜 탐사에 사용한다. 이러한 임펄스는 송신 안테나를 통해 방사되고 배경 매질과 대상을 통과하거나 반사되어 수신 안테나로 입력되게 된다. 본 논문에서 목표로 하는 시추공 레이다는 지하에 구축된 최대 2m 크기의 터널을 식별하기위한 GPR로, 이 목표물을 탐지하기 위해 송신하는 임펄스의 펄스 간격은 5ns이다. 이를 주파수로 환산하게 되면 중심주파수는 200MHz 대역이므로 수신기의 최소한의 샘플링 해상도는 나이키스트율에 의해 400MHz가 요구된다. 또한 배경 매질이 화강암인 2m 구형의 터널에전자파가 통과할 경우에는 아래 식 (1)과 (2)에 의해서 10~13ns 정도의 속도 차이가 발생한다. 따라서 이를 감지하기 위한 샘플링 해상도가 요구되며 본 논문에서는 1ns를 목표로 하였다.

$$t_{\text{$\frac{1}{2}$}, \text{$\frac{1}{2}$}} = \frac{2 m}{(3 \times 10^8/3) m/\text{sec}} = 20 nsec$$

(1)

$$t_{\bar{z},7} = \frac{2 m}{(3 \times 10^8) m/\text{sec}} = 6.67 \, nsec$$

(2)

Ins의 해상도를 확보하기 위한 샘플링 클럭의 주파수를 1GHz로 구현하기 위해서는 그 구조가 복잡하고, 고가의 ADC가 요구되므로 수십 MHz의 저 해상도를 갖는 ADC로도 수GHz급의 샘플링 데이터를 얻을 수 있는 ETS 방식으로 구현하였다.

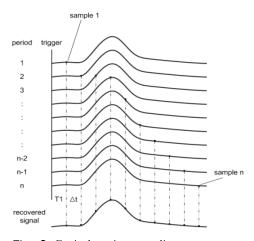

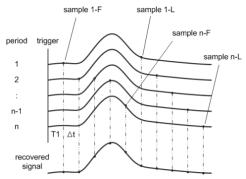

Fig. 2. Equivalent time sampling

ETS는 한 번의 신호 입력에 전체 샘플이 아닌 하나 혹은 일부 샘플을 획득하고, 다음 신호의 입력에서는 앞서 획득한 샘플과 시간 차이를 갖는 다른 샘플을 획득한다[6-7]. 이 과정을 Fig. 2에 나타내었다.

이를 위해서 ETS 샘플러는 신호와 신호의 반복 기준이 되는 동기신호가 필요하다. 첫 번째 동기신호가 입력되면 초기화 시간(T1)이후에 첫 번째 샘플을 획득하게되며, 두 번째 샘플은 두 번째 동기신호 입력 후 첫 번째 샘플을 획득한 T1에 미세하게 정의된 지연( $\Delta t$ )을 더한시간에서 획득하게 된다. 즉 트리거가 입력될 때마다 이전 샘플을 획득한 시간에  $\Delta t$ 를 더해 샘플을 획득하는 과정을 전체 신호의 파형을 복구할 수 있는 n번째 샘플을 획득할 때까지 반복한다. 만약  $\Delta t$ 를 게이트의 전파지연과 같은 ps단위로 일정하게 할 수 있다면 저속의 ADC로도 GHz급의 실시간 샘플링 한 것과 같은 결과를 얻을수 있다.

그러나  $\Delta t$ 를 미세하게 할수록 같은 범위에 대해서 샘플 수가 늘어나게 되고 샘플 수만큼 신호가 입력되어야하므로 RTS(Real-Time Sampling)에 비해 속도가 매우느리다. 이는 신호 입력 주기마다 하나가 아닌 여러 개의샘플을 가져오는 방식으로 개선할 수 있다.

#### 2.1.2 샘플링 범위의 조정

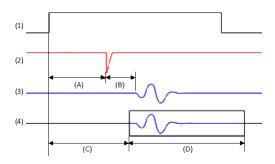

GPR 시스템은 전자파 송수신을 위해서 다음 Fig. 3과 같이 동기신호를 기준으로 송신기의 송신펄스 발생시간과 샘플링 범위를 동기신호 한 주기 내에서 조절할 수 있어야 한다. 송신기에서 동기신호 입력 후 송신펄스 발생까지 걸리는 시간은 펄스 발생 소자 및 방법에 따라고정되어 진다. 따라서 송신 펄스 발생시간을 임의적으로 조절하기 위해서는 기준이 되는 동기신호의 송신기로입력되는 시간을 조절할 수 있어야 한다. 즉 Fig. 3(A)의동기신호로부터 송신동기 신호를 조절할 수 있어야 한다.

송신기에서 송신펄스가 발생되어 송신 안테나를 통해 방사된 전자파는 지하공동이 의심되는 지하 매질을 통하여 수신 안테나로 입력되는데 이 과정에 소요되는 시간 (Fig. 3(B))은 송수신기의 물리적인 이격 거리와 Table. 1에 나타낸 전자파가 진행되는 매질의 유전상수에 따라다르며 이를 인위적으로 조절할 수는 없다. 따라서 지하매질을 통해 전달되는 전자파 신호를 수신하기 위해서수신기에서는 동기신호를 기준으로 샘플링이 시작되는시간(Fig. 3(C))과 범위(Fig. 3(D))를 조절 할 수 있어야

한다. 샘플링 범위는 샘플링 해상도와 데이터 개수에 의해 정해지는데 일반적으로 GPR 수신기와 신호처리 운용 S/W와의 연동을 위해 고정되므로 샘플링이 시작되는 시간을 조절하는 방식으로 그 범위를 조절하게 된다. 이를 위해 동기신호로부터 수신동기 신호를 조절할 수 있어야 한다.

Fig. 3. Electromagnetic wave transmission timing of borehole radar

- (1) Triggering clock (2) Tx pulse

- (3) Rx signal

- (4) Sampling range

Table 1. Permittivity and electromagnetic wave propagation speed according to materials

| Meterial  | Permittivity $(\epsilon_r)$ | Speed<br>(m/sec) |

|-----------|-----------------------------|------------------|

| Air       | 1                           | 300              |

| Dry sand  | 36                          | 120~170          |

| Wet clay  | 8~15                        | 86~110           |

| Soil      | 16                          | 75               |

| Limestone | 7~9                         | 100~113          |

| Granite   | 5~8                         | 106~120          |

| Basalt    | 8                           | 106              |

| Sandstone | 6                           | 112              |

| Concrete  | 6~30                        | 55~112           |

| Asphalt   | 3~5                         | 134~173          |

#### 2.2 샘플링 클록의 위상지연

#### 2.2.1 기존 Delay generator를 사용한 구조

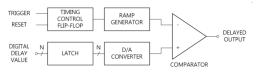

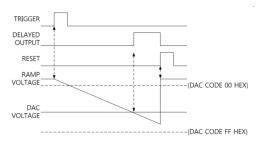

지연 발생기는 Fig. 4와 같이 트리거 입력을 DAC 입력 값에 해당하는 시간까지 지연한 후 출력한다. 트리거에 의해 낮아지는 램프 전압과 DAC의 출력 전압을 비교하여 일치하였을 때 출력을 내보내는 구조로 Fig. 5에 동작 타이밍을 나타내었다[8-9].

지연 발생기를 이용한 샘플링 클록 지연 방법은 그 원리가 간단하여 제어가 비교적 간단하나 us 단위의 램프전압 충 방전 시간으로 인해 한 번의 수신 파형에 하나

의 샘플데이터 획득만이 가능하다. 이는 1ns 해상도로 수백 ns 단위의 샘플링 범위를 확보하기 위해서는 샘플 링 범위를 해상도로 나눈 만큼의 지연 단수를 확보해야 하는 문제가 발생하며, 물리적 회로가 커지므로 수 cm 폭 내에 회로를 구현해야하는 시추공 레이다 보드의 특 성상 구현을 어렵게 하는 단점으로 작용한다. 따라서 이 를 해결하기 위해 다음의 DCM을 이용한 구현 방법을 연구하였다.

Fig. 4. Internal structure of the delay generator IC

Fig. 5. Operation timing of the delay generator

#### 2.2.2 다수의 DCM을 사용한 구조

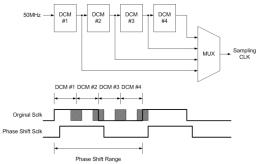

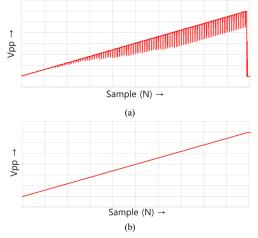

DCM(Digital Clock Manager)는 Xilinx FPGA가 제 공하는 클럭의 채배, 분주, 위상 이동 등을 제어할 수 있 는 모듈이다[10]. 하나의 DCM에서 클럭을 지연시킬 수 있는 범위는 해당 DCM에 입력 클럭에 종속되어 결정되 는데, 일반적으로 수십 ns 범위에 머무르게 된다. 따라서 수십~수백 ns로 정의된 샘플링 범위를 충족하기 위해서 는 Fig. 6과 같이 한 번의 동기 입력에 다수의 샘플데이 터를 가져오는 방식을 선택하여 수십ns 범위의 샘플링 클럭 한 주기 내에서의 지연을 수행하여 만족시킨다. 이 를 위해 다음 Fig. 7과 같이 다수의 DCM을 직렬로 연결 하여 샘플링 클럭의 한 주기를 만족하는 각각의 구간을 담당하여 지연을 수행한다. 그러나 이와 같은 방법은 Fig. 7 에서 음영으로 표현된 각 단의 DCM에 할당된 지 연범위 구간에서 중복되는 구간이 발생하여 샘플링 데이 터 순서에 맞지 않는 구간이 발생하게 된다. 이를 방지하 기 위해서는 샘플러 구현 후에 데이터 순서를 맞춰 보정 하는 작업이 필요하다. 이러한 보정작업은 시간에 따라 전압이 증가하는 RAMP 파형을 ADC에 입력하여 이용하여 수행하게 되며, 보정 작업 전후 결과를 Fig. 8에 나타내었다. 보정 전 시간 순서에 맞지 않는 데이터가 보정후 일정하게 증가하는 RAMP 파형으로 변화되었음을확인할 수 있다.

Fig. 6. Multiple point acquisition from ETS

Fig. 7, 20ns Sampling clock delay using 4 DCMs

Fig. 8. Calibration result of ETS sampler using RAMP wave

(A) Before calibration (B) After calibration

#### 2.2.3 단일 DCM을 사용한 구조

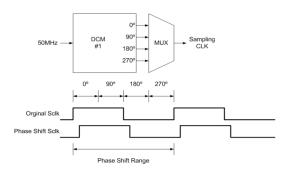

다수의 DCM을 사용하여 샘플링 클럭의 한 주기를 지연시키는 방법은 보정작업이 필수로 필요하게 되며 이를 위해서 보정을 위한 회로 로직과 보정 값을 저장하기 위한 저장 공간이 필요하게 된다. 이는 회로의 복잡성 및 하드웨어 추가로 인한 비용이 발생하게 되며 또한, 설계된 샘플러 별로 보정 작업이 요구된다. 이것은 여러 개의 DCM을 이용하여 구간별로 할당된 지연 구간의 중첩에 그 원인이 있다. 따라서 보정작업을 생략하고 샘플링 클럭의 한 주기를 만족할 지연방법의 연구가 필요하게 되고, 이를 위해 Fig. 9와 같이 하나의 DCM에서 출력되는 0°, 90°, 180°, 270°의 4개의 다른 위상 클럭을 사용하여 샘플링 클럭 한 주기를 만족할 수 있도록 구현하였다.

Fig. 9. ETS sampling clock delay using DCM's 0, 90, 180, 270 phase output

# 2.3 ETS 샘플러 설계 및 구현 2.3.1 ETS 샘플러 목표 성능

목표로 하는 시추공 레이다 시스템은 두 개의 시추공에 송신 및 수신 안테나를 각각 투입하는 투과형 시스템으로 일반적으로 사용하는 시추공간 거리는 최소 7~8m에서 최대 20m까지로 설정하였다. 이를 위한 수신기의 샘플링 범위 및 해상도 등의 설계 사양은 아래 Table. 2

Table 2. Sampler design for target specifications

| Item                        | Target specifications | Remark                             |

|-----------------------------|-----------------------|------------------------------------|

| Sampling range              | 500                   |                                    |

| Number of data              | 500                   | S/W specifications                 |

| Sampling resolution         | 1ns                   | 1GHz                               |

| Number of data accumulation | 128                   | 32 times accumulated,<br>4 buffers |

| Data bit                    | 16bit                 | 10bit ADC, 64 times accumulated    |

| Data IF                     | RS-485                | 600m communication                 |

와 같다. 기존의 운용프로그램과 호환 가능하도록 데이 터 프로토콜은 유지하며 시추공 투입을 위한 케이블 길 이를 고려하여 직렬통신을 사용하였다.

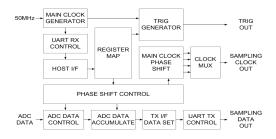

#### 2.3.2 단일 DCM을 사용한 ETS 샘플러 구조

본 논문에서 구현한 샘플러의 전체 구성은 Fig. 10과 같다. 50MHz 입력 클럭을 시스템 클럭으로 사용하기 위해 내부 클럭으로 설정하는 부분과 DCM 출력 클럭을 샘플링 클럭으로 사용하기 위해 동기신호를 발생하고 지연하는 부분, 그리고 출력된 샘플링 클럭에 의해 입력되는 ADC 데이터를 누적하고 직렬 인터페이스를 통해 출력하는 부분과 전체 시스템의 동작을 제어하는 레지스터 맵으로 구성된다. 전체 회로는 Verilog 언어를 사용하여 FPGA에 구현하였다.

Fig. 10. System logic structure of 1-DCM ETS sampler with Verilog HDL

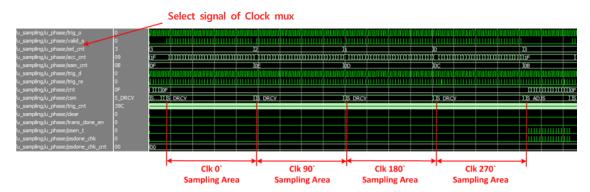

#### 2.3.3 단일 DCM을 사용한 시뮬레이션 결과

DCM의 0°, 90°, 180°, 270° 4개의 클럭을 순차적으로 선택하여 샘플링 클럭으로 출력하고 DCM의 Phase Shift를 위한 제어 신호를 출력하는 시뮬레이션 결과를 Fig. 11에 나타내었다. 50MHz 20ns 주기의 DCM 입력 클럭을 각각 25회씩 출력하여 500ns 범위의 샘플링 범위를 확보하였으며, 하드웨어 구현을 위해 선택한 FPGA는 1회의 phase shift enable 신호에 입력 클럭의 1/256위상이 이동하므로 13회의 PSEN 제어를 통해 1.015ns 지연하여 1GHz급 샘플링 해상도를 확보하였다.

목표로 하는 사양의 샘플러를 설계하기 위하여 지연 발생기를 이용하는 기존의 설계 방식에서 샘플링에 요구 되는 시간은 다음 수식(3)과 같이 계산되며, 본 논문에서 제안하는 하나의 DCM을 사용하는 방식에서 샘플링에 소요되는 시간은 수식 (4)와 같이 계산된다. 계산 결과 기존 방법에 비해 샘플링 시간이 1/23로 단축됨을 확인 할 수 있었다.

Fig. 11. Phase shifting module simulation result

$$\begin{split} t_{dg} &= \frac{1}{40K\!H\!z} \!\!\times\! 512(steps) \!\times\! 32(Accumulate) \\ &= 409.6ms \end{split} \tag{3}$$

$$\begin{split} t_{1DCM} &= \frac{1}{40K\!H\!z} \!\!\times\! 20(steps) \!\times\! 32(Accumulate) \\ &\quad + \frac{1}{40K\!H\!z} \!\!\times\! 13(psen) \!\times\! 5 = 17.625ms \end{split} \tag{4}$$

### 2.3.4 시스템 합성 결과

Xilinx Spartan3 FPGA에 전체 회로 로직을 합성한 결과, 아래 Table. 3과 같은 크기의 FPGA 자원이 사용되었으며 검증에 사용한 수신기용 회로를 Fig. 12와 같이 제작하였다.

Table 3. Result of logic synthesis

| Item         | Item used | Usage |

|--------------|-----------|-------|

| Flip-flops   | 1,906     | 26%   |

| 4-input LUTs | 2,270     | 31%   |

| RAMB16s      | 8         | 50%   |

| DCM          | 2         | 50%   |

Fig. 12. Implementation of 1-DCM sampler for borehole radar

#### 2.3.5 시스템 검증

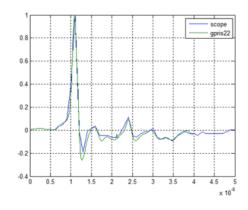

샘플링 결과의 검증을 위해 동일한 신호 입력에 대해 상용 오실로스코프로 측정한 데이터와 비교하였으며 그 결과를 아래 Fig. 13에 나타내었다. 비교 측정에 사용한 오실로스코프는 2GHz급으로 본 논문에서 제안한 방법 으로 구현한 샘플러로 획득한 데이터와의 동일함을 확인 하였다.

Fig. 13. Verification of sampling result by oscilloscope

#### 3. 실험 결과 및 고찰

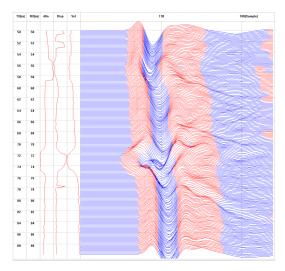

#### 3.1 ETS 샘플러 적용 및 결과

본 연구로 제작된 샘플러를 장착한 시추공 레이다를 이용하여 지하 73m 지점에 있는 1.5m 크기의 터널을 탐사한 결과를 Fig. 14에 나타내었다. Fig. 14는 0.2m 단위로 송수신기 안테나를 이동하면서 수신한 데이터를 겹쳐 표현한 wiggle 그래프로 송신 펄스의 도달 시간 변화를 시각적으로 보기 위한 가장 기본적인 GPR 데이터 디스플레이 방법이다. 심도 70m까지 시추공 천공 편차로 인해 완만한 도달 시간 변화를 보이던 수신 파형이 70m 지점부터는 급격하게 빨라져 73m 지점에서 가장 일찍

도착하고 76m까지 다시 느려지는 현상을 확인하였다. 이는 지하 73m 지점에 있는 공기로 채워진 인공 터널로 인해 발생하는 현상으로 예상된 범위 내에서 도달 시간 이 변화됨을 확인할 수 있었다.

Fig. 14. 1.5m underground cavity detection result at depth 73m

#### 4. 결론

본 논문에서는 90°의 위상 차이를 갖는 4개의 클럭을 1ns 단위로 동일하게 지연시켜 샘플링 클럭으로 사용할수 있는 1GHz급 ETS 샘플러를 구현하는 방법을 제안하였다.

본 연구에서 제안하는 방법은 기존의 지연 발생기를 사용하거나 다단의 DCM을 사용하는 방법에 비해 그 하 드웨어 구조가 간단하고, 샘플링 데이터를 획득하는데 요구되는 시간이 단축된다.

동기신호 40kHz와 32회 누적 횟수의 동일한 조건에서 기존에는 데이터 획득에 요구되는 시간이 409.6ms가 필요하지만, 본 연구를 통해 구현된 방식에서는 17.6ms로 단축되었다. 이를 통해 최종 데이터 출력 주기가 2Hz인 기존 방식보다 9.53Hz로 개선되어 탐사 속도를 향상할 수 있었다. 또한, 최대 누적횟수를 데이터 용량을 고려하여 기존 32회에서 96회로 변경하여도 7.29Hz의 초당 데이터 출력주기를 확보할 수 있었으며, 64회 증가한 누적으로 인해 신호품질 개선 효과도 얻을 수 있었다.

#### REFERENCES

- David J. Daniels, Ed., "Ground Penetrating Radar," Radar, Sonar & Navigation, pp. 10-14, 2004.

- [2] L. P. Peters Jr., J. J. Daniels, and J. D. Young, "Ground penetrating radar as a subsurface environmental sensing tool," Proceedings of the IEEE, vol. 82, no. 12, pp. 1802-1822, Dec. 1994. DOI: https://doi.org/10.1109/5.338072

- [3] J. J. Park, J. K. Han, S. K. Yoo, K. K. Hong, "GPR technology for underground cavity exploration in the ground", J. Korean Geosynthetics Society vol. 14, no. 3, pp. 12-17, 2015.

- [4] S. J. Cho, J. H. Kim, C. R. Kim, J. S. Son, and N. H. Sung, "Application of Borehole Radar to Tunnel Detection," Geophysics and Geophysical Exploration, vol. 9, no. 4, pp. 279-295, 2006.

- [5] S. W. Kim, S. Y. Hyun, J. H. Lee, S. Y. Lee, J. H. Cho, K. T. Oh, and S. Y. Kim, "The development of a pulse borehole radar system for underground cavity detection", Technical Report of IEICESANE, vol. 107, no. 277, pp. 93-97, Oct, 2007.

- [6] E. Moreno-Garcia, J. M. de la Rosa-Vazquez, and O. Alonzo-Larraga, "An Approach to the Equivalent-Time Sampling Technique for Pulse Transient Measurements," in 16th International Conference on Electronics, Communications and Computers (CONIELECOMP'06), pp. 34-34, 2006.

DOI: https://doi.org/10.1109/CONIELECOMP.2006.12

- [7] E.M.Garcia, J.M. de la Rosa-Vazquez, O. Alonzo-Larraga, "An Approach to the Equivalent-Time Sampling Technique for Pulse Transient Measurements", Proceeding of the 16th IEEE International Conference on ECC, 2006.

DOI: https://doi.org/10.1109/CONIELECOMP.2006.12

- [8] Craven Hilton and Jeff Barrow, "Programmable-delay ICs control system timing," Analog Devices Inc., 1988s.

- [9] M Yan, M Tian, L Gan, X Chen, "Impulse Ground Penetrating Radar Hardware System Design", ITS Telecommunications Proceedings, 2006 6th International Conference on, IEEE DOI: <a href="https://doi.org/10.1109/ITST.2006.288852">https://doi.org/10.1109/ITST.2006.288852</a>

- [10] Digital Clock Manager (DCM) Module, Xilinx Product Datasheet DS485, 2009.

### 유 영 재(Young-jae Yoo)

#### [준회원]

• 1988년 2월 : 한양대학교 전자공학 과 (공학사)

- 2014년 2월 ~ 현재 : 한국산업기 술대학교 지식기반기술에너지대학 원 (박사과정)

- 1978년 1월 ~ 1986년 12월 : 한국 방송(KBS) 기술부

- 1988년 1월 ~ 현재 : ㈜엘프프로 페셔널

<관심분야> GPR, Audio 응용

## 오 재 곤(Chaegon Oh)

#### [정회원]

- 1989년 2월 : 금오공과대학교 전자 공학과 (공학사)

- 1999년 8월 : 경희대학교 전자공학 과 (공학박사)

- 1989년 12월 ~ 1997년 9월 : 삼성 전자 선임연구원

- 1997년 10월 ~ 현재 : 한국산업기 술대학교 전자공학부 교수

<관심분야> SoC설계, GPR, Laser 응용