Journal of Sensor Science and Technology Vol. 26, No. 5 (2017) pp. 348-352 http://dx.doi.org/10.5369/JSST.2017.26.5.348 pISSN 1225-5475/eISSN 2093-7563

# 내장 필터를 갖는 15b 고해상도 혼합형 A/D 변환기

안경찬 · 임신일\*

# A 15b High Resolution Hybrid A/D Converter with On-Chip Filter

Kyung-Chan An and Shin-Il Lim<sup>+</sup>

#### **Abstract**

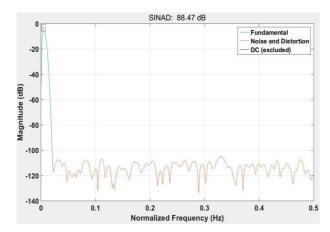

In this paper, we propose a high resolution A/D converter for a sensor interface that processes low frequency AC signals. A 6b SAR ADC with low power consumption and a 11b incremental ADC with high resolution are combined together to perform 15b resolution. Conventional hybrid ADC has a disadvantage that it can convert t only DC signal, but in this paper, it is possible to convert data to AC signal by increasing input range of incremental ADC. The decimation filter is implemented on-chip. The designed Hybrid ADC operates at supply voltage of 1.8V and consumes the current of 6.98uA. The OSR (oversampling ratio) is 90. And SFDR, SNDR, ENOB and FoMs are 96.59dB, 88.47dB, 14.4-bit and 139.5dB, respectively.

Keywords: SAR ADC, Incremental ADC, Hybrid ADC, Oversampling ADC

#### 1.서 론

IoT 시대가 다가옴에 따라, 다양한 관련 제품들이 개발되고 있다. IoT 제품의 특징은 주변 환경에 관련된 정보를 수집하고, 그에 따라 사용자에게 알맞은 정보 또는 환경을 제공해주는 것이다. 이러한 정보 수집은 일반적으로 센서 인터페이스를 통해 이루어진다[1,2]. 이때 수집된 아날로그 정보를 디지털 데이터로 변환하는 과정에서 손실을 줄이기 위해 고해상도의 특징을 갖는증가형 ADC가주로 사용된다. 하지만증가형(incremental) ADC의 경우, 고해상도로 갈수록 높은 과 표본화 비(OSR, oversampling ratio) 또는 높은 차수의 루프 필터(loop filter)를 요구하게 된다[3]. 높은 OSR은 일반적으로 데이터 변환시간의증가를 요구하며, 데이터 변환 시간을 줄이기 위해서는 고속 동작을 요구하게 된다. 이러한 현상은 회로 동작에 필요한 소모전력을 증가시킨다. 또한 높은 차수의 루프 필터구조는 회로의 복잡성과 면적 그리고 설계 난이도를 증가시키는 문제를 가지고 있다. 이러한 문제점을 해결하기 위한 방법으로 혼합형 ADC

가 제안되었다[4-7]. 하지만, 참고문헌[4]의 ADC는 증가형 ADC 의 입력범위가 SAR ADC 동작 결과의 2 LSB라는 좁은 입력범위를 가짐으로써, DC 신호에 대해서만 데이터 변환이 가능하다는 한계와 40ms라는 긴 변환 시간의 단점을 가지고 있다. 참고문헌[6]의 ADC는 AC 입력신호를 처리할 수 있지만 수 mW의 큰 전력 소비를 한다는 단점을 가지고 있다. 또한 참고문헌[4,6]의 ADC는 데시메이션 필터를 CIC(cascaded integrated comb) 필터를 사용했는데 칩 내부에 내장하여 구현하지 못하고 칩 외부에 구현하였다는 단점이 있다. 본 논문에서는 12.56uW의 적은 소비전력과 칩 내장형 데시메이션 필터를 갖는 고해상도 결합형 ADC를 제안하였다.

#### 2. 제안한 결합형 ADC 구조

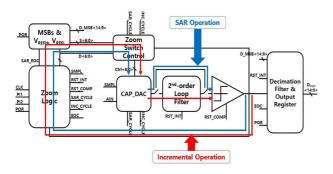

Fig. 1은 제안하는 결합형 ADC의 블록도를 보여준다. Fig. 1에 보이는 바와 같이, 제안된 결합형 ADC는 SAR ADC 동작과 증가형 ADC 동작으로 구성되어 있으며, 각 동작은 순차적으로 진행된다. SAR ADC 동작이 먼저 이루어지며, 7-비트의디지털 코드를 출력한다. 이 7-비트의디지털 코드를 기반으로, 결합형 ADC의 MSB 6-비트와 증가형 ADC 동작에 필요한 입력범위 및 기준전압을 결정한다. 즉, 증가형 ADC 동작의 입력범위는 SAR ADC 동작의 6-비트 출력결과 중 4 LSBs를 설정하여 구현하였다. 증가형 ADC 동작을 통해 LSB 11-비트의디지털 코드가 출력되며, 이 값은 SAR ADC 동작의 MSB 6-비트와 결합하여 최종적으로 15-비트의 고해상도 결과를 출력한

This is an Open Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License(http://creativecommons.org/licenses/bync/3.0) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

서경대학교 전자공학과(Dept. of Electronics Engineering, Seokyeong University)

Seokyeong University, 124, Seogyeong-ro, Seongbuk-gu, Seoul, 02713, Korea <sup>†</sup>Corresponding author: silim@skuniy.ac.kr

<sup>(</sup>Received: Sep. 15, 2017, Revised: Sep. 14, 2017, Accepted: Sep. 20, 2017)

Fig. 1. Block diagram of proposed hybrid ADC

다. 이 때 중간 2-비트는 SAR ADC 동작의 에러를 수정하기 위해 겹치게 된다. SAR ADC 동작과 증가형 ADC 동작은 하나의 비교기를 이용하여 서로 공유한다. 그림의 CAP DAC은 SAR ADC 동작 동안에 커패시터 DAC으로 동작하며, 증가형 ADC 동작 동안에는 2차 루프 필터의 입력 커패시터로 동작한다.

# 2.1 사용한 2차 루프 필터 [4]

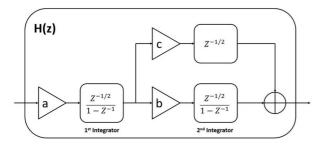

Fig. 2는 2차 루프 필터의 블록도를 보여준다. 두 개의 반주기 지연 적분기 (half delayed integrator)와 하나의 반주기 지연 덧셈기 (half delayed adder)로 구성되어 있으며, 각 적분기와 덧셈기의 이득에 따라 2차 루프 필터의 전달함수 H(z)는 식(1)과 같이 표현된다. 본 논문에서 설계한 2차 루프 필터는 a=1.28, b=0.5, c=1로 설계되었다. 내부에 사용된 두 개의 적분기는 인 버터(inverter) 기반의 증폭기로 설계되었으며, 옵셋을 없애기 위해 오토 제로(auto zeroing) 기능을 포함한다.

$$H(z) = \frac{ac \cdot z^{-1}}{(1 - z^{-1})^2} + \frac{ac \cdot z^{-1}}{1 - z^{-1}}$$

(1)

Fig. 2. Block diagram of 2nd-order loop filter

# 2.2 인버터(inverter)기반의 증폭기를 사용한 적분기 [6]

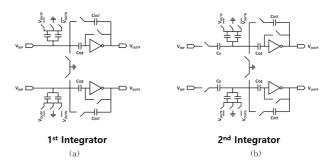

Fig. 3은 인버터 기반의 적분기 회로도를 보여준다. Fig. 3 (a) 와 (b)는 각각 첫 번째 적분기와 두 번째 적분기의 회로도이다. 인버터형 증폭기를 사용하면 소모 전력을 줄일 수 있다. 두 개의 인버터 기반의 적분기를 가상 차동(pseudo differential) 형태

로 구성하였으며, 오토 제로 회로와 공통전압 귀환 (CMFB, common-mode feedback) 회로를 포함한다. 첫 번째 적분기는 입력 커패시터를 SAR 동작시의 CAP DAC과 공유하므로, 2차 루프 필터에 포함되지 않는다. 첫 번째 적분기의 입력 커패시터와 적분 커패시터(CINT)는 각각 10.24pF, 8pF이고, 두 번째 적분기의 입력 커패시터와 적분 커패시터(CINT)는 각각 320fF, 640fF이다.

Fig. 3. (a) 1st and (b) 2nd inverter based integrator

#### 2.3 증가형 동작의 확장된 입력 범위

기존의 혼합형 ADC는 SAR ADC 동작의 2-LSB 내에서 증가형 ADC 동작의 입력범위로 설정하였었다[2]. 이는 SAR ADC의 오프셋과 양자화 오차를 완화시켜 주며, 입력 신호가증가형 ADC 동작 동안 입력범위 안에 안정적으로 들어올 수있도록 하기 위함이다. 하지만, 참고문헌[2]의 혼합형 ADC는 300의 OSR로 인해 긴 변환주기를 요구하게 되었고, 긴 변환주기 동안 입력신호가 증가 혹은 감소하게 될 경우 2-LSB라는 증가형 ADC 동작의 좁은 입력범위 밖으로 입력신호가 벗어나는 문제가 있어 DC 신호에 대해서만 데이터 변환 동작이가능하다는 한계를 가지고 있다. 이를 해결하기 위해, 본 논문에서는 Fig. 4와 같이 증가형 ADC 동작의 입력범위를 SAR ADC 동작 결과의 4-LSB로 확장 하였으며, SAR ADC 동작

Fig. 4. Simple block diagram of feedback system

의 부담을 줄이고, 입력 신호가 증가형 ADC 동작의 입력범위 가운데 위치하게 함으로써 최대크기 입력신호에서 발생하는 양자화 오차의 영향을 제거하였다. SAR ADC 동작의 결과를 k<6:0>이라 하였을 때, 증가형 ADC 동작의 입력범위는 Fig. 4과 같이 k<0> 값에 따라 입력신호가 가운데 위치할 수있도록 결정된다.

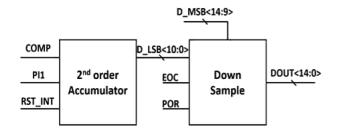

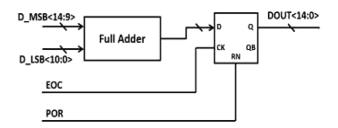

#### 2.4 내장 데시메이션 필터

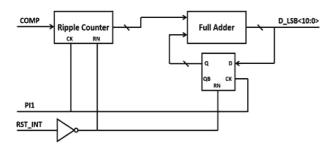

일반적으로 고해상도  $\Delta\Sigma$  ADC 또는 증가형 ADC는 데시메 이션 필터로써 CIC 필터를 사용하며, FPGA를 이용하여 칩 외 부에 구성한다. 본 논문에서는 증가형 ADC는 2차 루프 필터와 2차누적기(accumulator)를 사용하고, OSR을 90으로 설정하였 다. 이러한 설정은 증가형 ADC 동작 결과의 최댓값을 2048로 만들어주며, 이는 증가형 ADC 동작 결과에 이득 오차가 발생 하기 않음을 의미한다. 결과적으로 데시메이션 필터를 CIC 필 터 대신에 2차 누산기(accumulator)로 설계하였으며 칩 내부에 구현하였다. 데시메이션 필터는 SAR ADC 동작 결과인 MSBs 와 증가형 ADC 동작 결과인 LSBs를 결합해주는 덧셈기와 혼 합형 ADC의 출력 레지스터를 포함한다. Flg. 5는 내장 데시메 이션 필터의 블록도 이다. 2차 누산기와 다운샘플 블록으로 구 성 되어있다. 증가형 ADC를 위한 데시메이션 필터로 2차 누산 기가 사용되었으며, 2차 누산기의 블록도는 Fig. 6과 같다. 첫 번째 누산기는 1-비트 신호를 입력 받으므로 리플카운터로 간 단하게 구성하였으며 7-비트 결과를 출력한다. 두 번째 누산기 는 전가산기와 한주기 지연회로로 구성 되어있으며, 7-비트 신 호를 입력 받아 11비트의 결과를 출력한다. 즉, 2차 누산기는 1-비트의 증가형 ADC 출력을 입력 받아 90주기에 걸쳐 11-비트

Fig. 5. Block diagram of decimation filter

Fig. 6. Block diagram of 2nd-order accumulator

Fig. 7. Block diagram of down sample

의 증가형 ADC 결과로 출력하는 회로이다. 이 11-비트 결과는 Fig. 7의 다운샘플 회로를 통해 6-비트의 SAR ADC 결과와 더해져서, 최종적으로 15-비트 결과로 출력된다. 증가형 ADC 동작의 입력범위는 SAR ADC 동작 결과의 4 LSB이며, 이는 SAR ADC 동작 결과의 하위 2-비트와 증가형 ADC 동작 결과의 상위 2-비트가 서로 겹침을 의미한다. 따라서 혼합형 ADC 의 최종 출력은 식(2)에 의해 결정된다. 식(2)에서 n은 증가형 ADC 동작 결과의 비트 수 이다.

$$D_{out} = MSBs \bullet 2^{n-2} + LSBs \tag{2}$$

# 3. 모의 실험

#### 3.1 레이아웃 및 모의실험 환경

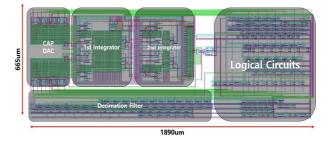

제안된 구조와 회로는 0.18 um 일반 CMOS 공정을 이용하여 설계되었다. Fig. 8은 설계된 혼합형 ADC의 레이아웃 도이고, 전체 면적은 665 um x 1890 um이다. 혼합형 ADC의 모의실험

Fig. 8. Layout of Hybrid ADC

Table 1. Simulation Environment of Hybrid ADC

| Parameter   | Value   | Description                          |

|-------------|---------|--------------------------------------|

| <br>VDD [V] | 1.8     | Supply Voltage                       |

| VCM [V]     | 0.9     | Common-mode Voltage                  |

| VINPP [V]   | 1.62    | Peak-to-Peak Voltage of input signal |

| FIN [Hz]    | 0.48992 | Input Frequency                      |

| Fs [kHz]    | 12.8    | Sampling Frequency                   |

| OSR         | 90      | Oversampling Rate                    |

환경은 Table 1과 같다. VDD, VCM은 각각 1.8 V, 0.9 V이고, V<sub>IN,PP</sub>와 FIN 은 각각 1.62 Vpp, 0.48992 Hz이다. Fs는 12.8 kHz 이고, OSR은 90으로 설정하였다.

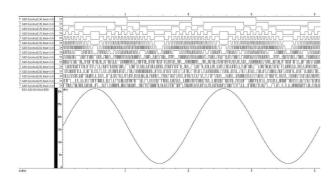

# 3.2 모의실험 결과

Fig. 9는 혼합형 ADC의 모의실험 결과이다. 그림의 상단 부분은 15-비트 디지털 코드 결과이고, 하단부분은 이상적인 디지털-아날로그 변환을 거친 결과의 그래프이다. Fig. 10은 Fig. 9의 결과에 대한 FFT 변환 결과로써, 혼합형 ADC의 출 력 결과가 88.47 dB의 SNDR 즉, 14.4의 ENOB를 갖는다는 것을 확인 할 수 있었다. Table 2는 혼합형 ADC의 성능 요 약을 보여준다. 참고문헌 [4]는 40 ms의 긴 변환시간과 DC 입력신호에 대한 데이터 변환만이 가능하다는 단점을 가지고 있고, 참고문헌 [6]은 AC 입력신호에 대한 데이터 변환이 가 능하지만 1.66 mW라는 큰 소비전력을 요구한다. 또한, 참고 문헌 [4,6]은 데시메이션 필터를 칩 내부에 구현하지 않고 외 부에서 FPGA를 이용해 구현하였다. 하지만, 본 논문에서는 0.0126 mW의 적은 소비전력으로 AC 입력신호에 대한 데이 터 변환이 가능할 뿐만 아니라, 2차 누산기로 설계된 데시메 이션 필터를 내장 설계함으로써 회로의 집적도를 향상시켰다 는 장점을 가진다.

Fig. 9. Simulation Results of Hybrid ADC

Fig. 10. FFT Result

Table 2. Performance summary of proposed hybrid ADC

| Parameter           | This paper                               | [4]                                      | [6]                                            |

|---------------------|------------------------------------------|------------------------------------------|------------------------------------------------|

| Architecture        | SAR + 2 <sup>nd</sup> -order Incremental | SAR + 2 <sup>nd</sup> -order Incremental | SAR +<br>3 <sup>rd</sup> -order<br>Incremental |

| Technology [µm]     | 0.18                                     | 0.16                                     | 0.16                                           |

| Chip area [mm²]     | 1.26                                     | 0.375                                    | 0.16                                           |

| Supply voltage [V]  | 1.8                                      | 1.8                                      | 1.8                                            |

| Supply current [µA] | 6.98                                     | 3.5                                      | 920                                            |

| Oversampling ratio  | 90                                       | 1024                                     | 282                                            |

| Signal type         | AC                                       | DC                                       | AC                                             |

| SFDR [dB]           | 96.59                                    | -                                        | -                                              |

| SNDR [dB]           | 88.47                                    | 119.8                                    | 98.3                                           |

| ENOB [bit]          | 14.4                                     | 19.6                                     | 16                                             |

| FoMs* [dB]          | 139.5                                    | 182.7                                    | 178.3                                          |

| $T_{CONV}$ [ms]     | 7.73                                     | 40                                       | 0.025                                          |

| Decimation filter   | On-chip                                  | Off-chip                                 | Off-chip                                       |

\*FoMs =  $SNR_{MAX} + 10log(1/(Power x 2T_{CONV}))$ , which is derived from Schreier's FoM [4]

### 4. 결 론

데시메이션 필터가 내장된 15-비트 고해상도 혼합형 ADC를 설계하였다. 데이터 변환은 두 단계로 이루어지며, SAR ADC 동작과 증가형 ADC 동작이 순차적으로 진행된다. SAR ADC 동작을 통해 상위 디지털 비트 값과 증가형 ADC 동작에 필요 한 기준 전압 값 들이 결정되며, 이를 바탕으로 증가형 ADC 동 작이 이루어진다. 증가형 ADC의 기준 전압 값 범위는 SAR ADC 결과의 4배의 LSB 범위로 설정하였다. 증가형 ADC의 OSR은 90이다. SAR ADC의 결과와 증가형 ADC의 변환 결과 를 결합해주는 출력 레지스터와 증가형 ADC의 데시메이션 필 터는 칩 내에 구현하였다. 증가형 ADC의 루프 필터와 데시메 이션 필터는 2차로 설계하였으며, 루프 필터에는 인버터 기반의 적분기 가 사용되었다. SAR ADC와 증가형ADC는 각각 6-비 트 MSB와 11-비트의 LSB를 출력하며, 혼합형 ADC 전체 결과 는 15-비트의 고해상도 출력을 갖는다. 제안된 혼합형 ADC는 0.18 um CMOS 공정에서 설계되었으며, 공급전압은 1.8 V, 소 비전력은 12.56 uW, 변환 시간은 7.73 ms이고, 96.59 dB의 SFDR, 88.47 dB의 SNDR과 14.4 bit의 ENOB를 성능을 얻었다.

#### 감사의 글

본 연구는 미래창조과학부 및 정보통신기술진흥센터의 대학 ICT연구센터육성 지원사업의 연구결과로 수행되었음 (IITP-2017-2012-0-00641).

CAD 툴은 반도체 교육 센터(IDEC)를 통해서 지원 받음.

#### REFERENCES

- [1] K. Souri, Y. Chae, and K. A. A. Makinwa, "A CMOS temperature sensor with a voltage- calibrated inaccuracy of 0.15°C() from -55 C to 125 C," *IEEE J. of Solid-State Circuits*, Vol. 48, No. 1, pp.292-301, Jan. 2013.

- [2] Y. Chae, J. Cheon, S. Lim, M. Kwon, K. Yoo, W. Jung, D.-H. Lee, S. Ham, and G. Han, "A 2.1 Mpixels 120 frame/s CMOS image sensor with column-parallel ∑△ ADC architecture," *IEEE J. Solid-State Circuits*, Vol. 44, No. 2, pp. 236-247, Jan. 2011.

- [3] J. Robert, G. C. Temes, V. Valencic, R. Dessoulavy and P. Deval, "A 16-bit low-voltage CMOS A/D converter," *IEEE J. of Solid-State Circuits*, Vol. 22, No. 2, pp. 157-163, April

1987.

- [4] Chae Youngcheol, Kamran Souri, and Kofi A. A. Makinwa, "A 6.3uW 20bit Incremental Zoom-ADC with 6ppm INL and 1uV Offset," *IEEE J. of Solid-State Circuits*, Vol. 48, No. 12, pp. 3019-3027, Dec. 2013.

- [5] R. Wu, Y. Chae, J. H. Huijsing, and K. A. A. Makinwa, "A 20-b 40mV range read-out IC with 50-nV offset and 0.04% gain error for bridge transducers," *IEEE J. Solid-State Cir*cuits, Vol. 47, No. 9, pp.2152-2163, Sept. 2012.

- [6] Burak Gonen, Fabio Sebastiano, Robert van Veldhoven and Kofi A. A. Makinwa, "A 1.65mW 0.16mm2 Dynamic Zoom-ADC with 107.5dB DR in 20 kHz BW," *IEEE ISSCC* 2016, pp. 282-284, 2016.

- [7] A.Agah, K. Vleugels, P. B.Griffin, M. Ronaghi, J. D. Plummer, and B. A.Wooley, "A high-resolution low-power oversampling ADC with extended-range for bio-sensor arrays," *IEEE J. Solid-State Circuits*, Vol.45, No. 6, pp. 1099-1110, Jun. 2010.