Regular Paper

J. Korean Inst. Electr. Electron. Mater. Eng.

Vol. 30, No. 7, pp. 423-426 July 2017

DOI: https://doi.org/10.4313/JKEM.2017.30.7.423

ISSN 1226-7945(Print), 2288-3258(Online)

# 1,700 V급 Static Induction Thyristor 소자 최적화

# 문경숙<sup>1</sup>, 구상모<sup>2,a</sup>

<sup>1</sup> 가천대학교 글로벌캠퍼스 <sup>2</sup> 광운대학교 전자재료공학과

## Optimization of 1,700 V Static Induction Thyristor Devices

Kyoung-Sook Moon<sup>1</sup> and Sang-Mo Koo<sup>2,a</sup>

<sup>1</sup> Global Campus, Gachon University, Seongnam 13120, Korea

(Received May 7, 2017; Accepted May 16, 2017)

**Abstract:** The designing approaches with consideration offabrication process technologies for high-frequency, high-powered, silicon-based static induction thyristors (SITH) are presented. The effects of doping concentration and thickness on the I-V characteristics and power performance of the devices are discussed. The dependence of SITH switching performances on material, geometric structure, and technological parameters is examined by using two-dimensional simulations. Thick-epitaxy technology is found to be one of the most critical steps in realizing the proposed structure and switching times,  $t_{\text{off}}$ , of SITH, which may be reduced to below ~0.26 µs for the proposed 1,700 V SITH devices after optimization.

Keywords: Static induction thyristor, Thyristor, Power devices

#### 1. 서 론

파워 반도체 소자 가운데 SITH (static induction thyristor)는 대용량, 고내압이 특징인 thyristor의 한 종류로서, 스위칭 특성이 탁월한 SIT (static induction transistor)와 PiN 구조를 결합하여, 높은 전류 구동 능력과 함께 낮은 온 저항 특성을 갖도록 한 구조로 주목을 받아왔다 [1-3].

SITH는 낮은 온 상태 전압강하와 우수한 순방향 전도 특성을 갖게 되는 바, 그 주된 메커니즘은 SIT의 N형 드레인을 P형으로 변경하였을 때 발생하는 전도성 변조 (conductivity modulation)에 기인하며 [3], SITH의

a. Corresponding author; smkoo@kw.ac.kr

Copyright ©2017 KIEEME. All rights reserved. This is an Open-Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License (http://creativecommons.org/licenses/by-nc/3.0) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

N+ 캐소드로부터 채널을 통해 주입되는 전자와 P+ 애노 드에서 주입된 홀이 N 드리프트 영역에 축적되어 전도 도향상이 가능하다 [4-6].

SITH는 높은 스위칭 속도와 우수한 dv/dt, di/dt 등 급을 가지고 있으며, 일반적으로 양의 게이트 전압  $V_G$ 을 인가하여 turn-on 시킬 수 있으며, 음의 전압을 인가하여 turn-off 시키게 된다. 충분한 크기의 게이트 전압  $(V_G < 0)$ 이 가해지면 공핍 영역이 인접 p+ 영역의 공핍층과의 전위장벽 상황에 따라 전류가 저감되고 turn-off가 가능하게 된다 [7].

SITH는 게이트 영역 채널과 기판, 캐소드 영역 등의 농도, 길이, 너비 등의 주요 설계 파라메터들이 MOSFET 보다 많으며, 이에 따라 스위칭이 매우 민감하게 동작하기 때문에 반도체 공정능력이 향상됨에 따라 SITH 소자의 전기적인 특성을 향상시키기 위한 방안들의 확립이 중요하다 [8,9]. 본 연구에서는 SITH소자의 전기적 특성들을 향상시키며, 전압 블로킹 특성을 유지할 수 있도록

<sup>&</sup>lt;sup>2</sup> Department of Electronic Materials Engineering, Kwangwoon University, Seoul 01897, Korea

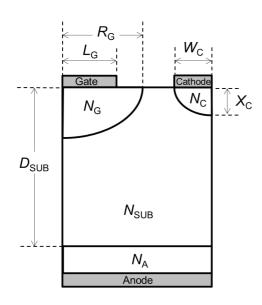

Fig. 1. Cross-sectional schematic diagram of a planar SITH device structure with representative design parameters.

특성 파라미터들을 최적화하는 연구를 수행하였다.

## 2. 실험 방법

표 1은 본 연구에서 수행한 SITH 소자의 설계 및 공정파라미터를 나타내고 있다. 전압 블로킹에 가장 중요기판 depth는 190~230 µm를 기준으로 설계하였고, 각영역의 도핑농도를 변화시키며 설계를 수행하였다. SITH

Table 1. Design parameter for Si-based SITH.

|                  | Symbol / Meaning                            | Unit             | Value                |

|------------------|---------------------------------------------|------------------|----------------------|

| $N_{ m SUB}$     | Substrate doping (n)                        | cm <sup>-3</sup> | 1~4×10 <sup>13</sup> |

| $D_{ m SUB}$     | Substrate depth                             | μm               | 190~230              |

| $N_{\rm C}$      | Doping concentration of cathode region (n+) | cm <sup>-3</sup> | 1×10 <sup>20</sup>   |

| $W_{\rm C}$      | Width of cathode region                     | μm               | 7                    |

| $x_{\rm C}$      | Depth of cathode region                     | μm               | 10                   |

| $L_{\mathrm{G}}$ | Length of gate (half)                       | μm               | 2                    |

| $N_{ m G}$       | Doping of gate region (p+)                  | cm <sup>-3</sup> | 1×10 <sup>20</sup>   |

| $r_{ m G}$       | Radius of gate contact region               | μm               | 3                    |

| $N_{\rm A}$      | Concentration of anode region (p)           | cm <sup>-3</sup> | 1×10 <sup>20</sup>   |

는 전력소자로서 온 상태에는 전력소모가 적으면서 고 전류를 도통시킬 수 있어야 한다며, 스위칭 시에 전력소 모를 줄이기 위해 스위칭 시간이 짧아야 하고, 고전압 인가 시 발생하는 열과 전계로 인하여 애노드와 캐소드 간의 단락이 발생되지 않고 오프상태 동작 시 고내압에 견딜 수 있도록 항복전압 특성이 높아야 한다. 그림 1은 기본적인 SITH구조를 보여주고 있다.

#### 3. 결과 및 고찰

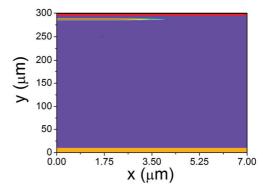

그림 2는 설계된 유효영역의 단면을 보여주며, anode 와 cathode 사이의 캐리어들은 전류흐름이 제한된 상태에서 anode전압이 증가되면서 채널영역의 전위장벽 높이가 낮아지는 static induction현상이 발생함을 알 수있다.

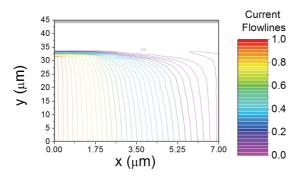

소자 항복 시 전류 흐름에서 알 수 있듯이. 항복은 그림 3에서와 같이 게이트 영역에서 일어나고 게이트 영역과 기판 간에 전계에 큰 영향을 받는다. 따라서 게이트와 기판과의 전계를 줄여 목표로 하는 내전압소자를 구현할 수 있다. 본 연구에서는 기판의 전계를 조절하기 위하여 기판 농도( $N_{SUB}$ )를  $1\times10^{13}$  cm<sup>-3</sup>에서  $9\times10^{13}$  cm<sup>-3</sup>까지 변화하면서 특성을 분석하였다.

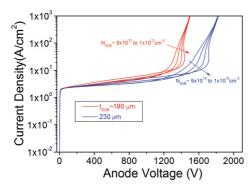

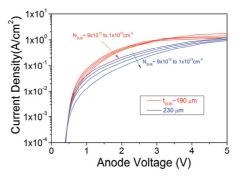

그림 4는 기판의 두께와 농도에 따른 소자의 항복 특성이다. 기판의 두께가 190 μm일 때, 기판의 농도가 1×10<sup>13</sup> cm<sup>-3</sup>에서 9×10<sup>13</sup> cm<sup>-3</sup>까지 증가함에 따라서 항복전압의 변화폭은 ~1,300 V를 기준으로 약 100 V 전후의 margin을 가지고 변화한다. 즉, 기판 농도의 변화를 이용하면 항복전압을 조절하는 데에 한계가 있으므

**Fig. 2.** Simulated structure of a planar SITH device showing charrier distributions.

Fig. 3. Current flow lines at device break down of SITH.

Fig. 4. Breakdown characteristics of SITs for different substrate thickness and doping concentration values.

로 목표로 하는 1,700 V급의 소자를 달성하기 위해서는 기판의 두께를 증가시켜야 한다. 기판의 두께를  $230 \text{ }\mu\text{m}$ 으로 증가시켰을 때, 농도가  $9\times10^{13} \text{ cm}^{-3}$ 에서  $1\times10^{13} \text{ cm}^{-3}$ 까지 변화함에 따라 항복전압은 1,700 V까지 증가함을 알 수 있다.

오프 상태일 때 SITH의 동작은 single channel double gate JFET 또는 MESFET과 유사하나 채널에서의 전위 분포의 조절로 채널의 공핍화에 따른 전류제한이 발생되며, off 상태의 경우 anode에서 cathode로 전류가 흐를 때 채널영역과 N 드리프트 영역이 모두 공핍화 되기 때문에 punch-through로 동작한다.

그림 5는 기판의 두께 및 농도에 따른 순방향 전압 강하 특성을 보여준다. 기판의 두께가 40  $\mu$ m 이상 추가 증가하였을 경우, 순방향 전압 강하 특성은 저전압 영역에서는 다소 열화 되는 특성을 보이고 있으나 소자가 완전히온-상태(on-state)에 이르러서는 기판 두께가 190  $\mu$ m인경우와 230  $\mu$ m인 경우 각각 비교하여 전류밀도 차이가 1  $\Delta$ /cm² 이내로 매우 적음을 알 수 있다.

SITH의 요구 성능들은 상대적인 trade-off 관계에

Fig. 5. Forward I-V Characteristics of SITH devices.

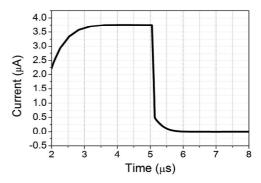

Fig. 6. Transient switching characteristics of a SITH device.

있게 되며, 채널영역의 폭이 넓을수록 채널영역의 병목현상이 완화되어 온 상태 전압강하가 낮아지지만 채널 영역의 전위장벽의 높이의 감소로 인하여 항복전압이 낮아질 수 있다. 온 상태일 때 anode에서 N-drift 영역으로 주입되는 홀은 전도도 변조 효과를 유도하여 저항을 낮추어 온 상태 전력소모를 줄일 수 있지만, trun-off시에는 주입된 홀이 N 드리프트 영역에 축적되어 이들이 재결합 되거나 게이트 전극으로 빠져나가는 시간만큼 turn-off 시간을 증가시켜 스위칭 손실이 증가하게 된다.

그림 6은 최적화된 1,700 V급 SITH 소자의 스위칭 특성을 나타내고 있다. 음(-)의 게이트 전압에 의해서 turn-off 되며, 충분한 게이트 전압과 함께 형성된 depletion 영역은 점차적으로 인접 게이트 영역으로 확장되게 된다. 채널 안에는 전위 장벽이 형성되면서 채널은 좁아지고 과잉 캐리어는 제거된다. 게이트 전압이 충분히 커지면 공핍 영역은 인접 채널로부터의 공핍영역과 맞닿게 되고 결국채널의 전자 전류는 흐르지 못하면서 turn-off가 일어나게 됨을 알 수 있다.

온 상태 시 최대전류가 클수록 소자의 열적파괴가 조 기에 일어나게 되므로 스위칭 시간과 shortcircuit capability를 향상시키기 위해 carrier life time을 조절하는 것이 가능하나, N 드리프트 영역의 축적 전하량이 감소하여 전도도 변조효과가 약해져 온 상태 전압강하가 증가하게 된다.

전자 전류의 흐름에도 불구하고 정공전류는 계속하여 베이스에 남아있던 전류 때문에 흐르면서 감소하게 된다. 턴-오프 스위칭 시간은 초기 온-상태의 전류가 1/10로 줄어드는데 걸리는 시간으로 정의할 수 있으며, 본 시뮬레이션에서 사용된 파라미터들에 의한 최적화된 구조는 0.258 µs의 turn-off 스위칭 시간을 보임을 알 수 있다.

### 4. 결 론

본 논문에서는 대용량 파워 스위칭 소자로 사용되는 1,700 V급 SKTH의 구조와 공정파라메터를 고려한 최적화 설계를 수행하여 전기적인 특성을 분석하였다. SITH 설계에서의 많은 고려사항 중에서 가장 중요한 전기적 특성인 온 상태 전압강하와 항복전압, 그리고 블로킹 이득과의관계를 분석하고 고찰한 결과, SITH의 전기적 특성들은서로 트레이드오프 관계를 가지고 있기 때문에 최적화 설계가 중요하며, 기판 두께 230  $\mu$ m 기준으로  $1\times10^{13}$  cm<sup>-3</sup>판 농도를 기반으로 최적화 구조를 도출하였고 turn-off스위칭 시간을 0.26  $\mu$ s 이하의 구현하였다.

#### 감사의 글

본 논문은 한국연구재단(과제번호: NRF - 2012K1A3 A7A03052292, 2015K1A3A1A59074209)의 지원을 받아 연구되었습니다.

#### **REFERENCES**

- [1] H. Onosea, Y. Kobayashib, and J. Onukic, *Solid-State Electronics*, **129**, 200 (2017). [DOI: https://doi.org/10.1016/j.sse.2016.11.004]

- [2] H. Li and S. Li, J. Semicond., 31, 124003 (2010). [DOI: https://doi.org/10.1088/1674-4926/31/12/124003]

- [3] W. Chen, F. So, and J. Guo, J. Appl. Phys., 116, 044505 (2014). [DOI: http://dx.doi.org/10.1063/1.4891231]

- [4] H. R. Li and S. Y. Li, *IEEE Trans. Electron Dev.*, 58, 1149 (2011). [DOI: http://dx.doi.org/10.1109/TED.2010.2103363]

- [5] B. J. Baliga, *IEEE Trans. Electron Dev.*, 29, 1560 (1980).[DOI: http://dx.doi.org/10.1109/T-ED.1982.20915]

- [6] Y. S. Wang, R. Wu, C. J. Liu, and Z. Wang, Semicond. Sci. Technol., 23, 152 (2008). [DOI: http://dx.doi.org/10.1088/ 0268-1242/23/2/025005]

- [7] B. J. Baliga, M. S. Adler, P. V. Gray, R. P. Love, and N. Zommer, *IEEE Trans. Electron Dev.*, 31, 683 (1984). [DOI: http://dx.doi.org/10.1109/IEDM.1982.190269]

- [8] T. Trajkovic, F. Udrea, G.A.J. Amaratunga, W. I. Milne, S.S.M. Chan, P. R. Waind, J. Thomson, and D. E. Crees, *Int. J. Electron.*, 86, 1153 (1999). [DOI: http://dx.doi.org/10.1080/002072199132716]

- [9] B. Kim, K. C. Ko, and E. Hotta, *IEEE Trans. Plasma Sci.*, 39, 901 (2011). [DOI: http://dx.doi.org/10.1109/TPS.2010.2099242]