J. Korean Inst. Electr. Electron. Mater. Eng.

Vol. 30, No. 7, pp. 413-416 July 2017

DOI: https://doi.org/10.4313/JKEM.2017.30.7.413

ISSN 1226-7945(Print), 2288-3258(Online)

# PMMA 보호막을 이용한 용액 공정 기반의 인듐-이티륨-산화물 트랜지스터에 관한 연구

김한상<sup>1</sup>, 김성진<sup>1,2,a</sup>

<sup>1</sup> 충북대학교 전자정보대학 <sup>2</sup> 충북대학교 컴퓨터정보통신연구소

# Study on Solution Processed Indium-Yttrium-Oxide Thin-Film Transistors Using Poly (Methyl Methacrylate) Passivation Layer

Han-Sang Kim1 and Sung-Jin Kim1,2,a

<sup>1</sup> College of Electrical and Computer Engineering, Chungbuk National University, Cheongju 28644, Korea <sup>2</sup> Institute for Computer and Information Communication, Chungbuk National University, Cheongju 28644, Korea

(Received February 22, 2017; Revised April 12, 2017; Accepted April 23, 2017)

**Abstract:** We investigated solution-processed indium-yttrium-oxide (IYO) TFTs using apoly (methyl methacrylate) (PMMA) passivation layer. The IYO semiconductor solution was prepared with 0.1 M indium nitrate hydrate and 0.1 M yttrium acetate dehydrate as precursor solutions. The solution-processed IYO TFTs showed good performance: field-effect mobility of  $13.13 \text{ cm}^2/\text{Vs}$ , a threshold voltage of 8.2 V, a subthreshold slope of 0.93 V/dec, and a current on-to-off ratio of  $7.2 \times 10^6$ . Moreover, the PMMA passivation layers used to protectthe IYO active layer of the TFTs, did so without deteriorating their performance under ambient conditions; their operational stability and electrical properties also improved by decreasing leakage current.

Keywords: Oxide semiconductor, IYO TFTs, PMMA passivation

#### 1. 서 론

최근 비정질 산화물 반도체가 우수한 특성과 높은 광투과율로 기존의 실리콘 기반 반도체를 대체할 수 있는 재료로 주목을 받고 있다. 산화물 반도체는 기존의 실리콘 반도체에 비해 제작 과정이 비교적 간단해 저렴한 가격과 높은 전하이동도, 신뢰성 등 우수한 전기적 특성을보이는 장점을 가지고 있기 때문이다 [1-7]. 특히 높은 전하 이동도를 요구하는 active matrix display의 backplane

a. Corresponding author; ksj@cbnu.ac.kr

Copyright ©2017 KIEEME. All rights reserved. This is an Open-Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License (http://creativecommons.org/licenses/by-nc/3.0) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

소자를 활용 가능할 뿐 아니라 밴드갭이 크기 때문에 투명 전자소자로서의 적용이 가능하다는 장점이 있다.

하지만 이런 장점을 가지고 있는 산화물 반도체는 공기 중의 수분, 산소와 같은 외부 환경에 민감한 반응을 보이는 단점이 보고된 바 있다. 외부 환경에 노출될 경우 박막의 특성이 변해 전기적으로 불안정한 상태를 야기할 수 있다 [8]. 이러한 문제는 산화물의 공정 변수, 외부 환경으로부터 보호될 수 있도록 passivation 공정을 통해 해결될 수 있다 [9].

본 논문에서는 용액 공정으로 연구되는 산화물 반도체 중 indium-yttrium-oxide (IYO) 반도체 박막을 제작하 였으며, 제작된 박막에 poly (methyl methacrylate) (PMMA) 물질을 스핀 코팅을 통해 passivation 공정을 진행하였다. 그 후 표면 보호 효과를 평가하기 위해 hysteresis 및 시간에 따른 전류 안정성에 관한 연구를 진행하였다.

# 2. 실험 방법

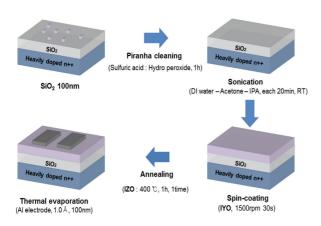

그림 1은 이번 연구에서 제작된 비정질 산화물인 IYO 기반의 top-contact bottom-gate (TC-BG) 구조인 thin-film-transistors (TFTs)의 제작 과정을 나타낸다. 기판이자 게이트 전극으로 두께가 100 nm인 heavily doped n++ Si 웨이퍼를 사용하였고, 절연막으로는 두 께가 100 nm인 SiO<sub>2</sub>를 사용하였다. 그 후 piranha cleaning과 표준 세정 공정을 통해 절연막 위의 오염물질들을 제거하였다.

용액 공정 기반의 IYO TFTs를 제작하기 위해 용질로 In(NO<sub>3</sub>)<sub>3</sub>•xH<sub>2</sub>O], Y(NO<sub>3</sub>)•4H<sub>2</sub>O를 용매로 2-methoxyethanol을 사용하였다. 용매와 용질을 혼합해 각각 0.1 M의 indium, zinc 용액을 만들었으며 안정제로써 acetylacetone을 두 용액에 첨가하였고, indium 용액에는 NH<sub>3</sub>을 촉매로써 첨가하였다.

그 후 온도를 일정하게 유지하기 위해 물중탕으로 60℃의 온도에서 stirring을 1시간 동안 진행하여 용액을 제작하였다. 이후 indium, yttrium 용액을 6:4 비율로 혼합하여 27℃의 온도로 2시간 동안 stirring을 진행하였다. 그리고 1,500 rpm의 속도로 30초 동안 spincoating을 진행해 30 nm 두께의 IYO 박막을 제작하였다. 이후 남아있는 용매를 증발시키기 위해 400℃의 hot plate에서 4시간 동안 annealing을 실시하였다.

그 후 2,000 µm의 channel length 값과 200 µm의

Fig. 1. Procedures used for the fabrication of IYO TFTs.

channel width 값을 갖는 channel을 생성하였고, top-contact 소스(source), 드레인(drain) 전극을 제작하기 위해 금속 증착기(metal evaporator)를 이용하여 Al을 100 nm 두께로 10<sup>-6</sup> torr의 진공도에서 증착하였다. 최종적으로, 외부환경으로 인한 소자의 성능 저하를 방지하고자 보호막을 형성하기 위해 toluene에 PMMA를 용해시켜 spin-coating을 진행하였으며, 진공 오븐에서 100°C의 온도에서 2시간 동안 annealing을 실시하여 30 nm두께의 PMMA 막을 형성하였다. 이 후 전자소자 파라미터 분석 장비인 Agilent 1500 B를 사용하여 소자의 전기적 특성을 상온의 공기 중에서 측정하였다.

#### 3. 결과 및 고찰

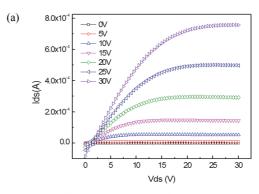

그림 2(a)는 제작한 소자를 output curve 측면에서 의 특성을 확인한 결과이다. 제작한 소자는 공기 중에서 안정적인 트랜지스터 특성이 보였다. Gate voltage가

**Fig. 2.** (a) Drain current versus voltage for the solution-processed IYO TFTs at  $V_{gs} = 5$  V intervals (W/L: 2,000  $\mu$ m/200  $\mu$ m) and (b) transfer characteristics of a solution-processed IYO TFTs with  $V_{ds} = +30$  V (Inset: AFM topographies of IYO film with a rms surface roughness of 1.4 nm).

Table. 1. Summary of the electrical characteristics of IYO TFTs.

| Mobility (cm <sup>2</sup> /V <sub>s</sub> ) | $I_{\rm on}/I_{\rm off}$ | $V_{\text{th}}\ (V)$ | S/S<br>(V/decade) |

|---------------------------------------------|--------------------------|----------------------|-------------------|

| 13.13                                       | $7.2 \times 10^{6}$      | 8.2                  | 0.93              |

30 V일 때 saturation 영역에서 drain current가 8.0 ×  $10^{-4}$  A인 것을 확인할 수 있었다. 그림 2(b)는 제작한 소자의 transfer curve 측면에서의 성능이다. Drain voltage가 30 V일 때, transfer curve를 분석해 파라 미터를 추출한 결과를 표 1에 나타내었다. 소자의 중요 파라미터는 mobility  $13.13~{\rm cm}^2/{\rm Vs}$ , current on/off ratio는  $7.2 \times 10^6$ , 문턱전압은  $8.2~{\rm Vz}$  확인되었다. 그림에서 추가된 삽화는 표면의 상태를 원자간력 현미경 (atomic force microscopy, AFM)을 통해 측정한 결과이며  $2 \times 2~{\rm µm}$  사이즈로 스캔하였을 때 전체적으로 그레인의 사이즈가 비슷하고 root-mean-square (RMS) 값이  $1.4~{\rm rm}$ 인 것을 확인할 수 있었다.

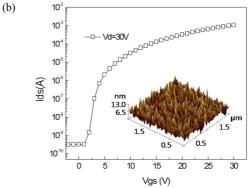

그림 3(a)는 소자에 passivation 공정이 이루어지지 않은 상태로 gate 전극에 바이어스 전압을 지속적으로 인가한 뒤 30번 반복 측정했을 때의 output curve이다. 게이트 전압을 지속적으로 가해줌에 따라 saturation 전류가 유지되지 못하고 떨어지는 모습을 확인할 수 있다. 또한 그림 3(b)는 소자를 공기 중에서 5일 간 노출했을때의 current on/off ratio를 확인한 결과이다. 일반적으로 외부 환경에 취약한 산화물 트랜지스터의 특성으로 인하여 오랜 시간 외부에 노출되었을 때 트랜지스터의 성능이 현격히 낮아지는 것을 확인할 수 있었다.

이것은 게이트 전압과 외부 환경으로 인한 구동 안정성의 감소는 소자 제작을 위한 용액공정 이후, pristine 상태에서의 남은 잔류용매가 소자의 특성에 영향을 주었던 것을 공기 중 보관 시 노출에 의해 산소, 수분의 흡착으로 문턱전압 이동 및 누설전류의 감소에 의한 것으로 추정되므로 유/무기물 형태의 보호막 공정이 반드시 필요함을 알 수 있다. 따라서 본 논문에서 제안한 바와 같이 PMMA 보호막을 통해 채널 표면이 산소 및 수분의 영향을 받아 성능이 저하되는 현상을 방지하며, 채널 계면의 표면거칠기(roughness)로 인해 발생하는 트랩 전하(trap charge) 현상을 PMMA 코팅으로 완화시켜 누설전류 및 히스테리시스를 개선하여 소자의 전기적 신뢰성 평가 시 특성이 안정적인 구동을 예측할 수있었다.

**Fig. 3.** Electrical and environmental stability of IYO TFTs of (a) output curve distortion and (b) time-dependent current decay.

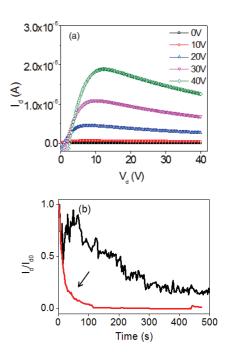

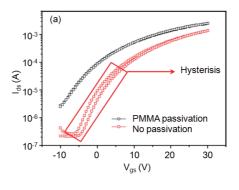

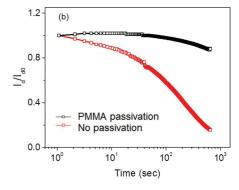

**Fig. 4.** (a) Transfer curve of IYO TFTs through double sweep and (b) retention stability test of the electrical stress states of IYO TFTs under constant bias.

그림 4(a)는 제작한 소자의 단일 측정이 아닌 왕복 측정을 통해서 소자의 hysteresis 발생 여부에 대해 조사한결과이다. 그림에서 알 수 있듯이 passivation을 하지않은 소자는  $-10\sim10~V$  사이에서 hysteresis 현상이 발생하지만 PMMA 보호막 공정을 한 소자는 hysteresis 현상이 거의 발생하지 않는 것을 확인할 수 있다. 그림 4(b)는 소자의 시간 경과에 따른  $I_{ds}$  전류 감소 및 안정성테스트를 진행한 결과이다. PMMA 보호막 공정을 하지않은 소자는 시간에 따라 gate 전압( $V_{gs} = +30~V$ )을 걸어줌에 따라 20% 수준까지 current가 떨어지는 것을 볼 수있었지만, 보호막 공정을 한 소자는 80%의 current 유지율을 보임으로써 전기적 바이어스에 대한 내구성이 향상되고 안정적인 구동을 확인할 수 있었다.

# 4. 결 론

본 논문에서는 산화물 반도체의 효과적인 표면 보호를 위해서 PMMA 보호막을 이용한 용액 공정 기반의 IYO 트랜지스터를 제작하였으며, 표면 보호 효과를 확인하기 위해 hysteresis와 외부 환경에 노출되었을 때의 소자의 변화, 전기적 바이어스에 따른 소자의 변화를확인하였다. 결과적으로 PMMA 보호막 공정을 한 소자가 전기적 신뢰성이 개선되었고, 시간에 따른 drain current의 성능 저하에 대한 내구성을 갖는 것을 확인할 수 있었다. 이 결과로 향후 빠른 이동도를 요구하는 대면적 디스플레이, 투명 전자 소자의 보호막 공정에서의 핵심 기술로 응용될 수 있을 것으로 판단한다.

## 감사의 글

This research was supported by Basic Science Research Program through the National Research Foundation of Korea (NRF) funded by the Ministry of Education (2017R1D1A3B03029782) and the Human Resources

Development of the Korea Institute of Energy Technology Evaluation and Planning (KETEP) grant funded by the Korea government Ministry of Trade, industry & Energy (No. 20144030200450). This research was also supported by the MSIP (Ministry of Science, ICT and Future Planning), Korea, under the ITRC (Information Technology Research Center) support program (IITP-2017-2015-0-00448) supervised by the IITP (Institute for Information & communications Technology Promotion).

#### **REFERENCES**

- [1] K. Nomura, H. Ohta, K. Ueda, T. Kamiya, M. Hirano, and H. Hosono, *Science*, **300**, 1269 (2003). [DOI: https://doi.org/10.1126/science.1083212]

- [2] H. Yabuta, M. Sano, K. Abe, T. Aiba, T. Den, H. Kumomi, K. Nomura, T. Kamiya, and H. Hosono, *Appl. Phys. Lett.*, 89, 112123 (2006). [DOI: https://doi.org/10.1063/1.2353811]

- [3] C. G. Van de Walle, Phys. Rev. Lett., 85, 1012 (2000). [DOI: https://doi.org/10.1103/PhysRevLett.85.1012]

- [4] K. Nomura, H. Ohta, A. Takagi, T. Kamiya, M. Hirano, and H. Hosono, *Nature*, 432, 488 (2004). [DOI: https://doi.org/ 10.1038/nature03090]

- [5] K. B. Park, J. B. Seon, G. H. Kim, M. Yang, B. Koo, H. J. Kim, M. K. Ryu, and S. Y. Lee, *IEEE Electron Device Lett.*, 31, 311 (2010). [DOI: https://doi.org/10.1109/LED.2010.2040130]

- [6] W. H. Jeong, G. H. Kim, H. S. Shin, B. D. Ahn, H. J. Kim, M. K. Ryu, K. B. Park, J. B. Seon, and S. Y. Lee, *Appl. Phys. Lett.*, 96, 093503 (2010). [DOI: https://doi.org/10.1063/1.3340943]

- [7] Y. S. Rim, H. S. Lim, and H. J. Kim, ACS Appl. Mater. Interfaces, 5, 3565 (2013). [DOI: https://doi.org/10.1021/am30 2722h]

- [8] P. C. Chang, Z. Fan, C. J. Chien, D. Stichtenoth, C. Ronning, and J. G. Lu, *Appl. Phys. Lett.*, 89, 133113 (2006). [DOI: https://doi.org/10.1063/1.2357013]

- [9] S. H. Song, W. K. Hong, S. S. Kwon, and T. H. Lee, *Appl. Phys. Lett.*, **92**, 263109 (2008). [DOI: https://doi.org/10.1063/1.2955512]