논문 2017-54-2-6

# C-DAC Array내 선형성을 향상시킨 10비트 CMOS SAR ADC 설계

(Design of a 10-bit SAR ADC with Enhancement of Linearity On C-DAC Array)

김 정 흠\*, 이 상 헌\*\*, 윤 광 섭\*\*\*

(Jeong Heum Kim, Sang Heon Lee, and Kwang Sub Yoon<sup>©</sup>)

요 약

본 논문에서는 생체 신호 처리를 위한 중간 속도를 갖는 A/D 변환기 설계를 위하여 1.8V 전원의 CMOS SAR(Successive Approximation Register) A/D 변환기를 설계하였다. 본 논문에서 C-DAC Array의 MSB단을 4분할하여 선형성을 향상시킨 10 비트 SAR A/D 변환기 설계를 제안한다. 아날로그 입력이 인가되는 MSB 단의 전하가 충전되는 시간을 확보하여 선형성을 높였다. MSB단이 아날로그 입력을 샘플링하는 블록이기 때문에 초기 값을 보다 정교하게 받아들이는 원리를 통해 선형성을 확보하였다. C-DAC에서 Split 커패시터를 사용하여 면적을 최소화하고, 전력을 감소시켰다. 제안된 SAR A/D 변환기는 0.18um CMOS 공정을 이용하여 설계하였고, 공급 전압 1.8V에서 4MS/s의 변환속도를 가지며, 7.5비트의 ENOB(Effective Number of Bit)이 측정되었다. 850×650um²의 면적, 총 전력소모는 123.105uW이고, 170.016fJ/step의 FOM(Figure of Merit)을 확인할 수 있다.

### Abstract

In this paper, CMOS SAR A/D converter 1.8V supply for the design of an A/D converter having an middle speed for the biological signal processing was designed. This paper proposes design of a 10-bit SAR Analog to Digital Converter improving linearity driven by MSB node of C-DAC array divided into 4 equal parts. It enhances linearity property, by retaining the analog input signal charging time at MSB node. Because MSB node samples analog input, it enhances resolution through getting initial input signal precisely. By using split capacitor on C-DAC array, it reduced chip size and power dissipation. The Proposed SAR A/D Converter is fabricated in 0.18um CMOS and measured 7.5 bits of ENOB at sampling frequency 4MS/s and power supply of 1.8V. It occupies a core area of 850×650um² and consumes 123.105uW. Therefore it results in 170.016fJ/step of FOM(Figure of Merit).

Keywords: SAR ADC, Linearity, C-DAC, ADC, bio-signal

Received; June 3, 2016 Revised; January 17, 2017

Accepted; January 19, 2017

#### I. 서 론

현대 사회가 점차 복지와 편의성이 강조됨에 따라, 저 전력 집적회로 기술에 대한 연구가 활발하게 이루어 지고 있다. 체내 삽입용 생체신호처리 시스템의 경우, 저전력, 적당한 해상도(8-12비트)와 중간 속도의 샘플 링 주기에서 동작하는 것이 일반적이다.

SAR(Successive Approximation Register) A/D변환 기는 정적전력을 소모하지 않아서 저전력의 중간 해상

<sup>\*</sup> 정회원, \*\* 학생회원, \*\*\* 평생회원, 인하대학교

<sup>(</sup>Department of Electronic Engineering, Inha University)

© Corresponding Author (E-mail: ksyoon@inha.ac.kr)

<sup>※</sup> 이 논문은 2010년도 정부(교육부)의 재원으로 한국 연구재단의 지원을 받아 수행된 기초연구사업임 (2010-0020163)

<sup>※</sup> 이 논문은 2015년도 정부(교육부)의 재원으로 한국 연구재단의 지원을 받아 수행된 기초연구사업임 (2015R1B1A1A01058603)

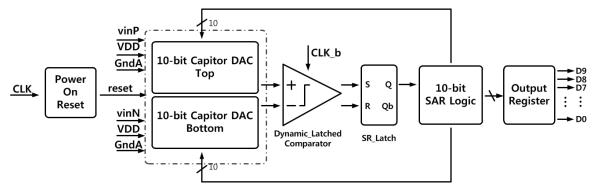

그림 1. 제안된 MSB단을 4분할한 차동 입력 10비트 SAR ADC 블록도

Fig. 1. The block diagram of the proposed Differential Input 10bit SAR ADC dividing MSB node into 4 parts.

도, 동작속도 설계에 적합하다. 생체신호 처리의 정확성을 위해 샘플링 입력 값을 오차 없이 변환해야 하므로 C-DAC의 정확도를 높이는 방법이 사용되거나<sup>[1~2]</sup> 새로운 형태의 스위치를 도입하여 정확성을 증가시키는 방식을 이용하고 있다<sup>[3~4]</sup>. 제안하는 회로에서는 C-DAC Array에서 MSB단을 4분할하여 누설전류량을 줄이고 샘플링 스위치의 선형성을 증가시켰고 Split Capacitor를 사용하여 면적을 줄이고 전력효율을 향상시켰다<sup>[5]</sup>.

본 논문의 Ⅱ장에서는 본 연구에서 제안하는 10비트 SAR ADC의 구조 및 동작 원리에 대해 설명하고, Ⅲ장에서는 전체회로의 모의실험 결과 및 레이아웃, 다른 회로와의 성능비교를 보이고, Ⅳ장에서는 제안된 논문의 결론을 맺기로 하겠다.

# Ⅱ. 제안하는 SAR ADC 설계

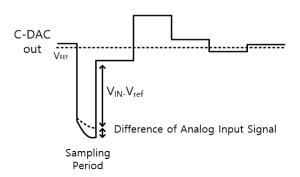

일반적인 SAR ADC의 경우 Reset 신호에 '1'이 입력되었을 때 아날로그 입력( $V_{IN}$ ) 값이 샘플링되고, 근사화가 진행된다. 다른 하나는 제안된 회로에서 사용된동작 원리와 같이 Reset 신호에 '1'이 인가되면  $V_{REF}$ 를 샘플링하고 다음 CLK 신호가 인가되기 전에  $V_{IN}$  값을 샘플링하게 된다. 이때  $V_{IN}$  값은 MSB 단에만 입력되어 샘플링되기 때문에 MSB 단의 정확도가 해상도에 큰 영향을 끼치게 된다. 만약 초기에 읽는 데이터가정확하지 않다면 정확한 데이터를 도출해내기 힘들 수밖에 없다.

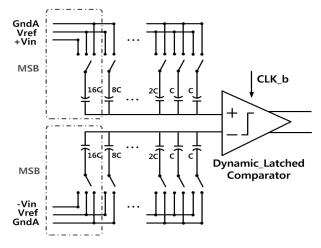

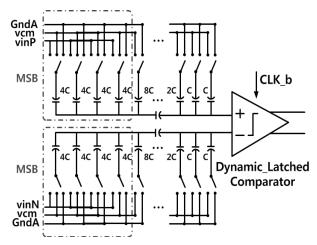

이러한 정확도를 개선하기 위해서 사용한 기법은 MSB 단을 같은 크기의 커패시터 양으로 4분할하는 것이다. 그림 2은 아이디어를 적용하지 않은 일반적인 C-DAC array 회로의 모습이고, 그림 3은 제안된 MSB 단이 적용된 C-DAC array의 블록다이어그램이다.  $16C_{IJ}$

의 커패시터 양을 갖는 MSB단을  $4C_U$ 의 같은 크기로 나누어 스위치를 4배 더 증가시켰다.  $16\,C_U$ 의 값이 charging

그림 2. 일반적인 SAR ADC의 C-DAC Array 구조 Fig. 2. The Structure of conventional SAR ADC's C-DAC Array.

그림 3. MSB단을 4분할한 SAR ADC의 C-DAC Array 구조 Fig. 3. The Structure of Dividing MSB node into 4 parts SAR ADC's C-DAC Array.

되는 속도보다  $4C_U$ 의 크기로 동시에 4개의 노드에서 한번에 charging 되기 때문에 변환 속도에 비교적 영향을 덜 받는 결과를 얻어낼 수가 있다. 커패시터와 스위치를 4분할시 스위치 크기의 증가를 통해 저항의 감소 및 공정오차를 줄일 수 있어 변환기의 오차를 줄일 수 있다.

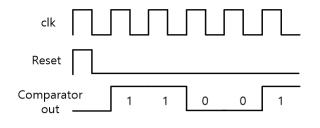

그림 4에서 확인할 수 있듯이 리셋 신호가 입력되고 다음 클럭 신호가 인가되기 전에 아날로그 입력 신호가 인가되는데 이 때 아날로그 입력 신호가 충전되는 단이 최상위 비트 단이다. 따라서 이 때 아날로그 값을 제대 로 입력 받지 못하면 제대로 된 값을 복원하기 어렵게 된다. 기존의 최상위 비트에서 사용한 같은 크기의 스 위치를 3개 더 사용하여 최상위 비트를 구성하였다. 스 위치를 3개 더 사용하여 최상위 비트에서 충전되는 속 도를 보다 빠르게 하여 클럭 속도가 일정 이상 빨라졌 을 때 발생할 수 있는 아날로그 입력신호의 오차를 감 소시킬 수 있다. 스위치를 1개 사용하면 4개를 사용했 을 때보다 아날로그 입력을 받는 속도가 느려서 원하는 만큼 값을 받기도 전에 다음 클럭으로 넘어가게 되고 원하는 값을 얻지 못하게 된다. 점선으로 표시된 부분 보다 실선으로 표시된 값이 실제로 처음에 받으려고 했 던 아날로그 입력 값과 유사하여 오차를 줄이게 되고, 전체 변환기의 유효비트수를 증가시키는 효과를 가져 올 수 있다.

그림 4. 기존의 회로와 제안된 회로의 아날로그 입력 신호 의 타이밍도

Fig. 4. The Timing Diagram of Analog Input Signal at Conventional Circuit and Proposed Circuit.

표 1은 MSB 커패시터의 3가지 분할방식에 따른 변환기의 이득 오차와, 오프셋 오차를 보여준다. 한 개의 16C, 두 개의 8C, 그리고 4개의 4C로 분할한 방식을 검증하였다. MSB커패시터를 4분할 방식을 적용하여 오프셋 오차가 감소하였다.

표 1. MSB 커패시터 방식에 대한 오프셋, 이득 오차 비교

Table 1. Comparison of offset and gain error of three different MSB capacitors.

|              | MSB 16C      | MSB 8C X2    | MSB 4C X 4  |

|--------------|--------------|--------------|-------------|

| Offset error | 999.066m LSB | 999.056m LSB | 998.541mLSB |

| Gain error   | -1.998LSB    | -1.998LSB    | -1.998LSB   |

C-DAC Array의 크기를 Split Capacitor를 사용함으로써  $2^{N+1}$ 의 개수(더미 커패시터 개수 제외)에서  $(2^{\frac{N}{2}+1}-1)\times 2$ 의 개수만큼 커패시터의 양을 줄여서 면적을 현저하게 줄일 수 있었다. 위의 식에 10비트의 C-DAC array의 개수의 차이를 비교해보면 2048개에서 62개로 감소하여 거의  $\frac{3}{100}$  배만큼 감소하는 큰 효과를 나타내었다.

# Ⅲ. 측정 결과

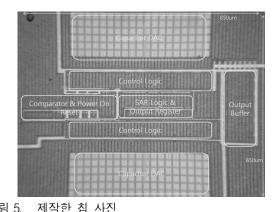

제안된 SAR ADC는 1 Poly 6 Metal의 0.18um CMOS 공정을 사용하여 설계하였다. 그림 5.은 제작한 10비트 SAR ADC의 칩 사진이며, 칩 면적은  $850\mu m$   $\times 650\mu m$ 를 차지한다.

실제로 제안된 회로를 사용한 SAR ADC의 모의실험 시 651.042Hz의 아날로그 정현파를 입력주파수, 800 KS/s의 샘플링 주파수에서 ENOB은 9.27bits의 모의실험 결과를 나타내었고, SFDR은 65.46dB, SNDR은 57.59dB이다.

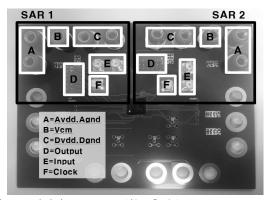

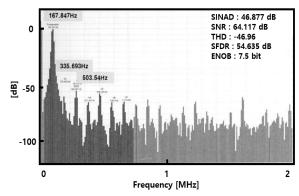

측정 결과는 그림 6과 같은 측정환경에서 측정 되었고, 아날로그 공급전압  $1.8\,V$ , 디지털 공급전압  $1.8\,V$ 에서 동작하고,  $900m\,V$ 의 기준전압  $V_{REF}$ 를 갖고, 아날로그 입력 전압의 범위는  $0\sim1.8\,V$ 의 풀 스케일의 입력 범위에서 동작한다. 측정 시 162.76Hz의 아날로그 정현파를 입력주파수로 사용하였고, 4MS/s의 샘플링주파수를 갖는다. 위의 정현파에 대해 복원된 출력신호의 파형은 그림 7에서 확인할 수 있고, 그림 7에 복원된 출력신호의 FFT스펙트럼 결과를 볼 수 있다. ENOB

그림 5. 제작한 칩 사진 Fig. 5. Fabricated Chip Photograph.

그림 6. 제작된 SAR ADC 성능 측정용 PCB 그림 8. Fig. 6. Performance Verification PCB for Fabricated SAR Fig. 8.

ADC.

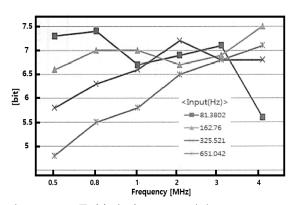

은  $7.5\,bits$ , SNDR은 46.877dB, SFDR은 54.635dB 의 측정결과를 도출하였다. 그림 8에서는 클럭 주파수와 입력 주파수에 따른 ENOB변화를 나타나고 있다. 전력소모는  $132.105\mu\,W$ 를 보였고, FOM(Figure of Merit)은  $170.016f\,J/step$ 로 확인하였다.

## Ⅳ. 결 론

본 논문에서는 생체 신호의 AD 변환을 위한 C-DAC Array내 선형성을 향상시킨 10비트 SAR ADC를 설계하였다. 제안된 SAR ADC는 MSB단을 4분할하여 누설 전류량을 줄이고 샘플링 스위치의 선형성을 증가시켰다. MSB단이 아날로그 입력을 샘플링하는 블록이고 가장 큰 캐패시터값을 가지기 때문에 초기 값을 보다 정교하게 받아들이는 원리를 통해 선형성을 확보하였다. 측정결과는 최대 SNDR은 46.877dB로 7.5 bits의 유효비트수를 나타내었고 소모전류량은 132.105 $\mu$  W로 측정되었다. FOM(Figure of Merit)은 170.016f J/ step

그림 7. FFT 측정 결과(Input: 162.76Hz, Sampling Frequency: 4MHz)

Fig. 7. FFT Measurement Result (Input: 162.76Hz, Sampling Frequency: 4MHz)

그림 8. Clock 주파수에 따른 ENOB 변화 Fig. 8. ENOB Variation at Clock Frequency.

로 확인되었다. 설계는 0.18um CMOS n-well 1폴리 6 메탈 공정을 사용하여 설계되었다.

# **REFERENCES**

- [1] Tsung-Che Lu, Lan-Da Van, Chi-Sheng Lin, Chun-Ming Huang, "A 0.5V 1KS/s 2.5nW 8.52-ENOB 6.8fJ/Conversion-Step SAR ADC for Biomedical Applications," 2011 IEEE CICC, pp. 1-4, San Jose, CA, Sept 2011.

- [2] Sang-Hyun Cho, Chang-Kyo Lee, Jong-Kee Kwon, Seung-Tak Ryu, "A 550-uW 10-b 40-MS/s SAR ADC With Multistep Addition-Only Digital Error Correction," IEEE JSSC, Vol. 46, no. 8, pp. 1881-1892, Aug 2011.

- [3] Chun-Cheng Liu, Soon-Jyh Chang, Guan-Ying Huang, Yin-Zu Lin, "A 0.92mW 10-bit 50-MS/s SAR ADC in 0.13µm CMOS Process," 2009 Symposium on VLSI Circuits, pp. 236-237, Kyoto, Japan, Jun 2009.

- [4] Yung-Hui Chung, Meng-Hsuan Wu, and Hung-

표 2. SAR ADC 성능 비교 (측정 결과) Table2. SAR ADC Performance Comparison (Measurement Results).

| Parameter         | [1]            | [2]          | [3]           | This Work         |

|-------------------|----------------|--------------|---------------|-------------------|

| Architecture      | SAR            | SAR          | SAR           | SAR               |

| CMOS Process      | 0.18 $\mu m$   | 0.13 $\mu m$ | 0.13 $\mu m$  | 0.18 $\mu m$      |

| Resolution(bit)   | 10             | 10           | 10            | 10                |

| Supply Voltage(V) | 0.5            | 1.2          | 1.2           | 1.8               |

| Speed             | 1KS/s          | 40MS/s       | 50MS/s        | 4MS/s             |

| Input Range(Vpp)  | 0.5            | N/A          | N/A           | 1.8               |

| SNDR(dB)          | 53.05          | 50.6         | 52.8          | 46.87             |

| ENOB(bit)         | 8.52           | N/A          | 8.48          | 7.5               |

| Power Dissipation | 2.5 <i>n W</i> | $550 \mu W$  | 920 $\mu$ $W$ | 132.105 $\mu$ $W$ |

| * FOM(fJ/step)    | 6.8            | 50           | 52            | 170.016           |

<sup>\*</sup>FOM(fJ/step) =  $Power/2^{ENOB} \cdot f_S$

- Sung Li "A 12-bit 8.47-fJ/Conversion-Step Capacitor-Swapping SAR ADC in 110-nm CMOS," IEEE Transactions on and systems, Vol. 62, NO.1, Jan 2015.

- [5] Yan Zhu, Chi-Hang Chan, U-Fat Chio, Sai-Weng Sin, Seng-Pan U, Rui Paulo Martins and Franco Maloberti, "Split-SAR ADCs: Improved Linearity With Power and Speed Optimization," IEEE Transactions on VLSI Systems, Vol. 22, NO. 2, Feb 2014.

- [6] Howard Tang, Zhuo Chao Sun, Kin Wai Roy Chew, Liter Siek "A 1.33 uW 8.02-ENOB 100 kS/s Successive Approximation ADC With Supply Reduction Technique for Implantable Retinal Prosthesis," IEEE J. Solid-State Circuits, Vol. 50, NO.4, April 2015.

- [7] Jin-Yi Lin, Chih-Cheng Hsieh, "A 0.3 V 10-bit 1.17f SAR ADC With Merge and Split Switching in 90nm CMOS," IEEE Transactions on and systems, Vol. 62, NO.1, Jan 2015.

- [8] Guan-Ying Huang, Soon-Jyh Chang, Chun-Cheng Liu, Ying-Zu Lin "A 1-μW 10-bit 200-kS/s SAR ADC With a Bypass Window for Biomedical Applications," IEEE J. Solid-State Circuits, Vol. 47, pp. 2783–2795, Nov 2012.

- [9] Y Chen, X. Zhu, T. Hirotaka. "Split capacitor DAC mismatch calibration in successive approximation ADC," J. IEEE CICC, pp. 279–282, San jose, CA, Sept 2009.

- [10] Binhee Kim, Long Yan, Jerald Yoo, Hoi-Jun Yoo, "A 40fJ/c-s 1 V 10 bit SAR ADC with Dual Sampling Capacitive DAC Topology," JSTS, pp. 23-32, Vol. 11, No. 1, Mar 2011.

[11] Shin-Il Lim, Jin Woo Kim, Kwang-Sub Yoon, Sangmin Lee, "A 12-b Asynchronous SAR Type ADC for Bio Signal Detection," JSTS, pp. 108-113, Vol. 13, No. 2, Apr 2013.

## ----- 저 자 소 개 -

김 정 흠(정회원) 2014년 인하대학교 전자공학과 학사 졸업.

2016년 인하대학교 전자공학과 석사 졸업.

<주관심분야: 전자공학, 아날로그 회로설계>

이 상 헌(학생회원)

2015년 인하대학교 전자공학과 학사 졸업.

2017년 인하대학교 전자공학과 석사 졸업 예정.

<주관심분야: 전자공학, 아날로그 회로설계>

윤 광 섭(평생회원)

1981년 인하대학교 전자 공학과 학사 졸업.

1983년 Georgia Institute Inc, Technology 전자 공학과 석사 졸업.

1989년 Georgia Institute Inc, Technology 전자 공학과 박사 졸업.

1984년 3월~1989년 2월 Georgia Institute of Technology Research Assistant.

1989년 3월~1992년 2월 Silicon Systems Inc, Tustin Calif. U.S.A Senior Design Engineer 1992년 3월~현재 인하대학교 전자공학과 교수 <주관심분야: 전자공학, 아날로그 회로설계>