Journal of the Korea Institute of Information and Communication Engineering

한국정보통신학회논문지(J. Korea Inst. Inf. Commun. Eng.) Vol. 21, No. 2: 339~344 Feb. 2017

# Early-late 감지기를 사용한 고속 단일 커패시터 루프필터 위상고정루프

고기영<sup>1</sup> · 최영식<sup>2\*</sup>

# Fast locking single capacitor loop filter PLL with Early-late detector

# Ki-Yeong Ko<sup>1</sup> · Yong-Shig Choi<sup>2\*</sup>

<sup>1</sup>Department of Electronic Engineering, Pukyong National University, Busan 48513, Korea <sup>2\*</sup>Department of Electronic Engineering, Pukyong National University, Busan 48513, Korea

## 요 약

본 논문에서는 Early-late detector, Duty-rate modulator, 그리고 LSI(Lock Status Indicator)를 사용하여 작은 크기와 빠른 위상고정 시간을 갖는 위상고정루프를 제안하였다. 제안된 위상고정루프는 작은 용량을 가진 하나의 커패시터를 사용하게 됨으로써 칩의 크기를 결정하는 루프필터의 크기가 작아지게 되어 크기를 최소화 하였다. 기존의 전하펌프와 달리 2개의 전하펌프를 사용하여 하나의 커패시터를 사용하더라도 2차 루프필터를 사용 한 것과 같은 전압파형을 만들어 줌으로써 위상을 고정시킬 수 있다. 2개의 전하펌프는 UP, DN신호 위상의 빠르기를 감지해주는 Early-late detector와 일정한 비율의 파형을 만들어주는 Duty-rate modulator에 의해 제어된다. LSI회로를 사용함으로써 빠른 위상고정시간을 얻을 수 있다. 제안된 위상고정루프는 1.8V 0.18 μm CMOS 공정을 사용하여 설계하였고, Hspice 시뮬레이션을 통해 회로의 동작을 검증하였다.

#### **ABSTRACT**

A novel structure of phase locked loop (PLL) which has small size and fast locking time with Early-late detector, Duty-rate modulator, and Lock status indicator (LSI) is proposed in this paper. The area of loop filter usually occupying the larger portion of the chip is minimized using a single small capacitor. While the conventional PLL with a single capacitor loop filter cannot work stably, the proposed PLL with two charge pumps works stably because the output voltage waveform of the proposed a single capacitor loop filter is the same as the output voltage waveform of the conventional 2nd-order loop filter. The two charge pumps are controlled by the Early-late detector which detects early-late status of UP and DN signals, and Duty-rate modulator which generates a steady duty-rate signal. Fast locking time is achieved using LSI. It has been simulated and proved by HSPICE in a CMOS 0.18µm 1.8V process.

키워드 : 위상고정루프, 빠른 위상고정시간, 작은 크기의 칩, 싱글 커패시터

Key word: PLL, fast locking time, small size chip, single capacitor

Received 12 August 2016, Revised 12 January 2017, Accepted 30 January 2017

\* Corresponding Author Young-Shig Choi(E-mail:choiys@pknu.ac.kr, Tel: +82-51-629-6222) Department of Electronic Engineering, Pukyong National University, Busan 48513, Korea

Open Access http://doi.org/10.6109/jkiice.2017.21.2.339

print ISSN: 2234-4772 online ISSN: 2288-4165

©This is an Open Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License(http://creativecommons.org/li-censes/by-nc/3.0/) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited. Copyright © The Korea Institute of Information and Communication Engineering.

#### Ⅰ. 서 론

위상고정루프(Phase Locked Loop; PLL)는 각종 무 선 통신 시스템과 고속의 시스템이 필요로 하는 다양한 주파수를 가진 신호와 고속 클록 신호를 만드는 것 등 에 널리 사용되고 있다. 최근 통신 장비의 고속화 및 고 주파수화 추세를 만족시키기 위해 빠른 위상 고정시간 (locking time), 낮은 위상잡음과 좋은 지터 특성을 실현 하기 위한 연구들이 활발하게 진행되고 있다. 위상고정 루프의 안정된 동작을 위해서는 대역폭이 최소 기준 신 호 주파수 보다 1/10이 되어야 한다[1]. 링 전압제어발 진기는 잡음 특성이 우수하지 않으나 크기가 작고 주파 수 동작 범위가 넓다. 링 전압제어발진기를 사용하면 잡음 특성이 좋은 출력 신호를 생성하기 위해서는 대역 폭이 좁은 것이 유리하다. 하지만 좁은 대역폭은 루프 필터에서 큰 용량의 커패시턴스를 필요로 한다. 이는 루프필터와 집적화가 불가능하게 하여 루프필터를 칩 외부에 배치하도록 한다.

작은 커패시턴스 용량이 큰 커패시턴스 용량이 된 것 처럼 역할을 하도록 연구가 진행되고 있으며 많은 구조 들이 제안 되었다. 복수의 루프와 능동 루프필터를 사 용하여 유효 커패시턴스 크기를 증가시켜, 작은 루프필 터 커패시턴스를 만들어 칩 내부로 집적화 하여 위상고 정루프를 하나의 칩으로 구현하였다[2-4]. [2-4]에서의 구조는 복수의 루프와 능동 루프필터를 사용함으로써 복잡한 구조가 되어 크기와 설계의 어려움이 있다. 빠 른 위상고정 시간과 넓은 대역폭, 좋은 지터 특성을 얻 기 위해 새로운 적응적 위상고정루프 구조[5], 빠른 위 상 고정시간과 낮은 위상 잡음 특성을 얻기 위해 단계 적 대역폭 변화 방식을 이용한 디지털 위상고정루프[6] 을 이용한 구조들이 연구되었다. [5]에서의 제안된 위상 고정루프 구조는 새로운 전하펌프 구조와 루프필터의 저항변화로 빠른 위상고정 시간과 낮은 위상잡음 특성 및 좋은 지터특성을 얻을 수 있지만 2차 루프필터의 사 용으로 인해 칩의 전체적인 크기가 커지게 된다. [6]에 서의 단계적 루프 대역폭 조절기는 복잡한 구조의 디지 털 블록으로 만들어지기 때문에 칩의 전체적인 크기가 커지고, 동작 속도가 느리며 소비전력이 증가하는 문제 를 가지고 있다. [7]은 루프필터 출력 전압 변화를 감지 하여 전하펌프 전류 크기를 조절하여 특성은 개선하였 으나 추가된 회로에 의해 크기가 증가하였다.

본 논문에서는 제안된 전하펌프를 사용하여 루프필터에 하나의 커패시터만을 사용하여 작은 크기의 위상고정 루프를 구현하였다. 제안된 구조는 루프필터에 하나의 커패시터를 사용하더라도 2차 루프필터를 사용한 것과 같은 전압파형을 얻음으로써 위상을 고정 시킬 수 있다. 또한 LSI(Lock Status Indicator)회로를 사용함으로써 빠른 위상고정 시간을 얻을 수 있다[8]. 제안된 구조는 기존의 2차 루프필터 사용으로 인한 집적화가 불가능한 크기의 칩 면적과 긴 위상고정 시간을 개선할수 있다.

# Ⅱ. 제안된 1차 루프필터를 사용하는 위상고정 루프 회로

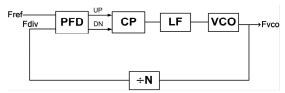

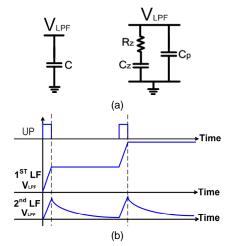

기본 위상고정루프(PLL)구조는 그림 1과 같이 위상· 주파수 검출기(PFD), 전하펌프(CP), 루프필터(LF), 전 압제어발진기(VCO) 그리고 분주기(Divider)로 구성된 다. 그림 2의 하나의 커패시터로 구성된 1차 루프필터 의 출력 전압 파형은 UP신호가 "High"가 되었을 때 충 전이 되지만 그 이후 빠지는 전류가 없기 때문에 일정 한 크기를 유지한다. 그러므로 위상고정루프 기준신호 한 주기 동안 발생하는 과위상변이(excess phase shift) 가 너무 커서 전체 동작이 불안해진다. 그림2의 2차 루 프 필터 출력 전압은 UP신호가 "High"가 되는 동안 전 류는  $C_p$ 로 충전되어서 증가하고, 그 후 UP신호가 "Low"가 되면  $R_z$ 를 통하여  $C_z$ 로 전하가 이동하여 전 압이 낮아진다. 그러므로 위상고정루프 기준신호 한 주 기 동안 발생하는 과위상변이(excess phase shift)가 작 아져서 전체가 안정하게 동작한다. 위상고정루프에서 는 안정한 동작을 위한 조건으로 대역폭이 기준 신호 주파수의 최소 1/10 이하가 되면서 루프 필터 출력 전압 에 의해 발생하는 과위상변이(excess phase shift)를 줄 이기 위해서는 그림 2의 2차 루프필터에서  $C_z$ 의 크기 가  $C_n$ 의 크기보다 최소 10배 이상 되도록 한다. 또한 개 루프 전달함수의 크기가 "1"일 때 45°의 위상여유를 가 지도록 하여야 한다. 이러한 조건을 만족하는 2차 루프 필터의 커패시터와 저항은 내부에 집적화가 불가능한 크기의 면적이 필요하게 된다.

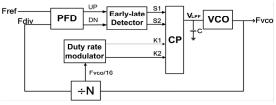

그림 3의 제안한 위상고정루프는 위상여유가 "0"이 되는 하나의 커페시터로 구성된 1차 루프필터를 사용하 나 추가된 회로에 의해 안정하게 동작한다. 이는 위상 고정루프에서 가장 큰 면적을 차지는 루프필터의 커패 시터 면적을 줄여 집적화를 가능하게 해준다.

그림 3의 위상고정루프는 기존의 위상고정루프와 달리 루프필터 커패시터를 1차로 사용하여 집적화가 가능하도록 한 것이다. 제안된 위상고정루프는 위상·주파수 검출기의 출력신호를 바로 전하펌프로 들어가는 것이아니라 Early-late Detector를 통과하고 전하펌프에 들어가게 된다. 전하펌프는 Early-late Detector에서 나오는 출력 S1, S2 외에도 분주기의 출력 중 한 신호를 입력으로 하여 만든 K1, K2 신호를 입력으로 받게 된다.

Fig. 1 Conventional PLL

**Fig. 2** Loop filter and voltage characteristic (a) 1st and 2nd loop filter (b)  $\Delta\Delta V_{LPF}$  of loop filter

Fig. 3 Proposed PLL structure

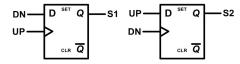

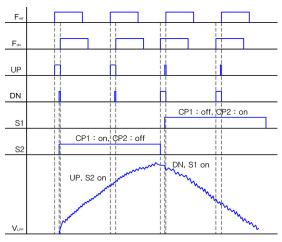

그림 4는 Early-late Detector의 회로를 보여주고 있다. 이 회로는 위상·주파수 검출기의 출력 신호인 UP신호와 DN신호 중 어느 것이 앞선 가에 따라 S1 혹은 S2의 신호를 생성한다.

그림 5는 Early-late Detector 신호들의 파형을 보여주고 있다. UP신호가 DN신호보다 앞서게 될 때 S1은 "Low" 상태가 되고, S2는 "High" 상태가 된다. 이는 DN신호가 UP신호보다 앞서게 될 때까지 유지된다. DN신호가 UP신호를 앞서게 되면 S1은 "High" 상태가 되고, S2는 "Low" 상태가 된다. Early-late Detector를 통해 나오는 S1신호와 S2신호를 사용하여 전하펌프를 제어한다. UP신호가 앞서게 되면 S2가 "High" 상태가되고  $V_{LPF}$  값은 증가하게된다. DN신호가 앞서게 되면 S1이 "High" 상태가되고  $V_{LPF}$  값은 감소하게된다. 이는 기존 위상·주파수 검출기에서 나오는 UP신호 혹은 DN신호가 High가될 때만 전압을 증가 혹은 감소시키는 경우보다 빠른 속도로 전압파형을 증가, 감소시킬수 있다. 이를 통해 빠르게 위상을 고정시킬수 있다.

Fig. 4 Early-late detector

Fig. 5 Early-late detector waveform

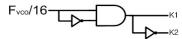

제안된 위상고정루프는 하나의 커패시터로 구성된 1 차 루프필터를 사용하더라도 그림 2의 2차 루프필터 전 압파형과 같이 전압상승과 하강을 만들어주어 위상을 고정시키게 된다. 그림 6은 분주기에서 생성된 신호를 "High"와 "Low" 비율을 그림 7에 나타난 봐와 같이 원하는 크기로 생성하는 회로이다. 생성된 신호인 K1과 K2는 제안된 전하펌프의 입력으로 들어가서 "Low" 구간에서는 전압이 상승하게 되고, "High" 구간에서 전압이 하강하게 되는 구조로써 2차 루프필터를 사용한 것처럼 전압파형을 만들어 된다.

그림 7 (a)는 UP신호에 의해 S2신호가 "High" 인 상황에서  $V_{LPF}$ 의 모습이다. K1의 "Low"와 "High"의 비율은 55:45로 설정 하였다. 제안된 전하펌프에 의해 K1의 파형이 "Low"가 될 때  $V_{LPF}$ 는 상승하게 되고, "High"가 될 때  $V_{LPF}$ 는 하강하게 된다. 같은 양의 전류가 상승 하강되기 때문에 K1의 비율에 따라 전압의 상승 폭이 결정된다. 그림 7 (b)는 DN신호에 의해 S1신호가 "High" 인 상황에서  $V_{LPF}$ 의 모습이다. K2의 "Low"와 "High"의 비율은 45:55로 설정하였다. 제안된 전하펌프에 의해 K2의 파형이 "Low"가 될 때  $V_{LPF}$ 는 상승하게 되고, "High"가 될 때  $V_{LPF}$ 는 하강하게 된다. 같은 양의 전류가 상승·하강되기 때문에 K2의 비율에 따라 전압의 하강 폭이 결정된다.

Fig. 6 Duty-rate Modulator

Fig. 7 Duty-rate Modulator (a) S2 "on" state waveform (b) S1 "on" state waveform

Fig. 8 Proposed charge pump and 1st loop filter

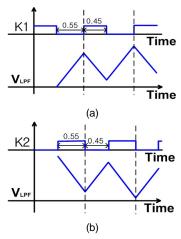

그림 8의 회로의 전하펌프는 Early-late Detector와 Duty-rate Modulator의 출력 신호를 입력으로 받아 전류를 제어하는 제안된 전류펌프 회로이다.  $V_{LPF}$ 전압이 UP신호에 의해 상승해야 할 경우 Early-late Detector에 의해 S2신호가 "High"가 되고 S1신호는 "Low"가 된다. 그 때 CP1은 "on" 상태가 되고 CP2는 "off" 상태가 된다. CP1이 "on" 상태가 될 때 Duty-rate Modulator에 의해 생성된 K1신호에 의해 55:45의 비율로 전압이 계속 상승하게 된다.

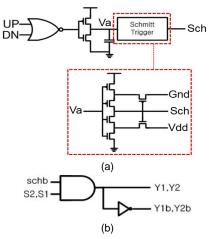

**Fig. 9** Additional circuits (a) LSI circuit (b) Control signal generation circuit with LSI output signals.

만약 DN신호에 의해 전압이 하강해야 한다면 S1신호가 "High"가 되고 CP2가 "on"이 된다. 그 후 K2 신호에 의해 전압이 계속 하강하게 된다. 이는 그림 5의  $V_{LPF}$  파형을 통해서 확인할 수 있다.

보조 전하펌프는 위상이 고정되기 전에 많은 전류를 흐르게 해줌으로써 위상고정 시간을 줄여주는 역할을 해주는 회로이다. 주 전하펌프와 같이 K1과 K2에 의해 전압이 상승하고 하강하게 되며, 위상이 고정된 후 "off"가 되어야하기 때문에 그림 9의 (a)의 LSI(Lock Status Indicator)회로를 통해서 제어가 된다. 그리고 S2와 S1신호 각각 독립적으로 동작해야 함으로 (b)와 같은 회로를 사용하여 제어한다.

## Ⅲ. 시뮬레이션 결과

제안한 구조의 위상고정루프는  $1.8 \mathrm{V}~0.18 \mu\mathrm{m}$  CMOS 공정을 사용하여 시뮬레이션 하였다.  $15.625 \mathrm{MHz}$ 의 입력주파수를 가지고 분주비는 64이며, 출력 주파수는  $1 \mathrm{GHz}$ 이다. 기존 위상고정루프와 제안한 위상고정루프는 모두 1차 루프필터를 사용하였으며, 변수 값은  $I_{CP}=25 \mu\mathrm{A}$ , C= $100 \mathrm{pF}$ ,  $K_{VCO}=330 \mathrm{MHz}/\mathrm{V}$ 이다.

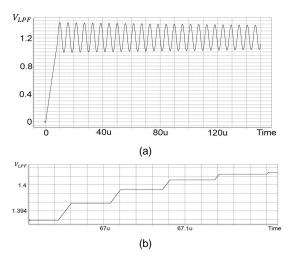

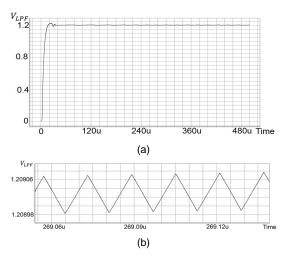

기존의 1차 루프필터를 사용한 위상고정루프는 그림 10 (a)처럼 위상고정이 되지 않는 것을 확인 할 수 있다. 기준 신호 한 주기 동안의 루프필터 출력 파형인  $\Delta\Delta V_{LPF}$  전압파형은 그림 10 (b)이며 2차 루프필터를 사용한 것처럼 만들어주기 위해 제안한 구조를 사용하였다. 제안한 위상고정루프는 위상 여유가 없는 하나의 커패시터로 구성된 1차 루프필터를 사용하여도 그림 11 (a)처럼 위상고정이 되게 만들었다. 크기가 작은 하나의 커패시터로 구성된1차 루프필터를 사용함으로써 추가적인 저항과 커패시터가 필요 없기 때문에 위상고정루프의 크기가 작아지게 된다. 그림 11의 (b)는 제안한 위상고정루프의 루프필터 출력 파형이 기존의 2차 루프 필터 출력 파형과 같은 전압파형을 보여주고 있다.

그림 10 (a)와 그림 11 (a)에서 위상고정루프의 위상고정 후 루프필터 출력전압 변동 폭을  $\Delta V_{LPF}$ 라고 한다.  $\Delta V_{LPF}$ 의 크기는 작을수록 잡음 특성에 더 좋아지게 된다. 제안한 구조의 경우 위상고정 시간이 약 60us가 되고  $\Delta V_{LPF}$ 의 크기는 2.4mV가 된다. 표 1에서 기존

의 1차 루프필터를 사용한 결과와 비교하여 커패시터 값을 고려했을 때 충분히 빠르고 작은 값으로 위상이 고정되는 것을 확인할 수 있다.

Fig. 10 Conventional PLL (a)  $V_{LF}$  waveform (b)  $\varDelta\varDelta\,V_{LF}$  waveform

Fig. 11 Proposed PLL (a)  $V_{LF}$  waveform (c)  $\Delta\Delta V_{LF}$  waveform

Table. 1 Lock time and loop filter voltage characteristic

|                         | Conventional PLL | Proposed PLL |

|-------------------------|------------------|--------------|

| Lock time               | Oscillation      | 60us         |

| $\Delta V_{LPF}$        | Oscillation      | 2.4mV        |

| $\Delta \Delta V_{LPF}$ | Oscillation      | 0.08mV       |

## Ⅳ. 결 론

본 논문에서는 기존의 구조로는 충분하지 않은 위상 여유로 인하여 안정하게 동작을 할 수 없는 하나의 커패 시터로 구성된 1차 루프필터를 사용하더라도 안정하게 동작하며 위장 고정시간이 짧고 크기가 아주 작은 위상 고정루프를 제안하였다. 하나의 커패시터로 구성된 1차 루프필터에서는 가질 수 없는 2차 루프필터의 전압 파형을 만들어 줌으로써 안정하게 동작 하도록 하였다. 2차 루프필터의 전압 파형처럼 만들어 주기 위해 2개의 전하펌프와 Early-late Detector와 Duty-rate Modulator를 사용해서 구현하였다. 제안한 구조를 통해 기존 위상고정루프의 면적을 결정하는 루프필터의 큰 용량의 커패시터를 사용하지 않음으로써 크기가 작고 위상고정 시간이 짧은 위상고정루프를 구현할 수 있다.

#### **REFERENCES**

- [1] P. K. Hanumolu, M. Brownlee, K. Mayaram and U. K. Moon, "Analysis of Charge-Pump Phase-Locked Loops," IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 51, no. 9, pp. 1665-1674, Sep. 2004.

- [2] J. Craninckx and M. Steyaert, "A fully integrated CMOS DCS-1800 frequency synthesizer," *IEEE International Solid-State Circuits Conference. Digest of Technical Papers*, vol. 33, no. 12, pp. 2054-2065, Dec. 1998.

- [3] Y. Koo, H. Huh, Y. Cho, J. Lee, J. Park, D. Jeong, and W. Kim, "A fully integrated CMOS frequency synthesizer with charge-averaging charge pump and dual-path loop filter for PCS- and cellular-CDMA wireless systems," *IEEE Journal of Solid-State Circuits*, vol. 37, no. 5, pp. 536-542, May 2002.

- [4] B. Catli, A. Nazemi, T. Ali, S. Fallahi, Y. Liu, J. Kim, M. Abdul-Latif, M. R. Ahmadi, H. Maarefi, A. Momtaz, and N. Kocaman, "A 2sub-200 fs RMS jitter capacitor multiplier loop filter-based PLL in 28 nm CMOS for high-speed serial communication applications," *Custom Integrated Circuits Conference*, pp. 1-4, 2013.

- [5] M. Ghasemzadeh, S. Mahdavi, A. Zokaei, K. Hadidi, "A New Adaptive PLL to Reduce the Lock Time in 0.18µm technology," MIXDES - 23rd International Conference Mixed Design of Integrated Circuits and Systems, pp. 140-142, June 2016.

- [6] J. Dunning et al., "An all-digital phase-locked loop with 50-cycle lock time suitable for high-performance microprocessors," *IEEE Journal of Solid-State Circuits*, vol. 30, no. 4, pp. 412-422, Apr. 1995.

- [7] Y. S. Choi, S. J. An, "Loop filter voltage variation compensated PLL with charge pump," *Journal of Korea Institute of Information and Communication Engineering*, vol. 20, no. 10, pp. 1935-1940, Oct. 2016.

- [8] Y. S. Choi, H. H. Choi, T. H. Kwon, "An Adaptive Bandwidth Phase Locked Loop with Locking Status Indicator," Proceedings. The 9th Russian-Korean International Symposium on Science and Technology, pp. 826-829, July 2005.

고기영(Ki-Yeong Ko)

2016년 부경대학교 전자공학과 학사 졸업. 2016년 부경대학교 전자공학과 석사 입학. ※관심분야: PLL, DLL 설계

최영식(Young-Shig Choi)

1982년 경북대학교 전자공학과 학사 졸업. 1986년 Texas A&M University 전자공학과 석사 졸업. 1993년 Arizona State University 박사 졸업. 1987년 ~ 1999년 현대전자(현 SK Hynix) 책임연구원 2003년 ~ 현재 부경대학교 전자공학 교수 ※관심분야: PLL, DLL 설계