**ARTICLE**

# 오프셋 전압을 이용한 계통 연계형 3상 3레벨 T-type 태양광 PCS의 중성점 전압 불평형 보상

박관남\*·최 익\*\*·최주엽\*\*·이영권\*\*\*

- \*광운대학교 로봇학과

- \*\*광운대학교 전기공학과

- \*\*\*금비전자

# Compensation of Unbalanced Neutral Voltage for Grid-Connected 3-Phase 3-Level T-type Photovoltaic PCS Using Offset Voltage

Park Kwan-Nam\* · Choy Ick\*† · Choi Ju-Yeop\*\* · Lee Young-Kwoun\*\*\*

- \*Department of Robotics, Kwangwoon University

- \*\*Department of Electrical Engineering, Kwangwoon University

- \*\*\*Keumbi Electronics Co., Ltd.

#### **Abstract**

The DC link of Grid-Connected 3-Phase 3-Level T-type Photovoltaic PCS (PV-PCS) consists of two series connected capacitors for using their neutral voltage. The mismatch between two capacitor characteristics and transient states happened in load change cause the imbalance of neutral voltage. As a result, PV-PCS performance is degraded and the system becomes unstable. In this paper, a mathematical model for analyzing the imbalance of neutral voltage is derived and a compensation method using offset voltage is proposed, where offset voltage adjusts the applying time of P-type and N-type small vectors. The validity of the proposed methods is verified by simulation and experiment.

**Keywords:** 태양광 PCS(Photovoltaic PCS), 3-레벨 T-type 인버터(3-Level T-type inverter), 중성점 전압 불평형 보상(Compensation of unbalanced neutral voltage), 오프셋 전압(Offset voltage), 공간 벡터 전압 변조(Space vector pulse width modulation)

#### 1. 서론

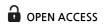

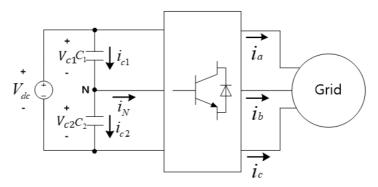

계통연계형 태양광 전력 변환 장치(PV-PCS, PhotoVoltaic-Power Conditioning System)는 태양전지로부터 얻은 전력을 변환하여 계통으로 전달해 준다. 일반적으로 PV-PCS는 태양 전지의 최대 전력점 추종(MPPT, Maximum Power Point Tracking)을 위한 승압형 DC-DC 컨버터와 DC 전력을 3상 계통 AC 전력으로 변환하기 위한 인버터로 구성되어 있다. 최근 전력 손실을 줄이는 동시에 높은 전력 품질을 얻기 위하여 Fig. 1과

Journal of the Korean Solar Energy Society Vol.37, No.6, pp.1-12, December 2017 https://doi.org/10.7836/kses.2017.37.6.001

pISSN: 1598-6411 eISSN: 2508-3562

Received: 31 July 2017

Revised: 11 December 2017

Accepted: 14 December 2017

Copyright © Korean Solar Energy Society

This is an Open-Access article distributed under the terms of the Creative Commons Attribution NonCommercial License which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

<sup>&</sup>lt;sup>†</sup>Corresponding author: ickchoy@kw.ac.kr

같은 3레벨 T-type 인버터로 구성된 PV-PCS가 사용되고 있다<sup>1,2,3)</sup>.

Fig. 1 Structure of grid-connected 3-phase 3-level T-type photovoltaic PCS

Fig. 1의 PV-PCS는 중성점 전압  $V_{c2}$ 가  $V_{c1}$ 과 전압이 다른 불평형 문제를 가지고 있다. 전압 불평형은  $C_1$ ,  $C_2$ 커패시터의 제조 공정상 커패시턴스 오차와 3레벨 T-type 인버터 스위칭 패턴에 따라 중성점에 흐르는 전류에 의해 발생된다. 전압이 한쪽 커패시터로 쏠리기 때문에 하나의 스위칭 소자에 인가되는 전압이 증가 되어 스위칭 소자의 스트레스가 증가되고 최악의 경우 스위칭 소자가 파괴될 수 있다. 출력 전류의 THD (Total Harmonic Distortion)가 증가하며 시스템이 불안정해진다 $^{4,5}$ . 따라서 3레벨 T-type PV-PCS의 중성점 전압 불평형을 보상하여 전압 평형을 유지하는 것은 중요한 요소라고 볼 수 있다 $^{6}$ .

중성점 전압 불평형을 보상하기 위한 방법으로 3레벨 T-type 인버터의 PWM 기법에 따라 보상하는 방법이연구되고 있다<sup>7,8,9,10,11)</sup>. 또 3레벨 T-type 인버터의 앞단에 중성점 전압 보상이 가능한 3레벨 승압형 DC-DC 컨버터를 이용하는 방법이 있지만 비용 증가 및 스위칭 손실이 증가 하는 단점이 있다<sup>12,13)</sup>.

본 논문에서는 3레벨 인버터의 PWM 기법으로 Min-Max 법을 적용한 공간 벡터 전압 변조 방법(SVPWM, Space Vector Pulse Width Modulation)을 사용하여 오프셋 전압을 주입하는 중성점 전압 불평형 보상 방법을 제안한다. Min-Max 법이 적용된 SVPWM은 총 27개의 전압 벡터가 존재한다. 각 전압 벡터가 3레벨 T-type 인버터에 인가될 때 중성점에 흐르는 전류  $i_N$ 은 인가된 전압 벡터에 의해 결정된다 $^{14}$ . 그리고 PWM 주기  $T_s$  동안 항상 양쪽 끝에 같은 전압 벡터지만 type이 서로 다른 P-type, N-type small 전압 벡터가 하나씩 인가된다. 이때 P-type small 벡터가 인가될 때 중성점 전류  $i_N$ 와 N-type small 벡터가 인가되는 동안 중성점 전류  $i_N$ 는 크기가 같고, 흐르는 방향이 서로 반대다. 따라서 만약 P-type small 벡터가 인가되는 시간동안 중성점 전류  $i_N$ 에 의해  $V_{c1}$ 는 증가하고  $V_{c2}$ 가 감소한다고 하면, N-type 벡터는 중성점 전류가 반대로 흐르기 때문에  $V_{c1}$ 는 감소하고  $V_{c2}$ 가 증가한다. 이러한 성질을 이용하여  $V_{c1}$ 와  $V_{c2}$ 의 크기를 비교하여 P-type, N-type small 벡터가 인가되는 시간을 적절히 조절하여 중성점 전압 불평형을 보상할 수 있다.

Min-Max 법을 적용한 SVPWM의 상전압 지령  $V_a^*, V_b^*, V_c^*$ 에 각각 오프셋 전압  $V_{offset}$ 을 주입했을 때, P-type small 벡터가 인가되는 시간  $T_p$ 가 오프셋 전압에 비례한 시간  $\Delta T$ 만큼 증가했다면, N-type 벡터가 인

가되는 시간  $T_n$ 은  $\triangle T$ 만큼 감소한다. 반대로  $T_p$ 가  $\triangle T$ 만큼 감소하면  $T_n$ 은  $\triangle T$ 만큼 증가한다. 기존의 오 프셋 전압 주입을 이용한 연구는 이러한 성질을 이용하여 중성점 전압 불평형을 보상하는 알고리즘이 제안되고 있지만 보상 제어기를 설계하기 위한 보상 시스템의 수학적 모델을 제시하지 못하는 한계가 있다 $^{15}$ .

따라서 본 논문에서는 보상을 위한 중성점 전압 불평형의 수학적 모델을 설명하고, 이를 기반으로 보상기를 설계하는 방법에 대하여 설명한다. 설명한 방법은 PSIM 시뮬레이션과 실제 계통연계형 3레벨 T-type PV-PCS로 실험을 진행하여 그 타당성을 증명하였다.

## 2. SVPWM에 의한 3레벨 인버터 출력전압 제어

#### **2.1 SVPWM**

3레벨 T-type 인버터는 Fig. 1처럼 한 상에 4개의 스위치가 있으며, 총 12개의 스위칭 소자를 사용하게 된다.

| <b>Table</b> 1 State of switch and output voltage $(X = a,b,c)$ | Table ' | State of switch and output voltage $(X = a,b,c)$ |

|-----------------------------------------------------------------|---------|--------------------------------------------------|

|-----------------------------------------------------------------|---------|--------------------------------------------------|

| Chaha |          | Output   |          |          |                        |

|-------|----------|----------|----------|----------|------------------------|

| State | $S_{X1}$ | $S_{X2}$ | $S_{X3}$ | $S_{X4}$ | Output pole voltage(V) |

| P     | On       | On       | Off      | Off      | $V_{dc}/2$             |

| O     | Off      | On       | On       | Off      | 0                      |

| N     | Off      | Off      | On       | On       | $-\ V_{dc}/2$          |

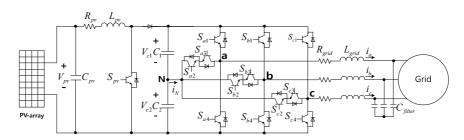

Fig. 2 Space vector diagram of 3-level inverter

이때 스위치 on, off 상태에 따른 3레벨 인버터의 출력 극전압은 Table 1과 같다. 3레벨 인버터는 스위치  $S_{X1}$ 와  $S_{X3}$ ,  $S_{X2}$ 와  $S_{X4}$ 가 서로 상보적으로 동작하며 한 상에 P,O,N 스위칭 상태가 3개 존재한다. 3개 상의 스위칭 상태를 조합하면 3레벨 인버터는 Fig. 2의 27개의 스위칭 벡터를 가질 수 있다.

SVPWM은 Fig. 2와 같이 스위칭을 통해 인버터에 인가되는 상전압 지령  $V_a^*, V_b^*, V_c^*$ 을 복소 공간에서 하나의 공간 벡터  $\overrightarrow{V_{ref}}$ 로 표현하여 스위칭 시간을 결정하는 기법이다. 일반적으로 6개의 Sector로 구분할 수 있으며,  $V_a^*, V_b^*, V_c^*$ 의 부호에 따라 6개의 Region으로 구분 할 수 있다.

| Space vector           |                   |                                 | $i_N$           |                           | Space ve | ctor   | $i_N$ |                           | Space ve | ctor   | $i_N$ |

|------------------------|-------------------|---------------------------------|-----------------|---------------------------|----------|--------|-------|---------------------------|----------|--------|-------|

| $\overrightarrow{V_0}$ | [PPP] [OOO] [NNN] | Zero vector                     | 0               |                           |          |        |       |                           |          |        |       |

| $\overrightarrow{V_1}$ | [POO] / [ONN]     |                                 | $-i_a/i_a$      | $\overrightarrow{V_7}$    | [PON]    |        | $i_b$ | $\overrightarrow{V_{13}}$ | [PNN]    |        | 0     |

| $\overrightarrow{V_2}$ | [PPO] / [OON]     | P-type / N-type<br>small vector | $i_c  /  -i_c$  | $\overrightarrow{V}_8$    | [OPN]    |        | $i_a$ | $\overrightarrow{V_{14}}$ | [PPN]    |        | 0     |

| $\overrightarrow{V_3}$ | [POP] / [NON]     |                                 | $-i_b/i_b$      | $\overrightarrow{V_9}$    | [NPO]    | Medium | $i_c$ | $\overrightarrow{V_{15}}$ | [NPN]    | Large  | 0     |

| $\overrightarrow{V_4}$ | [OPP] / [NOO]     |                                 | $i_a  /  - i_a$ | $\overrightarrow{V_{10}}$ | [NOP]    | vector | $i_b$ | $\overrightarrow{V_{16}}$ | [NPP]    | vector | 0     |

| $\overrightarrow{V_5}$ | [OOP] / [NNO]     |                                 | $-i_c/i_c$      | $\overrightarrow{V_{11}}$ | [OPN]    |        | $i_a$ | $\overrightarrow{V_{17}}$ | [NNP]    |        | 0     |

| $\overrightarrow{V_6}$ | [POP] / [ONO]     |                                 | $i_b$ / $-i_b$  | $\overrightarrow{V_{12}}$ | [PNO]    |        | $i_c$ | $\overrightarrow{V_{18}}$ | [PNP]    |        | 0     |

**Table 2** Neutral current  $i_N$  according to space vector

SVPWM은 벡터 크기에 따라 Zero 벡터, P-type small 벡터, N-type small 벡터, Medium 벡터, Large 벡터 가 존재하며, 인버터에 각 공간 벡터 전압이 인가될 때 중성점에 흐르는 전류  $i_N$ 는 Table 2와 같다 $^{12)}$ . 중성점에 흐르는 전류  $i_N$ 는 3상 상전류  $i_a$ ,  $i_b$ ,  $i_c$ 로 표현된다.

#### 2.2 Min-Max 기법

Min-Max 기법은 식(1)과 같이 상전압 지령의 최대값  $V_{Max}$ , 최소값  $V_{Min}$ 의 평균  $V_S$ 을 모든 상전압 지령에서 빼주면 중성점(0V) 기준으로 재배치된 상전압 지령  $V_{ar}^*$ ,  $V_{br}^*$ ,  $V_{cr}^*$ 을 얻을 수 있다.

$$V_{S} = \frac{V_{Max} + V_{Min}}{2}$$

$$V_{ar}^{*} = V_{a}^{*} - V_{S}, \quad V_{br}^{*} = V_{b}^{*} - V_{S}, \quad V_{cr}^{*} = V_{c}^{*} - V_{S}$$

$$(1)$$

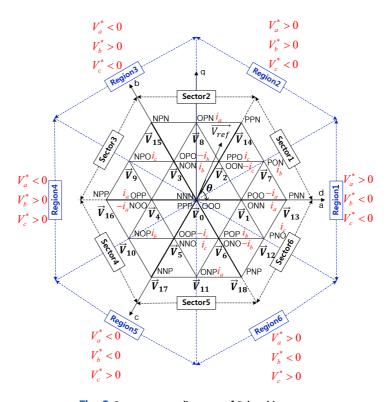

Fig. 3은 Region1에서 Min-Max 기법을 적용한 SVPWM의 예시다. Min-Max 기법을 적용 하였을 때 얻는

이점은 인버터 제어시 출력 상전압 지령  $V_a^*, V_b^*, V_c^*$ 이 중성점 전압 기준으로 재배치되어  $V_S$  만큼 전압 여유가 더 생기므로 변조 영역이 확장된다는 것이다. 따라서 중성점 전압 불평형을 보상하기 위한 오프셋 전압  $V_{offset}$ 을 확장된 전압 여유만큼 더 인가할 수 있다. 그리고 항상 제어주기  $T_s$ 에서 양 끝에 같은 전압 벡터가 P-type, N-type 형태로 위치하게 된다. 중성점 전압 불평형은 중성점 전류  $i_N$ 에 의해 발생되는데 P-type, N-type small 벡터는 Table 2에서 볼 수 있듯 중성점 전류  $i_N$ 은 서로 반대이다. 즉두 전압 벡터가 중성점 전압에 미치는 영향은 서로 정 반대라는 사실을 알 수 있다. 예를 들어 P-type small 벡터가 전압  $V_{c1}$ 을 증가시키고  $V_{c2}$ 을 감소시킨다면, N-type small 벡터는 반대로  $V_{c1}$ 을 감소시키고  $V_{c2}$ 을 증가시킨다. 따라서 Fig. 3과 같이 불평형 전압에 따라 적절한  $V_{offset}$ 을 주입하여 양끝의 P-type, N-type small 벡터가 인가되는 시간을  $\Delta T$ 시간만큼 조절하여 중성점 전압 불평형을 감소시킬 수 있다.

Fig. 3 SVPWM applied Min-Max method in Region1

# 3. 중성점 전압 불평형 보상

#### 3.1 중성점 전압 불평형 해석

중성점 전압이 평형이 되려면 Fig. 1의  $V_{c1}$  전압과  $V_{c2}$  전압이 각각  $V_{dc}/2$ 씩 동일한 값이 되어야 한다.  $C_1$ 에 흐르는 전류를  $i_{c1}$ ,  $C_2$ 에 흐르는 전류를  $i_{c2}$ 라 하면 PWM 주기  $T_s$ 동안 두 커패시터에 흐르는 전류에 의해 커패시터 전압이 결정된다. DC-Link 전압  $V_{dc}$ 는 Fig. 3의 PWM 주기  $T_s$ 동안 3레벨 인버터에서 일정하게 제어되고 있기 때문에 제어되는 일정한 전원 소스전압으로 볼 수 있다. 따라서 커패시터 전압 변화를 해석하기 위한 모델은 Fig. 4와 같다. Fig. 4의  $V_{dc}$ 는 일정한 상수이므로  $\dot{V}_{c1}$ = $-\dot{V}_{c2}$ 을 만족한다. 이때 중성점(N)에서 키르히호

프 전류 법칙을 적용하면 식(2)와 같이  $T_s$ 동안 커패시터  $V_{c1}$ ,  $V_{c2}$  전압을 구할 수 있다.

Fig. 4 Neutral voltage unbalance model

$$i_{N} = i_{c1} - i_{c2} = C_{1} \dot{V}_{c1} - C_{2} \dot{V}_{c2}$$

$$= (C_{1} + C_{2}) \dot{V}_{c1} = -(C_{1} + C_{2}) \dot{V}_{c2}$$

$$\dot{V}_{c1} = \frac{1}{C_{1} + C_{2}} i_{N}, \qquad \dot{V}_{c2} = \frac{1}{C_{1} + C_{2}} (-i_{N})$$

$$V_{c1} = \frac{1}{C_{1} + C_{2}} \int_{0}^{T_{s}} i_{N} dt, \quad V_{c2} = \frac{1}{C_{1} + C_{2}} \int_{0}^{T_{s}} (-i_{N}) dt$$

(2)

주기  $T_s$  동안 두 커패시터 전압 차이를  $V_d$ 라고 하면 식(2)를 통해 식(3)을 유도할 수 있다.

$$V_d = V_{c1} - V_{c2} = \frac{2}{C_1 + C_2} \int_0^{T_s} i_N dt$$

(3)

$T_s$ 동안 두 커패시터 전압의 차이는 식(3)과 같이 중성점 전류  $i_N$ 에 의해 결정된다. Min-Max 기법이 적용되었기 때문에 Fig. 3과 같이 항상  $T_s$ 동안 양 끝에 P-type, N-type small 벡터가 놓이며, 중간에 Large 또는 Medium, Zero, small 벡터들이 놓이게 된다. 특히 양쪽 끝에 놓이는 P-type, N-type small 벡터는 Fig. 2의 Region 마다 한 개 씩 존재하는 small 벡터다. 예를 들어 Region1에선  $\overrightarrow{V_1}$ 의 [POO], [ONN] 벡터가 양쪽 끝에 위치하고, Region2에선  $\overrightarrow{V_2}$ 의 [PPO], [OON] 벡터가 위치하게 된다.

중성점에 흐르는 전류  $i_N$ 는 Table 2와 같이 Large, Zero 벡터는 0이므로 커패시터 전압 변화에 아무런 영향을 주지 않지만 Medium 벡터와 small 벡터는 중성점에 흐르는 전류가 존재하므로 커패시터 전압에 영향을 준

다. 그러나  $\overrightarrow{V_{ref}}$ 의 위상이 한주기가 지났을 때 평균적으로 중성점 전류가 0으로 수렴한다고 가정하여 중간의 Medium 벡터와 small 벡터의 영향을 무시할 수 있다. 따라서 오직 양 끝의 P-type, N-type small 벡터가 인가될 때 흐르는 중성점 전류  $i_N$ 에 의해 중성점 전압이 결정된다고 볼 수 있다. Table 2에서 보듯 P-type small 벡터가 인가될 때 중성점 전류는  $i_N$ 이 흐르고, N-type small 벡터가 인가될 때 중성점 전류는  $-i_N$ 만큼 흐르게 된다. 따라서 위의 가정에 의하여 전압 불평형이 일어나지 않는 이상적인 경우, P-type small 벡터가 인가되는 시간  $T_p$ 와 N-type small 벡터가 인가되는 시간  $T_p$ 은 같아야한다.

#### 3.2 오프셋 전압 주입에 의한 중성점 전압 불평형 보상 시스템

중성점 보상을 위하여 상전압 지령  $V_{ar}^*$ ,  $V_{br}^*$ ,  $V_{cr}^*$ 에 오프셋 전압  $V_{offset}$ 이 더해지면, Fig. 3과 같이 P-type 벡터가 인가되는 시간은  $T_p+\Delta T$ 이고, N-type 벡터가 인가되는 시간은  $T_n-\Delta T$ 이 된다. 3.1절의 가정에 의해  $T_s$ 동안 오프셋 전압  $V_{offset}$ 으로 인하여 각 커패시터의 전압 변화량을  $\Delta V_{c1}$ ,  $\Delta V_{c2}$ 라 하면, 오프셋 전압 주입에 의해 두 커패시터 전압 차이  $\Delta V_d$ 는 식(2)를 이용하여 식(4)와 같이 구할 수 있다.

$$\Delta V_{d} = \Delta V_{c1} - \Delta V_{c2}

= \frac{2}{C_{1} + C_{2}} \left( \int_{T_{p}}^{T_{p} + \Delta T} i_{N} dt + \int_{T_{n} - \Delta T}^{T_{n}} -i_{N} dt \right) - \frac{2}{C_{1} + C_{2}} \left( \int_{T_{p}}^{T_{p} + \Delta T} (-i_{N}) dt \int_{T_{n} - \Delta T}^{T_{n}} -(-i_{N}) dt \right)

= \frac{4}{C_{1} + C_{2}} \left( \int_{T_{n}}^{T_{p} + \Delta T} i_{N} dt + \int_{T_{n} - \Delta T}^{T_{n}} (-i_{N}) dt \right) = \frac{8}{C_{1} + C_{2}} \int_{0}^{\Delta T} i_{N} dt \left( T_{p} = T_{n} \right) \tag{4}$$

적분 주기는 PWM 주기  $T_s$ 이므로, 식(4)는 식(5)와 같이 다시 표현할 수 있다.

$$\Delta V_{d} = \frac{1}{C_{N}} \int_{0}^{\Delta T} i_{N} dt = \frac{\Delta T}{T_{s}} \frac{1}{C_{N} S} i_{N} \quad (C_{N} = \frac{C_{1} + C_{2}}{8})$$

(5)

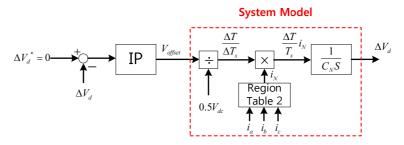

식(5)는 오프셋 전압  $V_{offset}$ 이 두 커패시터 전압 차이에 미치는 영향으로, 중성점 전압 불평형 보상 시스템의 수학적 모델이다. 이 모델을 기반으로 Fig. 5의 두 커패시터 전압 차이  $\Delta$   $V_d$ 를 입력으로 하고, 오프셋 전압  $V_{offset}$ 을 출력으로 하는 보상 제어기를 설계할 수 있다. 보상 제어기 출력  $V_{offset}$ 의 범위는  $V_{c2}+V_{Min}\leq V_{offset}\leq V_{c1}-V_{Max}$   $V_{c2}=\frac{1}{C_1+C_2}\int_0^{T_s}(-i_N)dt$ 으로 커패시터 전압의 여유가 된다. 여기서  $V_{Min}$ 은 상 전압 지령의 최소값이고,  $V_{Max}$ 는 상전압 지령의 최댓값을 지칭한다.

다음으로  $i_N$ 을 결정해주기 위해선 가장 먼저 인버터의 상전압 지령  $V_{ar}^*$ ,  $V_{br}^*$ ,  $V_{cr}^*$ 을 통해 현재 전압 벡터가 어떤 Region에 있는지 판별해야 한다. 앞서 P-type small 벡터가 인가될 때, 중성점에 흐르는 전류  $i_N$ 을 기준으로 식(4),(5)와 같이 중성점 보상 시스템을 모델링했다. 따라서 Fig. 2의 Region에 따라 P-type small 벡터가 인 가될 때 중성점에 흐르는 전류  $i_N$ 에 해당하는 인버터의 상전류를 측정하여 대입하면 된다. Region에 따라  $i_N$ 을 판별하는 부분을 Fig. 5에서 Region Table 2로 표기하였다.

Fig. 5에서 일반적으로 PI 제어기를 사용하면 폐루프 전달함수의 영점이 존재하므로 원하는 제어 성능을 얻을 수 없다. 때문에 PI 제어기 대신 IP 제어기를 사용하여 식(7)과 같이 폐루프 전달함수를 구해보면 영점을 없앨 수 있다. 2차 시스템이 되어 제어기의 고유 진동수와 감쇠비를 적절히 설정해 줄 수 있으므로 원하는 성능으로 제어기 튜 닝이 가능해진다. 튜닝된 IP 제어기 게인은 항상 중성점에 흐르는 전류  $i_N$ 에 영향을 받기 때문에 가변 게인이 된다.

Fig. 5 Block diagram of compensation system of unbalanced neutral voltage

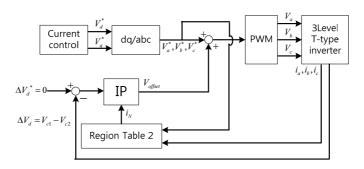

Fig. 6 Overall inverter system block diagram

$$T_{closed} = \frac{\frac{2i_{N}}{S} \frac{2i_{N}}{1 + \frac{2i_{N}k_{p}}{V_{dc}C_{N}S}}}{1 + \frac{2i_{N}k_{p}}{V_{dc}C_{N}S}} = \frac{\frac{2i_{N}k_{i}}{V_{dc}C_{N}}}{S^{2} + \frac{2i_{N}k_{p}}{V_{dc}C_{N}}S + \frac{2i_{N}k_{i}}{V_{dc}C_{N}}}$$

$$1 + \frac{k_{i}}{S} \frac{\frac{2i_{N}}{V_{dc}C_{N}S}}{1 + \frac{i_{N}k_{p}}{V_{dc}C_{N}S}}$$

(7)

Fig. 6은 중성점 보상 제어기가 추가된 전체 3레벨 T-type 인버터 시스템 블록도다.

# 4. 실험 결과

시뮬레이션과 실험을 통해 오프셋 전압을 이용한 중성점 전압 불평형 보상 제어기를 적용하기 전과 후를 비교 분석한다. 시뮬레이션과 실제 실험 환경은 동일한 조건에서 진행하였다. 인버터의 DC-Link 전압  $V_{dc}$ 는  $600~\rm V$ 로 제어하며 역률은 1로 제어되고 있다. Table 3은 Fig. 1의 실제 시스템과 시뮬레이션 시스템의 중요 파라메터들이다.

Table 3 System parameter

| $L_{grid}$ | 2 [mH]          | $C_1$        | 1650 [uF] |  |

|------------|-----------------|--------------|-----------|--|

| $R_{grid}$ | 1 [m $\Omega$ ] | $C_2$        | 1650 [uF] |  |

| $L_{pv}$   | 5 [mH]          | $C_{filter}$ | 6.8 [uF]  |  |

| $R_{pv}$   | 5 [m $\Omega$ ] | $C_{pv}$     | 20 [uF]   |  |

Fig. 7 Before compensation of unbalanced neutral voltage

#### 4.1 시뮬레이션 결과

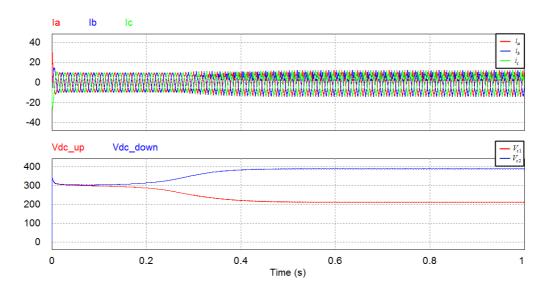

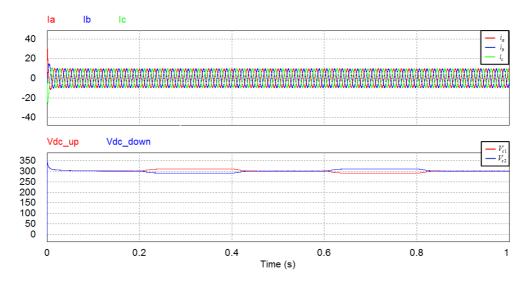

PSIM 시뮬레이션 툴을 이용하여 시뮬레이션을 진행하였다. Fig. 7은 오프셋 전압을 이용한 중성점 전압 불평형 보상 제어기를 적용하기 전 상전류 파형과 상,하 커패시터 전압 파형이다. 발전을 시작하면서 중성점 전압 불평형이 발생되며 이로 인해 출력 상전류에 악영향을 미치게 된다. Fig. 8은 오프셋 전압을 이용한 중성점 전압 불평형 보상 제어기를 적용한 상전류 파형과 상,하 커패시터 전압 파형이다. 특별히 보상 제어기의 동특성을 확

Fig. 8 After compensation of unbalanced neutral voltage

인하기 위하여 보상 제어기 레퍼런스  $\Delta V_d^*$ 를 0 V, 20 V, 0 V, -20 V, 0 V 순으로 0.2초마다 step 입력을 가하였다. 그 결과 보상 제어기가 설계된 대로 레퍼런스  $\Delta V_d^*$ 를 잘 추종하였고, Fig. 7의 보상하기 전 출력 상전류와 비교하여 현저히 개선된 출력 결과를 얻을 수 있다.

#### 4.2 실험 결과

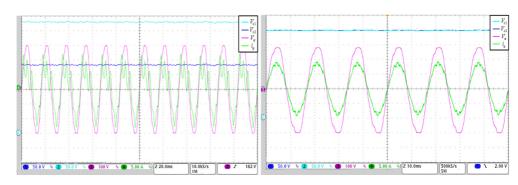

금비전자 S120K 3레벨 T—type 태양광 PCS 모델과 최대 전력점에서 발전량이 4.4 [kW]인 PV 시뮬레이터를 이용하여 실험을 진행하였다. Fig. 9의 왼쪽 파형은 오프셋 전압을 이용한 중성점 전압 불평형 보상 제어기를 적용하기 전이고 오른쪽 파형은 적용 후다. 보상 제어기가 적용되기 전에는 중성점 전압 불평형이 발생되어  $V_{c1}$ 이  $V_{c2}$ 보다 약 150 V정도 커진 상태이다. 중성점 전압 불평형으로 시뮬레이션과 같이 출력 상전류 파형이 무너지게 된다. 반면 보상 제어기가 적용된 오른쪽 파형은 중성점 전압 불평형이 사라져  $V_{c1}$ 과  $V_{c2}$ 가 각각 300 V로 제어된다. 그리고 출력 상전류 파형이 찌그러지지 않고 개선되는 결과를 얻을 수 있다.

Fig. 9 Comparison of waveform before and after applying compensation method

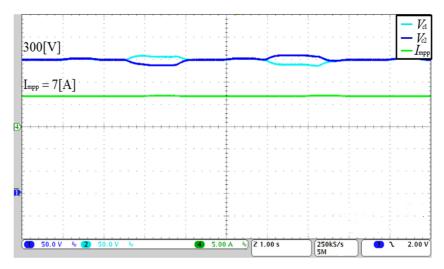

Fig. 10은 본 논문에서 설명한 오프셋 전압을 이용한 보상 제어기의 동특성을 확인하기 위하여 시뮬레이션과 마찬가지로 보상 제어기 레퍼런스 전압  $\Delta V_d^*$ 를 0 V, 20 V, 0 V, -20 V, 0 V 순으로 step입력을 가하였다. 시뮬 레이션과 동일한 결과를 실제 실험을 통해서 얻을 수 있었다.

Fig. 10 Dynamic characteristics of the applied compensation method

# 5. 결론

본 논문에선 3레벨 T-type PCS의 중성점 전압 불평형의 수학적 모델을 제시하고, 오프셋 전압 주입을 이용한 보상 제어기 설계 방법을 설명하였다. 중성점 전압 불평형 보상 제어기를 적용하기 전, 중성점 불평형이 발생되고 출력 상전류에 왜곡이 생기는 문제가 있었다. 본 논문에서 설명한 중성점 전압 불평형 제어기를 추가하여 중성점 전압 불평형이 보상되어 상전류도 왜곡이 사라짐을 확인하였다. 본 논문은 3상 평형인 상황에서 중성점 불평형을 보상하였지만 추후 3상 불평형인 상황에서도 중성점 전압 불평형을 보상하는 방법이 연구되어야 할 것이다.

## 후기

이 논문은 2016년도 광운대학교 교내학술연구비 지원과 한국전력공사의 2016년 선정 기초 연구개발과제(과 제번호: R17XA05-26) 지원을 받아 연구되었음.

#### **REFERENCES**

- 1. Nabae, A., Takahashi, I., and Akagi, H., A New Neutral-point-clamped PWM Inverter, IEEE Trans. Ind. Appl., Vol. IA-17, No. 5, pp. 518-523, 1981.

- 2. Rodriguez, J., Bernet, S., Steimer, P. K., and Lizama, I. E., A Survey on Neutral-point-clamped Inverters, IEEE

- Trans. Ind. Electron., Vol. 57, No. 7, pp. 2219-2230, 2010.

- 3. Franquelo, L. G., Rodriguez, J., Leon, J. I., Kouro, S., Portillo, R., and Prats, M. M., The Age of Multilevel Converters Arrives, IEEE Ind. Electron. Mag., Vol. 2, No. 2, pp. 28-39, 2008.

- 4. Celanovic, N. and Boroyevich, D., A Comprehensive Study of Neutral-point Voltage Balancing Problem in Three-level neutral-point-clamped Voltage Source PWM Inverter, IEEE Trans, Power Electron, Vol. 15, No. 2, March 2000.

- 5. McGrath, B. P. and Homes, D. G., Multicarrier PWM Strategies for Multilevel Inverters, IEEE Trans, Industrial Electronics, Vol. 49, No. 4, Aug 2002.

- 6. Newton, C., Sumner, M., Neutral Point Control for Multi-level Inverters: Theory, Design and Operational limitations, in Proc. Ind. Appl. Soc. (IAS), Vol. 2, pp. 1336-1343, 1997.

- 7. Lee, Y. H., Kim, R. Y., and Hyum, D. S., A Novel SVPWM Strategy Considering Dc-link Balancing for a Multi-level Voltage Source Inverter, IEEE Proc. APEC-99, pp 509-514, 1999.

- 8. Aspen HYSYS. Version 8.0, Aspen Technology Inc, 2014.

- 9. Nabae, A., Takahashi, I., and Akagi, H., A New Neutral-point-clamped PWM Inverter, IEEE Trans. Ind. Appl., Vol. IA-17, No. 5, pp. 518-523, 1981.

- Yoon, J. I., Son, C. H., Baek, S. M., Kim, H. J., and Lee, H. S., Efficiency Comparison of Subcritical OTEC Power Cycle Using Various Working Fluids, Journal of Heat and Mass Transfer, Vol. 50, No. 7, pp. 985-996, 2014.

- 11. Yoon, J., Performance Characteristics of a Mixed Refrigerant OTEC Power Cycle Using Hot Waste Water, Journal of the Korea Society for Power system Engineering, Vol. 17, No. 8, pp. 103-108, 2013.

- 12. Li, W. and He, X., Review of Nonisolated High-Step-Up DC/DC Converters in Photovoltaic Grid-Connected Applications, IEEE Trans. Ind. Electron., Vol. 58, No. 4, pp. 1239-1250, 2011.

- 13. Haddad, K., Three Level DC-DC Converters as Efficient Interface in Two Stage PV Power Systems, IEEE Energy Tech, pp. 1-6, 2012.

- Kim, Y. S., Goo, T. H., Choi, J. H., Huh, D. Y., and Kwon, B. H., Novel Neutral-point Voltage Control of Three-level T-type Inverter, The Korean Institute of Power Electronics, Conf., Vol. 2015, No. 7, pp. 307-308, 2015.

- 15. Choi, U. M., Jeong, H. G., and Lee, K. B., Simple Neutral-Point Voltage Control of Grid-Connected 3-level NPC Inverter System, The Korean Institute of Power Electronics. Conf., Vol. 2011, No. 11, pp. 213-214, 2011.