JPE 17-1-27

https://doi.org/10.6113/JPE.2017.17.1.272 ISSN(Print): 1598-2092 / ISSN(Online): 2093-4718

# A New Reclosing and Re-breaking DC Thyristor Circuit Breaker for DC Distribution Applications

Jin-Young Kim\*, Seung-Soo Choi\*, and In-Dong Kim<sup>†</sup>

\*,†Department of Electrical Engineering, Pukyong National University, Busan, Korea

#### **Abstract**

The DC circuit breaker is essential for supplying stable DC power with the advent of DC transmission/distribution and sensitive loads. Compared with mechanical circuit breakers, which must interrupt a very large fault current due to their slow breaking capability, a solid-state circuit breaker (SSCB) can quickly break a fault current almost within 1 [ms]. Thus, it can reduce the damage of an accident a lot more than mechanical circuit breakers. However, previous DC SSCBs cannot perform the operating duty, and are not economical because many SCR are required. Therefore, this paper proposes a new DC SSCB suitable for DC grids. It has a low semiconductor conduction loss, quick reclosing and rebreaking capabilities. As a result, it can perform the operating duties of reclosing and rebreaking. The proposed DC SSCB is designed and implemented so that it is suitable for home dc distribution at a rated power of 5 [kW] and a voltage of 380 [V]. The operating characteristics are confirmed by simulation and experimental results. In addition, this paper suggests design guidelines so that it can be applied to other DC grids. It is anticipated that the proposed DC SSCB may be utilized to design and realize many DC grid systems.

Key words: DC circuit breaker, DC SSCB, Operating duty, Solid state circuit breaker (SSCB), Thyristor circuit breaker

#### I. Introduction

Recently, DC transmission/distribution has become a major concern because it can increase overall system power efficiency compared to existing AC transmission/distribution. Furthermore, since a lot of loads that are sensitive to short faults or voltage sags/swells are being widely utilized with the development of the IT industry, more reliable and stable power supply technologies are required [1], [2].

However, techniques regarding the stability of DC power grids are lacking compared to existing AC power grids. In addition, there is no zero crossing of the current in DC power grids while there is zero crossing of the current in AC power grids. Thus, in DC power grids there are some difficulties in breaking over-currents and short-circuit currents. In addition, unless short-circuit current is quickly cut off, more subsequent damage can occur due to electrical fires caused by electric arcs or sparks [3].

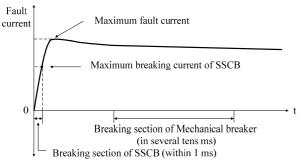

Fig. 1 shows the maximum currents and breaking times of

mechanical circuit breakers and SSCBs when short faults occur in a DC Grid. The mechanical circuit breakers are capable of breaking faults in about several tens of [ms] due to their physical structure, Thus, it is difficult for mechanical circuit breakers to prevent a lot of the damage caused by short-circuit faults because of their slow break capability [4].

In contrast, the SSCB can break faults within 1 [ms] at a much lower current level than the maximum fault current level, which reduces a lot of the damage to grid devices.

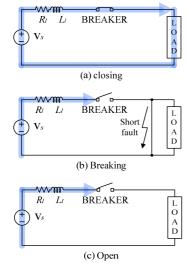

Fig. 2 shows the operation of a circuit breaker. In the normal state to transmit energy, it performs the closing operation as shown in Fig. 2-(a). If a short fault occurs, it performs the breaking operation as shown in Fig. 2-(b). However, as shown Fig. 2-(c), if the power line is held in the open state for a long time without supplying electric power after a power line is restored to normal operation, the power customers may receive a lot of consequent damages due to the electric power outage. For this reason, IEC-62271-100 prescribes the circuit breaker's operating duty that the reclosing and rebreaking operations of a circuit breaker should be able to be performed repeatedly. Therefore, a SSCB should break the fault quickly, and perform the operating duty.

There are several types of semiconductor switching

Manuscript received May 11, 2016; accepted Sep. 8, 2016 Recommended for publication by Associate Editor Yihua Hu.

<sup>\*</sup>Corresponding Author: idkim@pknu.ac.kr

Tel: +82-51-629-6318, Fax: +82-51-629-6305, Pukyong Nat'l Univ.

<sup>\*</sup>Dept. of Electrical Engineering, Pukyong National University, Korea

Fig. 1. Breaking section of mechanical circuit breaker and SSCB.

Fig. 2. Closing and breaking operation of DC circuit breaker.

elements such as the IGBT, GTO, GCT and SCR used to implement a SSCB. Among them the SCR is the most suitable for use in SSCBs because it is economical and its on-state loss is relatively small [5], [6]. However, since an AC SSCB using a SCR is based on AC grid characteristics that line commutation is possible, directly applying an AC SSCB to a DC grid can cause a lot of difficulties in terms of interrupting the fault current. Therefore, it is necessary to suggest a DC SSCB that is suitable for DC power grids [7]-[11].

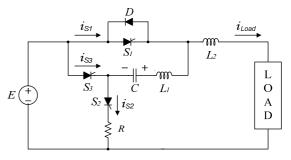

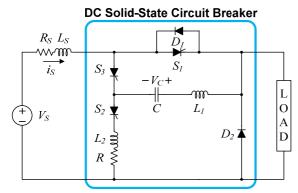

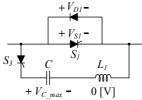

Fig. 3 shows a previously presented DC SSCB [10]. This SSCB supplies power through the main SCR  $S_1$ , and the capacitor C is charged when turning on the SCR  $S_1$  and  $S_2$ . If a fault occurs, the fault current is broken through the  $L_1$ -C resonance current ( $S_3$ -C- $L_1$ ) by turning on SCR  $S_3$ .

A large inductor  $L_2$  is used in this SSCB in order to limit the fault current when a short fault occurs. Therefore, a malfunction of the load may occur because the power source works as a kind of current source. In addition, this SSCB cannot perform the operating duty because it cannot recharge the commutation capacitor C under short circuits on the load side.

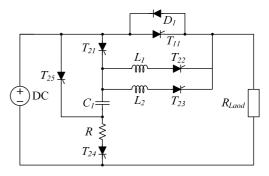

Fig. 4 shows another DC SSCB [11]. This SSCB supplies power through the main SCR T<sub>11</sub>. If a fault occurs, the fault

Fig. 3. Previous DC SSCB of Ref [10].

Fig. 4. Previous DC SSCB of Ref [11].

current is broken through the  $L_1$ - $C_1$  resonance current ( $T_{25}$ - $C_1$ - $L_1$ - $T_{22}$ ) by turning on the SCR  $T_{25}$  and  $T_{22}$ . This SSCB can perform the operating duty because it can recharge the capacitor. However, since many SCRs are used for the charging and recharging loop of the capacitor and the breaking loop in this SSCB, its economic feasibility is low. In addition, a complex control is required because it has many SCRs.

To overcome such shortcomings, this paper proposes a new DC SSCB that has a low semiconductor conduction loss, and quick reclosing and rebreaking capabilities. As a result, it can perform the operating duties of reclosing and rebreaking [12].

The proposed DC SSCB is designed and implemented at a rated power of 5 [kW] and a voltage of 380 [V] that is suitable for home dc distribution. The operating characteristics are confirmed by simulation and experimental results.

# II. PROPOSED DC SOLID-STATE CIRCUIT BREAKER

# A. Proposed DC SSCB

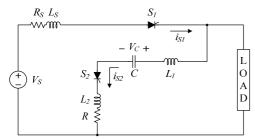

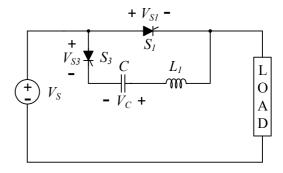

Fig. 5 shows the proposed DC SSCB circuit. In the normal mode of the SSCB, the energy is supplied to the load through  $S_1$ , and if a short-circuit fault occurs, the fault current is quickly broken by using the  $L_1$ -C resonance current  $i_{S3}$  through the resonant path of  $S_3$ -C- $L_1$ - $S_1$ . Since the number of the auxiliary switches is only two, one  $(S_2)$  for charging the commutation capacitor C and the other  $(S_3)$  for breaking the

Fig. 5. Proposed DC Solid-State Circuit Breaker.

Fig. 6. Operating modes of the proposed DC SSCB.

fault current, the structure of the DC SSCB is simple and economical. Furthermore, the proposed DC SSCB can perform the reclosing and rebreaking operations according to the operation duty because the recharging operation of the commutation capacitor C is possible even when a short-circuit fault lasts on the load side.

Fig. 6 shows the circuit operation modes of the proposed DC SSCB, and Fig. 7 shows the operation waveforms corresponding to each mode. As shown in Fig. 7, the operation of the proposed DC SSCB may be divided into four operation modes. The four operation modes are the charging mode  $(t_1 \sim t_2)$  to charge the commutation capacitor C, the normal mode  $(t_2 \sim t_4)$  to supply electric power to the load, the breaking mode  $(t_4 \sim t_8)$  to break the fault current, and the recharging mode  $(t_8 \sim t_9)$  to recharge the commutation capacitor.

Fig. 7. Operating waveforms of the proposed DC SSCB.

TABLE I

THE COMPARISON BETWEEN PREVIOUS DC SSCBS AND PROPOSED

DC SSCB

| Necessary<br>Functions and<br>components | previous<br>DC SSCB 1<br>(Fig 3) | previous<br>DC SSCB 2<br>(Fig 4) | Proposed<br>DC SSCB |

|------------------------------------------|----------------------------------|----------------------------------|---------------------|

| SCR                                      | 3                                | 6                                | 3                   |

| Diode                                    | 1                                | 1                                | 2                   |

| Inductor L                               | 2                                | 2                                | 2                   |

| Capacitor C                              | 1                                | 1                                | 1                   |

| Operating Duty                           | X                                | 0                                | 0                   |

At  $t_3$  in Fig. 7, when a short-circuit fault occurs, the fault current  $i_{\rm S3}$  rapidly increases. At  $t_4$ , when the fault current is three or four times higher than the full load current, the short-circuit fault is detected and the breaking mode begins. When the breaking mode is completed, the recharging mode to recharge the commutation capacitor begins in order to perform reclosing of the DC SSCB.

The operating characteristics at each mode are as follows.

# B. Operation Modes

# (a) Mode 1 (Charging mode: $t_1 \sim t_1' \sim t_2$ )

Charging the capacitor C must be preceded because the proposed DC SSCB breaks the fault current by using the  $L_1$ -C resonance current. Thus, at mode 1, the capacitor is charged

to a certain voltage required for breaking the fault current by turning on the SCR  $S_1$  and  $S_2$ .

At  $t_2$ , the charging of the commutation capacitor is already completed, the SCR  $S_2$  is naturally turned off, and the normal mode of the DC SSCB begins.

At  $t_2$ , the voltage of the commutation capacitor is higher than the source voltage E [V]. However, the charged voltage decreases due to natural discharge because the leakage resistance of the AC capacitor used in the DC SSCB is small. Thus, the voltage of the capacitor  $V_C$  decreases to the source voltage E [V].

#### (b) Mode 2 (Normal mode: $t_2 \sim t_3$ )

Since mode 2 is the normal operating mode of the DC SSCB, electric energy is supplied to the load through SCR S<sub>1</sub>. In addition, the DC SSCB monitors faults such as voltage sag/swell and short circuit current.

#### (c) Mode 3 (Normal mode: $t_3 \sim t_4$ )

Mode 3 is the section where the fault current increases after a short circuit fault occurs on the load side. Although the short circuit current increases from  $t_3$ , the SSCB operates in the normal mode because the magnitude of the fault current is still smaller than a preset reference value to determine the presence of a short circuit fault.

#### (d) Mode 4 (Breaking mode: $t_4 \sim t_5$ )

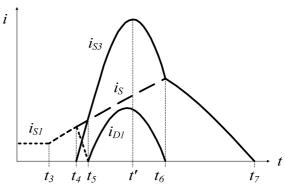

Mode 4 is the section where the SCR  $S_1$  is turned off. At  $t_4$ , when the SCR  $S_3$  is turned on, the  $L_1$ -C resonance current  $i_{S3}$  begins to flow. Thus, the  $L_1$ -C resonance current  $i_{S3}$  gradually increases. When the  $L_1$ -C resonance current  $i_{S3}$  becomes equal to the short circuit current  $i_{S}$  at  $t_5$ ,  $S_1$  is naturally turned off because the current  $i_{S1}$  becomes 0 [A].

#### (e) Mode 5 (Breaking mode: $t_5 \sim t_6$ )

At  $t_5$ , the  $L_1$ -C resonant current  $i_{S3}$  becomes larger than the short circuit current  $i_{S}$ . Thus, at  $t_5 \sim t_6$ , the current  $i_{D1}$  flows as much as the difference between the  $L_1$ -C resonance current  $i_{S3}$  and the short circuit current  $i_{S}$ .

At  $t_6$ , the  $L_1$ -C resonant current  $i_{S3}$  is the same as the short circuit current  $i_S$ , and the diode  $D_1$  is turned off.

#### (f) Mode 6 (Breaking mode: $t_6 \sim t_7$ )

At mode 6, since the SCR  $S_1$  and the diode  $D_1$  are turned off, the current  $i_{S3}$  is the same as the short circuit current  $i_{S3}$ . Therefore, the L-C resonant current flows depending on the combined inductance of the inductors  $L_S$  and  $L_1$ .

When the L-C resonance current  $i_{S3}$  gradually decreases to zero, the SCR  $S_3$  is naturally turned off at  $t_7$  and the capacitor C is reversely charged to the maximum voltage value.

### (g) Mode 7 (Breaking mode: $t_7 \sim t_8$ )

Mode 7 is the section where no current flows in the DC SSCB because all of the short-circuit current flowing through each device is interrupted.

#### (h) Mode 8 (Recharging mode: $t_8 \sim t_9$ )

Mode 8 is the section where the commutation capacitor is recharged before being discharged again in the next breaking mode. In the DC SSCB, the commutation capacitor should be

TABLE II

ELECTRICAL CHARACTERISTIC FOR DESIGN

| Mode             | Element              | electrical characteristic                     |  |

|------------------|----------------------|-----------------------------------------------|--|

| Charging mode    | $L_1$                | Inductance [uH], Peak current [A]             |  |

|                  | С                    | Capacitance [uF], Max voltage [V]             |  |

|                  | SCR S <sub>1</sub>   | Max voltage [V], Average current [A], tq [us] |  |

|                  | SCR S <sub>3</sub>   | Peak current [A]                              |  |

|                  | Diode D <sub>1</sub> | Max voltage [V], Peak current [A]             |  |

| Breaking<br>mode | $L_2$                | Inductance [uH], Peak current [A]             |  |

|                  | R                    | Resistance $[\Omega]$                         |  |

|                  | SCR S <sub>2</sub>   | Max voltage [V], Peak current [A]             |  |

|                  | SCR S <sub>3</sub>   | Max voltage [V],                              |  |

|                  | Diode D <sub>2</sub> | Max voltage [V], Peak current [A]             |  |

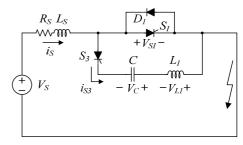

recharged to a certain voltage required for the re-break before performing the next reclosing operation. If SCR  $S_2$  is turned on, the capacitor is recharged through the path  $S_2$ - $L_2$ - $D_2$ - $L_1$ -C as shown in Fig. 6-(h). Thus, the proposed SSCB can recharge the commutation capacitors even under a short circuit fault on the load side.

When the recharging of the capacitor is complete, the SSCB should again perform the reclosing operation by turning on SCR S<sub>1</sub> regardless of the state of the load side in order to carry out the operation duty of the reclosing and rebreaking operations. When turning on SCR S<sub>1</sub>, if the short fault is already removed, the SSCB works in (b) mode 2 of Fig. 6. However, if the short-circuit fault still lasts, as shown in (c) mode 3 of Fig. 6, the SSCB rebreaks the fault current in Mode 4~7 and performs the recharging of the capacitor in Mode 8.

#### III. DESIGN OF THE PROPOSED DC SSCB

In order to design the proposed DC SSCB, a characteristic derivation of the voltage and current in each mode is required. Each component of the proposed DC SSCB has the maximum current and voltage in the breaking mode and recharging mode. Therefore, the capacity of the device should be determined considering the breaking mode and recharging mode. The electrical characteristic of the circuit components are considered according to each mode as shown in Table II.

#### A. Characteristic Derivation in the Charging Mode

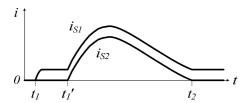

Fig. 8 shows an equivalent circuit of the charging mode, and Fig. 9 shows the waveforms of  $i_{S1}$  and  $i_{S2}$  in the charging mode. In section  $t_1$ ', if the SCR  $S_2$  is turned on, the underdamped current  $i_{S2}$  flows through the capacitor.

If the charging current  $i_{S2}$  is controlled as overdamped, quick break is impossible because the charging time becomes longer and too much time is spent until the SCR  $S_2$  is turned off. Therefore, the condition of the underdamped circuit is expressed as Equation (1), and the charging current  $i_{S2}$  is derived as Equation (2).

Fig. 8. Equivalent circuit of charging mode.

Fig. 9. i<sub>S1</sub> and i<sub>S2</sub> waveforms in charging mode.

$$R < 2\sqrt{\frac{L_{Th}}{C}} \qquad (L_{Th} = L_S + L_1 + L_2)$$

$$i_{S2}(t) = \frac{V_S}{L_{Th} \cdot \omega_d} e^{-\frac{R}{2L_{Th}}t} \cdot \sin(\omega_d \cdot t)$$

$$(\omega_d = \sqrt{\frac{1}{L_{Th}C} - \frac{R^2}{4L_{Th}^2}})$$

(2)

The maximum current of the charging mode does not have to be considered because it is less than the short circuit fault current.

### B. Characteristic Derivation in the Breaking Mode

Fig. 10 shows an equivalent circuit in the breaking mode (Mode  $4\sim7$ :  $t_4\sim t_8$ ) of the DC SSCB and Fig. 11 shows the current waveform of the devices in the breaking mode ( $t_4\sim t_8$ ).

At t<sub>3</sub>~t<sub>6</sub>, the short-circuit current i<sub>S</sub> is as follows:

$$i_S = i_{S1} = \frac{E}{L_S} (t - t_3) + i_{LOAD}$$

(3)

In Fig. 6-(d), the voltage equation is the same as Equation (4) because the SCR  $S_1$  is turned on and the resistance of the loop is almost 0  $[\Omega]$ . The  $L_1$ -C resonant current  $i_{S3}$  is expressed as Equation (5).

Thus, the maximum current flowing through the proposed DC SSCB is equal to equation (6) when a short fault occurs.

$$V_{S1} = -(V_C + V_{I1}) = 0 (4)$$

$$i_{S3} = \frac{E}{\sqrt{\frac{L_1}{C}}} \sin\left(\frac{t - t_4}{\sqrt{L_1 C}}\right) \qquad (t_4 \le t \le t_6)$$

(5)

$$i_{S3_{\text{max}}} = \frac{E}{\sqrt{\frac{L_1}{C}}} \text{ [A]}$$

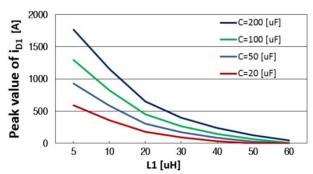

As Equation (6) implies, if the capacitance C becomes larger or the inductance of  $L_1$  becomes smaller, the peak value of the  $L_1$ -C resonance current  $i_{S3}$  becomes larger. If the

Fig. 10. Equivalent circuit of breaking mode (Mode  $4 \sim 7$ : $t_4 \sim t_8$ ).

Fig. 11.  $i_{S1}$ ,  $i_{S3}$ ,  $i_{S}$  and  $i_{D1}$  waveforms of breaking mode. (Mode  $4 \sim 7 : t_4 \sim t_8$ ).

peak value of the  $L_1$ -C resonant current  $i_{S3}$  becomes excessively larger, it is not economical because a large capacity of the SCR and diode are required. Therefore, the inductance  $L_1$  and the capacitance C should be properly selected considering the necessary ratings of SCR  $S_3$  and the diode.

If the inductance  $L_1$  is larger than the line inductance  $L_S$ , the SSCB cannot break the fault current. In order to break the fault current, the current  $i_{S3}$  should be higher than the short circuit current at  $t_5 \sim t_6$  in Fig. 11. Thus, if the inductance  $L_1$  is larger than the inductance  $L_S$ , the current is increases faster than  $i_{S3}$ . Thus, the current  $i_{S3}$  cannot be higher than the current  $i_{S4}$ .

The line inductance  $L_S$  varies depending on the installation environment of the SSCB and the point where the short circuit occurs. The line inductance  $L_S$  can be measured when the shortest short circuit fault point is determined. Since the line inductance  $L_S$  measured in experimental setup of this paper is 64 [uH], the inductance  $L_1$  should less than about 60 [uH]. The inductor  $L_1$  in this paper is designed to be 25 [uH].

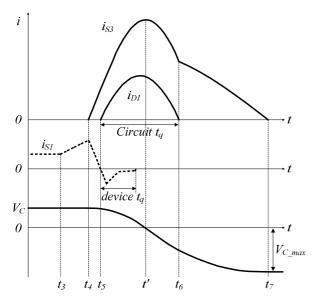

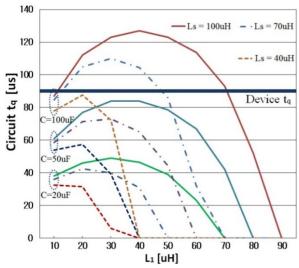

The capacitance C should be selected in order to secure the  $t_q$  (turn-off time) of the SCR  $S_1$ . Fig. 12 shows the circuit turn-off time  $t_q$  guaranteed by the circuit topology, and the device turn-off time  $t_q$  of the SCR  $S_1$  provided by the datasheets.

In order for SCR  $S_1$  to be turned off completely, the applied anode-to-cathode voltage  $V_{S1}$  should maintain a negative value for a longer duration than the device  $t_q$ . In

Fig. 12. Turn-off times of SCR S<sub>1</sub> and capacitor voltage V<sub>C</sub>.

Fig. 13. Circuit turn-off time  $t_q$  with the variations of  $L_S,\,L_1$  and C.

other words, the circuit turn-off time  $t_q$  should be longer than the device turn-off time  $t_q$  of the SCR  $S_1$  as expressed in equation (7).

$$device \ t_{a} < circuit \ t_{a} \tag{7}$$

Since the SCR  $S_1$  and the diode  $D_1$  are connected in parallel, as shown in Fig. 10, the reverse voltage of the SCR  $S_1$  is equal to the on-drop voltage of the diode. Therefore, if the conduction time of the diode corresponding to the circuit  $t_q$  satisfies equation (7), the SCR  $S_1$  can be turned off completely.

Fig. 13 shows the circuit turn-off time  $t_q$  for the main SCR  $S_1$  when the line inductance  $L_S$ , the inductor  $L_1$ , and the capacitor C vary. When the commutation capacitor C becomes larger, the circuit turn-off time  $t_q$  becomes longer. Therefore, if a sufficiently large capacitance is chosen, the SCR  $S_1$  can be

turned off stably. However, since too large a capacitor may be expensive, the capacitance C should be selected properly large, while ensuring that the circuit  $t_q$  is longer than the device  $t_q$ .

The device  $t_q$  shown in the data sheet of the SCR  $S_1$  is about 50[us] under a test condition voltage of 50[V]. In the proposed DC SSCB, since the reverse voltage of the SCR  $S_1$  is kept as low as the on-drop voltage, about 1.2[V], of the diode D1, the actual device  $t_q$  increases to approximately 1.8 times longer than the datasheet device  $t_q$ . Thus, considering the actual device  $t_q$  of 90(=50[us]x1.8) [us], shown in Fig. 13, the capacitance C should be selected, as shown in Fig. 13, so that the circuit  $t_q$  may be longer than the actual device  $t_q$  of 90 [us]. In this paper, when selecting a capacitance of 100 [uF], the device  $t_q$  of 110 [us] is secured.

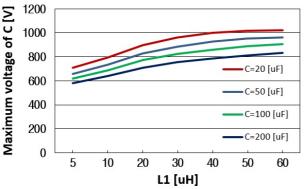

The rated voltage of the commutation capacitor C should be determined by section t' $\sim$ t<sub>7</sub> in Fig. 12. The capacitor C begins charging in the reverse direction, and has a maximum charging voltage V<sub>C\_max</sub> at t<sub>7</sub>. Therefore, the maximum voltage V<sub>C\_max</sub> of the commutation capacitor C can be obtained by equation (8) $\sim$ (11).

$$V_C(t_6) = E \cdot \cos(\frac{t_6 - t'}{\sqrt{L_1 C}}) \tag{8}$$

$$i_{S3}(t_6) = i_S(t_6) = \frac{E}{L_S}(t_6 - t_3) + i_{LOAD}$$

(9)

$$i_{S3}(t) = i_{S3}(t_6) \cdot \cos(\frac{t - t_6}{\sqrt{L_S + L_1}}) + \frac{E - V_C(t_6)}{\sqrt{\frac{L_S + L_1}{C}}} \cdot \sin(\frac{t - t_6}{\sqrt{(L_S + L_1)C}})$$

$$(t_6 \le t \le t_7) \tag{10}$$

$$V_{C_{-\max}} = -\frac{1}{C} \int_{t_6}^{t_7} i_{S3}(t) \cdot dt + V_C(t_6)$$

(11)

Fig. 14 shows the maximum voltage  $V_{C_{\_max}}$  of the capacitor C when the inductance  $L_1$  and the capacitance C vary.

Fig. 15 shows the voltages of a devices that performs the breaking operation at  $t \rightarrow t_7^-$  of Fig. 12. As shown in Fig 15, since the SCR S<sub>3</sub> is turned on until just before  $t_7$ , the maximum positive voltage of the SCR S<sub>1</sub> satisfies equation (12).

$$V_{C_{\max}}(t_7^-) = V_{S1_{\max}}(t_7^-) = V_{D1_{\max}}(t_7^-)$$

(12)

In addition, the reverse voltage of the SCR  $S_1$  is always the same as the on-drop voltage of the diode  $D_1$ . Therefore, the rated voltage of the SCR  $S_1$  should be determined considering its forward voltage, that is, the maximum voltage of the commutation capacitor.

The current flowing through the SCR  $S_1$  has a maximum value at  $t_4$  in Fig. 12, and it is three or four times higher than the average current (full-load current). Since the peak non-repetitive surge current of the SCR is approximately ten times higher than the mean on-state current, the SCR  $S_1$  can be selected considering only its average current.

Fig. 16 shows the maximum current of the diode  $D_1$  when  $L_1$  and C vary. Since the maximum voltage of the diode  $D_1$  is

Fig. 14. Maximum voltage  $V_{C\_max}$  of capacitor when  $L_1$  and C vary.

Fig. 15. Voltage of devices at  $t_7$  in breaking mode.

Fig. 16. Maximum current of diode D<sub>1</sub> when L<sub>1</sub> and C vary.

Fig. 17. Equivalent circuit of recharging mode.

the same as the voltage  $V_{C_{\_max}}$  of the capacitor C, the rated voltage of the diode  $D_1$  should be designed only considering the maximum voltage of the commutation capacitor C.

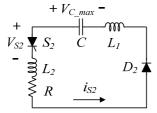

#### C. Characteristic Derivation in the Recharging Mode

Fig. 17 shows an equivalent circuit of the recharging mode. Since the SCR  $S_2$  and the diode  $D_1$  are turned on at  $t_8$ – $t_9$ , the voltage equation of the recharging mode is equal to equation (13).

The most important role of the recharging mode is to recharge the commutation capacitor to a certain voltage. It should be enough to re-break the SSCB. Therefore, the

Fig. 18. Equivalent circuit of SSCB at t<sub>9</sub> in Fig 7.

recharging current  $i_{S2}$  should be under damped. The condition where the recharging current  $i_{S2}$  becomes an underdamped current is equal to equation (14). The resistance R and inductor  $L_2$  can be selected by equation (14).

In the recharging mode, the recharging current equation is expressed as Equation (15), and the recharging voltage equation of the commutation capacitor C is expressed as Equation (16).

$$V_{C_{\max}} = (L_1 + L_2) \frac{di_{S2}}{dt} + R \cdot i_{S2} + \frac{1}{C} \int_{t_8}^{t_9} i_{S2}$$

(13)

$$R < 2\sqrt{\frac{L_1 + L_2}{C}} \tag{14}$$

$$i_{S2}(t) = \frac{V_{C \max}}{L \cdot \omega_d} e^{-\frac{R}{2L}t} \cdot \sin(\omega_d \cdot t)$$

$$(L = L_1 + L_2, \, \omega_d = \sqrt{\frac{1}{LC} - \frac{R^2}{4L^2}})$$

(15)

$$V_{C}(t_{9}) = \int_{t_{0}}^{t_{9}} i_{S2}(t) \cdot dt - V_{C \text{max}}$$

(16)

Since the capacitor is charged to E [V] in the charging mode, the recharged voltage of the capacitor should be E [V] or secure  $t_q$  of the SCR  $S_1$ . Therefore, the resistance R and the inductance  $L_2$  should be selected according to equations  $(14)\sim(16)$  so that the recharging voltage of the commutation capacitor  $V_C(9)$  is E [V].

All of the currents flowing through the resistance R, inductance  $L_2$ , SCR  $S_2$ , and diode  $D_2$  are the same. Therefore, if the resistance R and the inductance  $L_2$  are determined, the peak current of the SCR  $S_2$  and the diode  $D_2$  can be obtained by equation (15).

The SCR  $S_2$  is turned off at t $\rightarrow$ t8° in Fig. 17. Therefore, the voltage of the SCR  $S_2$  is the same as the maximum voltage  $V_{C\_max}$  of the commutation capacitor C.

Fig. 18 shows the equivalent circuit of the SSCB at  $t_9$  of Fig. 7. At  $t_9$ , the recharging mode is completed. Since the SCR  $S_1$  is in the off-state, the voltage  $V_{S1}$  of the SCR  $S_1$  is equal to  $V_S$ . In addition, the recharged voltage  $V_C$  of the capacitor is  $V_S$ . Therefore, the maximum voltage  $V_{S3}$  of the SCR  $S_3$  is  $2V_S$ .

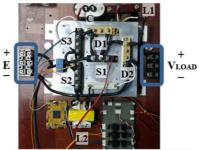

Fig. 19. Experimental device of proposed DC SSCB.

# TABLE III SYSTEM PARAMETERS

| Parameters                                     | Specification                                               |

|------------------------------------------------|-------------------------------------------------------------|

| Power rating                                   | 5 [kW], 380 [Vdc]                                           |

| Full load current                              | 13.1 [A]                                                    |

| Line impedance R <sub>S</sub> , L <sub>S</sub> | 50 [mΩ], 64 [uH]                                            |

| Range of trip setting                          | 13.1 [A] → 50 [A]                                           |

| Short fault switch resistance                  | 100 [mΩ]                                                    |

| $L_1$                                          | 23 [uH], i <sub>peak</sub> = 1000 [A]                       |

| $L_2$                                          | 400 [uH], i <sub>peak</sub> =500 [A]                        |

| С                                              | 100 [μF], 1200 [VAC]                                        |

| R                                              | 1 [Ω], 40 [W]                                               |

| SCR - SKKT 56/16E<br>(semikron, module type)   | 1600[V], i <sub>av</sub> =60[A], i <sub>peak</sub> =1500[A] |

| Diode - SKKD 81/16E<br>(semikron, module type) | 1600[V], i <sub>av</sub> =80[A], i <sub>peak</sub> =2000[A] |

#### IV. SIMULATION AND EXPERIMENTAL RESULTS

Fig. 19 shows an experimental prototype of the proposed DC SSCB. The design specifications and system parameters of the proposed DC SSCB are shown in Table 3. The simulation results are obtained through PowerSim (PSIM version 9.1) simulation software.

#### A. Charging Mode

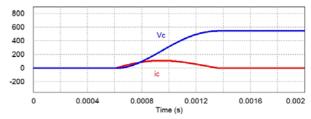

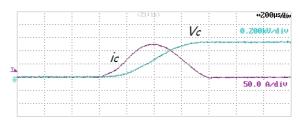

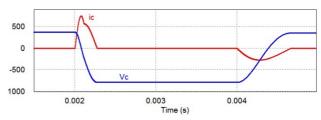

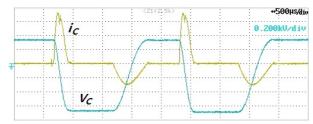

Fig. 20 shows simulation waveforms of the commutation capacitor voltage and current when the SCR  $S_1$  and  $S_2$  is turned on in the charging mode. Fig. 21 shows the measured waveform of Fig. 20.

# B. Breaking Mode

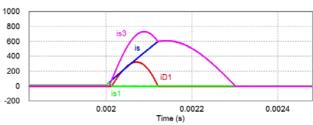

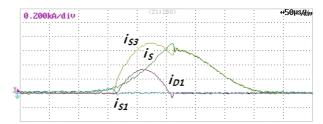

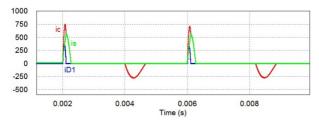

Fig. 22 shows simulation waveforms of  $i_S$ ,  $i_{S3}$ ,  $i_{S1}$  and  $i_{D1}$  in the breaking mode, and Fig. 23 shows measured waveforms of Fig. 22. It can be seen that the SCR  $S_1$  is turned off by the  $L_1$ -C resonant current  $i_{S3}$ , and that the fault current  $i_S$  is broken rapidly within 300 [usec].

#### C. Recharging Mode

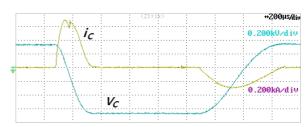

In the recharging mode of the proposed DC SSCB, it should be possible to recharge the capacitor even under a short circuit fault on the load side. Fig. 24 shows simulation waveforms of the capacitor voltage  $V_C$  and the current  $i_C$  in the recharging mode, and Fig. 25 shows measured waveforms

Fig. 20. Simulation waveforms  $V_{\text{C}}$  and  $i_{\text{C}}$  of charging mode.

Fig. 21. Measured waveforms  $V_{C}$  and  $i_{C}$  of charging mode.

Fig. 22. Simulation waveforms  $i_S,\ i_{S1},\ i_{S3}$  and  $i_{D1}$  of breaking mode.

Fig. 23. Measured waveforms  $i_S$ ,  $i_{S1}$ ,  $i_{S3}$  and  $i_{D1}$  of breaking mode.

Fig. 24. Simulation waveforms V<sub>C</sub> and i<sub>C</sub> of recharging mode.

Fig. 25. Measured waveforms  $V_C$  and  $i_C$  of recharging mode.

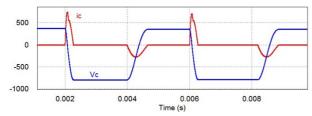

Fig. 26. Simulation waveforms V<sub>C</sub> and i<sub>C</sub>.

Fig. 27. Measured waveforms  $V_{\text{\tiny C}}$  and  $i_{\text{\tiny C}}.$

Fig. 28. Simulation waveforms i<sub>S</sub>, i<sub>C</sub> and i<sub>D1</sub>.

Fig. 29. Measured i<sub>S</sub>, i<sub>C</sub> and i<sub>D1</sub> waveforms.

of Fig. 24. It can be seen that the capacitor C is properly recharged by turning on the SCR  $S_2$ . Therefore, Fig. 24 and 25 confirm that the proposed DC SSCB can recharge the commutation capacitor even when a short-circuit fault lasts on the load side. Thus, it is able to reclose and rebreak repeatedly in the short-circuit fault on the load side.

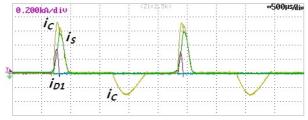

Fig. 26 shows the capacitor voltage  $V_{\rm C}$  and the capacitor current  $i_{\rm C}$  when performing the operation duty of reclosing and rebreaking, and Fig. 27 shows measured waveforms. In the case of a short circuit fault that lasts it can be verified that the rebreaking operation is properly performed through the detection of the short-circuit fault as soon as the DC SSCB is reclosed.

Fig. 28 shows simulation waveforms of the current  $i_S$ ,  $i_{D1}$  and  $i_C$  in the recharging and rebreaking modes, and Fig. 29 shows the measured waveforms of Fig. 28.

It can be seen that the DC SSCB sequentially performs breaking, recharging, reclosing, rebreaking, and recharging operations very well even when a short circuit fault lasts.

As shown in Fig. 8, 10 and 17, the stray inductance is connected to the inductor  $L_1$  or  $L_2$  in series, and it has a much lower value than the inductance  $L_1$  or  $L_2$ . Therefore, they do not affect the charging, breaking and recharging operations of the SSCB. As shown in Fig. 23, the effect of the stray capacitance occurs for a short time 10 [usec] from the time when the diode  $D_1$  is turned off. However, since the resonance current caused by the stray capacitance of the diode  $D_1$  has a very low value and the SCR  $S_1$  is already in the turn-off state, it has little effect on the breaking operation of the SSCB. Therefore, there is no need to consider parasitic components such as stray inductance and stray capacitance.

#### V. CONCLUSIONS

Since sensitive loads and DC distribution are used widespread, the DC SSCBs are essential to maintain the high power quality of the DC grid. Therefore, this paper proposes a new DC SSCB that has low conduction loss due to its main thyristor, simple structure, and good characteristic of rapid breaking within 300[usec] of short circuit faults. Furthermore, the manufacturing cost of the proposed DC SSCB can be reduced thanks to lower rated devices and a reduced number of auxiliary SCRs. It can also perform the operating duty of reclosing and rebreaking since the recharging operation of the capacitor is possible regardless of the fault state on the load side.

The operating characteristics of the proposed DC SSCB are verified by simulations and experiments under short circuit faults. In addition, this paper suggests design guidelines so that it can be applied to other DC grids. It is anticipated that the proposed DC SSCB may be utilized to design and realize many DC grid systems.

#### ACKNOWLEDGMENT

This work was supported by a Research Grant of Pukyong National University(2015 year).

# REFERENCES

- D. Salomonsson and A. Sannino, "Low-voltage DC distribution system for commercial power systems with sensitive electronic loads," *IEEE Trans. Power Del.*, Vol. 22, No. 3, pp. 1620-1627, Jul. 2007.

- [2] C.-N. Lu and C.-C. Shen, "Estimation of sensitive equipment disruptions due to voltage sags," *IEEE Trans. Power Del.*, Vol. 22, No. 2, pp. 1132-1137, Apr. 2007.

- [3] G. Parise and L. Parise, "Unprotected faults of electrical and extension cords in AC and DC systems," *IEEE Trans. Ind. Appl.*, Vol. 50, No. 1, pp.4-9, Jan./Feb. 2014.

- [4] S. Lee and H. Kim, "A study on low-voltage DC circuit breakers," in *IEEE International Symposium on Industrial Electronics (ISIE)*, pp. 1-6, May 2013.

- [5] C. Meyer, S. Schroder, and R. W. De Doncker,

- "Solid-state circuit breakers and current limiters for medium-voltage systems having distributed power systems," *IEEE Trans. Power Electron.*, Vol. 19, No. 5, pp. 1333-1340, Sep. 2004.

- [6] C. Meyer, S. Schroder, and R. W. De Doncker, "Solid-state circuit breakers and current limiters for medium-voltage systems having distributed power systems," *IEEE Trans. Power Electron.*, Vol. 19, No. 5, pp. 1333-1340, Sep. 2004.

- [7] M. Steurer, K. Ferohlich, W. Holaus, and K. Kaltenegger, "A novel hybrid current-limiting circuit breaker for medium voltage principle and test results," *IEEE Trans. Power Del.*, Vol. 18, No. 2, pp. 460-467, Apr. 2003

- [8] F. Luo, J. Chen, X. Lin, Y. Kang, and S. Duan, "A novel solid state fault current limiter for DC power distribution network," in 23<sup>rd</sup> Annual IEEE Applied Power Electronics Conference and Exposition (APEC), pp. 1284–1289, Feb. 2008.

- [9] J. Mu, L. Wang, and J. Hu, "Analysis and design of topological structure for DC solid-state circuit breaker," in 2009 World Non-Grid-Connected Wind Power and Energy Conference (WNWEC), pp.1-5, Sep. 2009.

- [10] J.-Y. Kim, I.-D. Kim, and E.-C. Nho, "A novel DC solid -state circuit breaker for DC grid," *The Transactions of the Korean Institute of Power Electronics*, Vol. 17, No. 4, pp. 368-376, Aug. 2012

- [11] J.-G. Mu, L. Wang, and J. Hu, "Research on main circuit topology for a novel DC solid-state circuit breaker," in 5th IEEE Conference on Industrial Electronics and Applications (ICIEA), pp. 926–930, Jun. 2010.

- [12] J.-Y. Kim, S.-S. Choi, and I.-D. Kim, "A novel reclosing and rebreaking DC solid state circuit breaker," in 9th International Conference on Power Electronics and ECCE Asia (ICPE-ECCE Asia), pp.1282-1288, Jun. 2015.

Jin-Young Kim received his B.S. degree in Electrical Engineering from Pukyong National University, Busan, Korea, in 2004; his M.S. degree in Electrical Engineering from Pusan National University, Busan, Korea, in 2006; and his Ph.D. degree in Electrical Engineering from Pukyong National University, Busan, Korea, in 2014.

His current research interests include solid-state circuit breakers and their applications.

degrees in Electrical Engineering from Pukyong National University, Busan, Korea, in 2013 and 2015, respectively, where he is presently working towards his Ph.D. degree. His current research interests include power electric control, power converters and power

Seung-Soo Choi was born in Busan, Korea,

in 1982. He received his B.S. and M.S.

amplifiers.

**In-Dong Kim** received his B.S. degree in Electrical Engineering from Seoul National University, Seoul, Korea, in 1984; and his M.S. and Ph.D. degrees in Electrical and Electronic Engineering from the Korea Advanced Institute of Science and Technology (KAIST), Daejeon, Korea, in 1987 and 1991, respectively. From 1991 to

1996, he was a Principal Engineer at the Rolling Stock R&D Center of Daewoo Heavy Industries, Ltd., Korea. From 1997 to 1998, he did Post-Doctoral research in the Department of Electrical and Computer Engineering, University of Tennessee, Knoxville, TN, USA. From 2004 to 2005, he served as a Visiting Professor in the Bradley Department of Electrical Engineering, Virginia Tech, Blacksburg, VA, USA. From 2012 to 2013, he served as a Visiting Professor in the FREEDM Systems Center, North Carolina State University, Raleigh, NC, USA. He has been a Senior Member of the IEEE since February 2007. In 1996, he joined the Department of Electrical Engineering, Pukyong National University, Busan, Korea, where he is presently working as a full Professor. His current research interests include power electronics, motor drives, power quality control, renewable distributed power sources, and DSP-based control of power converters. He became the vice president of KIPE, Seoul, Korea, in 2016.