# Journal of the Korea Institute of Information and Communication Engineering

한국정보통신학회논문지(J. Korea Inst. Inf. Commun. Eng.) Vol. 21, No. 11: 2009~2014 Nov. 2017

# 시정수 비교기를 이용한 작은 크기의 위상고정루프

고기영<sup>1\*</sup> · 최영식<sup>2</sup>

## Small-size PLL with time constant comparator

Gi-Yeong Ko<sup>1\*</sup> · Young-Shig Choi<sup>2</sup>

<sup>1\*</sup>Department of Electronic Engineering, Pukyong National University, Busan 48513, Korea

<sup>2</sup>Department of Electronic Engineering, Pukyong National University, Busan 48513, Korea

#### 요 약

본 논문에서는 변화하는 루프필터 전압을 시정수 비교기를 사용하여 감지하고, 이의 출력에 따라 루프필터 전압 변화를 보상하여 단일 칩으로 구현이 가능한 작은 크기의 위상고정루프를 제안하였다. 제안된 위상고정루프는 기존 구조에서는 안전한 동작이 불가능한 크기인 작은 용량을 가지는 커패시터를 사용하여 칩의 크기를 최소화 하였다. 시정수 비교기는 작은 시정수 값을 가지는 저항, 커패시터와 높은 시정수 값을 가지는 저항, 커패시터를 통과한 신호들을 입력으로 받아 루프필터 출력 전압의 변화를 감지한다. 시정수가 큰 노드의 출력은 루프필터 출력전압의 평균 값을 가지고, 시정수가 작은 노드의 출력은 루프필터 출력전압과 거의 같은 값을 가진다. 각 노드의 차이를 비교하여 나온 출력은 전류 보상기를 제어하여 작은 크기의 루프필터 커패시터를 충 방전 시킨다. 이는 제안된 위상고정루프를 안정하게 동작하도록 한다. 제안된 위상고정루프는 1.8V 0.18µm CMOS 공정을 사용하여 설계하였고, Hspice 시뮬레이션을 통해 회로의 동작을 검증하였다.

#### **ABSTRACT**

A novel structure of phase locked loop (PLL) with a time constant comparator and a current compensator has been proposed. The proposed PLL uses small capacitors which are impossible for stable operation in a conventional PLL. It is small enough to be integrated into a single chip. The time constant comparator detects the loop filter output voltage variations using signals which are passed through small and large RC time constants. The signal from the large RC time constant node is the average of the loop filter output voltage. The output voltage of another node is approximately equal to the present loop filter voltage. The output of the time constant comparator controls a current compensator and charge/discharge small size loop filter capacitors. It makes the proposed PLL operate stably. It has been simulated and proved by HSPICE in a CMOS 0.18µm 1.8V process.

키워드: 위상고정루프, 시정수 비교기, 집적화회로, 전류 보상기

Key word: Phase locked loop, Time Constant Comparator, Small-size, Current compensator

Received 11 July 2017, Revised 28 July 2017, Accepted 12 October 2017

\* Corresponding Author Gi-Yeong Ko(E-mail: qw8956@daum.net, Tel: +82-51-629-6222) Department of Electronic Engineering, Pukyong National University, Busan 48513, Korea

Open Access https://doi.org/10.6109/jkiice.2017.21.11.2009

print ISSN: 2234-4772 online ISSN: 2288-4165

©This is an Open Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License(http://creativecommons.org/li-censes/ by-nc/3.0/) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited. Copyright © The Korea Institute of Information and Communication Engineering.

#### Ⅰ. 서 론

위상고정루프는 각종 무선 통신 시스템과 고속의 시스템이 필요로 하는 다양한 주파수를 가진 신호와 고속 클록 신호를 만드는 것 등에 널리 사용되고 있다. 최근 통신 장비의 고속화 및 고주파수화 추세를 만족시키기위해 빠른 위상고정시간과 낮은 위상잡음, 좋은 지터특성을 실현하기위한 연구들이 활발하게 진행되고 있다. 또한 칩의 소형화가 불가피해지게 되면서 넓은 면적을 차지하는 커패시터를 사용하는 위상고정루프와같은 회로에서 커패시터의 크기를 줄이는 것은 매우 중요한 일이다. 위상고정루프에서 가장 큰 면적을 차지하는 루프필터의 커패시터를 줄이는 것은 칩의 크기를 줄일수 있고, 위상고정루프의 집적화에 도움이 된다.

넓은 주파수 동작범위와 크기가 작은 링 전압제어 발진기를 사용하는 위상고정루프는 잡음을 낮추기 위 해 적절한 대역폭이 필요하다[1]. 하지만 좁은 대역폭 은 큰 커패시터 용량을 필요로 한다. 이는 루프필터가 집적화를 불가능하게 하여 루프필터를 칩 외부에 배 치하게 만든다. 이를 위해 작은 커패시턴스 용량으로 큰 커패시턴스 용량이 된 것처럼 역할을 할 수 있게 많 은 연구가 진행되고 있다[2]. 지터의 크기를 줄이기 위 해서 능동 루프필터와(ALF)[3] 두 개의 링 구조 전압 제어발진기 기술이[4] 제안되었다. 이와 같은 방법은 LDO-regulator를 사용하므로 직류 공급 전압을 높은 것 과 출력 리플 전압이 잡음을 증가시키는 문제점을 가지 고 있다. 두 개의 루프와 능동 루프필터를 사용하기 때 문에 구조가 복잡하고 추가적인 잡음 특성에 영향을 미 친다. Sampled-feedforward 루프필터를 추가여 작은 크 기의 커패시터로 루프필터를 구현하였다[5]. 이 구조에 서는 기준 신호 한주기마다 MOSFET으로 만들어진 스 위치를 통해 전하를 전달해야 하므로 커패시터를 줄이 면 기준 신호 스퍼가 커지게 된다. 빠른 위상 고정시간 과 낮은 위상 잡음 특성을 얻기 위해 단계적 대역폭 변 화 방식을 이용한 디지털 위상고정루프[6]를 구현하였 다. [6]에서의 단계적 루프 대역폭 조절기는 복잡한 구 조의 디지털 블록으로 만들어지기 때문에 칩의 전체적 인 크기가 커지고, 동작 속도가 느리며 소비전력이 증 가하는 문제를 가지고 있다. 빠른 위상고정 시간과 넓 은 대역폭, 좋은 지터 특성을 얻기 위해 새로운 적응적 위상고정루프 구조를 구현하였다[7]. [7]에서의 제안된 위상고정루프 구조는 새로운 전하펌프 구조와 루프필 터의 저항변화로 빠른 위상고정 시간과 낮은 위상잡음 특성 및 좋은 지터특성을 얻을 수 있지만 2차 루프필터 의 사용으로 인해 칩의 전체적인 크기가 커지게 된다. 시정수 비교기와 추가적인 보조 전하펌프를 사용하여 루프필터 전압 변동 폭을 억제하는 위상고정루프를 구 현하였다[8]. [8]에서의 추가적인 보조 펌프는 위상고정 루프의 주 전하펌프로 들어가서 전류를 보상시켜 준다. 전하펌프로 들어가게 되면 위상여유를 고려해야 하므로 루프 필터의 커패시턴스와 저항의 크기를 줄일 수가 없다.

본 논문에서는 변화하는 루프필터 전압을 시정수 비교기를 사용하여 감지하고 이를 전류 보상기를 사용하여 다시 루프필터로 직접 보상해주는 회로를 제안하였다. 이를 통해 한 주기 동안 발생하는 초과 위상 변위의 크기를 줄일 수 있다. 그러므로 위상여유 문제로 인해루프 필터의 커패시턴스와 저항의 크기를 줄일 수 없는 기존 구조와 달리 작은 크기의 커패시터를 사용하여 위상고정루프를 구현하고, 지터 특성도 개선할 수 있었다. 제안된 구조를 통해서 루프필터 커패시터의 크기가 작더라도 안정하게 동작하도록 하여 단일 칩으로 집적화가 가능하도록 하였다.

#### Ⅱ. 제안한 위상고정루프의 구조

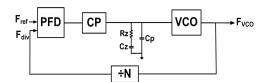

기존의 위상고정루프(PLL)구조는 그림 1과 같이 위상 주파수 검출기(PFD), 전하펌프(CP), 루프 필터(LF), 전압제어발진기(VCO), 분주기(Divider)로 구성된다. 위상고정루프가 안정된 동작을 위해서는 충분한 위상여유를 가져야 한다. 이를 위해서는 그림 1의 루프필터에서  $C_z$ 의 크기가  $C_p$ 의 크기보다 10배이상 되도록 하여 충분한 위상여유를 가지도록 하는 것이 일반적인설계 방법이다. 그러나 이러한 기준 구조는 영점을 결정하는  $C_z$ 의 크기가 커져서 하나의 칩으로 구현하는 것이 쉽지 않다.

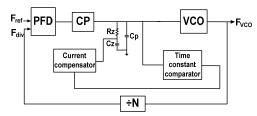

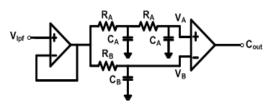

그림 2의 위상고정루프는 작은 값의 C<sub>2</sub>를 사용하여 하나의 칩으로 구현이 가능하고, 빠른 위상고정시간을 가지는 회로를 제안하였다. 제안된 위상고정루프는 논 문 [8]의 시정수 비교회로를 병렬 구조로 바꾸어 커패시 터 크기를 줄여 사용하였다. 루프필터 출력 전압이 시 정수 비교기로 들어가서 전류 보상기를 제어하여  $C_z$ 의 전압을 제어하도록 하였다.

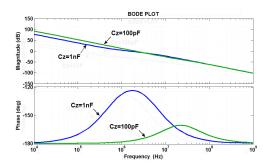

그림 3은 기존 구조일 때의 커패시턴스 크기, Cp가 100pF이고, Cz가 1nF와 제안된 구조일 때의 커패시턴 스 크기인 Cp와 Cz 둘 다 100pF일 때의 개 루프 전달 특 성과 위상여유를 보여주고 있다. 그림 3에서 나타난 봐 와 같이 Cz가 Cp의 크기보다 10배 이상 크게 할 때는 위 상고정루프는 충분한 위상 여유를 가지나, 제안된 구조 의 위상고정루프에서 사용될 C<sub>p</sub>와 같은 크기를 가질 때 는 안정된 동작을 위한 위상여유가 충분하지 않음을 보 여주고 있다. 이는 기준 신호 한 주기 당 발생하는 위상 변위가 C2와 C3의 크기가 같을 때는 과도하다는 것을 나타낸다. 기준신호 한 주기 당 발생하는 위상 변위의 크기를 결정하는 루프필터 출력 전압 파형에 가장 큰 영향을 미치는 Cz의 전압을 제어하는 시정수 비교 회로 와 전류 보상기를 도입하였다. 추가된 회로들은 C<sub>z</sub>와 C<sub>n</sub> 의 크기가 같을 때도 기준 신호 한 주기 당 발생하는 위 상 변위가 크지 않도록 하여 제안된 구조의 위상고정루 프가 안정하게 동작하도록 해준다.

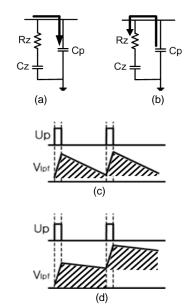

그림 4는 위상 주파수 검출기에서 UP 신호가 발생하였을 때 2차 루프필터의  $C_p$ 와  $C_z$ 에서 시간에 따라 전하가 움직이는 방향과, 이에 따른 전압파형을 보여주고 있다. 그림 4(a)에서 위상주파수검출기에서 UP신호가 발생하게 되면 시정수가 낮은  $C_p$ 로 대부분의 전류가 흘러 충전이 된다. 그에 따라 루프필터 전압  $V_{LPF}$ 의 값은 증가하게 된다. UP신호가 사라지면 그림 4(b)와 같이  $C_p$ 에 충전되어 있던 전하가  $C_p$ 와 C고쪽으로 방전이 되면서  $C_p$ 에 충전되어 있던 전하가  $C_p$ 와 같이  $C_p$ 가  $C_p$ 보다  $C_p$ 보

$$\Delta \phi_{out}(t) = K_{VCO} \int \Delta V_{cont} dt \tag{1}$$

그러므로 기존 구조의 2차 루프필터를 가진 위상고 정루프는 안정하게 동작한다. 제안된 구조처럼 하나의 칩으로 구현하기 위해  $C_z$ 의 값이 작아져  $C_p$ 와 비슷한 경우 그림 4(d)와 같이  $V_{LPF}$  파형이 하나의 커패시터로 구성된 1차 루프필터를 사용했을 때와 비슷한 형태가

된다. 그림 4(d)에 나타난 봐와 같이 면적이(줄친 부분) 증가하고, 이에 따라 한 주기 당 발생하는 위상 변위가 커져서 위상고정루프는 불안하게 동작한다.

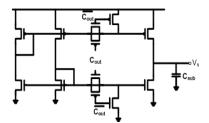

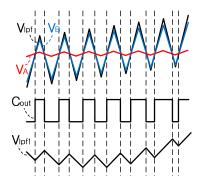

제안된 위상고정루프에서 시정수 비교기(TCC: Time Constant Comparator)와 전류 보상기는 위상고정 루프를 하나의 칩으로 구현하기 위해 Cz를 Cp와 거의 같은, 작은 크기로 사용한 2차 루프필터에서도 위상고 정루프가 안정하게 동작하여 위상이 고정될 수 있도록 도와주는 역할을 한다. 그림 5는 제안된 위상고정루프 에 사용된 시정수 비교기 회로이다. 시정수가 큰 노드 의 출력인  $V_4$ 는 루프 필터 출력 전압 평균값을 가지고, 시정수가 작은 노드의 출력인  $V_{B}$ 는 루프 필터 출력 전 압 값과 거의 같은 값을 가진다. 시정수 비교기 회로는 루프필터 전압을 입력으로 받아서 시정수가 큰  $R_4$ 와  $C_A$ 부분을 거친  $V_A$ 와 시정수가 낮은  $R_B$ 와  $C_B$ 부분을 거친  $V_B$ 의 차이를 비교한다. 비교한 결과는 그림 6의 전류 보상기의 입력으로 들어가게 된다. 그림 7에서  $V_{R}$ 가  $V_A$ 보다 크면, 즉 현재 루프필터 출력 전압 값이 평 균값보다 크면 출력  $C_{out}$ 에는 'HIGH'가 나오고,  $V_A$ 가  $V_B$ 보다 크면, 즉 현재 루프필터 출력 전압 값이 평균값 보다 작으면 Cout이 'LOW'가 된다. 출력 Cout은 전류 보 상기의 입력으로 들어가 루프필터 C,을 충전하거나 방 전하여 루프 필터 출력 전압을 제어하는 역할을 하게 된다. 그림 7에서  $V_{sub}$  파형은 전류 보상기를 구동하기 위해 시정수 비교회로 출력단에 버퍼를 연결하여 만든 신호이다. Cout이 'HIGH' 일 경우 Csub를 방전시켜 루프 필터  $C_z$ 에서  $C_{sub}$ 로 전하를 흐르도록 하여  $C_z$  전압, 즉 루프 필터 출력 전압을 하강하도록 한다. Cout이 'LOW' 일 경우  $C_{sub}$ 를 충전시켜 루프필터  $C_{sub}$  에서  $C_z$ 로 전하 를 흐르도록 하여  $C_z$  전압, 즉 루프 필터 출력 전압을 증 가하도록 한다. 이를 통해 Cp와 거의 같은 작은 크기의  $C_z$ 로 인하여  $C_p$ 의 전하가  $C_z$ 로 충·방전이 제대로 일어 나지 못하여, 그림 4 (d)와 같은 루프필터 출력 전압파 형을 그림 4 (c)와 같은 루프필터 출력 전압파형으로 만 들어 준다. 시정수 비교 회로와 전류 보상기는 하나의 칩으로 구현할 수 있도록 크기를 줄인 커패시터를 사 용하여도 한 주기 당 발생하는 초과 위상 변위를 감소 시켜 제안된 위상고정루프가 안정하게 동작하도록 하 여 지터 크기를 줄여준다.

Fig. 1 Conventional PLL

Fig. 2 Proposed PLL

Fig. 3 Open loop transfer function and phase margin

Fig. 4 2<sup>nd</sup> Loop filter and voltage waveform

Fig. 5 Proposed unit gain buffer and TIme Constant Comparator circuit

Fig. 6 Proposed current compensator

Fig. 7 Proposed TCC circuit and current compensator operation waveform

### Ⅲ. Simulation 결과

제안한 구조의 위상고정루프는  $0.18 \mu m$  CMOS 공정 파라미터를 사용하여 Hspice로 시뮬레이션을 수행하였고, 동작을 검증하였다. 15.625 MHz의 입력 주파수를 가지고 분주 비는 64분주이며, 출력주파수는 1GHz이다. 사용된 루프필터 파라미터 값은  $R_z=100\Omega$ ,  $C_z=100 p F$ ,  $C_p=100 p F$ 이고, 전하펌프의 전류량은  $I_p=100 \mu A$ , 전압제어 발진기이득  $K_{vco}=330 MHz/V$ , 전류 보상기의 전류량은  $1 \mu A$ 이다. 시정수 비교기 회로에 사용된 파라미터 값은  $C_A=50 p F$ ,  $C_B=1 p F$ ,  $C_A=50 \mu A$

이다. 보조 전하펌프에 사용된 커패시터,  $C_{sub}$ 는 0.1pF이다. 칩의 크기를 결정하는 사용된 커패시터 용량은 모두 301.1pF이며, 이는 제안된 위상고정루프를 단일 칩으로 구현을 가능하게 해준다.

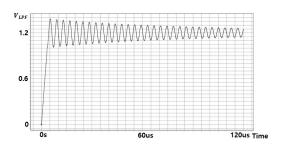

기존의 위상고정루프 구조에서 루프필터의 C<sub>2</sub>와 C<sub>p</sub>를 같은 크기의 100pF로 하였을 때의 루프 필터 출력전 압파형은 그림 8에서와 같이 발진하는 것을 확인 할 수 있다. 그림 9는 제안된 구조에서 C<sub>2</sub>와 C<sub>p</sub>를 같은 크기의 100pF로 하였을 때 루프 필터 출력 전압이 수렴하는 것을 보여주고 있다. 추가된 시정수 비교 회로와 보조 전 하펌프는 2장에 설명한 것과 동작하여 제안된 위상고정 루프를 안정하게 동작하도록 하였다. 그림 10은 제안된 위상고정루프의 지터를 측정하기 위해 시뮬레이션 한 결과이다. 그림 9 (b)에 나타난 봐와 같이 지터를 크기를 결정하는 위상 고정 후의 루프 필터 출력 전압 변동 폭은 380µV이다.

그림 10 (a)는 루프필터 파라미터 값이  $R_x=1k\Omega$ ,  $C_z=1nF$ ,  $C_p=100pF$  일 때의 지터 값이고, 그림 10 (b)는 작은 면적을 가지고 제안된 구조를 사용한 회로의 지터 이다. 그림 10 (a)의 경우 칩의 면적을 좌우하는 커패시터와 저항의 면적은 180nm공정에서 총 550,566  $\mu m^2$ 이다. 그림 10 (b)의 경우 루프필터와 시정수비교기의 사용된 커패시터와 저항의 면적은 총 153,437  $\mu m^2$ 이다. 그러므로 제안된 시정수 비교기를 사용함으로써 칩 전체 크기를 좌우하는 커패시터와 저항의 면적을 약 1/3.6로 줄일 수 있고, 지터특성 또한 135ps에서 105ps로 개선시킬 수 있다. [8]과 달리 이 구조에서는 루프필터의 커패시턴스 크기를 줄임에도 불구하고 기준 신호한 주기 동안 발생하는 초과 위상변위 크기를 줄일 수 있어 지터 특성을 개선 할 수 있었다.

Fig. 8  $V_{LPF}$  waveform of PLL without current compensator

Fig. 9 Proposed PLL (a)  $V_{LPF}$  waveform after locking (b) Enlarged  $V_{LPF}$  waveform after locking

Fig. 10 (a) Conventional and (b) proposed PLL jitter characteristic

#### Ⅳ. 결 론

본 논문에서는 위상고정루프를 하나의 칩으로 구현하기 위해 작은 크기의 루프필터 커패시턴스를 사용함에 따라 불안정하게 동작하는 기존 구조의 위상고정루프에 시정수 비교기와 전류 보상기를 사용하여 안정하

게 동작하여 위상을 고정시키는 위상고정루프를 제안하였다. 제안된 위상고정루프는  $C_z$ 와  $C_p$ 의 크기가 비슷하더라도 시정수 비교기를 사용해 루프필터 전압을 비교하고 이를 전류 보상기를 사용하여 보상해주어 한주기 동안 발생하는 초과 위상 변위를 감소시켜 안정성을확보하였다. 또한 기존 구조 위상고정루프의 지터 특성보다 개선된 지터 특성을 가질 수 있도록 해준다.

#### **ACKNOWLEDGMENTS**

This work was supported by a Research Grant of Pukyong National University (2017-2018)

#### **REFERENCES**

- [1] H. Y. Chang, Y. L. Yeh, Y. C. Liu, M. H. Li, and K. Chen, "A low-jitter low-phase-noise 10-GHz sub-harmonically injection-locked PLL with self-aligned DLL in 65-nm CMOS technology," *IEEE Transactions on Microwave Theory and Techniques*, vol. 62, no. 3, pp. 543-555, Mar. 2014.

- [2] B. Catli, A. Nazemi, T. Ali, S. Fallahi, Y. Liu, J. Kim, M. Abdul-Latif, M. R. Ahmadi, H. Maarefi, A. Momtaz, and N. Kocaman, "A sub-200fs RMS jitter capacitor multiplier loop

- filter-based PLL in 28 nm CMOS for high-speed serial communication applications," *IEEE Custom Integrated Circuits Conference*, pp. 1-4, Nov. 2013.

- [3] G. Jeon, K. K. Kim and Y. B. Kim, "A low jitter PLL design using active loop fiter and low-dropout regulator for supply regulation," *International SoC Design Conference (ISOCC)*, pp. 223-224, Nov. 2015.

- [4] G. Blasco, E. Isern, E. Martin, "Design of a stable pulse generator system based on a Ring-VCO Phase-Locked Loop using 180nm CMOS technology," *IEEE Design of Circuits* and Integrated Systems (DCIS), pp. 25-27, Nov. 2015.

- [5] J. Kim, J. Kim, B. Lee, N. Kim, D. Jeong, and W. Kim, "A 20-GHz phase-locked loop for 40-Gb/s serializing transmitter in 0.13-µm CMOS," *IEEE J. Solid-State Circuits*, vol. 41, no. 4, pp. 899-908, Apr. 2006.

- [6] D. W. Jee, J. Y. Sim and D. Blaauw, "Digitally Controlled Leakage-Based Oscillator and Fast Relocking MDLL for Ultra Low Power Sensor Platform," *IEEE Journal of Solid-State Circuits*, vol. 50, no. 5, pp. 1263-1274, May 2015.

- [7] M. Ghasemzadeh, S. Mahdavi, A. Zokaei, K. Hadidi, "A New Adaptive PLL to Reduce the Lock Time in 0.18µm technology," MIXDES-23rd International Conference Mixed Design of Integrated Circuits and Systems, pp. 140-142, June 2016.

- [8] S. J. An and Y. S. Choi, "Loop filter voltage variation compensated PLL with charge pump," *Journal of Korea Institute of Information and Communication Engineering*, vol. 20, no. 10, pp. 1935-1940, Oct. 2016.

고기영(Gi-Yeong Ko)

2016년 부경대학교 전자공학과 학사 졸업. 2016년 부경대학교 전자공학과 석사 입학. ※관심분야: PLL, DLL 설계

최영식(Young-Shig Choi)

1982년 경북대학교 전자공학과 학사 졸업. 1986년 Texas A&M University 전자공학과 석사 졸업. 1993년 Arizona State University 박사 졸업. 1987년 ~ 1999년 현대전자(현 SK Hynix) 책임연구원 2003년 ~ 현재 부경대학교 전자공학 교수 ※관심분야: PLL, DLL 설계