# 차세대 웨어러블 전자시스템용 실리콘 나노선 트랜지스터 연구

http://dx.doi.org/10.5757/vacmac.3.3.15

임경민, 김민석, 김윤중, 임두혁, 김상식

Research on Silicon Nanowire Transistors for Future Wearable Electronic Systems

Kyeungmin Im, Minsuk Kim, Yoonjoong Kim, Doohyeok Lim, and Sangsig Kim

In future wearable electronic systems, 3-dimensional (3D) devices have attracted much attention due to their high density integration and low-power functionality. Among 3D devices, gate-all-around (GAA) nanowire transistor provides superior gate controllability, resulting in suppressing short channel effect and other drawbacks in 2D metal-oxide-semiconductor field-effect transistor (MOSFET). Silicon nanowires (SiNWs) are the most promising building block for GAA structure device due to their compatibility with the current Sibased ultra large scale integration (ULSI) technology. Moreover, the theoretical limit for subthreshold swing (SS) of MOSFET is 60 mV/ dec at room temperature, which causes the increase in loff current. To overcome theoretical limit for the SS, it is crucial that research into new types of device concepts should be performed. In our present studies, we have experimentally demonstrated feedback FET (FBFET) and tunnel FET (TFET) with sub-60 mV/dec based on SiNWs. Also, we fabricated SiNW based complementary TFET (c-TFET) and SiNW complementary metal-oxide-semiconductor (CMOS) inverter. Our research demonstrates the promising potential of SiNW electronic devices for future wearable electronic systems.

## 1. MOSFET의 한계 및 대안

최근 웨어러블 기기에 대한 관심이 증가하면서 저전력 전자소자에 대한 연구가 많이 진행되고 있다. 하지만 현재의 metal-oxide-semiconductor field-effect transistor (MOSFET)로 구현한 웨어러블 전자소자는 짧은 배터리 수명, 높은 생산비용, 제한된 면적 내의 고집적화 등에서 한계를 보이고 있다. 이러한 문제점을 해결하기 위해 CMOS 공정을 사용하면서 기존의 전자소자보다고집적화, 저전력화가 가능한 새로운 개념의 전자소자에 대한 연구가 필요하다.

1960년대 실리콘 (Si) 및 실리콘 산화물 (SiO<sub>2</sub>)을 이용한 2차원 채널 구조의 MOSFET이 개발되었고, 소자의 성능 향상과 집적화 연구가 활발히 진행되었다. 이후, 내부전기장의 세기는 동일하게 유지하면서 소자의 수직/수평적인 요소들을 일정하게 줄여나가는 Dennard 이론을 기반으로 채널 길이를 감소시키는 연구가 진행되었다 [1]. 하지만 채널의 길이가 점점 줄어듦에 따라 단 채널 효과에 의한 문턱 전압의 변화가 부각되고 게이트의 채널 통제력도 낮아져 이에 따른 누설전류가 증가하였다 [2]. 이

#### 〈저자 약력〉

- 김상식 교수는 1985년, 1987년에 고려대학교 물리학과에서 학사, 석사학위를 받았으며, 1996년에 미국 Columbia 대학교에서 응용 물리 박사학 위를 받았고, 1999년부터 고려대학교 전기전자공학과 교수로 재직중이다. (sangsig@korea,ac,kr)

- 김민석 연구원은 2011년 홍익대학교 전자전기공학부에서 학사학위를 받았으며, 현재 고려대학교 전기전자공학부에서 석박통합과정 중이다. (kminsuk0217@korea,ac,kr)

- 임두혁 연구원은 2014년 고려대학교 전기전자공학과에서 학사학위를 받았으며, 현재 고려대학교 전기전자공학부에서 석박통합과정 중이다. (ladu@korea ac kr)

- 임경민 연구원은 2016년 고려대학교 전기전자공학과에서 학사학위를 받았으며, 현재 고려대학교 전기전자공학부에서 석박통합과정 중이다. (kymim@korea,ac,kr)

를 극복하기 위해 strained Si, 높은 유전율을 갖는 게이 트 절연막 그리고 금속 게이트 전극을 사용하였지만 2차 원 평면 구조로는 점점 한계에 다다르게 되어 채널의 세 면을 게이트로 감싸는 (Tri-gate) 3차원 구조를 적용하 여 MOSFET의 단 채널 효과를 개선하는 연구가 진행되었 다 [3]. 최근에는 tri-gate 구조를 더욱 발전시킨 gateall-around (GAA)구조에 대한 연구가 많이 진행되고 있 다. GAA 구조는 평면 채널 구조나 tri-gate 구조보다 게 이트의 채널 통제력이 높으므로 단 채널 효과를 줄일 수 있어 소자의 특성 향상에 최적화된 구조이다. 3차원 구조 의 나노선은 GAA 구조에 적용되기 가장 적합한 구조로, 여러 반도체 물질 중 실리콘을 채널 물질로 사용하는 나노 선 (silicon nanowire, SiNW)이 활용가치가 가장 높다. 그 이유는 실리콘과 실리콘 산화물, 실리콘 질화물에 대 한 연구가 많이 진행되어 있고. 현재의 반도체 소자 생산 설비는 실리콘을 기반으로 구축되어 있기 때문이다.

하지만 3차원 GAA 구조를 적용하더라도 MOSFET 기반의 집적회로는 전력 소모 측면에서의 물리적인 한계가있다. MOSFET은 캐리어(전자 또는 홀)들이 전계의 영향을 받아 이동하면서 전류가 흐르는 원리를 이용하는데, Maxwell—Boltzmann 분포에서 캐리어들의 열적 한계에의해 300 K의 온도에서 subthreshold swing (SS) 최소값이 60 mV/dec로 제한된다. SS값의 한계로 인해 소자의 동작 전압을 줄일 때 누설전류가 증가하게 되어 대기전력이 급증하는 문제가 발생하게 된다. 이를 해결하기위해, 기존 MOSFET의 한계를 극복할 수 있는 새로운 물리적인 원리를 적용한 소자들에 대한 연구의 필요성이 증가하였다. 이에 본 연구실에서는 SiNW를 이용하여 양성피드백 루프를 활용한 feedback FET (FBFET)와 밴드와밴드 간 터널링을 활용한 tunnel FET (TFET)을 구현하는 연구를 진행하였다 [4-8].

# 2. SiNW 및 소자 제작

SiNW를 형성하는 방법은 'bottom-up'과 'top-down' 두 가지 방식이 있다. Bottom-up 방식의 SiNW는 chemical vapor deposition (CVD)등의 공정을 이용하여 형성된다. 하지만 bottom-up 방식으로 SiNW를 형성하면 나노선의 배열이 어렵고, 적합한 위치에 도핑 공정을 진행하는데 어려움이 있어 회로나 시스템에 적용하기

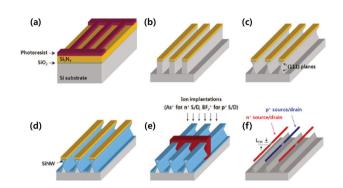

[Fig. 1] Key process steps used to obtain the silicon nanowire (SiNW) arrays from a bulk Si wafer. (a) Definition of Si active regions along the [110] direction after pad oxidation and nitride deposition. (b) Si trench etching. (c) Wet etching in 25 wt% TMAH solution to obtain the inverted triangle-shaped Si lines. (d) Thermal oxidation of the Si lines. (e) Source/drain implantations, followed by activation annealing. (f) Release of the SiNWs via wet chemical etching using BOE solution [9].

에는 부적절하다. 이와 달리 top-down 방식으로 형성된 SiNW는 포토-리소그래피 공정을 이용한 정확한 패터닝과 얼라인으로 보다 정밀한 소자를 제작할 수 있어 이를 집적회로에 적용 할 수 있다는 장점이 있다. Top-down 방식으로 효율적이고 정확한 SiNW를 제작하는 과정은 그림 1과 같다.

벌크 상태의 p-type 실리콘 웨이퍼(8-12 Ω·cm)에 실리콘 산화물을 oxidation 공정으로, 실리콘 질화물을 저압 CVD 공정으로 증착한다. 증착 후 포토-리소그래피 공정을 통해 [110] 방향의 실리콘을 활성화 영역으로 정해 준다 (그림 1a). 이후 실리콘 질화물을 hard mask로 이용 해서 식각 공정을 진행한다 (그림 1b). 실리콘의 [111] 면 의 dangling bond는 단위 셀 당 1개인데 비해 다른 면의 경우 2개이기 때문에 25 wt% tetramethylammonium hydroxide (TMAH) 용액에 대한 반응 속도의 차이가 발 생한다. 이를 이용해서 습식 식각을 진행하여 역 삼각형 모양의 실리콘 선을 형성한다 (그림 1c). 형성된 실리콘 선은 약 400 nm의 너비를 갖는데 이를 100 nm이하로 만 들기 위해 oxidation 공정을 통해 선 표면에 실리콘 산화 물을 형성한다 (그림 1d). SiNW에 As<sup>+</sup>/BF<sub>2</sub><sup>+</sup> 이온을 주 입하여 n- 또는 p-type으로 도핑 공정을 진행한다 (그 림 1e). Buffered oxide etchant (BOE) 용액을 사용해서

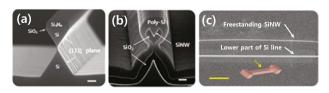

[Fig. 2] SEM images taken after the key process steps shown in Figure 1. (a) Cross section of the inverted-triangle-shaped Si line. (b) Cross section of the SiNW after size reduction oxidation. (c) Plane-view image of the freestanding SiNW after all process [9].

선을 감싸고 있던 실리콘 산화물을 제거하면 SiNW이 완성된다 (그림 1f). 그림 2는 주요 공정을 진행한 후 실리콘 선의 scanning electron microscopy (SEM) 이미지다. 그림 2a는 TMAH 용액을 사용해서 습식 식각 공정을 진행한 후 형성된 역 삼각형 모양의 실리콘 선의 단면이고 그림 2b는 선의 크기를 줄이기 위해 oxidation 공정을 진행한 후의 단면이다. 그림 2c는 최종적으로 모든 공정을 진행한 후 형성된 SiNW의 평면 이미지다.

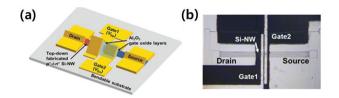

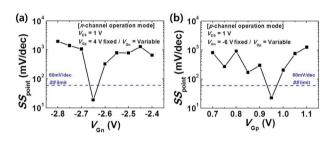

위에서 제작된 SiNW를 기반으로 FBFET와 TFET를 각각 제작하였다. 제작된 FBFET는 모식도 (그림 3a)와 같은 두개의 게이트 구조이고 이를 광학 현미경을 통해확인하였다 (그림 3b). FBFET의 동작원리는 다음과 같다. p<sup>+</sup>-i-n<sup>+</sup>으로 도핑된 SiNW의 채널 영역에 두개의 게이트 전압을 인가하여 에너지 장벽을 형성한다. 이때 게이트 전압을 점점 증가시키면 일부의 캐리어들이 장벽을 넘어가고 다른 쪽의 에너지 장벽을 낮추게 된다. 다른 쪽의 장벽이 낮아지면 반대편의 캐리어가 장벽을 넘고 이는 다시 맞은편의 장벽을 낮추게 되어 양성 피드백 루프를 발생시킨다 [4-5]. 인가된 게이트 전압에 따른 SS 값은 n-SiNW FBFET의 경우는 18-19 mV/dec, p-SiNW FBFET의 경우는 23 mV/dec이다 (그림 4a, b) [4-5].

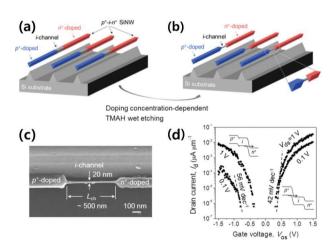

TFET는 p<sup>+</sup>-i-n<sup>+</sup>으로 도핑된 SiNW을 이용하여 제작하였다. 밴드와 밴드 간 터널링은 게이트에 인가한 전압으로 에너지 장벽을 조절하여 터널링 확률을 증가시켜 캐리어들을 이동시킨다. 전자가 가전자대에서 전도대까지이동하는 밴드와 밴드 간 터널링은 열에 의존하지 않기때문에 기존 MOSFET과는 달리 열로 인한 SS 한계의 영향을 받지 않는다 [6-8]. 제작된 SiNW (그림 5a)에 터널링 확률을 높이기 위해 TMAH로 습식 식각 공정을 진행하여 채널 부분의 두께를 감소시켰다 (그림 5b). 이후

[Fig. 3] (a) Schematic illustration and (b) optical image of dual-topgate SiNW FBFET [4-5].

[Fig. 4] SS characteristics of the (a) n- and (b) p- SiNW FBFET with various fixed gate voltages [4-5].

[Fig. 5] (a) Schematic of SiNWs. (b) Wet etched SiNWs in TMAH solution. (c) SEM image of etched SiNW. (d) Electrical characteristics of SiNW TFET [10].

SiNW의 감소한 두께가 20 nm 임을 SEM을 통해 확인하였다 (그림 5c). SiNW 기반 p- 와 n- TFET의 SS는 각각 56, 42 mV/dec 이다 (그림 5d) [10].

기존 MOSFET은 캐리어들의 열적 한계로 인해 SS 값의 한계가 60 mV/dec로 나타나는데 SiNW 기반 FBFET와 TFET는 각각 다른 물리적 원리를 활용하기 때문에 60 mV/dec 이하의 SS 값을 갖는다. 이는 단일 소자로 동작할 때 기존 MOSFET에서 축소화가 진행됨에 따라 증가

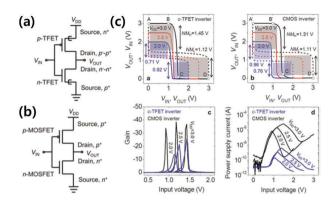

[Fig. 6] Inverter circuit diagrams of (a) SiNW c-TFET and (b) SiNW CMOS. (c) Static voltage transfer characteristics of the inverters in butterfly shape as a function of power supply voltage V<sub>DD</sub>, voltage gain characteristics and transfer curve of the power supply current - input voltage [11].

하던 누설전류의 영향을 감소시킨다. 즉, 기존 MOSFET 보다 축소화 할 수 있고 낮은 전력에서 구동 가능하다는 장점이 있다.

#### 3. 저전력 논리회로 구현

위에서 기존 MOSFET의 SS값보다 낮은 소자들을 제작하였고, 그 중 SiNW TFET로 inverter 논리회로를 구현하여 (그림 6a, b) 구동 및 대기 전력의 차이를 확인하였다 (그림 6c). VIN, VOUT에 따른 VOUT, VIN의 전기적특성 그래프를 통해 노이즈 마진을 확인해 보면 SiNW complementary TFET (c-TFET)의 경우가 SiNW CMOS의 경우보다 작은 전이 영역을 갖는다. 또한 대기 전력은 꺼진 상태에서 전류의 영향이 큰데, SiNW c-TFET의 경우 13.5 pW로 같은 조건에서의 SiNW CMOS의 대기 전력 값 1.6 nW 보다 약 0.008배 수준으로 낮음을 확인하였다 (그림 6) [11]. 현재 웨어러블 전자소자 기술이 기존의 트랜지스터를 기반으로 구현되는 점을 고려할 때, 앞에서 언급한 바와 같이 새로운 물리적 원리를 기반으로 하는 SiNW TFET, FBFET로 논리 회로를 구현하면 저전력 및 고집적화에 대한 대안이 될 수 있다.

#### 4. 맺음말

웨어러블 전자소자는 낮은 전력 소모와 높은 집적도

가 가능하도록 발전해 나갈 것이다. 3차원 GAA구조인 SiNW 기반 트랜지스터는 기존 2차원 MOSFET 대비 큰 게이트의 채널 통제력과 낮은 누설전류 특성뿐만 아니라 집적도의 향상이 가능한 소자이다. 더 나아가, SiNW로 FBFET, TFET를 구현하여 집적화 향상뿐 만 아니라 기존 MOSFET의 전력소모 문제도 해결할 수 있음을 확인하였다. 기존의 CMOS 공정을 활용하면서 초저전력, 고집 적화가 가능한 SiNW 기반 트랜지스터는 차세대 웨어러블 전자소자의 핵심기술이 되어 다양한 분야에 적용될 것으로 기대된다.

## 감사의 글

이 논문은 정부(미래창조과학부)의 재원으로 2013년도 한국연구재단(NRF-2013R1A2A1A030 70750), 2015년 도 한국연구재단(NRF-2015R1A2A1A15055437), 2016 년도 BK 21 Plus 프로젝트의 지원을 받아 수행된 연구임.

#### References

- D. J. Frank, R. H. Dennard, E. Nowak and P. M. Solomon, Proc. IEEE 89, 259-288 (2001).

- [2] M. Lee, Y. Jeon, J.-C. Jung, S.-M. Koo, and S. Kim, Applied Physics Letters 100, 253506 (2012).

- [3] J. T. Smith, S. Das, and J. Appenzeller, IEEE Electron Device Lett. 32, 1367 (2011).

- [4] Y. Taur and T. H. Ning, Fundamentals of Modern VLSI Devices (2009), chap. 4.

- [5] B. Doyle, B. Boyanov, S. Datta, M. Doczy, S. Hareland, B. Jin, J. Kavalieros, T. Linton, R. Rios, and R. Chau, Tech. Dig. Of Symposium on VLSI Tech. 133 (2003).

- [6] Y. Jeon, M. Kim, D. Lim, and S. Kim, ACS Nano 8, 3781-3787 (2014).

- [7] Y. Jeon, M. Kim, D. Lim, and S. Kim, Nano Letters 15, 4905-4913 (2015).

- [8] Y. Khatami and K. Banerjee, IEEE Trans. Electron Devices 56, 2752 (2009).

- [9] M. Lee, Y. Jeon, T. Moon, and S. Kim, ACS Nano **5**, 2629-2639 (2011).

- [10] M. Lee, Y. Jeon, M. Kim, and S. Kim, Journal of Applied Physics 117, 224502 (2015)

- [11] M. Lee, Y. Jeon, K. Son, J. Shim, and S. Kim, Phys. Status Solidi A 209, 1350-1358 (2012).