# Modification of Schottky Barrier Properties of Ti/p-type InP Schottky Diode by Polyaniline (PANI) Organic Interlayer

P. R. Sekhar Reddy<sup>1,a</sup>, V. Janardhanam<sup>1,a</sup>, I. Jyothi<sup>1</sup>, Shim-Hoon Yuk<sup>1</sup>, V. Rajagopal Reddy<sup>2</sup>, Jae-Chan Jeong<sup>3</sup>, Sung-Nam Lee<sup>4</sup>, and Chel-Jong Choi<sup>1,\*</sup>

Abstract—The electrical properties of Ti/p-type InP Schottky diodes with and without polyaniline (PANI) interlayer was investigated using current-voltage (I-V) and capacitance-voltage (C-V) measurements. The barrier height of Ti/p-type InP Schottky diode with PANI interlayer was higher than that of the conventional Ti/p-type InP Schottky diode, implying that the organic interlayer influenced the spacecharge region of the Ti/p-type InP Schottky junction. At higher voltages, the current transport was dominated by the trap free space-charge-limited current and trap-filled space-charge-limited current in Ti/p-type InP Schottky diode without and with PANI interlayer, respectively. The domination of trap filled space-charge-limited current in Ti/p-type InP Schottky diode with PANI interlayer could be associated with the traps originated from structural defects prevailing in organic PANI interlayer.

Index Terms—Schottky diode, PANI, InP, barrier height, interface state density

#### I. Introduction

advancement in semiconductor technology, Indium phosphide (InP) and its alloys have become more and more attractive semiconductor materials for the applications high speed optoelectronic devices and high power microwave devices because of its direct bandgap and high mobility [1-3]. For instance, InP based Schottky devices are one of the most requisite elements for microwave circuits. Schottky diodes are the majority carrier devices that offer the advantage of faster reverse recovery without the minority-carrier stored charge which is observed in p-n rectifiers and p-i-n rectifiers. This property makes it particularly suited for applications in the high frequency area. Generally the performance and reliability of Schottky diodes are strongly influenced by the interface quality between the metal and semiconductor surface. Practically, most of the Schottky diodes are not intimate metal-semiconductor contacts; rather they boast a thin interfacial layer between the metal and semiconductor unless carefully fabricated. This interfacial layer between the metal and semiconductor results in a higher barrier height and ideality factor than those of intimate metalsemiconductor structure. Previously, it was reported that introduction of an organic film between the metal and inorganic semiconductor was effective in modifying the Schottky barrier properties [4, 5]. This modification is often attributed to the formation of a dipole layer between the semiconductor and the organic film even though the organic-inorganic interface appears abrupt

Manuscript received Mar. 8, 2016; accepted Jun. 14, 2016

<sup>&</sup>lt;sup>1</sup> School of Semiconductor and Chemical Engineering, Semiconductor Physics Research Center (SPRC) Chonbuk National University, Jeonju 561-756, Korea

$<sup>^2</sup>$  Department of Physics, Sri Venkateswara University, Tirupati-517502, India

<sup>&</sup>lt;sup>3</sup> Electronics & Telecommunication Research Institute, Daejeon 305-700, Korea

<sup>&</sup>lt;sup>4</sup> Department of Nano-Optical Engineering, Korea Polytechnic University, Siheung 429-793, Korea

E-mail : cjchoi@jbnu.ac.kr <sup>a</sup> P. R. Sekhar Reddy and V. Janardhanam contributed equally to this work

and unreactive [6, 7]. Until now, several attempts have been made to realize a modification and continuous control of the barrier height of InP-based Schottky devices using organic interlayer [8-12]. For instance, Güllü. [8] fabricated the Al/n-InP Schottky diodes with deoxyribo nucleic acid (DNA) biopolymer as interlayer and demonstrated that the barrier heights could be tuned by varying the thickness of DNA biopolymer interlayer. Aydin et al. [10] reported that an increase in barrier height and ideality factor could be attributed to the modification of the Al/p-type InP interface by poly (3,4dioxythiophene):poly(styrene (PEDOT:PSS) interlayer. Reddy et al. [12] investigating the electrical properties of Au/poly(methyl methacrylate) (PMMA)/n-type InP Schottky structure at different annealing temperatures using I-V and C-V methods, showed that the interface state density and series resistance can give a significant effect on the electrical properties of the Au/PMMA/n-type InP Schottky diode. Among the various conducting polymers, polyaniline (PANI) has received greater attention due to its advantages over other conducting polymers such as the simplicity of its preparation from cheap materials, superior stability to air oxidation, and controllable electrical conductivity by doping [13-15]. Despite prominent features of PANI, however, its utilization as interlayer to improve the Schottky barrier properties of InP-based Schottky devices has not been explored yet, though the employment of PANI interlayer is expected to widen the range of their device applications. In this work, we fabricated Ti/p-type InP Schottky diode with PANI interlayer and investigated its electrical properties using current-voltage (I-V) and capacitance-voltage (C-V)characteristics. The Ti has been used as a Schottky contact metal because of its improved adhesion to the semiconductor and its low work function that can provide high barrier heights for p-type semiconductors [3, 16]. It will be shown that the introduction of PANI interlayer in-between Ti film and InP substrate leads to an increase in barrier height and a decrease in interface state density. It will be further shown that at higher voltages, the carrier transport of Ti/p-type InP Schottky diode with PANI interlayer is governed by the trap-filled space-charge-limited current associated with the traps originated from structural defects prevailing in organic PANI interlayer.

### II. EXPERIMENT

A schematic of the Ti/p-type InP Schottky diode with PANI interlayer is represented in the inset of Fig. 1. Zn doped p-type InP (100) wafers with a resistivity of 0.44 - $0.58 \Omega$  cm were used as a starting material. The wafers were initially degreased with organic solvents like trichloroethylene, acetone, and methanol by means of ultrasonic agitation for 5 min in each step, to remove the undesirable impurities, followed by rinsing in deionized (DI) water. Then, the samples were etched with HF (49%) and H<sub>2</sub>O (1:10) to remove the native oxide from the substrate. The 50 nm-thick Pt film was sputterdeposited on the back side of the InP wafer as an Ohmic contact and then annealed at 350 °C for 1 min in N<sub>2</sub> atmosphere. PANI powder with a conductivity of 2 - 4 S/cm (purchased from Sigma Aldrich) was used in this work. Prior to the deposition of PANI films and Schottky electrodes, above surface cleaning and etching processes were performed again. For forming Schottky contacts, 20 nm-thick PANI and 40 nm-thick Ti films were sequentially evaporated on the cleaned front side of InP wafer through a metal shadow mask with an area of 500 × 500 μm<sup>2</sup>. All evaporation processes were carried out under a vacuum pressure of  $7 \times 10^{-7}$  torr. In the present work, we fabricated the metal contacts using metal shadow masks very carefully in order to minimize the physical and chemical damages of PANI occurring during standard photolithography process and is feasible for the investigation of forward and reverse I-V characteristics [17, 18]. For comparison purposes, the conventional Ti/p-type InP Schottky diodes were fabricated under similar process conditions. The I-V and C-V measurements were performed at room temperature using precision semiconductor parameter analyzer (Agilent 4156C) and precision LCR meter (Agilent 4284A), respectively.

#### III. RESULTS AND DISCUSSION

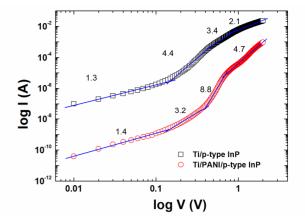

Fig. 1 shows the I-V characteristics of Ti/p-type InP Schottky barrier diodes with and without PANI interlayer measured at room temperature. For both devices, the linear part of the semi-log I-V curve for the forward bias voltage range (- 0.1  $\sim$  - 0.3 V) was clearly visible. This indicates that the carrier conduction of Ti/p-type InP

**Fig. 1.** I–V characteristics of Ti/p-type InP Schottky diodes with and without PANI interlayer. The inset shows the Schematic of Ti/p-type InP structure with PANI interlayer.

Schottky barrier diodes with and without PANI interlayer is limited by the thermionic emission regime. According to the thermionic emission theory, the current through Schottky contact is described by the following equation [19, 20]:

$$I = I_0 \exp\left(\frac{q(V - IR_s)}{nkT}\right) \left[1 - \exp\left(-\frac{q(V - IR_s)}{kT}\right)\right]$$

(1)

where V is the applied voltage across the junction,  $R_s$  is the series resistance, q is the charge of electron, n is the ideality factor, T is the room temperature, k is the Boltzmann constant and  $I_0$  is the saturation current obtained from intercept of the plot of  $\ln(I)$  versus V at V=0 and is given by [21, 22]:

$$I_0 = AA^{**}T^2 \exp\left(-\frac{q\Phi_{b0}}{kT}\right) \tag{2}$$

A is the diode area,  $A^{**}$  is effective Richardson's constant equal to 60 Acm<sup>-2</sup>K<sup>-2</sup> for p-type InP [10], and  $\Phi_{b0}$  is the barrier height whose value is obtained from the value of  $I_0$  using [19, 20]:

$$\Phi_{b0} = \frac{kT}{q} \ln \left( \frac{AA^{**}T^2}{I_0} \right) \tag{3}$$

The ideality factor can be determined from slope of the linear region of the forward bias ln(I) versus V using [19, 20]:

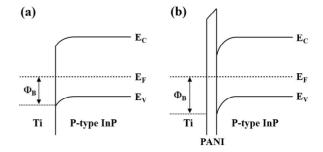

**Fig. 2.** Schematic energy band diagram of (a) Ti/p-type InP, (b) Ti/PANI/p-type InP structure.

$$n = \frac{q}{kT} \left( \frac{dV}{d(\ln I)} \right) \tag{4}$$

The barrier heights extracted from the Ti/p-type InP Schottky diodes with and without PANI interlayer were determined to be 0.81 and 0.64 eV, respectively. Namely, the barrier height of Ti/PANI/p-type InP Schottky diode was higher than that of Ti/p-type InP Schottky diode. This indicates that the introduction of PANI interlayer influenced the interfacial potential barrier of the Ti/InP Schottky junction, resulting in a modification of the effective barrier height, as shown in Fig. 2 [6, 23, 24]. Namely, PANI interlayer can act as a physical barrier between Ti film and p-type InP substrate for preventing their direct contact, causing a substantial shift in the work function of a metal and in the electron affinity of a semiconductor. In particular, both devices exhibited an ideality factor deviating from the value of unity, of which values were 1.72 and 1.49 for Ti/p-type InP Schottky diodes with and without PANI interlayer, respectively. The ideality factor values were obtained in the range of 0.01 - 0.1 V. This deviation of the ideality factor from unity could be associated with the presence of a wide distribution of low-Schottky barrier patches caused by a laterally inhomogeneous barrier [25, 26]. Furthermore, when comparing to Ti/p-type InP Schottky diode, the higher value of the ideality factor in Ti/PANI/p-type InP Schottky diode could be attributed to secondary mechanisms such as interface dipoles caused by PANI interlayer, a specific interface structure or fabricationinduced defects at the interface [27, 28]. Additionally, the relatively high reverse leakage current was observed in Ti/p-type InP Schottky diodes with and without PANI interlayer. This could be a large number of native defects prevailing in InP substrate [29, 30]. Since these defects

are conductive, they can serve as the leakage path of current through Schottky junction. Therefore, irrespective of employing PANI interlayer, the both device showed high leakage current in the reverse bias region, resulting in their poor rectification behavior [31].

The forward bias *I–V* characteristics of the Schottky diodes deviated considerably from linearity at sufficiently large voltages due to the effect of series resistance and the presence of interface states. In order to accurately determine the series resistance and other Schottky parameters such as the barrier height and ideality factor, Cheung's functions were employed. Cheung's function can be expressed as [32]:

$$\frac{dV}{d(\ln I)} = \frac{nkT}{q} + IR_{S} \tag{5}$$

$$H(I) = V - \left(\frac{nkT}{q}\right) \ln\left(\frac{I}{AA^{**}T^2}\right)$$

(6)

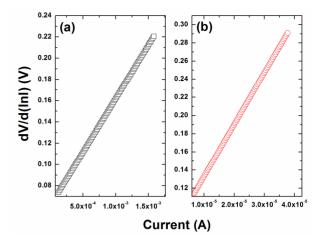

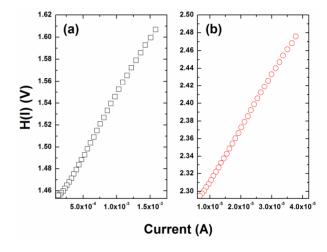

Fig. 3 represents the plots of  $dV/d(\ln I)$  versus I for Ti/p-type InP Schottky diode without and with PANI interlayer. A plot of  $dV/d(\ln I)$  versus I is linear for the data in the nonlinear region of the forward bias I-Vcharacteristics with the slope giving the series resistance and y-axis intercept yields the ideality factor following Eq. (5). From linear fit to data of Fig. 3, the series resistance and ideality factor were found to be 100  $\Omega$  and 2.32 for Ti/p-type InP Schottky diode, and 5.70 k $\Omega$  and 2.90 for Ti/PANI/p-type InP Schottky diode, respectively. The plots of H(I) versus I for Ti/p-type InP Schottky diode with and without PANI interlayer are shown in Fig. 4. Similar to the plot of  $dV/d(\ln I)$  versus I, H(I) versus I linearly increased with increasing I. According to Eq. (6), a linear curve fitting of the data yields series resistance from the slope, and barrier height from the ordinate using the value of ideality factor obtained from Eq. (5). The series resistance and barrier height extracted from the plot of H(I) versus I plot were obtained as 109  $\Omega$  and 0.61~eV for Ti/p-type InP Schottky diode and as  $6.0~K\Omega$ and 0.77 eV for Ti/PANI/p-type InP Schottky diode. The values of series resistance calculated from the plots of dV/d(lnI) versus I were almost identical to those from the plots of H(I) versus I, implying the consistency of cheung's method. It should be noted that the series resistance of Ti/PANI/p-type InP Schottky diode was much higher than that of Ti/p-type InP Schottky diode.

**Fig. 3.** Plots of  $dV/d(\ln I)$  as a function of I taken from the (a) Ti/p-type InP, (b) Ti/PANI/p-type InP Schottky diodes.

**Fig. 4.** Plots of H(I) as a function of I taken from the (a) Ti/p-type InP, (b) Ti/PANI/p-type InP Schottky diodes.

This indicates that the series resistance is a current limiting factor for the Ti/PANI/p-type InP Schottky diode. In other words the voltage drop across the PANI interlayer is likely to retain forward current conduction in the Ti/PANI/p-type InP Schottky diode.

Norde proposed an alternative method for the determination of barrier height and series resistance for the Schottky diode. The Norde function is defined as [33]:

$$F(V) = \frac{V}{\gamma} - \frac{kT}{q} \ln \left( \frac{I(V)}{AA^{**}T^2} \right)$$

(7)

where  $\gamma$  is an integer greater than ideality factor. In this method, the function F(V) is plotted against the applied voltage and obtained it's minimum. The barrier height

**Fig. 5.** Norde plot of Ti/p-type InP Schottky diodes with and without PANI interlayer.

can be determined using [33]:

$$\Phi_{b0} = F(V_{\min}) + \frac{V_{\min}}{\gamma} - \frac{kT}{q}$$

(8)

where  $F(V_{min})$  is the minimum point of F(V) and  $V_{min}$  is the corresponding voltage. Fig. 5 shows the Norde plot for the Ti/p-type InP Schottky diode with and without PANI interlayer. The values of the series resistance can be estimated from Norde's function as [33, 34]:

$$R_{S} = \frac{kT(\gamma - n)}{qI_{\min}} \tag{9}$$

where  $I_{\min}$  is the current corresponding to the voltage  $V_{\min}$ . The values of barrier height and series resistance were calculated to be 0.66 eV and 14 kΩ for Ti/p-type InP Schottky diode and 0.83 eV and 37 MΩ for Ti/PANI/ptype InP Schottky diode, respectively. There is a difference in the values of barrier height and series resistance obtained from the Norde method and forward bias ln(I)-V, Cheung's method. Such a difference in the values obtained from the three methods may be attributed to the extraction from the different regions of the *I-V* plot. Cheung functions are applied only to the nonlinear region in the high voltage section of the forward bias *I–V* characteristics, while Norde's functions are applied to full forward bias region of the I-V characteristics of the junction [25]. Further, the Norde method is not a suitable method for rectifying junctions with high ideality factors, which are not compatible with the pure thermionic

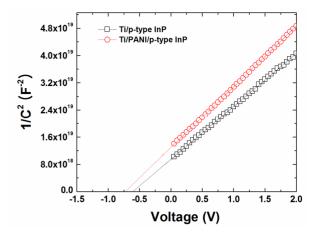

**Fig. 6.** Plot of  $1/C^2-V$  taken from Ti/p-type InP Schottky diodes with and without PANI interlayer.

emission theory. Hence, the values of the barrier height and series resistance obtained from Norde method are higher than those obtained from other methods.

Fig. 6 represents the room temperature  $1/C^2-V$  plot of the Ti/p-type InP Schottky barrier diode with and without the PANI interlayer. The C-V data were measured at a frequency of 1MHz. The straight lines obtained from the  $1/C^2-V$  plots are consistent with the Schottky-Mott model [35], which assumes that the carrier concentration is constant through the depletion width of the Schottky junction. The C-V relationship for a Schottky barrier diode is given as [19]:

$$\frac{1}{C^2} = \left(\frac{2}{\varepsilon_s q N_d A^2}\right) \left(V_{bi} - \frac{kT}{q} - V\right) \tag{10}$$

where  $V_{\rm bi}$  is built-in potential.  $\varepsilon_s$  is the semiconductor permittivity of p-type InP (12.5 $\varepsilon_{\rm o}$ , where  $\varepsilon_{\rm 0}$  is the permittivity of the free space), A is the area of the Schottky barrier contact and q is the charge of electron, respectively. The x-intercept of the plot of  $1/C^2$  versus V gives the diffusion potential ( $V_o$ ). The  $V_o$  is related to  $V_{\rm bi}$  by the equation  $V_{bi} = V_o + kT/q$ , where T is the absolute temperature. The barrier height can be obtained from the equation  $\Phi_{b(C-V)} = V_{bi} + V_n$  where  $V_n$  is potential difference between the Fermi level and the top of the valance band of p-type InP which can be estimated by knowing the carrier concentration  $N_A$  and is obtained from the equation  $V_n = (kT/q) \ln(N_V/N_A)$ , where  $N_V$  is the density of effective states in the valance band of p-type InP given by  $N_V = 2(2\pi m * kT/h^2)^{3/2}$ , where m \* 0.078  $m_o$  and its

value is  $N_V = 1.11 \times 10^{19} \,\text{cm}^{-3}$  [3]. From  $1/C^2 - V$  plots, the barrier heights were determined to be 0.86 and 0.99 eV for the Ti/p-type InP Schottky diodes without and with PANI interlayer. It is noted that the barrier heights obtained from the C-V measurements were higher than those obtained from the *I–V* method. The barrier heights obtained from the I-V and C-V methods are not always the same because of the different nature of the measurements. The difference between the barrier heights measured from I-V and C-V methods could be associated with the spatial inhomogeneity of the barrier heights having low and high Schottky barrier height patches along the interface [35]. Generally, in the I-Vmeasurement, the current across the Schottky interface depends exponentially on the barrier height and thus is sensitive in the detailed barrier distribution at the interface. The current preferentially flows through the height leading lower barrier region, underestimation of the barrier height in the *I–V* method. While the C-V method yields the average barrier height of the whole diode [28]. Thus the barrier height obtained from the I-V method is significantly lower than the weighted arithmetic average of Schottky barrier heights obtained from the *C*–*V* method [36].

The downward concave curvature of the forward bias I-V characteristics at sufficiently large voltages has been attributed to the presence of the interface states  $(N_{ss})$ which are in equilibrium with the semiconductor, apart from the effect of  $R_s$  [18]. In this region, the ideality factor n is rather controlled by the interface states and the series resistance. The energy distribution of the interface state density can thus be determined from forward bias I-V data by taking into account the bias dependence of the ideality factor and barrier height. The interface states refers to the imperfections at the semiconductor surface like dangling bonds at the surface, other types of defects and impurities unintentionally incorporated during the processing steps, or the unintentionally formed native oxide during the subsequent processing steps that may give rise to oxide trapped charges and interface trapped charges. The expression for the density of interface states  $(N_{ss})$  proposed by Card and Rhoderick as [25]:

$$N_{SS} = \frac{1}{q} \left\{ \frac{\varepsilon_i}{\delta} \left[ n(V) - 1 \right] - \frac{\varepsilon_S}{w_D} \right\}$$

(11)

where  $W\square$  is the space charge width,  $\varepsilon_s$  is the permittivity of the semiconductor,  $\varepsilon_i$  is the permittivity of the interface layer, of which thickness is  $\delta$ , and  $n(V)=V/(kT/q)\ln(I/I_0)$  is the voltage dependent ideality factor. For, a p-type semiconductor, the energy of the interface state (E<sub>ss</sub>) with respect to the top of the valance band (E<sub>V</sub>) at the surface of the semiconductor is given by [25]:

$$E_{ss} - E_V = q\Phi_e - qV \tag{12}$$

where V is the applied voltage drop across the depletion layer and  $\Phi_e$  is the effective barrier height given by [17]:

$$\Phi_e = \Phi_b + \beta V \tag{13}$$

where

$$\beta = \frac{d\Phi_e}{dV} = 1 - \frac{1}{n(V)} \tag{14}$$

The energy distribution of the N<sub>ss</sub> were determined from the forward bias I-V data (Fig. 1) using the voltagedependent values of ideality factor and other parameters in Eq. (11). Fig. 7 shows the values of N<sub>ss</sub> as a function of E<sub>ss</sub>-E<sub>V</sub> for the Ti/p-type InP Schottky diodes with and without PANI interlayer. The values of N<sub>ss</sub> were varied in the range of  $2.14 \times 10^{13} \,\text{eV}^{-1} \,\text{cm}^{-2}$  in  $(0.62 - \text{E}_{\text{V}}) \,\text{eV}$  to  $5.65 \times 10^{14} \, \text{eV}^{-1} \, \text{cm}^{-2} \, \text{in} \, (0.32 - \text{E}_{\text{V}}) \, \text{eV} \, \text{for the Ti/p-type}$ InP Schottky diode and varied from  $2.47 \times 10^{11}$  in (0.75 - $E_V$ ) eV to  $2.29 \times 10^{13} \, \text{eV}^{-1} \, \text{cm}^{-2} \, \text{in} \, (0.39 - E_V) \, \text{eV}$  for the Ti/PANI/p-type InP Schottky diode. It can be observed that the N<sub>ss</sub> decreased exponentially from midgap towards the top of the valence band. Further, at any specific energy, the N<sub>ss</sub> of Ti/PANI/p-type InP Schottky diode was lower than that of the Ti/p-type InP Schottky diode. This indicates that the PANI interlayer was effective in the reduction of N<sub>ss</sub> in the Schottky diode. It is well known that the insertion of an organic interlayer in-between the metal and semiconductor modifies the interface properties of the Schottky junction even though the organic/inorganic interface appears abrupt and unreactive [6, 7]. A decrease in the interface state density of the Ti/PANI/p-type InP structure could be responsible for an increase in barrier height and hence the reduction in the leakage current [37]. Generally, the presence of an interfacial thin layer separating the semiconductor and the metal causes the net charge of the gap states along with its image charge on the surface of the metal forming

**Fig. 7.** Plots of  $N_{ss}$  as a function of  $E_c$  -  $E_{ss}$  extracted from the Ti/p-type InP Schottky diodes with and without PANI interlayer.  $N_{ss}$  was derived from forward I-V characteristics.

a dipole layer that will alter the energy barrier, implying the strong dependency of the barrier height on the surface states density [38].

An investigation of the current transport mechanism through the Ti/p-type InP Schottky diodes with and without PANI interlayer was performed using the plot of log I-log V as shown in Fig. 8. In general, the log I-log V plot shows a power-law dependence of the current as  $I \propto$  $V^m$ , and the value of the exponent m can be calculated from the slope of the linear fit to log *I*–log *V* plot. From Fig. 8, it can be observed that for both devices, there existed four different regions (indicated as region-I, region-II, region-III and region-IV) having different slopes. In region-I, the slopes were found to be 1.4 and 1.3 for the Ti/p-type InP Schottky diode with and without PANI interlayer, respectively. These values were close to unity, indicating a linear dependence of the current as  $I \sim V$ . In other word, for both devices, the current transport of region-I follows the Ohm's law in which the current is controlled by the thermally activated carriers rather the injected carriers [39]. For Ti/p-type InP Schottky diode without PANI interlayer, there was an exponential increase of current in region-II and region-III with the values of m being obtained as 4.4 and 3.4 in region-II and region-III, respectively. Such a power-law dependence (m > 2) indicates that the current transport mechanism could be attributed to space-charge-limited current controlled by the traps distributed exponentially in energy. At higher voltages (region-IV), the slope of Ti/ptype InP Schottky diode without PANI interlayer tended to decrease (m = 2.1). This implies that Ti/p-type InP

**Fig. 8.** Forward  $\log I$  – $\log V$  characteristics of the Ti/p-type InP Schottky diodes with and without PANI interlayer.

Schottky diode without PANI interlayer approached the trap-filled limit regime at high injection level, where most of traps were occupied by injected carriers, followed by the creation of a field impeding further injection caused by the accumulation of space charge near the electrode. Namely, in higher voltage region (region-IV), Ti/p-type InP Schottky diode without PANI interlayer behaved as if there are no traps in it, and its carrier transport was governed by trap free space-chargelimited current, where current varies as the square of the voltage [40]. Similarly, Ti/p-type InP Schottky diode with PANI interlayer exhibited the power law relation having m > 2 in the region-II and region-III, which was indicative of the predomination of space-charge-limited current. However, unlike Ti/p-type InP Schottky diode without PANI interlayer, the slope in region-IV of Ti/ptype InP Schottky diode with PANI interlayer was much higher than 2 in spite of high injection level, implying that space-charge-limited current still predominated even at higher voltages. This is due to numerous traps originated from structural defects prevailing in organic PANI interlayer caused by its non-uniformity and sub atomic structure [41, 42].

# IV. CONCLUSIONS

PANI interlayer was employed to modify the Schottky barrier properties of Ti/p-type InP Schottky diode. The barrier height of Ti/p-type InP Schottky diode with PANI interlayer was higher than that without PANI interlayer. This increase in barrier height could be attributed to the fact that the organic interlayer increased the effective

barrier height by influencing the space-region of InP. The introduction of the PANI interlayer led to the reduction of the interface state density in the Ti/p-type InP Schottky diode. The analysis of the forward log *I*–log *V* characteristics revealed that the domination of carrier transport by Ohmic conduction at lower voltage, controlled by the thermal activation of intrinsic carriers. At higher voltages, the carrier transport was governed by trap free space-charge-limited current in Ti/p-type InP Schottky diode. However, the carrier transport in Ti/p-type InP Schottky diode with PANI interlayer was dominated by the trap filled space-charge-limited current at higher voltages due to the traps originated from structural defects prevailing in organic PANI interlayer.

#### ACKNOWLEDGMENTS

This research was supported by the Basic Science Research Program (NRF-2015R1A6A1A04020421) through the National Research Foundation of Korea funded by the Ministry of Education, Republic of Korea, and by a grant from the R&D Program (Grant No. 10045216) for Industrial Core Technology funded by the Ministry of Trade, Industry and Energy, Republic of Korea. It was also financially supported by the research support project of the ETRI (Grant No. B0132-15-1001) by the Ministry of Science, ICT and Future Planing, Republic of Korea.

## REFERENCES

- [1] J. Chen, Q. Wang, J. Lv, H. Tang, and X. Li, "Current-voltage-temperature and capacitance-voltage-temperature characteristics of TiW alloy/p-InP Schottky barrier diode," *J. Alloy. Compd.*, Vol. 649, pp. 1220–1225, 2015.

- [2] B. Akkal, Z. Benamara, N. B. Bouiadjra, S. Tizi, B. Gruzza, "Illumination dependence of *I–V* and *C–V* characterization of Au/InSb/InP(1 0 0) Schottky structure," *Appl. Surf. Sci.*, Vol. 253, No. 3, pp. 1065–1070, 2006.

- [3] V. Janardhanam, H. K. Lee, K. H. Shim, H. B.Hong, S. H. Lee, K. S. Ahn, C. J. Choi, "Temperature dependency and carrier transport mechanisms of Ti/p-type InP Schottky rectifiers," *J. Alloy. Compd.*, Vol. 504, pp. 146–

- 150, 2010.

- [4] O. F. Yuksel, N. Tugluoglu, H. Safak, and M. Kus, "The modification of Schottky barrier height of Au/p-Si Schottkydevices by perylene-diimide," *J. Appl. Phys.*, Vol. 113, pp. 044507-1–044507-9, 2013.

- [5] N. Kavasoglu, C. Tozlu, O. Pakma, A. S. Kavasoglu, S. Ozden, B. Metin, O. Birgi, and S. Oktik, "Room-temperature interface state analysis of Au/Poly(4-vinyl phenol)/p-Si structure," *Synth. Met.*, Vol. 159. No. 17, pp. 1880–1884, 2009.

- [6] M. Cakar, N. Yildirim, S. Karatas, C. Temirci, and A. Turut, "Current-voltage and capacitance-voltage characteristics of Sn/rhodamine- 101 / n - Si and Sn/rhodamine- 101 / p - Si Schottky barrier diodes," *J. Appl. Phys.*, Vol. 100, No. 7, pp. 074505-1–074505-6, 2006.

- [7] T. U. Kampen, S. Park, and D. R. T. Zahn, "Barrier height engineering of Ag/GaAs(100) Schottky contacts by a thin organic interlayer," *Appl. Surf. Sci.*, Vol. 190, pp. 461–466, 2002.

- [8] O. Gűllű, "Ultrahigh (100%) barrier modification of *n*-InP Schottky diode by DNA biopolymer nanofilms," *Microelectron. Eng.*, Vol. 87, No. 4, pp. 648–651, 2010.

- [9] M. Soylu, B. Abay, and Y. Onganer, "The effects of annealing on Au/pyronine-B/MD n-InP Schottky structure," *J. Phys. Chem. Solids.*, Vol. 71, No. 9, pp. 1398–1403, 2010.

- [10] M. E. Aydin, and F. Yakuphanoglu, "Electrical characterization of inorganic-on-organic diode based InP and poly(3,4-ethylenedioxithiophene)/ poly(styrenesulfonate)(PEDOT:PSS)," *Microelectronics Reliab.*, Vol. 52, No. 7, pp. 1350– 1354, 2012.

- [11] O. Güllü, O. Pakma, and A. Turut, "Current density-voltage analyses and interface characterization in Ag/DNA/p InP structures," *J. Appl. Phys.*, Vol. 111, No. 4, pp. 044503-1–044503-6, 2012.

- [12] V. R. Reddy, A. Umapathi, and S. Sankar Naik, "Influence of Annealing on Electrical Properties of an Organic Thin Layer-Based *n*-Type InP Schottky Barrier Diode," *J. Electron. Mater.*, Vol. 42, No. 6, pp. 1282–1288, 2013.

- [13] S. Aydogan, M. Saglam, and A. Turut, "On the barrier inhomogeneities of polyaniline/p-Si/Al

- structure at low temperature," *Appl. Surf. Sci.*, Vol. 250, No. 1, pp. 43–49, 2005.

- [14] M. Wolszczak, J. Kroh, and M. M. A. Hamid, "Some aspects of the radiation processing of conducting polymers," *Radiat. Phys. Chem.*, Vol. 45, No. 1, pp. 71-78, 1995.

- [15] G. Gustafsson, G. M. Treacy, Y. Cao, F. Klavetter, N. Colaneri, and A. J. Heeger, "The "plastic" led: A flexible light-emitting device using a polyaniline transparent electrode," *Synth. Met.*, Vol. 57, No. 1, pp. 4123–4127, 1993.

- [16] W. Deqi , D. Wuchang, Y. Shanshan, J. Rui, J. Zhi, and L. Xinyu," Optimization of ohmic contact for Inp-based transferred electronic devices," *J. Semicond.*, Vol. 35, No. 3, pp. 036001-1 036001-5, 2013.

- [17] O. F. Yuksel, M. Kus, N. Simsir, H. Safak, M. Sahin, and E. Yenel, "A detaile analysis of current- voltage characteristics of Au/perilene monoimide/n-Si Schottky barrier diode over a wide temperature range," *J. Appl. Phys.*,Vol. 110, No. 26, pp. 024507-1 024513-7, 2011.

- [18] P. Koteswara Rao, B. Park, S. T. Lee, Y. K.Noh, M. D. Kim, and J. E. Oh, "Analysis of leakeage current mechanisms in Pt/au Schottky contact on Gapolarity GaN by Frenkel-poolyemission and deep level studies," *J. Appl. Phs.*, Vol. 110, pp. 013716-1-013716-5, 2011.

- [19] E.H. Rhoderick, and R.H. Williams, "Metal Semiconductor Contacts," second ed. Clarendon, Oxford, pp. 39., 1988.

- [20] S.M. Sze, "Physics of Semiconductor Devices", second ed., John Wiley & Sons, New York., 1981.

- [21] R. T. Tung, "Recent advances in Schottky barrier concepts," *Mater. Sci. Eng. R.*, Vol. 35, pp. 1-138, 2001.

- [22] H. K. Henisch, "Semiconductor Contacts," London, Oxford University, 1984.

- [23] A. R. Vearey-Roberts, and D. A. Evans, "Modification of GaAs Schottky diodes by thin organic interlayers," *Appl. Phys. Lett.*, Vol. 86, No. 7, pp. 072105-1–072105-3, 2005.

- [24] I. Jyothi, V. Janardhanam, V. R. Reddy, and C. J. Choi, "Modified electrical characteristics of Pt/n-type Ge Schottky diode with a pyronine-B interlayer," *Superlattices Microstruct.*, Vol. 75, pp. 806–817, 2014.

- [25] H. C. Card, and E. H. Rhoderick, "Studies of tunnel MOS diodes I. Interface effects in silicon Schottky diodes," *J. Phys.*, Vol. 4, No. 10, pp. 1589–1601, 1971.

- [26] M. Saglam, and A. Turut, "Aging effects on the interface state density obtained from current– voltage and capacitance–frequency characteristics of polypyrrole/p-Si/Al structure," *J. Appl. Polym. Sci.*, Vol. 101, No. 4, pp. 2313–2319, 2006.

- [27] R. F. Schmitsdorf, T. U. Kampen, and W. Monch, "Explanation of the linear correlation between barrier heights and ideality factors of real metalsemiconductor contacts by laterally nonuniform Schottky barriers," *J. Vac. Sci. Technol.*, Vol. 15, No. 4, pp. 1221–1226, 1997.

- [28] W. Monch, "Barrier heights of real Schottky contacts explained by metal-induced gap states and lateral inhomogeneities," *J. Vac. Sci. Technol.*, Vol. B 17, No. 4, pp. 1867 – 1876, 1999.

- [29] Robert W. Jansen, "Theoretical study of native defects and impurities in InP," *Phys. Rev. B*, Vol. 41, pp. 7666-7673, 1990

- [30] Rohan Mishra, Oscar D. Restrepo, Ashutosh Kumar, and Wolfgang Windl, "Native point defects in binary InP semiconductors," *J. Mater. Sci.*, Vol. 47, pp 7482-7497, 2012

- [31] A.M. Rodrigues, H. L. Gomes, P. Stallinga, L. Pereira, and E. Pereira, "Electrical characterization of CVD diamond-n<sup>+</sup> silicon junctions," *Diam. Relat. Mat.*, Vol. 10, No. 3-7, pp. 858–862, 2001.

- [32] S. K. Cheung, and N. W. Cheung, "Extraction of Schottky diode parameters from forward current-voltage characteristics," *Appl. Phys. Lett.*, Vol. 49, pp. 85–87, 1986.

- [33] H. Norde, "A modified forward I- V plot for Schottky diodes with high series resistance," *J. Appl. Phys.*, Vol, 50, No. 7, pp. 5052–5053, 1979.

- [34] V. Janardhanam, Y. K. Park, H. J. Yun, K. S. Ahn, and C. J. Choi, "Conduction Mechanism of Se Schottky Contact to n-Type Ge," *Eletron. Dev. Lett.*, Vol. 33, No. 33, pp. 949–951, 2012.

- [35] I. Jyothi, V. Janardhanam, Yi-Rang Lim, V. R. Reddy, Kwang-Soon Ahn, and Chel-Jong Choi, "Effect of copper phthalocyanine (CuPc) interlayer on the electrical characteristics of Au/n-GaN Schottky rectifier," *Mater. Sci. Semicond. Process.*, Vol. 30, pp. 420-428, 2014.

- [36] M. Gokcen, T. Tunc, S. Altındal, and I. Uslu, "The effect of PVA (Bi<sub>2</sub>O<sub>3</sub>-doped) interfacial layer and series resistance on electrical characteristics of Au/n-Si (110) Schottky barrier diodes (SBDs)," *Curr. Appl. Phys.*, Vol. 12, No. 2, pp. 525–530, 2012.

- [37] M. Mamor, "Interface gap states and Schottky barrier inhomogeneity at metal/n-type GaN Schottky contacts," *J. Phys. Condens. Matter.*, Vol. 21, pp.335802-1–335802-12, 2009.

- [38] S. R. Forrest, "Ultrathin Organic Films Grown by Organic Molecular Beam Deposition and Related Techniques," *Chem. Rev.*, Vol. 97, No. 6, pp. 1793–1896, 1997.

- [39] V. Janardhanam, I. Jyothi, J. H. Lee, J. Y. Kim, V. R. Reddy, and C. J. Choi, "Electrical Properties and Carrier Transport Mechanism of Au/n-GaN Schottky Contact Modified Using a Copper Pthalocyanine (CuPc) Interlayer," *Mater. Trans.*, Vol. 55, No. 5, pp. 758–762, 2014.

- [40] A. C. Varghese, and C. S. Menon, "Electrical properties of hybrid phthalocyanines thin films using gold and lead electrodes," *Eur. Phys. J.*, Vol. 47, No. 4, pp. 485 489, 2005.

- [41] A. A. Kumar, V. R. Reddy, V. Janardhanam, M. W. Seo, H. B. Hong, K. S. Shin, and C. J. Choi, "Electrical Properties of Pt/n-Ge Schottky Contact Modified Using Copper Phthalocyanine (CuPc) Interlayer," *J. Electrochem. Soc.*, Vol. 159, No. 1, pp. H33 H37, 2011.

P. R. Sekhar Reddy was born in Andhra Pradesh, India, on 1990. He received B.Sc. and M.Sc. degrees in Physics, from Sri Venkateswara University, Tirupati, India, in 2011 and 2014, respectively. He is currently pursuing the Ph.D degree in

Department of School of Semiconductor and Chemical Engineering, Semiconductor Physics Research Center, Chonbuk National University Republic of Korea. His research interests include preparation of metal-polymer composite films for the development of organic-inorganic hybrid nanomaterials.

V. Janardhanam received the M.Sc., and Ph.D. degrees in Physics, from Sri Venkateswara University, Tirupati, India, in 2003 and 2009, respectively. Dr. V. Janardhanam joined as post-doctorate in the Semiconductor Physics Research Center, Chonbuk

National University, in November 2009. As author and co-author, he has published 50 articles in referred journals and has been the author and co-author of over 30 conference papers. His current research interests include fabrication of Ohmic and Schottky contacts to germanium for post-silicon CMOS technologies, polymer based contacts for Schottky diodes, and preparation of metal-polymer composite films for the development of organic-inorganic hybrid nanomaterials.

I. Jyothi received the M.SC., and Ph.D. degrees in Physics, from Sri Venkateswara University, Tirupati, India, in 2007 and 2011, respectively. She joined as a Post-doctorate in the Semiconductor Physics Research Center, Chonbuk National University,

in November 2009. As author and co-author, she has published 19 articles in referred journals and has been the author and co-author of over 20 conference papers. Her interests are Ohmic and Schottky contacts to wide-band gap semiconductors and polymer based contacts to GaN, Ge for Schottky diodes.

**Shim-Hoon Yuk** is a School of Semiconductor and Chemical Engineering, Semiconductor Physics Research Center (SPRC) Chonbuk National University, Jeonju 561-756, Republic of Korea.

V. Rajagopal Reddy received the M.Sc and Ph.D degrees in Physics from Sri Venkateswara University, Tirupati in 1989 and 1994. From September 2002 to December 2003, Prof. Reddy was a Visiting Research Professor, at the Semiconductor Thin

Film and Device laboratory, Gwanju Institute of Science and Technology, Gwanju, Korea, where he performed research on Ohmic and Schottky Contacts to wide band gap semiconductors (GaN). Prof. Reddy has published more than 175 articles in referred journals, and has been author or co-author of over 115 conference papers. Prof. Reddy has successfully guided 17 Ph.Ds in the field of Advanced Electronic Materials (GaN). He is holder of one Korean patent. His current research interests are (i) Ohmic and Schottky Contacts to wide- band gap semiconductors, (ii) Polymer-based Schottky Contacts to InP, (iii) Surface analysis of III-V and II-VI semiconductors, and (iv) Deep level studies in wide band gap semiconductors such as GaN and ZnO.

**Jae-Chan Jeong** is Electronics & Telecommunication Research Institute, Daejeon 305-700, Republic of Korea.

**Sung-Nam Lee** is a Department of Nano-Optical Engineering, Korea Polytechnic University, Siheung 429-793, Republic of Korea

Chel-Jong Choi was born in Korea, on June 16, 1974. He received the B.S. degree in ceramic engineering from Hanyang University, Seoul, Korea, in 1997, and the M.S. and Ph.D. degrees in materials science engineering from the Gwangju

Institute of Science and Technology (GIST), Gwangju, Korea, in 1999 and 2003, respectively. From 2003 to 2005, he was with the Samsung Advanced Institute of Technology (SAIT), Suwon, Korea, in the areas of semiconductor-device characterization. From 2005 to 2008, he worked with the Electronics and Telecommunications Research Institute (ETRI), Daejon, Korea, where he was involved in the process integration of nano-scaled Schottky barrier MOSFETs. Since 2008, he has been with Chonbuk National University, Jeonju, Korea. His research interests include the novel nano-scaled Ge- and III-V- based electronic devices for the ultimate CMOS and post-CMOS technologies.