ISSN: 1226-7244 (Print) ISSN: 2288-243X (Online) 논문번호 16-03-22

122

# 밴더블 a-Si:H 박막트랜지스터의 전기적 특성에 미치는 채널 길이의 영향

# Effect of Channel Length on Electrical Characteristics of a Bendable a-Si:H TFTs

오 현 곤\*, 조 경 아\*, 김 상 식\*\*

Hyungon Oh\*, Kyoungah Cho\*, Sangsig Kim\*\*

#### Abstract

In this study, we investigate the influence of channel length of bendable a-Si:H thin film transistors (TFTs) on their electrical characteristics as a function of bending strain. Under a tensile strain of 1.69%, 8  $\mu$ m -channel-length TFT has the threshold voltage shift up to 5.25 V, while 100  $\mu$ m-channel-length TFT operates stably.

#### 요 약

본 연구에서는 8와 100  $\mu$ m의 채널 길이를 가지는 밴더블 a-Si:H 박막 트랜지스터를 제작하고, 밴딩 스트레인에 따른 전기적 특성변화를 측정하였다. 1.69%의 밴딩 스트레인에서 8  $\mu$ m 채널 길이를 가지는 박막트랜지스터는 문턱 전압이 5.25 V까지 이동하였으나 100  $\mu$ m 채널 길이를 가지는 박막트랜지스터는 전기적 특성 변화 없이 안정적으로 동작하였다.

Key words: a-Si:H TFT, channel length, bending strain, bendable TFT

- \* Dept of Electrical Engineering, Korea University

- ★ Corresponding author

sangsig@korea.ac.kr, TEL: +82-2-3290-3245

\* Acknowledgment

This work was supported in part by the Mid-career Researcher Program

$(No.NRF-2013R1A2A1A03070750,\ NRF-2015R1A2A1A15055437) \\ and \ Basic \ Science \ Research \ Program$

(No. NRF-2015R1D1A1A01057641) through the National Research Foundation of Korea (NRF), funded by the Ministry of Education, Science and Technology, Samsung Display Co. Ltd., the Brain Korea 21 Plus Project, and a Korea University Grant.

This is an Open-Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License (http://creativecommons.org/licenses/by-nc/3.0) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

## I . 서론

최근 유연 디스플레이의 구동소자로 사용되는 밴더블 박막트랜지스터의 기계적 내구성은 유연 디스플레이 분야에서 중요한 이슈가 되고 있다 [1-6]. 최근까지는 밴더블 박막트랜지스터에 밴딩스트레인이 가해졌을 때, 트랜지스터의 채널 두께가 트랜지스터의 특성에 미치는 영향을 파악하기 위해 연구가 진행되어 왔다 [5, 6]. 밴더블 박막트랜지스터의 특성에 영향을 미치는 트랜지스터의 채널 파라미터에는 두께뿐만 아니라 길이도 포함되나, 아직까지 밴더블 박막트랜지스터의 채널 길이에 대한 연구는 미흡한 실정이다. 따라서본 연구에서는 밴딩 상태에서 a-Si:H 박막트랜지

스터의 채널 길이에 따른 a-Si:H 박막트랜지스터의 전기적 특성 변화를 알아보고자 한다.

# II. 본론

#### 1. 실험방법

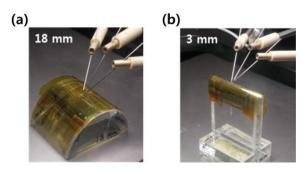

a-Si:H 박막트랜지스터는 폴리이미드 기판 위에 a-Si:H 채널과 몰리브덴 (Mo) 전극 및 SiNx 게이트 절연막으로 제작되었다. a-Si:H 채널층과 SiNx 게이트 절연막은 플라즈마 화학증착 (PECVD) 방법으로 증착하였다. 채널의 너비는 20 µm으로, 길이는 8 와 100 µm로 각각 제작하였다. 게이트, 소스 및 드레인 전극으로 사용된 Mo물질은 DC 스퍼터링 방법으로 증착하였다. 밴딩스트레인은 그림 1과 같이 자체 제작된 18 mm와 3 mm의 밴딩 스테이지를 이용하여 박막트랜지스터의 인가하였으며, 전기적 특성은 HP4155C로 측정하였다.

Fig. 1. Optical image of the bending stages (a) 18 mm, (b) 3 mm

그림 1. 밴딩 스테이지의 광학 이미지 (a) 18 mm, (b) 3 mm

# 2. 결과 및 고찰

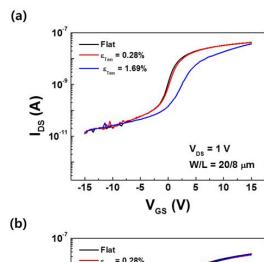

그림 2 (a)와 (b)는 각각 8, 100  $\mu$ m의 채널 길이를 가지는 a-Si:H 박막트랜지스터의 밴딩 스트레인에 따른 드레인-소스 전류와 게이트-소스 전압 ( $I_{DS}$ - $V_{GS}$ ) 그래프이다. 밴딩 스트레인은 곡률반경을 18 mm와 3 mm로 하여 얻어진 값으로, 아래와 같은 식으로 계산되었다[7].

$$\epsilon_{suface}(\%) = \left(\frac{d_f + d_s}{2R}\right) \!\! \left(\frac{\left(1 + 2\eta + \chi\eta^2\right)}{\left(1 + \eta\right)\left(1 + \chi\eta\right)}\right) \!\! \times 100$$

여기서  $d_f$ 와  $d_s$ 는 각각 박막트랜지스터 전체 박 막 두께  $(0.82~\mu m)$  와 기판의 두께 $(25~\mu m)$ ,  $\eta$ 은  $d_f/d_s$ ,  $\chi$ 는 박막트랜지스터와 기판의 Young's

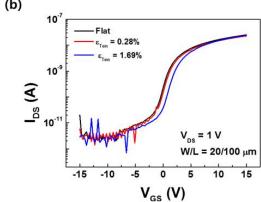

modulus 비율 ( $\chi=Y_f/Y_s$ ;  $Y_f=325$  GPa,  $Y_s=2.5$ GPa), R은 곡률반경이다. 여기서, Yf는 a-Si:H 박 막트랜스터에서 가장 큰 Young's modulus를 가 진 몰리브덴 전극의 수치이다. 곡률반경이 18 mm 와 3 mm일 때, 밴딩 스트레인은 각각 0.28%와 1.69%로 계산되었다. 그림 2는 8, 100 µm의 채널 길이를 가지는 a-Si:H 박막트랜지스터의  $I_{DS}$ - $V_{GS}$ 그래프이다. 8  $\mu$ m의 채널 길이를 가지는 a-Si:H 박막트랜지스터의 전자이동도는 플랫일 0.28%, 1.69%의 밴딩 스트레인이 가해졌을 때 각 각 0.158, 0.145, 0.095 cm<sup>2</sup>/V·s이였으며, I<sub>on</sub>/I<sub>off</sub>의 비는 각각 3.2×10<sup>3</sup>, 2.9×10<sup>3</sup>, 2.4×10<sup>3</sup>이였다. 이에 비하여, 100 μm의 채널 길이를 가지는 a-Si:H 박 막트랜지스터의 전자이동도는 플랫일 때와 0.28%, 1.69%의 밴딩 스트레인이 가해졌을 때 각각 0.178, 0.175, 0.171 cm<sup>2</sup>/V·s이였으며, I<sub>on</sub>/I<sub>off</sub>의 비는 각각 1.1×10<sup>4</sup>, 1.0×10<sup>4</sup>, 1.2×10<sup>4</sup>이였다.

Fig. 2.  $I_{DS}-V_{GS}$  curves of the a-Si:H TFTs as a function of the bending strain and the channel length: (a)W/L=20/8  $\mu$ m,(b) W/L=20/100  $\mu$ m

그림 2. 밴딩 스트레인과 채널 길이에 따른 a-Si:H 박막 트랜지스터의 I<sub>DS</sub>-V<sub>GS</sub> 그래프 : (a) W/L=20/8 μm, (b) W/L=20/100 μm

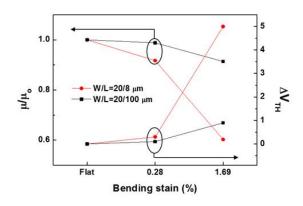

I<sub>DS</sub>-V<sub>GS</sub> 그래프를 통해 각각 8, 100 μm의 채널 길이를 가지는 a-Si:H 박막트랜지스터의 밴딩 스 트레인에 따른 이동도 변화(μ/μ₀) 와 문턱전압 변 화 $(\Delta V_{TH})$ 를 그림 3에 나타내었다. 밴딩 스트레 인이 증가할수록 박막트랜지스터의 문턱전압은 이동되고, 이동도는 감소하는 경향을 보였다. 이 것은 외부 스트레스로 인해 채널층과 절연층 사 이에서의 전하트랩 및 전극과의 접촉 저항 증가 로 인한 것으로 사료된다[8]. 특히, 8 μm 채널 길 이를 가지는 박막트랜지스터는 1.69%의 밴딩 스 트레인 상태에서 문턱전압이 5.25 V까지 이동하 였다. 이에 반해, 채널 너비가 100 um인 박막 트 랜지스터는 1.69%의 밴딩 스트레인에서도 안정적 으로 동작하였다. 밴더블 박막트랜지스터의 채널 길이와 밴딩 스트레인에 대한 소자의 전기적 특 성 열화는 반비례적인 관계를 가지는 것을 확인 하였다.

Fig. 3. μ/μ₀ and  $\Delta V_{TH}$  of the a-Si:H TFTs as a function of the bending strain and the channel length 그림 3. 밴딩 스트레인과 채널 길이에 따른 a-Si:H 박막트랜지스터의 μ/μ₀ 와  $\Delta V_{TH}$ 그래프

### Ⅲ 결론

본 연구에서는 플라스틱 기판 위에 밴더블 a-Si:H 박막트랜지스터를 제작하고, 밴딩 스트레인에 따른 전기적 특성을 확인하였다. a-Si:H 박막트랜지스터는 채널 길이가 길 경우에 밴딩 스트레인에 대해서도 안정적인 동작을 한다는 것을 확인하였다.

# References

- [1] R. Amalraj, S. Sambandan, "Influence of curvature on the device physics of thin film transistors on flexible substrates," *J. Appl. Phys.* 116, 164507, 2014.

- [2] K. D. Harris. A. L. Elias, H. J. Chung, "Flexible electronics under strain: a review of mechanical characterization and durability enhancement strategies," *J. Mater. Sci*, 51, 2771, 2016.

- [3] J. Yun, K. Cho, S. Kim, "Improved Electrical Characteristics of HgSe Nanoparticle-based Thin Film Transistors by Thermal Annealing," *j.inst.Korean.electr.electron.eng* 14, 3, 194, 2010.

- [4] B. J. Yu, H. M. Cho, "A Design of PLL for 6 Gbps Transmitter in Display Interface Application," *j.inst.Korean.electr.electron.eng* 17, 1, 16, 2013.

- [5] H. Gleskova, I. C. Cheng, S. Wagner, J. C. Sturm, Z. Suo, "Mechanics of thin-film transistors and solar cells on flexible substrates," *Solar Energy* 80, 687, 2006.

- [6] Z. Suo, E. Y. Ma, H. Gleskova, S. Wagner, "Mechanics of rollable and foldable film-on-foil electronics," Appl. Phys. Lett. 74, 8, 1999.

- [7] K. Fukuda, K. Hikichi1, T. Sekine, Y. Takeda, T. Minamiki, D. Kumaki, "Strain sensitivity and durability in p-type and n-type organic thin-film transistors with printed silver electrodes," *Sci. Rep.* 3, 2048, 2013.

- [8] M. H. Lee, B. F. Hsieh, S. T. Chang, "Electrical properties correlated with redistributed deep states in a-Si:H thin-film transistors on flexible substrates undergoing mechanical bending," *Thin Solid Films*, 528, 82, 2013.