# PSFB 컨버터에서 변압기 최적 설계에 관한 연구

이일운\*

A Study on the Optimal Design of the Transformer in the PSFB Converter

Il-Oun Lee\*

요 약

위상변조 풀브리지 컨버터를 설계, 개발하는데 있어, 전력반도체와 그 전력반도체 구동회로, 변압기 및 인덕터, 정류기 등을 포함한 많은 설계 요인들이 존재한다. 그 중에서 위상변조 풀브리지 컨버터의 최적 성능에 매우 큰 영향을 끼치는 것은 변압기 설계이다. 특히 변압기 설계는 대형 컴퓨터 데이터센터에 사용되는 전원장치에서처럼 저전압, 고전류 응용에서 매우 중요하다. 이 논문에서는 위상변조 풀브리지 컨버터의 최적 성능을위한 변압기설계에 관한 연구 결과를 발표한다. 변압기 설계에 관련된 설계 수식들을 유도하고 세밀한 분석을 한다. 이를 토대로, 12V, 1200W 서버전원장치 응용을 위한 위상변조 풀브리지 컨버터 최적 성능을 위한 변압기 설계를 결과물로 제시한다.

#### **ABSTRACT**

In the Phase Shifted Full Bridge(: PSFB) converter, there are several design factors including power switches, power switches' driving circuits, transformer and inductor, and rectifier stage, etc. Among them, a key factor influencing an optimal performance of the PSFB converter is the design of transformer. Especially, its effect becomes more important in low voltage and high power applications. In this paper, a study on an optimal design of transformer in the PSFB converter is presented. The design equations for the transformer are derived and analyzed in details, and an example design of the transformer for a 12V, 1200W server power supply application is showed as the result of analysis.

#### 키워드

Phase-Shift, Full-Bridge Converter, Transformer, Efficiency 위상 변조, 풀브리지 컨버터, 변압기, 효율

# 1. 서 론

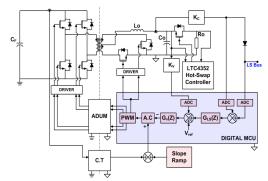

전원장치를 개발하는데 사용될 수 있는 다양한 토폴로지들이 존재한다. 그 중에서 kW급 대용량 응용분야에서는 전용 제어 IC의 존재, 추가 소자 없이도가능한 소프트 스위칭 동작, 출력 LC 필터에 의한 낮은 출력 전류 리플 등의 장점으로 그림 1의 위상변조

풀브리지(Phase-Shifted Full-Bridge, PSFB) 컨버터가 가장 널리 사용된다[1-5].

PSFB 컨버터를 개발하는데 있어 다양한 설계 요소들이 있다. 그 중에서도 변압기 설계는 PSFB 컨버터의 부하 변동에 따른 효율 특성에 아주 큰 영향을 끼치고, 전체 시스템의 성능을 결정하는 핵심 소자이다. PSFB 컨버터에 사용되는 변압기는 시중에서 쉽

\* 교신저자 : 계명대학교 전자전기공학부

• Received : Aug. 10, 2016, Revised : Sep. 13, 2016, Accepted : Sep. 24, 2016

• 접 수 일: 2016. 08. 10 • 수정완료일: 2016. 09. 13

Corresponding Author: II—Oun Lee

Dept. of Electrical Energy Engineering, Keimyung University,

·게재확정일 : 2016. 09. 24

Email: leeiloun@kmu.ac.kr

게 구할 수 있는 소자는 아니며, 컨버터의 주어진 사양을 고려하여 엔지니어가 직접 설계해야 하는 부품이다. 특히, 저전압 대전류 응용에서는 변압기 설계가컨버터 전체 효율 성능을 결정할 만큼 매우 중요한부품이라 할 수 있다[6-8].

본 논문에서는 저전압, 대전류 응용의 예로 PSFB 컨버터 최적 트랜스포머 설계를 위한 주요 설계 요소 들을 분석하고 설계에 필요한 이론적 수식들을 정립 하고 발표한다.

# II. PSFB 컨버터 트랜스포머 최적 설계 요소 분석

### 2.1 Hold-up 시간을 고려한 최소 입력전압 선정

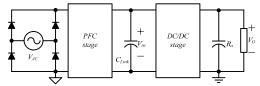

그림 2는 대형 컴퓨터 데이터센터용 전원시스템을 포함한 분산 전력시스템에서, 일반적인 전원시스템에 구조를 보여 준다. 그림 2에서처럼 상용 입력 AC 전원의 고조파 규제를 만족하기 위한 PFC(:Power Factor Corrector) 회로와 시스템의 버스 전압을 만드는 front-end DC-DC 컨버터로 이루어져 있다.

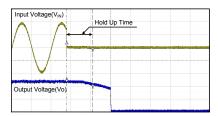

데이터센터용 서버 전원시스템을 포함한 분산 전력 시스템에서는 AC 입력이 차단되더라도 그림 3과 같 이 시스템의 출력 전압을 레귤레이션 범위 내에서 일 정 시간 동안 유지해야 하는 기능이 있으며, 이를 hold-up 시간이라 한다. 이 hold-up 시간 동안에는 AC 입력이 차단되어 있기 때문에 PFC의 출력 전압 을 저장하는 링크 커패시터에서만 출력으로 부하전류 를 공급하게 되어 DC-DC 컨버터의 입력 전압 Vin은 점점 감소하게 된다. 서버 전원시스템의 예로 설명하 면 DC-DC 전력단의 입력 전압은 그림 3에서 표현한 것과 같이 Vin\_nom에서 hold-up 시간 동안 최소 입력 전압 Vin min까지 변하게 된다. 여기서, Vin nom은 PFC 에 의한 정상상태 입력 전압으로 400V이고, Vin min은 서버 전원시스템 DC-DC 컨버터의 출력 전압 12V로 레귤레이션 가능한 최소 입력 전압을 나타낸다. Hold-up 구간 동안 두 입력 전압에서 커패시터에 축 적되는 에너지의 차는 전력에 hold-up 시간을 곱한 값과 같으므로 식 (1)과 같이 쓸 수 있다.

그림 1. 위상변조 풀브리지 컨버터 Fig. 1 Phase-shifted full-birdge converter

그림 2. 분산 전력 시스템에서의 front-end converter Fig. 2 Front-end converter in distributed power system

(a) Hold-up 동안 AC 전원과 직류 출력 전압 (a) AC input voltage and DC output voltage during hold-up interval

(b) Hold-up 동안 입력 전압 변동 (b) Input voltage variation during hold-up time 그림 3. Hold - up 시간 Fig. 3 Hold-up time

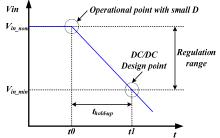

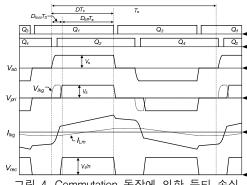

그림 4. Commutation 동작에 의한 듀티 손실 Fig. 4 Duty-loss due to commutation interval

$$\frac{1}{2}C_{link}V_{in\_nom}^{2} - \frac{1}{2}C_{link}V_{in\_mim}^{2} = \frac{P_{o}}{\eta} \cdot t_{hold-up}$$

(1)

식 (1)로부터 레귤레이션을 위한 최소 입력 전압을 구하면 식 (2)와 같다.

$$V_{\text{in\_min}} = \sqrt{V_{\text{in\_nom}}^2 - \frac{2P_{_{o}} \cdot t_{_{\text{hold-up}}}}{\eta \cdot C_{_{\text{link}}}}} \tag{2}$$

1200W 서버 전원시스템 기준으로 hold-up 시간 thold-up은 서버 전원시스템에 관한 공인 사양에 준하여 20ms로 하고, 링크 커패시턴스 Clink는 20ms의 hold-up 시간과 사이즈 및 상용 콘덴서를 고려하여 330μF 3개를 병렬로 사용한 990μF으로 선정하면 hold-up 시간을 고려한 최소 입력전압은 식(2)로부터 식 (3)처럼 330V임을 알 수 있다.

$$V_{\text{in\_min}} = \sqrt{400^{2} - \frac{2 \times 1200 \times 20 \times 10^{-3}}{0.95 \times 990 \times 10^{-6}}} = 330V$$

(3)

# 2.2 최소 입력 전압과 듀티 및 권선 관계

설계의 여유를 두어  $V_{\text{in,min}}$ 을 320V로 설정하면, 트랜서포머 턴 비는 2차측 CTR(:Center-Tap Rectifier) 정류회로로부터 유도한 식 (4)를 이용하여 식 (5)와 같이 n=27로 결정되며, 이때 정상 동작 시비율  $D_{\text{nom}}$ 은 식 (6)에 의해 0.4가 된다. 하지만, 식 (4), (5)은 PSFB 컨버터의 dead-time 및 commutation에 의한 유효 듀터의 손실을 고려하지 않은 식이므로 실제 동

작 시에는 이를 고려하여 턴 비 및 동작 시비율을 설정하여야 한다. 그림 4에 나타낸 바와 같이 풀-브리지 인버터의 양단 전압  $V_{ab}$ 가 변하더라도 commutation 동작 중에는 2차측 정류단의 입력전압  $V_{rec}$ 에는 전압이 인가되지 않게 된다. 이로 인하여 항상  $D_{loss}$ 만큼 듀티의 손해를 보게 되므로 0.5- $D_{loss}$ 가실제 PSFB 컨버터가 얻을 수 있는 최대 유효 듀티  $D_{max}$ 가 된다[9-10]. 뿐만 아니라 회로 내부의 기생 성분에 의한 전압 강하까지 고려하여 실제 PSFB 컨버터의 턴 비는 24로 선정되어야 하며, 이 때의 유효 듀티는 식 (6)로부터 약 0.36정도가 된다.

$$n = 2D_{max} \cdot \frac{V_{in\_min}}{V_{O}} = 2 \times 0.5 \times \frac{320}{12} = 27$$

(4)

$$D_{\text{nom}} = \frac{n \times V_{\text{O}}}{2 \times V_{\text{in nom}}} = \frac{27 \times 12}{2 \times 400} = 0.4$$

(5)

$$D_{\text{eff}} = \frac{n \times V_{\text{O}}}{2 \times V_{\text{in nom}}} = \frac{24 \times 12}{2 \times 400} = 0.36$$

(6)

# 2.3 트랜스포머 코어 선정

일반적으로 코어 선정에는 Area Product  $A_P$ = $A_CA_W$ 를 이용한 방식이 많이 사용된다. 물리적으로 단면적( $A_C$ )과 창면적( $A_W$ )의 곱은 코어의 크기로 나타낼 수 있으며, 또한 권선수(전압에 비례)와 권선 굵기(전류에 비례)와의 곱은 파워를 뜻한다. 여기서 창면적( $A_W$ )과 단면적( $A_C$ )이 각각 권선의 총단면적과 턴 수에 관계되므로 이를 이용하여 용량에 맞는 코어를 선정할 수 있다. 먼저,  $A_C$ 와 $A_W$ 의 수식을 유도해보도록 한다.

$$\lambda = LI = N\Phi \tag{7}$$

$$\Phi = BA_{C} \tag{8}$$

식 (7), (8)를 패러데이 법칙에 의해 식 (9)와 같이 나타낼 수 있다.

$$L\frac{\Delta I}{DT_{S}} = NA_{C}\frac{\Delta B}{DT_{S}} \tag{9}$$

식 (9)로부터 코어의 단면적AC는 아래 식 (10)과 같이 구할 수 있다.

$$A_{C} = \frac{L\Delta I}{N\Delta B} \quad or \quad \frac{LI_{peak}}{NB_{max}} \tag{10}$$

KU는 윈도우 활용 인자로서 창면적에 대한 총권 선 단면적을 나타내므로 식 (11)와 같이 표현된다.

$$K_{U} = \frac{NA_{S}}{A_{W}} \tag{11}$$

그러면 식 (11)로부터 코어의 창면적은 식 (12)와 같이 표현될 수 있다.

$$A_{\mathrm{W}} = \frac{NA_{\mathrm{S}}}{K_{\mathrm{U}}} = \frac{NI_{\mathrm{rms}}}{K_{\mathrm{U}}J} \tag{12} \label{eq:A_W}$$

식 (10)과 (12)로부터, Area Product AP는 식 (13) 와 같이 구할 수 있다.

$$A_{P} = A_{C}A_{W} = \frac{LI_{peak}}{NB_{max}} \frac{NI_{rms}}{K_{U}J} = \frac{LI_{peak}I_{rms}}{B_{max}K_{U}J} \tag{13} \label{eq:AP}$$

PSFB 컨버터에서 AC와AW는 위 식으로부터 각각 (14)와 (15)와 같이 다시 쓸 수 있다. 여기서, VP는 트랜스포머1차측에 걸리는 전압이다. 그리고 AWP와AWS는 각각 1차측 권선과 2차측 권선의 단면적, IP\_rms와 IS\_rms는 각각 트랜스포머 1차측과 2차측 권선의 rms전류, KU는 윈도우 활용 인자(일반적으로 0.3~0.5), JP와 JS는 각각 1차측 권선과 2차측 권선의전류 밀도(A/cm2), Bmax는 사용할 최대 자속 밀도를나타낸다. 출력 인덕터 전류를 정전류로 가정하면 트랜스포머의 1, 2차측 rms 전류는 식 (16) 및 (17)과 같이 구할 수 있다.

$$A_{\rm C} = \frac{DV_{\rm P}}{2B_{\rm max}N_{\rm P}f_{\rm S}} \tag{14}$$

$$A_{W} = \frac{N_{P}A_{WP} + 2N_{S}A_{WS}}{K_{U}} = \frac{N_{P}}{K_{U}} \left(\frac{I_{P_{rms}}}{J_{P}} + \frac{2I_{S_{rms}}}{nJ_{S}}\right)$$

$$= \frac{N_{P}I_{O}}{nK_{U}} \left(\frac{1}{J_{P}} + \frac{\sqrt{2}}{J_{S}}\right)$$

(15)

$$I_{P_{-rms}} = \frac{I_{O}}{n} \tag{16}$$

$$I_{S_{\_rms}} = \frac{\sqrt{2}I_{O}}{2} \tag{17}$$

식 (14)-(17)로부터 AP는 식 (18)과 같이 나타내어 지며 이로부터 대략적인 코어를 선정할 수 있다.

$$A_{P} = A_{C}A_{W} = \frac{D \cdot V_{P} \cdot I_{O}}{2 \cdot n \cdot B_{max} \cdot f_{S} \cdot K_{U}} \left(\frac{1}{J_{P}} + \frac{\sqrt{2}}{J_{S}}\right)$$

(18)

식 (18)에서 각 파라미터 값을 다음과 같이 선정하면 코어의 AP는 약 3.5cm4이며 이를 기준으로 코어데이터 시트로부터 적합한 코어를 선정할 수 있게 된다.

[사용된 파라미터]

- 유효듀티D=0.36

- 트랜스포머1차측 전압VP=400[V]

- 출력전류IO=100[A]

- 턴 비n=24

- 최대 자속 밀도Bmax=0.1[T]

- 스위칭 주파수fS=86[kHz]

- 윈도우 활용 인자KU=0.3

- 전류밀도Jp=Js=800[A/cm2](일반적으로 400~600A/cm2정도로 선정하지만 냉각 팬을 사용하면 1000A/cm2이상으로도 사용할 수 있다.)

$$\begin{split} A_{\rm P} = & \frac{0.36 \!\times\! 400 \!\times\! 100}{2 \!\times\! 24 \!\times\! 0.1 \!\times\! 10^4 \!\times\! 86 \!\times\! 10^3 \!\times\! 0.3} \! \left( \frac{1}{800} \!+\! \frac{\sqrt{2}}{800} \right) \\ = & 3.5 \! \left[ \text{cm}^4 \right] \end{split}$$

(19)

# 2.4 트랜스포머 턴 수 선정

일반적으로 변압기의 1차측 턴 수는 패러데이 법 칙에 의해 식 (20)으로부터 설계되며, 2차측의 턴 수 는 턴 비 관계로부터 구해진다.

$$N_{P} = \frac{DV_{P}}{2B_{max}A_{C}f_{S}} \tag{20}$$

하지만 서버 전원시스템과 같은 대전류 사양에서는 2차측 권선의 손실을 최소화하기 위하여 2차측 권선은 1턴으로 구현하므로 1차측 권선의 턴 수는 턴비 n으로 정해지게 된다. 이 경우 트랜스포머의 AC와 AW는 식 (21), (22)와 같이 나타내어진다. 2.3절에 언급된 파라미터들을 적용하여 구한 값의 곱은 식 (19)에서 구한 값과 동일하다는 것을 알 수 있다.

$$\begin{split} A_{C} &= \frac{DV_{P}}{2nB_{max}f_{S}} \\ &= \frac{0.36 \times 400}{2 \times 24 \times 0.1 \times 10^{4} \times 86 \times 10^{3}} = 3.5 \Big[ cm^{2} \Big] \quad \text{(21)} \end{split}$$

$$A_{W} = \frac{I_{O}}{K_{U}} \left( \frac{1}{J_{P}} + \frac{\sqrt{2}}{J_{S}} \right)$$

$$= \frac{100}{0.3} \times \left( \frac{1}{800} + \frac{\sqrt{2}}{800} \right) = 1.0 \left[ \text{cm}^{2} \right]$$

(22)

#### 2.5 권선 선정

만약 공간적 제약에 의해서 변압기의 크기가 어느 정도 정해져 있고, 1차측과 2차측의 권선이 각각 n과 1로 정해져 있으면, 트랜서포머를 제작하기 위한 권선의 굵기만 결정하면 된다.

# III. 설계 요소들을 반영한 실제 변압기 제작

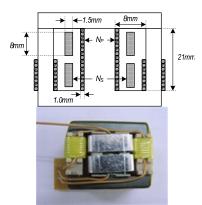

2장에서 1200W, 12V 서버 전원시스템 기준으로 대략적인 코어의 크기(창면적, 단면적)는 AP가3.5 cm4정도였다. 하지만 실제 설계 시에는 제약 조건들 을 만족시키는 코어를 선정하여야 한다. 전원시스템에 사용되는 부품은 전원시스템이 사용되는 전체 시스템 의 기구 요구 사양 때문에 사용되는 부품들의 높이 제한이 있을 수 있다. 예로 설명되는 1200W, 12V 출 력 서버 전원시스템에서는 부품 높이 제한 31mm 이 므로 트랜스포머 제작에 사용되는 보빈 및 권선 고려 하여 높이 20mm의 코어로 제작되어야 한다. 20mm의 높이와 앞에서 계산 AP를 만족시키기 위해EI4033\*20 core를 선정하였다. 해당하는 사양에 적합한 상용 코 어가 없으므로 신규 금형 코어로 제작하였다. EI4033\*20코어는Aw와Ac가 각각1.68cm2,2.40cm2으로 AP가4.0cm4이 되므로 앞서 계산된AP=3.5 cm4를 마 진을 갖고 만족하게 된다.

2차측의 권선을 1턴으로 구현한다고 가정하였을 경우 1차측의 권선수는 24가 된다. 이로부터 선정된 코어의 AC를 이용하여 식 (21)로부터 사용할 코어의 최대 자속 밀도를 구해 볼 수 있다.

$$\begin{split} B_{max} &= \frac{DV_p}{2nA_Cf_S} = \frac{0.36 \times 400}{2 \times 24 \times 2.4 \times 86 \times 10^3} \times 10^4 \\ &= 0.15 \big[ T \big] \end{split}$$

(23)

1차 권선의 경우 안전규격을 고려하여 삼중절연 권선을 사용하였다. 1차 권선으로 사용한 0.8mm 삼중 절연 권선은 절연두께를 포함한 전체 외경이 1.0mm 이다.

PSFB 컨버터의 스위칭 손실을 줄이기 해 Leakage 인덕터를 키우는 SPW(: Separated Primary Winding)권선 방법의 경우 센터 레그에 16턴 (1.0mm\*16=16.0mm)을 감고, 나머지 사이드 레그에 각각 8턴((1.0mm\*8=8.0mm)씩을 감아 1차측 턴 수를 24턴이 되게 한다. 1차측 전류의rms값은 식 (16)로부터 약 4.2A이므로 1차측 권선의 전류 밀도는 식 (24)와 같이 구해진다.

$$J_{P} = \frac{I_{P_{-rms}}}{A_{WP}} = \frac{4.2}{\pi \times (0.4 \times 10^{-1})^{2}} = 836 [A/cm^{2}]$$

(24)

2차 권선은 대전류 사양이므로 그림 6(b)의 실물 사진과 같이 클립 구조의 권선을 사용하였다. 1차측 권선이 차지하고 남는 공간을2차측 권선이 사용할 수 있으나 보빈이 차지하는 공간 및 작업 오차를 위한 여유를 두어8mm×1.5mm의 클립형태의 권선을 사용 하였다. 식 (17)로부터 2차측 권선의rms 전류는 약 70A이므로 전류밀도는 식 (25)와 같이 구해진다.

$$J_{s} = \frac{I_{s_{rms}}}{A_{ws}} = \frac{70.7}{8 \times 10^{-1} \times 1.5 \times 10^{-1}}$$

$$= 589 \left[ A / cm^{2} \right]$$

(25)

그림 5는 PSFB 컨버터의 트랜스포머 설계 요소들을 분석하고, 이 분석 결과를 토대로 최적으로 설계하여 실제 1200W, 12V출력 서버 전원시스템에 적용한 SPW PSFB DC-DC 컨버터의 트랜스포머 권선도 및실물 사진을 보여 준다.

그림5. 제작된 트랜스포머 Fig. 5 Manufacted transformer

# Ⅳ. 결 론

대용량 전원시스템응용에서는 PSFB 컨버터가 가 장 널리 사용된다. PSFB 컨버터에는 전력반도체, 전 력반도체 구동드라이버, 출력 제어를 위한 보상기를 포함한 컨트롤러, 변압기, 인덕터, 콘덴서 등 많은 설계 요소들이 있다. 그중에서도 변압기 설계는 PSFB 컨버터의 부하변동에 따른 효율 특성에 아주 큰 영향을 끼치고, 전체시스템에 큰 영향을 주는 중요 부분이다. 특히, 저전압 대전류 응용에서는 변압기 설계가 컨버터 전체 성능을 결정할 만큼 매우 중요한 부분이다. 본 논문에서는 저전압, 대전류응용을 예로 하여 PSFB 컨버터 최적 트랜스포머 설계를 위한 주요설계 요소들을 분석하고 설계에 필요한 이론적 수식들을 정립하였다. 정립된 이론을 바탕으로 1200W, 12V 출력 응용을 위한 트랜스포머 제작하였고, 제작된 트랜스포머는 실제 제품에 장착되어 사용되고 있다.

# 감사의 글

본 논문은 2015년도 정부의 재원으로 한국연구 재단의 지원을 받아 수행된 이공분야기초연구사 업임(NRF-2015R1C1A1A01051992)

#### References

- [1] I. Lee and G. Moon, "Soft-Switching DC/DC Converter with a Full ZVS Range and Reduced Output Filter for High-Voltage Applications," *IEEE Trans. Power Electron*, vol. 28, no. 1, Jan. 2013, pp. 112-122.

- [2] I. Lee, S. Cho, and G. Moon, "Improved Phase-Shift PWM Converters for larger-sized PDP slim sustain power module," *IEEE Trans. Power Electron*, vol. 28, no. 2, Feb. 2013, pp. 945-958.

- [3] I. Lee and G. Woon, "Half-bridge Integrated ZVS Full-Bridge Converter With Reduced Conduction Loss for Electric Vehicle Battery Chargers," *IEEE Trans. Ind. Electron*, vol. 61, no. 8, Aug. 2014, pp. 3978-3988.

- [4] Y. Chai and W. Do, "Development of 2kW Power Bidirectional LDC for Electric Vehicle," *J. of the Korea Institute of Electronic Communication Sciences*, vol. 11, no. 1, 2016, pp. 65-72.

- [5] Y. Cho and J. Lai, "Digital Plug-In Repetitive

- Controller for Single-Phase Bridgeless PFC Converters," *IEEE Trans. Power Electron*, vol. 28, no. 1, Jan. 2013, pp. 165-175.

- [6] L. Mweene, C. Aright, and M. Schlecht, "A 1 kW 500 kHz Front-End Converter for a Distributed Power Supply System," *IEEE Trans. Power Electron*, vol. 6, no. 3, July 1991, pp. 398-407.

- [7] C. Jung, "Design Procedures of LLC Resonant Converter for Electric Vehicle On-Board Charger," J. of the Korea Institute of Electronic Communication Sciences, vol. 9, no. 1, 2014, pp. 91-96.

- [8] C. Jung, "Input Ripple Current Formula Analysis of Multi-Stage Interleaved Boost Converter," J. of the Korea Institute of Electronic Communication Sciences, vol. 6, no. 6, 2011, pp. 865-871.

- [9] R. Ayyanar and N. Mohan, "Novel Soft-Switching DC-DC Converter with Full ZVS-Range and Reduced Filter Requirement," IEEE Trans. Power Electron, vol. 16, no. 2, March 2001, pp. 184-192.

- [10] J. Cho, K. Park, J. Park, G. Moon, and M. Youn, "Design of a Digital Offset Compensator Eliminating Transformer Magnetizing Current Offset of a Phase-Shift Full-Bridge Converter," IEEE Trans. Power Electron, vol. 27, no. 1, Jan. 2012, pp. 331-341.

# 저자 소개

### 이일운(II-Oun Lee)

2000년 경북대학교 전자전기공학부 졸업(공학사) 2003년 서울대학교 대학원 전기컴

2003년 서울대학교 대학원 전기록 퓨터공학과 졸업(공학석사)

2013년 한국과학기술원 대학원 전기및전자공학과 졸 업(공학박사)

2003년~2008년 삼성SDI PDP개발팀 전임연구원

2008년~2013년 삼성전기 Power개발팀 책임연구원

2014년~2015년 한국에너지기술연구원 선임연구원

2015년~현재 계명대학교 전기에너지공학전공 조교수