**JPE 16-5-30**

http://dx.doi.org/10.6113/JPE.2016.16.5.1918 ISSN(Print): 1598-2092 / ISSN(Online): 2093-4718

# Active Frequency Drift Method for Islanding Detection Applied to Micro-inverter with Uncontrollable Reactive Power

Raeho Kwak\*, June-Hee Lee\*, and Kyo-Beum Lee†

\*,†Department of Electrical and Computer Engineering, Ajou University, Suwon, Korea

#### **Abstract**

This paper proposes active frequency drift (AFD) as an anti-islanding method applied to micro-inverters with uncontrollable reactive power. When using ordinary inverter topologies, such as full bridge inverters in photovoltaic systems, the islanding phenomenon can be detected with reactive power-based methods, such as reactive power variation. However, when the inverter topology cannot control the reactive power, conventional anti-islanding methods with reactive power cannot be utilized. In this work, the topology used in this paper cannot control the reactive power. Thus, an anti-islanding method that can be used in topologies that cannot control the reactive power is proposed. The conventional anti-islanding method of the topology that cannot control reactive power is introduced and analyzed. Unlike the conventional AFD method, the proposed method extends a zero current interval every predetermined cycle. The proposed method offers certain advantages over conventional AFD methods, such as total harmonic distortion. The proposed method is validated through simulation and experiment.

Key words: Active Frequency Drift (AFD), Anti-islanding, Grid-connected inverter, Islanding phenomenon, Micro-inverter

#### I. INTRODUCTION

Fossil fuels and greenhouse gas emissions have been cited as major causes of climate change and environmental pollution. The gradual reduction of fossil fuel use is now a major issue [1]. Recently, small-scale power systems have attracted attention. In micro-grid systems, electric power generated from distributed generation (DG), such as solar energy or wind power, can be supplied to a local load independently and to a connected main grid in cases of surplus power [2], [3].

In these small-scale power systems, the DC power generated by renewable energy must be converted to AC power prior to grid connection. Accordingly, research into inverters and DC–AC conversion systems has been actively conducted [4]-[7].

In DGs that are directly connected to a grid, the islanding phenomenon can occur during unplanned disconnections from the grid. Specifically, islanding occurs when the grid-connected inverter of the DG and part of the local load are disconnected from the rest of the grid. If this phenomenon is not detected and the generation from a photovoltaic (PV) or other energy source remains operative, the islanded DG system remains energized by the inverter. The islanding phenomenon in PV systems is one of the most important problems in this area because it poses a safety hazard to repair and maintenance personnel. Moreover, islanding may damage inverters and loads in cases of unsynchronized re-closers of the main grid owing to a phase difference in voltage between the grid and the inverter [8]-[10].

$$P_{load} = P + \Delta P = \frac{V_L^2}{R} \tag{1}$$

$$Q_{load} = Q + \Delta Q = V_L^2 \times \left[ (\omega L)^{-1} - \omega C \right]$$

(2)

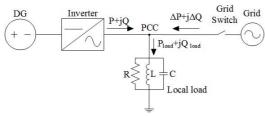

Several anti-islanding methods have been developed in the past decade. Anti-islanding methods resident in inverters have been classified as passive and active, whereas methods nonresident in inverters can be obtained using a specific communication system between the point of common coupling (PCC) and the inverter as shown in Fig. 1 [11], [12]. Passive techniques measure voltage, frequency, harmonic characteristics, and so on. Equations (1) and (2) describe the

Manuscript received Jun. 9, 2015; accepted May 3, 2016

Recommended for publication by Associate Editor Alian Chen.

<sup>&</sup>lt;sup>†</sup>Corresponding Author: kyl@ajou.ac.kr

Tel: +82-31-219-2376, Fax: +82-31-212-9531, Ajou University

<sup>\*</sup>Dept. of Electrical and Computer Eng., Ajou University, Korea

Fig. 1. PV system overview.

active and reactive power being consumed by the local load shown in Fig. 1. Equations (1) and (2) show that if the active or reactive power production of the PV system and the active or reactive power demand of the local load are mismatched in the island, the magnitude or frequency of the voltage at the PCC must change until  $P_{load} = P$  or  $Q_{load} = Q$  [13].

However, when the output power of the DG is equivalent to the local load, a non-detection zone (NDZ) emerges. If the output power falls in the NDZ, passive techniques fail to detect islanding. Such drawback is addressed through active techniques. In most cases, active techniques are more effective and robust than passive ones. Thus, in most grid-connected inverters, active techniques are more frequently used than passive techniques [14], [15].

Most inverters can control their reactive power. Therefore, most inverters detect islanding by applying reactive power variation (RPV). However, inverters that cannot control the reactive power depending on the switching method cannot apply RPV. In this case, other methods must be used.

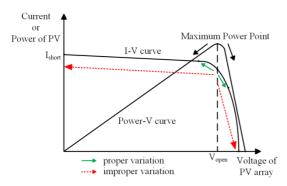

Conventionally, in inverters that cannot control reactive power, methods that periodically change the active power of the inverters are used. However, in such methods, the inverters can be stopped in the maximum power point tracking (MPPT) control if the active power varies excessively.

This paper proposes a novel active frequency drift (AFD) method with a pulsation of zero current intervals. The applied switching method of a bridgeless inverter that cannot control the reactive power is used to verify the proposed algorithm.

This paper is organized into six sections. Section II presents the operational principle of the topology used in this paper. Section III describes the principles of the proposed method. Sections IV and V present the simulation and experimental results, respectively. Section VI provides the conclusions.

### II. OPERATION PRINCIPLE OF THE TOPOLOGY

# A. Basic Operation Principle of Single-Phase Bridgeless Inverter

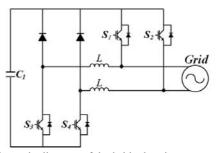

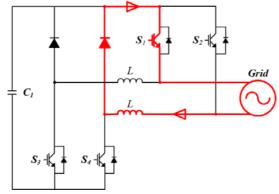

Fig. 2 shows the bridgeless inverter topology used in this paper. Unlike the conventional bridgeless inverter topology, the topology used in this paper comprises two additional switches. The additional switches are connected in parallel to

Fig. 2. Schematic diagram of the bridgeless inverter.

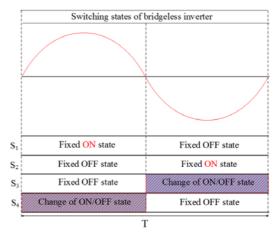

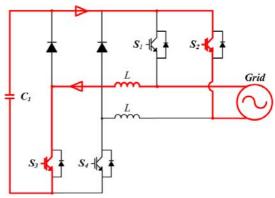

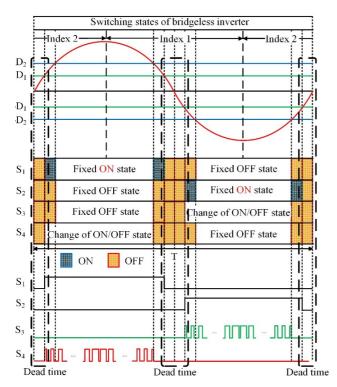

Fig. 3. Switching state of the bridgeless inverter.

the diode in the pole as depicted in Fig. 3. The proposed topology minimizes the ground leakage current of the panel. This topology can also achieve a relatively high efficiency because the inductors only carry current in the half cycle [19].

The switching method of the inverter is operated by a sinusoidal wave obtained from the grid voltage. The sinusoidal wave of the grid voltage is obtained by dividing the grid voltage by its magnitude; it is expressed as

$$v_{grid} = V_{mag} \sin(\omega t) \tag{3}$$

$$\sin(\omega t) = \frac{v_{grid}}{V_{mag}} \tag{4}$$

$$I_{ref} = I_{mag} \cdot |\sin(\omega t)| \tag{5}$$

If the current reference is obtained with (5), the output current of the inverter shares the same phase angle as the grid voltage. Therefore, during a normal grid-connected operation, the inverter normally operates with a unity power factor, is synchronized with the grid voltage, and operates at the grid frequency [8].

In the case of a positive half cycle in the sinusoidal wave,  $S_I$  is always turned on, whereas  $S_4$  is repeatedly turned on and off to track the current reference via pulse width modulation (PWM). Similarly, in the case of a negative half cycle in the sinusoidal wave,  $S_2$  is always turned on, whereas  $S_3$  is repeatedly turned on and off to track the current reference via PWM. Fig. 3 presents the switching states of the bridgeless

Fig. 4. Current path when  $S_1$  and  $S_4$  are turned on.

Fig. 5. Current path when  $S_I$  is turned on and  $S_4$  is turned off.

inverter [16], [17].

When the inverter is controlled with the above method, it cannot control the reactive power, as the topology is controlled with a unity power factor. If the grid voltage is synchronized to active power, the output current of the inverter is also synchronized to active power. Therefore, the inverter topology shown in Fig. 2 cannot control the reactive power.

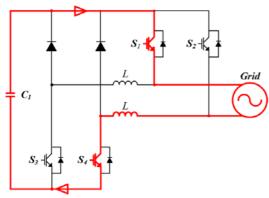

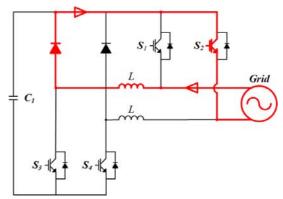

# B. Current Path of the Topology Based on Switching States

The current paths of the bridgeless inverter used in this paper are categorized into four types according to switching states. In the positive half cycle of the sinusoidal wave (i.e., when the grid is positive),  $S_I$  and  $S_4$  operate. In Fig. 4,  $S_I$  and  $S_4$  are turned on. In this case, the DC power source in the input stage supplies power to the output stage and stores energy in the inductor. In Fig. 5,  $S_I$  is turned on, and  $S_4$  is turned off. Freewheeling current flows to the grid using the inductor energy that is stored while  $S_4$  is turned on.

In the negative half cycle of the sinusoidal wave (i.e., when the grid is negative), current flows in the same way as that in the positive half cycle.  $S_2$  and  $S_3$  operate in the negative half cycle. In Fig. 6,  $S_2$  and  $S_3$  are turned on. The DC power source in the input stage supplies power to the output stage and stores energy in the inductor, as in the positive cycle. In Fig. 7,  $S_2$  is turned on, and  $S_3$  is turned off. Freewheeling

Fig. 6. Current path when  $S_2$  and S3 are turned on.

Fig. 7. Current path when  $S_2$  is turned on and  $S_3$  is turned off.

current flows to the grid using the inductor energy that is stored while  $S_3$  is turned on.

### C. Switching Method Applied to the Topology

The topology shown in Fig. 2 is controlled by dividing the sinusoidal wave (i.e., the grid voltage) into the positive and negative half cycles. However, if this method is directly applied to the topology, excessive surge current occurs at the zero crossing point of the grid voltage. Such current can cause the breakdown of switches and adversely affect the total harmonic distortion (THD) of the output current. Such surge current must be eliminated.

The modified switching method is applied to the topology to eliminate the surge current. In the modified switching method, the dead time is injected to the switches around the zero crossing point of the grid voltage. All switches are then turned off during the dead time, thus eliminating the surge current.

The sinusoidal wave (i.e., grid voltage) is divided into several sectors to inject dead time as shown in Fig. 8. On the basis of the sinusoidal wave,  $90^{\circ} \le \omega t \le 270^{\circ}$  is defined as *index 1*, and the remaining interval is defined as *index 2*. The index is divided by phase angle to classify the direction of the sinusoidal wave as increasing or decreasing. As shown in Fig. 8, the slope of the sinusoidal wave in *index 1* is negative, whereas that in *index 2* is positive.

In the latter case,  $D_1$  and  $D_2$  are defined. Unlike in *indexes*

Fig. 8. Switching method of the topology.

I and 2, which are classified in terms of the increasing or decreasing direction of the sinusoidal wave,  $D_1$  and  $D_2$  remain constants when determining the amount of dead time. This condition is necessary because switching occurs when  $D_1$  and  $D_2$  intersect with the sinusoidal wave, in which case dead time increases or decreases, that is,  $D_1$  and  $D_2$  increase or decrease, respectively (Fig. 8).

If  $D_1 < sin(\omega t) \le D_2$  in index 1 and the conventional switching method in subsection A is applied to the topology, the switches operate in the positive half cycle. In the modified switching method, high-frequency switch  $S_4$  is turned off first. When  $-D_1 < sin(\omega t) \le D_1$  in index 1, all switches are turned off by turning off  $S_I$ , which is a low frequency switch. When  $-D_2 < sin(\omega t) \le -D_1$ , the dead time is injected into the introduction of the negative half cycle (i.e.  $-D_1 < sin(\omega t) \le 0$ ), with  $S_2$  and  $S_3$  operated at the same time (Fig. 8). Similarly,  $-D_1$  and  $-D_2$  are used to inject the dead time at the zero crossing of the grid voltage in *index 2*. When  $-D_2 < sin(\omega t) \le -D_1$  in index 2, high-frequency switch  $S_3$  is turned off first. When  $-D_1 < sin(\omega t) \le D_1$  in index 2, all switches are turned off by turning off  $S_I$ , which is a low-frequency switch. The dead time is also injected into the introduction of the positive half cycle (i.e.,  $0 < \sin(\omega t) \le D_1$ ), with  $S_1$  and  $S_4$  operated simultaneously (Fig. 8).

The division of energy in  $D_1$  and  $D_2$  is caused by the energy stored in the inductors as explained in subsection A. To minimize the distortion of the current in the next switching state, such stored energy must be eliminated by turning off the bottom switch in advance.

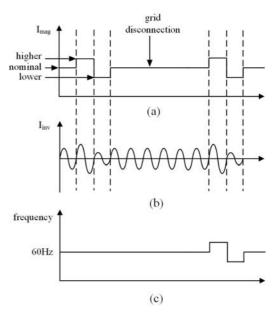

Fig. 9. Anti-islanding method about active power variation. (a) Magnitude of inverter output current. (b) Inverter output current; (c) Frequency of output voltage.

#### III. PROPOSED ANTI-ISLANDING METHOD

# A. Conventional Anti-Islanding Method in the Topology That Cannot Control the Reactive Power

The topology shown in Fig. 2 cannot control reactive power as mentioned in Section II.A. Therefore, commonly used conventional anti-islanding methods, such as RPV, that vary the reactive power cannot be applied to this topology. In this case, the islanding phenomenon is detected by using active power, which can be controlled by the topology. The typical method that uses active power is the active power variation (APV) method.

The APV method varies the output current reference periodically as depicted in Fig. 9 (a). In this case, if islanding occurs, islanding detection is realized with the magnitude variation of the PCC voltage. This method only varies the output current reference; it does not vary the frequency and phase of the output current. The APV method also exhibits better characteristics in terms of the THD of the output current in comparison with the methods that vary the frequency of the voltage.

However, the APV method varies the output current reference periodically (the shape of the output current is shown in Fig. 9 (b)). When the inverter performs MPPT in this situation, the perturbation and observation (P&O) method is typically used. In the P&O method, the PV cell voltage is repeatedly decreased from the PV open voltage, and the PV cell output power of the previous period is compared with that of the present period to continuously track the maximum power point [1]. In this situation, if the active power varies excessively, the PV cell current short circuits, the PV voltage

Fig. 10. MPPT operation of PV module.

Fig. 11. Inverter output current of AFD method.

(i.e., the inverter input voltage) suddenly becomes zero (Fig. 10), and the inverter stops operation unexpectedly. In sum, the critical drawback of this method is that the system operates precariously depending on the amount of APV.

# B. Basic Principle of AFD Method

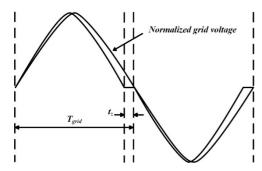

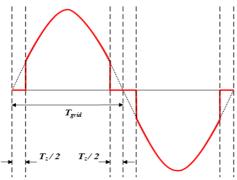

The AFD method adds a short period of zero conduction interval into the inverter output current, thus causing a phase difference between the current and the voltage at the PCC as depicted in Fig. 11 [20]. The zero conduction interval causes the current injected into the grid by the DG to be slightly distorted (6) such that when islanding occurs, the frequency of the PCC voltage drifts up or down according to (2) [9].

$$i_{AFD}(t) = \begin{cases} I \sin(2\pi f't) & \to & 0 \le \omega t < \pi - t_z \\ 0 & \to & \pi - t_z \le \omega t < \pi \\ I \sin(2\pi f't) & \to & \pi \le \omega t < 2\pi - t_z \\ 0 & \to & 2\pi - t_z \le \omega t < 2\pi \end{cases}$$

(6)

where

$$f'$$

is  $f\left(\frac{1}{1-cf}\right)$ .

Introducing the zero conduction interval  $t_z$  at the end of each half cycle causes the phase angle of the fundamental component of the current to shift. The chopping fraction cf is the ratio of the zero conduction interval  $t_z$  to half of the period of the voltage waveform  $T_{grid}$ . cf, defined in (7), determines the difference between the frequency of the inverter output current and the frequency of the grid voltage.

$$cf = \frac{t_z}{T_{grid}} \tag{7}$$

Fig. 12. AFD operation by load condition. (a) Resistive load. (b) Inductive load. (c) Capacitive load.

The grid-connected inverter normally operates with a unity power factor. The inverter generates an output voltage that is synchronized with the grid voltage; thus, the frequency of the output voltage is equal to the grid frequency [9]. When islanding occurs, the added zero conduction in the current produces a permanent drift in the operating frequency toward the resonance frequency of the local load to maintain a unity power factor. Therefore, the frequency of the PCC voltage increases or decreases because of islanding. This frequency drift eventually reaches the frequency boundary limits to detect islanding [8].

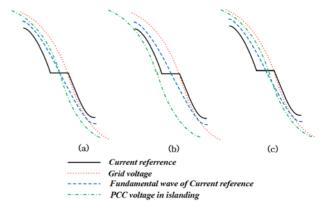

Fig. 12 shows the operational overview of the PCC voltage and current in the AFD method. The local load in Fig. 1 is divided into resistive load, inductive load, and capacitive load. In the case of resistive load in Fig. 12 (a), when islanding occurs, the PCC voltage must have the same phase as the fundamental wave of the current reference. In such a case, the frequency of the PCC voltage is higher than that of the PCC voltage under a normal operation. As the voltage leads the current in the case of an inductive load in Fig. 12 (b), the frequency of the PCC voltage increases and exceeds the resistive load. Consequently, islanding can be detected by checking the increase in frequency under the resistive and inductive loads. However, in the case of capacitive load as depicted in Fig. 12 (c), the frequency of the PCC voltage can be either increased or decreased. Thus, the islanding phenomenon cannot be detected [20].

# C. Principle of the Proposed Method

The AFD method generates a zero conduction interval, and the zero conduction time injects reactive power into the output current. The conventional AFD method generates a precise sinusoidal wave in the non-zero conduction interval (Fig. 11). By contrast, the topology used in the present work cannot produce an output current in the form of a precise sinusoidal wave. Such form can only be realized when the reactive power can be controlled. However, if the switching method in Section II.C is applied to the topology, it easily inject the zero conduction interval into the output current. If

Fig. 13. Normalized inverter output current waveform.

the zero conduction interval is injected into the topology by applying the switching method in Section II.C, the output current is obtained as shown in Fig. 13. The waveform of the output current in Fig. 13 does not have the ideal shape shown in Fig. 11, but its shape is nonetheless similar to the ideal one. Therefore, the AFD method could be applied to the topology. The injected reactive power could also be obtained by producing the zero conduction interval using a switching method in the topology that cannot control the reactive power.

As mentioned in Section III.C, the AFD method detects islanding by checking changes in the frequency of the PCC voltage. As power mismatch generally exists in the PCC voltage (i.e.,  $\Delta P \neq 0$ ,  $\Delta Q \neq 0$ ), the magnitude and frequency of the PCC voltage are changed by this power mismatch when islanding occurs. The relationship between the ratio of the power mismatch and the threshold condition of the magnitude and frequency of the PCC voltage can be expressed as

$$\left(\frac{V}{V_{\text{max}}}\right)^2 - 1 \le \frac{\Delta P}{P} \le \left(\frac{V}{V_{\text{min}}}\right)^2 - 1 \tag{8}$$

$$Q_f \left( 1 - \left( \frac{f}{f_{\min}} \right)^2 \right) \le \frac{\Delta Q}{P} \le Q_f \left( 1 - \left( \frac{f}{f_{\max}} \right)^2 \right) \tag{9}$$

where  $V_{max}$ =110%,  $V_{min}$ =88%, f=60Hz,  $f_{max}$ =60.5Hz, and  $f_{min}$ =59.3Hz [21]. These values are substituted into (8) and (9) as follows:

$$-17.36\% \le \frac{\Delta P}{P} \le 29.13\%$$

(10)

$$-2.37\% \le \frac{\Delta Q}{P} \le 1.65\% \tag{11}$$

As shown in (8) and (9), (9) is related to the frequency. Given that the AFD method is related to the frequency, (9) must be applied to use the AFD method in the topology.

Under a grid-connected operation, the inverter is controlled such that it has the same phase angle for the current and voltage. Therefore, the displacement factor (DPF) of the inverter topology is controlled with unity. The DPF and PF show the following relationship:

$$PF = DF_i \times DPF \tag{12}$$

where  $DF_i$  is the distortion factor that represents the distortion degree of the current; it can be calculated as

$$DF_i = \sqrt{\frac{1}{1 + THD_i^2}} \tag{13}$$

As mentioned previously, the DPF of the inverter is controlled with unity.

$$PF = DF_i = \frac{1}{\sqrt{1 + THD_i^2}} \tag{14}$$

PF is the ratio of the active power and the apparent power.

$$PF = \frac{P}{S} = \frac{P}{\sqrt{P^2 + Q^2}}$$

(15)

As (15) and (14) are equal, (16) is

$$\frac{Q}{P} = THD_i \tag{16}$$

Equations (10) and (11) show the NDZ resulting from a power mismatch [9], [10]. In the AFD method, increasing the injected reactive power to diminish the NDZ increases the output current THD because Q/P=THD, as shown in (16) [10]. Equation (11) is derived by applying the parameters to (9). If the mismatch of the reactive power lies in this interval, islanding is not detected.

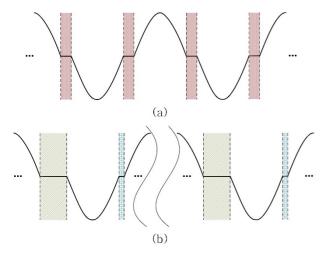

The proposed method involves changing the size of the zero conduction interval injected into the output current every certain period, with the size of the interval not being constant. When the magnitude of the zero conduction interval is increased, the mismatch of the reactive power is set to be sufficiently large to exceed the interval of (11) and thereby eliminate the NDZ. The other zero conduction interval is set to be sufficiently small to reduce the output current THD. Fig. 14 depicts the conventional AFD method and the proposed method.

In the proposed method, the switching method explained in section II.C can inject the zero conduction interval. The zero conduction interval can be controlled by  $D_1$  and  $D_2$ .  $D_1$  and  $D_2$  are increased in the cycle of the extended zero conduction interval and decreased in the cycle of the reduced zero conduction interval. In the proposed method, cf is increased in the cycle of the extended zero conduction interval. Therefore, the proposed method can control cf through  $D_1$  and  $D_2$ .

In sum, the proposed method can be considered to control the output current THD through  $D_1$  and  $D_2$ . Therefore, the proposed method can control the reactive power through (16), which is not related to the active power, because the proposed method perturbs the THD of the output current, assuming that  $\Delta P/P$  is nearly zero. If the mismatch of the reactive power lies in the interval of (11) at the moment that the islanding phenomenon occurs, then the mismatch of the reactive power depending on cf can be expressed as

$$\frac{\Delta Q + Q_{cf}}{P} \ge 1.65 \text{ where } -2.37 \le \frac{\Delta Q}{P} \le 1.65$$

(17)

Fig. 14. Operation of anti-islanding method. (a) Conventional AFD. (b) Proposed AFD.

Fig. 15. THDi vs. chopping fraction for the waveform in Fig. 11.

If islanding occurs when the proposed method is not applied, then the frequency of the PCC voltage lies in the NDZ (11), and islanding is not detected. Therefore, the proposed method causes a mismatch of reactive power in the output current and must thus make the output current leave the NDZ (11) to detect islanding. In this situation, the proposed method effectively injects reactive power.

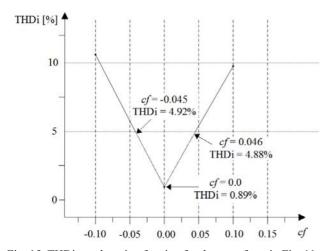

The IEEE 1547 standard stipulates that the THD of the inverter output current should not exceed 5%. To satisfy this condition, a relationship must be established between *cf* and the THD of the output current. Fig. 15 shows the relationship between the THD of the output current and *cf* obtained via simulation. As shown in Fig. 15, a proportional relationship exists between the magnitude of *cf* and the THD. Fig. 15 shows that when *cf* is between -0.045 and 0.046, the THD of the output current is less than 5%. Thus, the range of *cf* that can be maximally used satisfies IEEE 1547.

Equation (17) shows the extent to which reactive power is injected into the output current using the proposed method. The proposed method extends the zero current interval every

predetermined cycle, as in the analysis in which cf is extended periodically. Therefore, cf is determined using (17). In the worst case, if the reactive power mismatch  $\Delta Q/P$  is -2.37%, which is the lower limit of the NDZ, then  $Q_c/P$  must be injected by 4.02 to cause the output current to leave the NDZ (11). Using (15) and (16),  $Q_c/P$  can be calculated as

$$\frac{Q_{cf}}{P} = THD_i = 4.02 \tag{18}$$

As indicated in (18) and Fig. 15, cf is approximately 0.04 when the THD of the output current is 4.02. If cf is 0.046, then islanding can be detected effectively, and the THD of the output current is less than 5%. The zero conduction interval is calculated using cf as follows:

$$cf = \frac{t_z}{T_{grid}} = \frac{t_z}{8.3333 \times 10^{-3}} = 0.046$$

$$t_z = 3.8333 \times 10^{-4} [\text{sec}]$$

(19)

$$D_1 = \sin[2\pi f (T_{orid} - t_z)] = 0.1440$$

(20)

$$D_2 = 2D_1 = 0.2880 \tag{21}$$

$D_I$  is determined via mathematical calculation.  $D_2$  is set to be twice the value of  $D_I$  to consume the energy stored in the inductors on the output side.

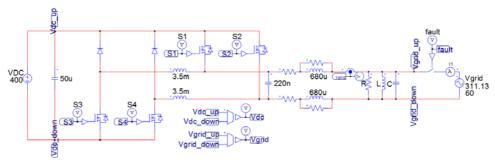

# IV. SIMULATION RESULTS

A simulation was conducted using PSIM software to validate the proposed method using the circuit configuration in Fig. 16. The simulation parameters are listed in Table I.

The load for the anti-islanding test must be designed to completely consume the rated power supplied by the inverter. The procedure of the load design is as follows:

$$R_{load} = \frac{V_{out}^2}{P_{out}} \tag{22}$$

$$L_{load} = \frac{R_{load}}{2\pi f_0 Q_f} \tag{23}$$

$$C_{load} = \frac{Q_f}{2\pi f_0 R_{load}} \tag{24}$$

where  $P_{load}$  is the rated power of the inverter,  $V_{out}$  is the root mean square voltage of the inverter output phase voltage,  $f_0$  is the resonance frequency, and  $Q_f$  is the quality factor that represents the ratio of the energy lost in one cycle and the average maximum energy stored in the load.

Equation (22) is used to calculate load resistance  $R_{load}$  and simulate the inverter with a 300 W rated power.  $Q_f$  is set to 1 to calculate the load inductor and capacitor ( $L_{load}$  and  $C_{load}$ , respectively), and the resonance frequency is 60 Hz. Using (23) and (24) and these parameters,  $L_{load}$  and  $C_{load}$  are calculated. The calculated values of the load are listed in Table I.

Thus, the input DC voltage is set to 400 V to supply input

Fig. 16. Schematic Circuit of PSIM.

TABLE I

PSIM SIMULATION AND EXPERIMENT PARAMETERS

| 1 SIM SIMULATION AND LAFERIMENT I ARAMETERS |                              |

|---------------------------------------------|------------------------------|

| Parameters                                  | Values                       |

| $Q_f$                                       | 1                            |

|                                             | $R_{load} = 161.33 [\Omega]$ |

| Load impedance (RLC)                        | $L_{load} = 0.4279 [H]$      |

|                                             | $C_{load} = 16.44  [\mu F]$  |

| Inverter rated power                        | 300 [W]                      |

| Rated voltage                               | 220 [V]                      |

| Rated frequency                             | 60 [Hz]                      |

| Rated frequency range                       | 59.3 < <i>f</i> < 60.5 [Hz]  |

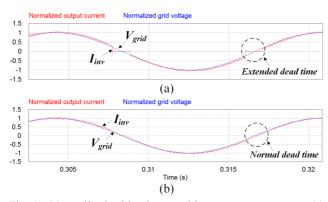

Fig. 17. Normalized grid voltage and inverter output current. (a) Extended dead time. (b) Normal dead time.

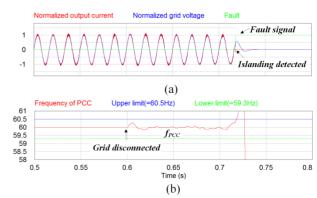

DC power to the grid. Fig. 17 shows the waveform of the output current with the application of  $D_1$  and  $D_2$ , which are calculated in Section III.C. Fig. 17 (a) shows the case with the expanded zero conduction interval, and Fig. 17 (b) shows the case with the normal zero conduction interval. Fig. 18 shows that islanding is detected by applying the proposed method in the case in which the frequency of the PCC voltage is in the normal interval. As mentioned in Section III.B, the frequency indeed increases beyond the normal operating range.

# V. EXPERIMENTAL RESULTS

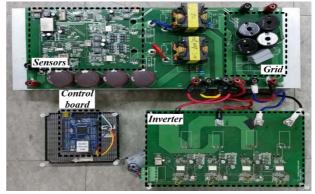

The proposed method is validated through experiments conducted with the 300 W grid-connected micro inverter set (Fig. 19). The experimental set comprises a control board, sensors, an inverter, and a grid. The RLC load calculated in

Fig. 18. Islanding detection test for an inverter. (a) PCC voltage, inverter current, fault signal. (b) Frequency of PCC voltage.

Fig. 19. Experimental setup.

Section IV is connected to the inverter. The inverter is controlled under current control mode by employing a STM32F405RG in the ARM-Cortex M4 family micro controller unit (MCU). The proposed anti-islanding algorithms are implemented in the MCU. In this experiment, the MCU generates 50 kHz PWM gate signals to implement a proportional—integral (PI) controller, which is a typical controller for single-phase AC systems.

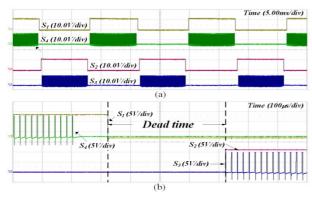

Fig. 20 shows the waveform of the switch operation. In Fig. 20 (b), the lower switch  $S_4$  is turned off in advance, then  $S_1$  is turned off to provide the freewheeling path mentioned in Section II.C. As a result, the dead time in which all the switches are turned off is formed after  $S_1$  is turned off and before  $S_2$  is turned on.

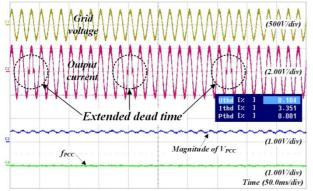

Fig. 21 shows the waveform of the proposed method

Fig. 20. Waveform of switch operation (experimental waveform). (a) Waveform of switch operation (ordinary). (b) Waveform of switch operation (enlarged).

Fig. 21. Output waveform using proposed method before islanding (experimental waveform).

applied to the inverter before the grid is disconnected. The zero conduction interval of the output current is extended periodically. In the experiment, the zero conduction interval of the output current is extended every 10 cycles of the grid voltage. When the grid is connected, the magnitude and frequency of the PCC voltage are maintained. However, the THD in the current is increased because of the extended zero conduction interval in the proposed method. A YOKOGAWA WT3000 power analyzer is used to measure the THD of the grid voltage and the output current, which are 0.104% and 3.351%, respectively.

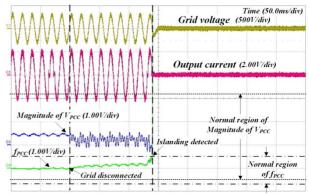

Fig. 22 shows that islanding is detected using the proposed method. If the grid is disconnected at an arbitrary time, islanding occurs until the output current enters the extended zero conduction cycle. The islanding phenomenon is detected in the extended zero conduction cycle. Therefore, once islanding occurs, the magnitude and frequency of the PCC voltage fall in the normal operating range. The frequency of the PCC voltage is then increased until it is out of the normal operating range in the extended zero conduction cycle. Finally, the inverter is shut down. Fig. 22 shows the procedure for detecting the islanding phenomenon with this process.

The experimental results in Figs. 21 and 22 match the simulation results of Figs. 17 and 18, respectively.

Fig. 22. Anti-islanding test result for proposed method (experimental waveform).

#### VI. CONCLUSIONS

This study proposes an anti-islanding method that is based on an application of the AFD method that periodically perturbs the zero conduction interval in an inverter topology that cannot control the reactive power. If the proposed method is applied to the said topology, the reactive power can be controlled indirectly by using the switching method and perturbing the output current. Thus, the islanding phenomenon can be detected by varying the reactive power. The simulation and experimental results demonstrate that the proposed method can effectively detect islanding in the inverter topology used in this work.

# ACKNOWLEDGMENT

This work was supported by the Basic Science Research Program through the National Research Foundation of Korea (NRF) funded by the Ministry of Science, ICT and Future Planning (2016R1A2B4010636) and the Human Resources Program in Energy Technology through the Korea Institute of Energy Technology Evaluation and Planning (KETEP), which was granted financial resource from the Ministry of Trade, Industry & Energy, Republic of Korea. (No. 20134030200310)

# REFERENCES

- [1] J. H. Lee, J. S. Lee, and K. B. Lee, "Current sensorless MPPT control method for dual-mode PV module-type interleaved flyback inverters," *Journal of Power Electronics*, Vol. 15, No. 1, pp. 54-64, Jan. 2015.

- [2] A. Kirubakaran, S. Jain, and R. K. Nema, "DSP-controlled power electronic interface for fuel-cell-based distributed generation," *IEEE Trans. Power Electron.*, Vol. 26, No. 12, pp. 3853-3864, Apr. 2011.

- [3] T. L. Lee and P. T. Cheng, "Design of a new cooperative harmonic filtering strategy for distributed generation interface converters in an islanding network," *IEEE Trans. Power Electron.*, Vol. 22, No. 5, pp. 1919-1927, Sep. 2007.

- [4] G. S Kim, K. B. Lee, D. C. Lee, and J. M. Kim, "Fault

- diagnosis and fault-tolerant control of DC-link voltage sensor for two-stage three-phase grid-connected PV inverters," *Journal of Electrical Engineering & Technology*, vol. 8, No. 4, pp. 752-759, Jul. 2013.

- [5] Y. Chen, and K. Smedley, "Three-Phase Boost-Type Grid-Connected Inverter," *IEEE Trans. Power Electron.*, Vol. 23, No. 5, pp. 2301-2309, Sep. 2008.

- [6] H. L. Jou, W. J. Chiang, and J. C. Wu, "A simplified control method for the grid-connected inverter with the function of islanding detection," *IEEE Trans. Power Electron.*, Vol. 23, No. 6, pp. 2775-2783, Nov. 2008.

- [7] M. A. Abusara, and S. M. Sharkh "Design and control of a grid-connected interleaved inverter," *IEEE Trans. Power Electron.*, Vol. 28, No. 2, pp. 748-764, Jun. 2012.

- [8] A. Yafaoui, B. Wu, and S. Kouro., "Improved active frequency drift anti-islanding detection method for grid connected photovoltaic systems," *IEEE Trans. Power Electron.*, Vol. 27, No. 5, pp. 2367-2375, May 2012.

- [9] M. E. Ropp, M. Begovic, and A. Rohatgi, "Analysis and performance assessment of the active frequency drift method of islanding prevention," *IEEE Trans. Energy Convers.*, Vol. 14, No. 3, pp. 810-816, Sep. 1999.

- [10] L. A. C. Lopes and H. Sun, "Performance assessment of active frequency drifting islanding detection methods," *IEEE Trans. Energy Convers.*, Vol. 21, No. 1, pp. 171-180, Mar. 2006.

- [11] C. Jeraputra and P. N. Enjeti, "Development of a robust anti-islanding algorithm for utility interconnection of distributed fuel cell powered generation," *IEEE Trans. Power Electron.*, Vol. 19, No. 5, pp. 1163-1170, Sept. 2004

- [12] M. Liserre, A. Pigazo, A. Dell'Aquila, and V. M. Moreno, "An anti-islanding method for single-phase inverters based on a grid voltage sensorless control," *IEEE Trans. Ind. Electron.*, Vol. 53, No. 5, pp. 1418-1426, Oct. 2006.

- [13] J. B. Jeong, H. J. Kim, S. H. Back, and K. S. Ahn, "An improved method for anti-islanding by reactive power control," in *Proc. ICEMS* 2005, Vol. 2, PP. 965-970, 2005.

- [14] C. C. Hou and Y. C. Chen, "Active anti-islanding detection based on pulse current injection for distributed generation systems," *IET Power Electronics*, Vol. 6, No. 8, pp. 1658-1667, Sep. 2013.

- [15] P. Du, J. K. Nelson, and Z. Ye, "Active anti-islanding schemes for synchronous-machine-based distributed generators," *Generation, Transmission and Distribution, IEE Proceedings*, Vol. 152, No. 5, pp. 597-606, 2005.

- [16] X. J. Yang, H. Wang, X. H. Yang, H. G. Lei, and H. Guan, "Theoretic analysis and experimental study of a novel bridgeless partial active PFC," in *Proc. ICEMS* 2008, pp.1179-1184, 2008.

- [17] S. Sajeev, and A. Mathew, "Novel cost effective induction motor drive with bridgeless PFC and four switch inverter," in *Proc. C2SPCA 2013*, pp. 1-6, 2013.

- [18] J. Wang, B. Ji, J. Zhao, and J. Yu, "From H4, H5 to H6 Standardization of full-bridge single phase photovoltaic inverter topologies without ground leakage current issue," in *Proc. IEEE ECCE 2012*, pp. 2419-2425, 2012.

- [19] S. K. Kim, J. H. Jeon, J. B. Ahn, B. Lee, and S. H. Kwon, "Frequency-shift acceleration control for anti-islanding of a distributed-generation inverter," *IEEE Trans. Ind. Electron.*, Vol. 57, No. 2, pp.434-504, Nov. 2009.

- [20] Z. Ye, A. Kolwalkar, Y. Zhang, P. Du, and R. Walling, "Evaluation of anti-islanding schemes based on nondetection zone concept," *IEEE Trans. Power Electron.*, Vol. 19, No. 5, pp.1171-1176, Sep. 2004.

Raeho Kwak received his B.S. degree in Electrical and Computer Engineering from Ajou University, Korea, in 2015. He is currently working toward his M.S. degree at Ajou University, Korea. His research interests include grid-connected systems, three-level inverter systems, and DC–DC converter systems.

June-Hee Lee was born in Korea. He received his B.S. degree in Electronic Engineering from Ajou University, Korea, in 2013. He is currently working toward his Ph.D. degree in Electronic Engineering at Ajou University, Korea. His research interests include power conversion and grid-connected systems.

**Kyo-Beum Lee** received his B.S. and M.S. degrees in Electrical and Electronic Engineering from Ajou University, Korea, in 1997 and 1999, respectively. He received his Ph.D. degree in Electrical Engineering from Korea University, Korea, in 2003. From 2003 to 2006, he worked with the Institute of Energy Technology, Aalborg University,

Aalborg, Denmark. From 2006 to 2007, he worked with the Division of Electronics and Information Engineering, Chonbuk National University, Jeonju, Korea. In 2007, he joined the School of Electrical and Computer Engineering, Ajou University, Suwon, Korea. His research interests include electric machine drives, renewable power generation, and electric vehicle applications. He is an associate editor of the IEEE Transactions on Power Electronics, the Journal of Power Electronics, and the Journal of Electrical Engineering & Technology.