# 디스플레이용 스위칭모드 전원장치의 단락 고장분석 검출기법

Techniques to Diagnose Short-Circuit Faults in the Switching Mode Power Supply for Display

이 재 원\*·전 태 원<sup>†</sup> (Jae-Won Lee · Tae-Won Chun)

**Abstract** - This paper proposes techniques to diagnose short-circuit faults of both the diodes and power FET in switching mode power supply (SMPS) by using a simple analog tester. The diodes in full-bridge rectifier, power FET, switching transformer, and some sensors are modelled with resistor. The total resistance value measured at the input terminal of a SMPS is analyzed when the short-circuit faults of diodes in a full bridge rectifier or power FET are occurred. The short-circuit faults of one or two diodes in a full bridge rectifier, power FET, and both the diodes in a full bridge rectifier and power FET can be detected by a range of total resistance, which is measured by the analog tester. Through experiments, the theoretical analysis for total resistance under short-circuit faults can be verified.

Key Words: Analog tester, Short-circuit fault, Switching Mode Power Supply (SMPS)

#### 1. 서 론

디스플레이용 스위칭모드 전원장치 고장은 대부분 전원장치내 4개의 다이오드로 구성된 단상 정류기의 다이오드와 전력용 FET의 단락회로 고장 또는 개방회로 고장 등에 의하여 발생된다. 이전원장치 고장 중 다이오드 정류기내 다이오드 고장은 직류단의 전압맥동을 발생시켜 출력단 인버터의 성능을 감소시키고 직류단커패시터의 수명을 단축시키며, 이 손상된 커패시터가 전체 시스템의 고장이나 사고를 유발하여 시스템전체의 안전성을 악화시키는 요인이 된다[1]. 또한 풍력터빈용 발전기구동장치에 사용되는다이오드 정류기의 개방고장 시 발전기의 토크리플 증가 및 직류단 커패시터 전압의 변동 등을 발생시킨다[2]. 그리고 다이오드및 FET 등 스위칭소자의 단락사고 시는 퓨즈가 단선되어 전원이차단됨으로써 전원장치가 완전히 정지됨으로써 전원공급이 중단되어 전압과 파형 측정도 불가능한 상태가 됨으로 고장진단에 어려움이 있다.

전력용 컨버터의 단락 또는 개방 고장 진단용으로 신경회로망 또는 적응 뉴로-퍼지 알고리즘을 사용하는 기법이 제시되었다 [3],[4]. 그리고 동기발전기의 회전자 여자기에 여자전류를 공급 하기 위한 다이오드정류기내 다이오드의 단락 또는 개방고장을 검출하기 위하여 여자전류의 고조파성분을 분석하는 방법 [5]-[7]과 전력용 컨버터 입력단에 있는 3상 다이오드 정류기 출력단 커패시터 전압리플을 분석하여 고장 진단방식[8]-[9] 등이 발표되었다.

그러나 이러한 기법들은 전류 또는 전압센서가 필요하며 전류의 고주파 분석 또는 커패시터전압 리플 성분을 분석하기 위한 장비가 요구된다. 그런데 산업현장에서는 이러한 기법들을 적용하기 위하여 고장발생시 고장진단을 위한 측정장비를 현장에 투입하여야 한다는 어려움이 있다. 그리고 다이오드 고장진단을 다룬 대부분 논문들은 개방고장에 중점을 두고 소개되었다[2], [6]-[9]. 그러나 실제로는 커패시터를 제외한 다이오드, 트랜지스터, FET 소자는 개방고장보다 단락고장이 월등히 많다. 그리고 트랜지스터 또는 FET의 두 단자 사이에 개방 고장이 발생할 경우에도 대부분 FET의 드레인-소스 (D-S) 사이에 이미 단락 상태임을 관찰할 수 있다. 앞에서 언급한 바와 같이 다이오드 1개만 단락되어도 단락되는 순간에 퓨즈가 바로 단선되어 전원을 공급할 수가 없으므로 고장진단을 위한 전압과 파형 측정도 불가능하여 고장진단에 상당히 어려움이 있는 실정이다.

따라서 본 논문에서는 이러한 문제점을 해결하기 위하여 디지털 테스터보다 순방향 또는 역방향 전압인가가 쉬운 아날로그 테스터를 사용하여 측정한 합성 저항값을 사용하여 전원장치의 단락고장 진단법을 제시한다. 다이오드 정류기내 다이오드의 단락고장일 경우, FET 단락고장일 경우와 다이오드 정류기의 다이오드와 FET 모두 단락 고장 시 각각 전원장치 회로의 각 소자별등가 저항을 분석하고, 실험을 통하여 이론적으로 해석한 합성저항값으로 전원장치의 단락고장을 진단하는 기법의 타당성을 확인한다.

E-mail: twchun@mail.ulsan.ac.kr

Received: January 9, 2016; Accepted: June 15, 2016

<sup>†</sup> Corresponding Author: Dept. of Electrical Engineering, University of Ulsan, Korea.

st Dept. of Electrical Engineering, University of Ulsan, Korea.

#### 2. 전원장치의 단락고장 진단방법

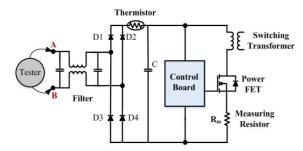

그림 1은 입력필터, 4개 다이오드로 구성된 다이오드정류기, 온도측정을 위한 서미스터, 정류용 커패시터, 전력용 FET 및 제 어회로, 전류측정용 저항과 부하와 연결된 변압기 등으로 구성된 전원장치 내 다이오드정류기와 스위칭소자 FET의 단락고장 진단을 위한 구성도이다.

그림 1 전원장치 고장검출회로 구성

Fig. 1 Configuration of fault detection in the power supply

전원장치내 다이오드정류기와 스위청소자 FET의 단락고장 진단을 위하여, 입력교류전압 220V대신 아날로그 테스터의 내부전압인 3V의 직류전압을 인가한다. 그리고 아날로그 테스터의 3V내부전압 극성을 순방향 및 역방향으로 바꾸면서 입력 측 A, B지점에서 전체 합성저항 값을 측정하여 전원회로의 단락고장을 진단하는 기법을 사용한다. 여기서 전원장치 내의 부품에서 단락고장 시 다양한 합성저항이 나타나며 순방향 저항값과 역방향 저항값이 동일하게 나타내면서 정상적인 동작하는 전원장치는 전무하다. 따라서 다이오드 정류기내 다이오드가 단락 시, FET가 단락 시, 다이오드와 FET 시 동시 단락 시 등 3가지 유형의 단락고장 시 각각 순방향 합성저항 값과 역방향 합성저항 값을 계산한다. 참고로 전원회로가 정상일 경우에는 순방향 및 역방향 전압 인가 시 모두 합성저항이 '∞'값이 나타난다.

한편 전류용량이 큰 반도체 소자는 장시간 동작에 대한 발열을 피할 수 없다. 방열판에 부착된 브릿지회로의 다이오드와 FET 스위칭소자는 도통 손실 및 스위칭 손실로 인하여 온도가상승하며 이 온도상승에 의해 다이오드 및 FET의 등가 저항값이변화된다. 그러나 이 온도상승에 따른 등가 저항값의 변동범위보다 정상상태와 단락 등 고장상태의 저항 차가 훨씬 높으므로소자의 온도에 대한 저항변화를 무시할 수 있다.

본 논문은 다이오드 정류기의 다이오드 단락고장 진단하는 방법을 기술하고, 다음은 FET의 단락고장 진단 방법과 다이오드 정류기와 FET 두 개 동시에 단락고장 시 진단하는 방법을 차례로 기술한다.

# 3. 다이오드 정류기의 단락고장 진단 방법

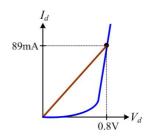

전원장치에서 다이오드정류기만 고려할 경우 다이오드 정류기 내 4개 다이오드 중 1개 다이오드가 단락 시와 2개 이상 다이오 도가 단락 시 각각 등가회로를 사용하여 순방향 및 역방향 전압 인가 시 합성저항을 유도한다. 한편 아날로그 테스터(Range×1)에서 저항 측정 시 +3 V전압이 출력되므로 이 테스터를 다이오드 순방향으로 연결 시, 다이오드에 +3 V 순방향 전압이 인가되어 다이오드가 도통된다. 그림 2와 같이 아날로그 테스터의 내부저항에 의해 다이오드 순방향 전압강하는 0.8 V가 되고 다이오드 순방향전류는 89 mA가 된다. 따라서 다이오드 등가저항 값은 다이오드 순방향 전압값에 순방향 전압값에 순방향 전류값을 나누면 약 9 요이 된다.

그림 2 다이오드 등가저항

Fig. 2 Equivalent resistance of diode

#### 3.1 브릿지 정류기 1개 다이오드 단락 시 합성저항

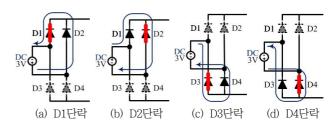

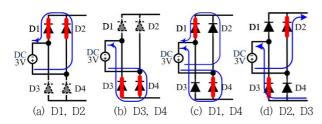

그림 3은 브릿지 정류기회로의 4개 다이오드 중 한 개 다이오드가 단락된 상태에서 테스터로 3 V 전압을 순방향 또는 역방향으로 공급하였을 때 한 개 다이오드가 도통되어 합성저항이 9  $\Omega$ 이 될 경우 등가회로를 보인 것이다.

그림 3 한 개 다이오드가 단락 시 등가회로

Fig. 3 Equivalent circuits under one diode short condition

그림 3(a)는 다이오드 D1이 단락 시 테스터로 3 V를 역방향으로 인가할 경우 D1와 D2를 통하여 전류가 흐른다. 단락된 다이오드 D1의 등가저항은 0 요이며 순방향으로 도통된 다이오드 D2의 등가저항은 9 요이므로, 합성저항은 약 9 요으로 나타난다. 만약 테스터로 3 V 순방향 전압을 인가할 경우에는 D1-FET-D4를 통하는 루프 형성되는데 FET가 오프상태이므로 합성저항은 거의 ∞가 된다. 같은 방법으로 그림 3(b)는 다이오드 D2 단락시 순방향으로 전압을 인가하면 합성저항은 정상 다이오드 D1의 등가저항인 9 요이 된다. 3 V 역방향 전압을 인가할 경우에는 합성저항이 거의 ∞가 된다. 그림 3(c)와 같이 다이오드 D3 단락시 순방향 전압을 인가할 경우와 그림 3(d)와 같이 다이오드 D4단락시 역방향 전압을 인가하면 합성저항은 역시 9 요이 된다. 여기서 D3 단락시 역방향 전압을 인가하면 합성저항은 역시 9 요이 된다.

단락 시 순방향 전압을 인가할 경우 모두 다이오드- FET를 통하는 루프가 형성되므로 합성저항이 거의  $\infty$ 가 된다.

표 1은 그림 3과 같이 한 개 다이오드가 단락고장일 경우 순방향 및 역방향 전압인가 시 합성저항을 보인 것이다.

#### 표 1 한 개 다이오드 단락고장 시 합성저항

Table 1 Total resistance under one diode short fault

| 단락 다이오드 | 합성저항     |          |  |  |  |

|---------|----------|----------|--|--|--|

| 한탁 다이오드 | 순방향 전압 시 | 역방향 전압 시 |  |  |  |

| D1      | ∞        | 9 Ω      |  |  |  |

| D2      | 9 Ω      | ∞        |  |  |  |

| D3      | 9 Ω      | ∞        |  |  |  |

| D4      | ∞        | 9 Ω      |  |  |  |

#### 3.2 브릿지 정류기의 2개 이상 다이오드 단락 시 합성저항

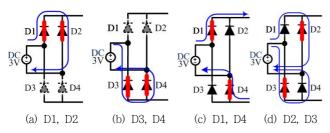

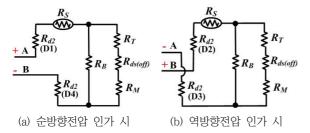

그림 4와 5는 브릿지 정류기 두 개 다이오드가 동시에 단락된 경우에 순방향 전압인가 시와 역방향 전압인가 시 각각 브릿지 정류기내에서 전류가 흐르는 경로를 보인다.

그림 4 두 개 다이오드 단락 시 순방향 전압인가 등가회로

Fig. 4 Equivalent circuits under two diodes short condition when positive voltage is applied

그림 5 두 개 다이오드 단락 시 역방향 전압인가 등가회로

Fig. 5 Equivalent circuits under two diodes short condition when negative voltage is applied

그림 4(a)와 5(a)는 상단측 두 개 다이오드 D1과 D2가 단락고장 시 테스터로 순방향 및 역방향전압을 각각 인가할 경우 브릿지 정류기내에 흐르는 전류경로를 보인 것이다. 인가전압 방향에 관계없이 다이오드 D1과 D2로 전류가 흐르는데 두 다이오드모두 단락상태이므로 등가저항이 거의 0 요로 합성저항 역시 거의 0 요이 된다. 그림 4(b)와 5(b)는 하단측 두 개 다이오드 D3과 D4가 단락고장 시 테스터로 순방향 및 역방향전압을 각각

인가할 경우 브릿지 정류기내에 흐르는 전류경로를 보인 것이다. 인가전압 방향에 관계없이 단락된 다이오드 D3과 D4로 전류가 흐르므로 합성저항 역시 거의  $0\Omega$ 이 된다.

그림 4(c)와 5(c)는 D1과 D4가 단락 고장 시 순방향 및 역방 향 전압을 각각 인가할 경우 브릿지 정류기내에 흐르는 전류경로 를 보인 것이다. 그림 4(c)와 같이 순방향 전압을 인가 시는 D1-FET-D4 경로상에서 FET가 오프상태이므로 합성저항은 거의 ∞가 된다. 그림 5(c)와 같이 역방향인가 시는 D2-D1 경로와 D4-D3 경로 등 2개의 경로로 전류가 흐르지만 두 경로 모두 정 상 다이오드와 단락상태 다이오드를 통하여 전류가 흐르므로 측 정 저항은 1개 정상 다이오드의 등가저항 값인 9 요이 된다. 그 림 4(d)과 5(d)는 D2과 D3가 단락 고장 시 순방향 및 역방향전 압을 각각 인가할 경우 브릿지 정류기내에 흐르는 전류경로를 보 인 것이다. 그림 4(d)와 같이 순방향 전압을 인가 시는 FET가 오프상태로 합성저항은 거의 ∞가 된다. 그림 4(d)와 같이 역방 향인가 시는 D2-D1 경로와 D3-D4 경로 등 2개의 경로로 전류 가 흐르지만 두 경로 모두 정상 다이오드와 단락상태 다이오드를 통하여 전류가 흐르므로 측정 저항은 1개 정상 다이오드의 등가 저항 값인 9 Ω이 된다. 그림 5(d)와 같이 역방향 전압을 인가할 경우에는 FET가 오프상태이므로 합성저항은 거의 ∞가 된다.

마지막으로 브릿지 정류기 4개 다이오드 모두 단락고장일 경우 테스터 순방향 전압 인가 시와 역방향 전압 인가 시 모두 합성저항이 0  $\Omega$ 이 된다. 표 2는 그림 4과 5를 참조하여 브릿지 정류기에서 두 개 다이오드가 동시에 단락되거나 또는 4개 다이오드 모두 단락되었을 때 테스터의 순방향과 역방향 전압 인가 시합성저항 값을 보인 것이다.

표 2 다이오드 2개 또는 4개 단락고장 시 합성저항

Table 2 Total resistance under two or four diodes short circuit

|    | 다이오드 상태 |    |    | 합성저항            |         |  |

|----|---------|----|----|-----------------|---------|--|

| D1 | D2      | D3 | D4 | 순방향 전압시         | 역방향 전압시 |  |

| 단락 | 단락      | -  | -  | 0 Ω             | 0 Ω     |  |

| -  | -       | 단락 | 단락 | 0 Ω             | 0 Ω     |  |

| 단락 | -       | -  | 단락 | $\infty \Omega$ | 9 Ω     |  |

| -  | 단락      | 단락 | -  | 9 Ω             | ∞Ω      |  |

| 단락 | 단락      | 단락 | 단락 | 0 Ω             | 0 Ω     |  |

### 4. FET 단락고장 진단 방법

FET가 정상상태에서 게이트-소스 전압  $V_{CS}$ 를 0으로 하여 FET를 턴오프 시 드레인-소스(D-S) 사이에  $1\,\mu\text{A}\sim50\,\mu\text{A}$ 의 매우 작은 전류가 흐르지만, FET소자가 단락이 되면 D-S 사이에 큰 전류로 흐르게 된다. 산업현장에서 FET 단락고장로 인한 과전류에 의해 전원이 차단된 상태에서 FET 단락고장여부를 판별할 수 있는 기법이 많이 요구되므로, 본 논문에서는 FET의 정상상태와 단락상태에서 입력단에 합성저항을 유도하여 이 합성저항 값을 이용하여 FET 단락고장 여부를 판별하는 방법을 제시한다.

#### 4.1 FET 단락 고장 시 합성저항

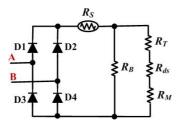

합성저항 값으로 FET의 단락고장 검출을 위하기 먼저 그림 1의 전원장치회로에서 FET를 포함한 서미스터, 변압기, 전류측정용 저항 및 FET제어회로 등 주요 소자들을 그림 6과 같이 저항으로 등가시킬 수 있다.

그림 6 전원장치의 등가회로

Fig. 6 Equivalent circuit of power supply

각 소자별 등가저항의 값과 정의는 다음과 같다.

•  $R_S$  = 10  $\Omega$  : 온도 25 $^{\circ}$ 일 경우 서미스터 저항

•  $R_T = 0.5 \Omega$  : 스위칭변압기 1차 측 등가저항

• R<sub>ds(off)</sub> ≅ 3 MΩ : FET 턴-오프 시 D-S 저항

• R<sub>ds(on)</sub> = 0.55 Ω 이하 : FET 턴-온 시 D-S 저항

•  $R_M = 0.5 \Omega$  : 전류측정용 저항

•  $R_B$  = 수십  $k\Omega$  : FET 제어회로 등가 저항

# 4.2 전원장치가 정상일 경우 합성저항

그림 7은 다이오드 정류기내 다이오드와 FET가 정상이면서, FET가 오프상태에서 A와 B점 사이 테스터로 순방향 전압과 역 방향 전압을 각각 인가 시 전원장치의 등가회로를 그린 것이다. 여기서 정상 동작하는 다이오드 정류기에 테스터로 +3 V 또는 -3 V가 인가하며, 테스터 출력전압 극성에 따라 다이오드 D1과 D4 또는 D2와 D3등 2개 다이오드가 동시에 도통된다. 따라서각 다이오드에 순방향으로 1.5 V씩 낮은 전압이 인가되므로 다이오드 특성곡선 상에서 문턱부분에서 동작되어 다이오드 등가 저항이 3장에서의 다이오드 등가저항  $R_d = 9$   $\Omega$  보다 증가된다. 이렇게 다이오드가 2개 동시에 도통 시 각 다이오드가 5자항을  $R_d$ 라고 정의하고, 다이오드 등가저항 값은  $\Omega$  1개 다이오드가 도통하였을 경우에 비하여 2배로 큰 약  $\Omega$  18  $\Omega$ 이 됨을 실험적으로 검증하였다.

그림 7 전원장치 정상상태일 경우 등가회로

Fig. 7 Equivalent circuit of power supply under normal operation

순방향 전압 인가할 경우와 역방향 전압 인가할 경우 도통되는 다이오드가 다르지만 A-B 단자에서의 통합저항은 동일하며다음 식과 같이 표현된다.

$$R_{eg} = 2R_{d2} + R_s + R_B / / (R_T + R_{ds(off)} + R_M)$$

(1)

여기서  $R_{ds(off)}\gg(R_T+R_M)$ ,  $R_{ds(off)}\gg R_B$ 이므로 다음과 같이 간략화 시킬 수 있다.

$$R_{eg} \simeq 2R_{d2} + R_s + R_B / / R_{ds(off)} \simeq 2R_{d2} + R_s + R_B$$

(2)

식 (2)에서  $R_P$ 가 수십  $k\Omega$  정도이므로 전원장치가 정상일 경우에는 테스터의 전압방향에 관계없이 합성저항이 수십  $k\Omega$ 으로 상당히 큰 값을 가진다.

#### 4.3 FET 단락 시 합성저항

FET가 단락고장 시에는 FET의 D-S사이 저항은 거의  $0\ \Omega$  ( $R_{ds}=0\ \Omega$ )이 되고 그림 7와 같이 테스터의 전압방향에 관계없이 합성저항이 동일하다. 따라서 FET 단락고장 시 순방향전압을 인가할 경우 또는 역방향전압을 인가할 경우 모두 그림 7에서 FET의 등가저항  $r_{Colority}$ 를  $0\ \Omega$  즉 단락상태로 한다.

따라서 FET의 D-S사이 단락 시 A-B 단자에서의 통합저항은 식(1)에서  $r_{ds(aff)}=0$   $\Omega$ 으로 대입하면 식 (3)과 같이 표현된다. 여기서  $R_B\gg(R_T+R_M)$ 이므로  $R_E$ 를 무시하고, 변압기 및 전류 검출센서의 저항까지 무시하면 통합저항 값이 약 46  $\Omega$ 이 된다.

$$R_{eg} = 2R_{d2} + R_s + R_B / / (R_T + R_M) \approx 2R_{d2} + R_s = 46 \Omega$$

(3)

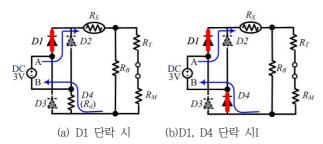

#### 4.4 FET와 다이오드 동시 단락 시 합성저항

FET와 다이오드정류기내에서 다이오드 1개가 동시에 단락고장 시 합성저항을 유도한다. 그런데 그림 3에서 보는 바와 같이다이오드 D1 또는 D4가 단락 시 역방향 전압 인가할 경우 모두 2개 다이오드 사이로 전류가 흐르므로 합성저항 값이 FET 단락고장과 상관없다. 그리고 다이오드 D2 또는 D3가 단락 시 순방향 전압 인가할 경우 모두 2개 다이오드 사이로 전류가 흐르므로 역시 합성저항 값이 FET 단락고장과 상관없다.

따라서 다이오드 D1 또는 D4가 단락 시 순방향 전압 인가할 경우와 다이오드 D2 또는 D3가 단락 시 역방향 전압 인가할 경우에는 합성저항 값이 FET 단락고장여부에 따라 많이 달라진다. 그림 8(a)는 위의 4가지 경우 모두 통합저항 값이 동일하므로 4가지 경우 중에 대표적으로 FET와 다이오드 D1이 단락 시 순방향 전압 인가할 경우에만 등가회로를 보인다. 전류는 단락된 다이오드 D1과 FET회로를 거쳐 D4를 통하여 흐르므로 통합저항식은 식 (4)와 같다. 식 (3)과 같이 R를 무시하여 근사화시키면통합저항 값은 약 20 Ω이 되며, 다른 3가지 경우에도 통합저항은 동일하다.

$$R_{eg} = R_d + R_s + R_B / / (R_T + R_M) \cong R_d + R_s + R_T + R_M = 20 \Omega$$

(4)

FET와 다이오드정류기내 다이오드 2개가 동시 단락고장 시

합성저항을 유도한다. 다이오드 2개가 동시 단락고장 시 그림 4(a), 4(b), 4(d)와 그림 5(a), 5(b), 5(c)의 경우 다이오드정류기내다이오드를 통하여 전류가 흐르므로 합성저항 값은 FET 단락고장과 상관없이 표 3과 같다. 그런데 그림 4(c)와 같이 다이오드 D1과 D2가 단락 시 순방향 전압을 인가하였을 경우 단락 다이오드 D1-단락 FET-단락 다이오드 D4를 통하여 전류가 흐르며, 그림 5(d)와 같이 다이오드 D2와 D3가 단락 시 역방향 전압을 인가하였을 시 단락된 두 다이오드 D2, D3와 FET를 통하여 전류가 흐른다.

그림 8(b)는 FET와 다이오드 D1과 D2이 단락고장 시 순방향전압을 인가하였을 경우 등가회로를 그린 것이다. 두 다이오드와 FET가 단락상태이므로 등가저항을 0 요으로 하면 합성저항 값은 다음 식 (5)와 같다. 한편 FET와 다이오드 D2과 D3이 단락고장시 역방향 전압을 인가하였을 경우에도 합성저항 값은 동일하다.

$$R_{eq} = R_s + R_B / / (R_T + R_M) \cong R_s + R_T + R_M = 11 \Omega$$

(5)

그림 8 FET와 다이오드 동시 단락 상태에서 등가회로

Fig. 8 Equivalent circuit under both FET and diode short conditions

#### 표 3 FET와 다이오드 동시에 단락고장 시 합성저항

Table 3 Total resistance under both FET and diodes short circuits

| 다이오드 상태 |    |    | H  | FET상태 | 합성      | 저항      |

|---------|----|----|----|-------|---------|---------|

| D1      | D2 | D3 | D4 | FET   | 순방향 전압시 | 역방향 전압시 |

| -       | -  | -  | -  | 단락    | 46 Ω    | 46 Ω    |

| 단락      | -  | -  | -  | 단락    | 20 Ω    | 9 Ω     |

| -       | 단락 | -  | -  | 단락    | 9 Ω     | 20 Ω    |

| -       | -  | 단락 | -  | 단락    | 9 Ω     | 20 Ω    |

| -       | -  | -  | 단락 | 단락    | 20 Ω    | 9 Ω     |

| 단락      | 단락 | -  | -  | 단락    | 0 Ω     | 0 Ω     |

| -       | -  | 단락 | 단락 | 단락    | 0 Ω     | 0 Ω     |

| 단락      | -  | -  | 단락 | 단락    | 11 Ω    | 9 Ω     |

| -       | 단락 | 단락 | -  | 단락    | 9 Ω     | 11 Ω    |

| 단락      | 단락 | 단락 | 단락 | 단락    | 0 Ω     | 0 Ω     |

표 3은 그림 7과 8을 참조하여 FET가 단락고장과 함께 다이 오드정류기내 다이오드도 1개, 2개, 4개가 단락되었을 때 테스터 로 순방향 전압과 역방향 전압을 각각 인가 시 통합저항 값을 보인 것이다.

#### 4.5 다이오드와 FET가 모델 변경 시 합성저항 영향 분석

다이오드와 전력용 FET 모델이 변경 시 두 소자의 등가저항 값이 바뀌므로 다이오드 및 FET 단락상태에서의 합성저항 값도 바뀌게 된다. 따라서 다이오드와 전력용 FET 모델이 변경 시 전원회로 단락상태에 따라 앞에서 유도한 합성저항 값의 변화를 분석한다. 먼저 본 논문에서 사용한 다이오드 (모델명 1N5404)를 포함하여 정격전류와 정격전압이 다른 3개 종류 실리콘 다이오드모델에 대하여 아날로그 테스터기로 측정한 등가저항 값은 표 4와 같다.

#### 표 4 실리콘 다이오드의 등가저항

Table 4 Equivalent resistance in silicon diodes

| 모델명    | 정격전류 | 정격전압  | 등가저항  |

|--------|------|-------|-------|

| 1N4001 | 1A   | 50V   | 9.4 Ω |

| 1N5404 | 3A   | 400V  | 9Ω    |

| 6A100  | 6A   | 1000V | 8.7Ω  |

| 10A10  | 10A  | 1000V | 8.5 Ω |

다이오드의 정격전류가 증가함에 따라 등가저항이 증가되며 다이오드 모델에 따라 다이오드 등가저항의 변화범위가  $9.4~\Omega$ 에서  $8.5~\Omega$ 이므로, 앞에서 유도한 다이오드 및 FET의 정상 또는 단락상태에서의 합성저항 값의 변화를 정리하면 표 5와 같다. 이 표 5에서 다이오드 모델 변경 시에도 합성저항이 최대 5.5~% 정도만변화되므로 다이오드 단락고장 진단에 큰 영향을 주지 않는다.

다음은 전력용 FET 모델 변경 시 합성저항의 영향을 분석한다. 전력용 FET모델에 따라 도통상태에서 FET D-S사이의 도통저항 즉  $r_{ds(on)}$ 값이 많이 차이가 나는데, 식(3)에서 식(5)까지와같이 FET가 오프상태 또는 단락상태에서만 합성저항 값을 계산하므로  $r_{ds(on)}$ 값의 차이는 합성저항에 영향을 주지 않는다.

# 표 5 다이오드 모델 변경 시 합성저항 영향

Table 5 Equivalent resistance effects when the different diode model is used

| 동작상태               | 1N5404<br>사용 시 | 모델<br>변경 시                   |

|--------------------|----------------|------------------------------|

| 전원장치 정상 시          | 수 kΩ           | 수 kΩ                         |

| 다이오드 1, 2, 4개 단락 시 | 9Ω             | 8.5Ω∼9.4Ω                    |

| FET 단락 시           | 46Ω            | $44\Omega \sim 47.6\Omega$   |

| FET와 다이오드 1개 단락 시  | 20Ω            | $19.5\Omega \sim 20.4\Omega$ |

| FET와 다이오드 2개 단락 시  | 11 Ω           | 11 Ω                         |

#### 5. 실험 결과

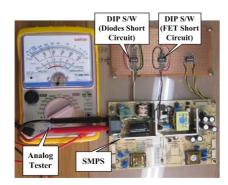

아날로그 테스터기를 사용하여 측정한 합성 저항값으로 스윗 칭모드 전원장치의 다이오드 정류기, FET단락 고장을 감지하는 기법의 타당성을 확인하기 위하여 실험을 실시하였다. 그림 9는 실험장치 사진을 보인 것으로, 하단보드는 시판되는 디스플레이용 전원장치이고 상단보드는 브릿지 정류기의 4개 다이오드와 FET별로 병렬로 DIP스위치를 연결한 것이다. DIP스위치를 이용하여 다이오드 및 FET 각 소자별 정상상태 또는 단락상태를 구현하여 실제상황에 맞게 실험을 수행하였다.

그림 9 실험장치 사진

Fig. 9 Photograph of experimental setup

#### 표 6 다이오드 1개 단락 시 합성저항 실험결과

Table 6 Experimental results of total resistance under one diode short circuit

| 다이오드 상태 |    |    |    | 합성저항 실험결과 |                  |  |

|---------|----|----|----|-----------|------------------|--|

| D1      | D2 | D3 | D4 | 순방향전압 시   | 역방향전압 시          |  |

| 단락      | -  | -  | -  | ∞ Ω       | 9 Ω              |  |

| -       | 단락 | -  | -  | 9 Ω       | ∞ Ω              |  |

| -       | -  | 단락 | -  | 9 Ω       | ∞ Ω              |  |

| -       | -  | -  | 단락 | ∞ Ω       | 9 Ω              |  |

| -       | -  | -  | -  | ∞ Ω       | $\otimes \Omega$ |  |

표 6은 브릿지 정류기내 다이오드 1개만 단락고장 시, 그림 1에서 입력단 (A, B점)에서 순방향과 역방향 전압인가 시 측정한 저항 값이다. 표 1에서 다이오드 1개만 단락고장 시 해석한 합성 저항 값과 거의 유사함을 알 수 있다.

표 7은 브리지회로 다이오드 2개가 동시단락 고장일 경우와 4개 다이오드 모두 단락 고장일 때, 그림 1의 입력단 에서 순방향과 역방향 전압을 각각 인가 시 측정한 저항값을 보인 것이다. 표 2와 비교하면 2개 다이오드 D1과 D2 및 D3와 D4가 동시에단락 시와 4개 다이오드 모두 단락 시 이론적으로는 합성저항이 0 요이지만 전선 저항 등이 있으므로 1.2 요인 비교적 낮은 저항값으로 측정되었다. 또한 다이오드 D1과 D4이 단락 시 순방향전압을 인가할 경우와 다이오드 D2과 D3이 단락 시 역방향전압을 인가할 경우에는 1개 다이오드의 등가전항 값인 9 요보다낮은 8.5 요이 측정되었는데 병렬형태의 두 경로 때문인 것으로추측된다.

표 8은 FET를 포함하여 모든 부품이 정상 동작 시와 FET의 드레인-소스 사이에 단락되고 그 외 부품은 정상인 경우에, 입력 단에서 정방향 및 역방향 전압을 각각 인가 시 측정된 저항 값이다. 전원 장치 모든 부품이 정상일 경우 식 (2)와 같이 수십 k

#### 표 7 다이오드 2개 단락 시 합성저항 실험결과

Table 7 Experimental results of total resistance under two diodes short circuit

|    | 다이오드 상태 |    |    |    | 합성저항 실험결과 |         |  |

|----|---------|----|----|----|-----------|---------|--|

| D: | 1       | D2 | D3 | D4 | 순방향전압 시   | 역방향전압 시 |  |

| 단  | 락       | 단락 | -  | -  | 1.2 Ω     | 1.2 Ω   |  |

| -  |         | -  | 단락 | 단락 | 1.2 Ω     | 1.2 Ω   |  |

| 단  | 락       | -  | -  | 단락 | 8.5 Ω     | ∞ Ω     |  |

| -  |         | 단락 | 단락 | -  | ∞ Ω       | 8.5 Ω   |  |

| 단  | 락       | 단락 | 단락 | 단락 | 1.2 Ω     | 1.2 Ω   |  |

| _  |         | -  |    | -  | Ω ∞       | ∞ Ω     |  |

#### 표 8 FET 단락상태에서 합성저항 실험결과

**Table 8** Experimental results of total resistance under FET short condition

| FET 상태 |     |     | 합성저항 실험결과       |         |  |

|--------|-----|-----|-----------------|---------|--|

| D-S    | G-D | G-S | 순방향전압 시         | 역방향전압 시 |  |

| 단락     | -   | -   | 48 Ω            | 48 Ω    |  |

| -      | -   | -   | $\infty \Omega$ | ∞ Ω     |  |

#### 표 9 FET와 다이오드 동시 단락 시 합성저항 실험결과

**Table 9** Experimental results of total resistance under both FET and diodes short circuits

| 다이오드 상태 |    |    |    | FET상태 | 합성저항 실험결과  |            |  |  |

|---------|----|----|----|-------|------------|------------|--|--|

| D1      | D2 | D3 | D4 | FET   | 순방향<br>전압시 | 역방향<br>전압시 |  |  |

| 단락      | -  | -  | -  | 단락    | 26 Ω       | 9 Ω        |  |  |

| -       | 단락 | -  | -  | 단락    | 9 Ω        | 26 Ω       |  |  |

| -       | -  | 단락 | -  | 단락    | 9 Ω        | 26 Ω       |  |  |

| -       | -  | -  | 단락 | 단락    | 26 Ω       | 9 Ω        |  |  |

| 단락      | 단락 | -  | -  | 단락    | 1.2 Ω      | 1.2 Ω      |  |  |

| _       | -  | 단락 | 단락 | 단락    | 1.2 Ω      | 1.2 Ω      |  |  |

| 단락      | -  | -  | 단락 | 단락    | 13 Ω       | 8.5 Ω      |  |  |

| -       | 단락 | 단락 | -  | 단락    | 8.5 Ω      | 13 Ω       |  |  |

| 단락      | 단락 | 단락 | 단락 | 단락    | 1.2 Ω      | 1.2 Ω      |  |  |

$\Omega$ 임으로 테스터 측정 시 거의  $\infty$ 로 표시되었으며, FET의 드레 인-소스 사이에 단락고장이 발생 시 측정한 저항 값은  $48~\Omega$ 으로 식 (3)의 이론적 합성저항인  $46~\Omega$ 과 비슷한 저항 값이 측정됨을 알 수 있다.

표 9는 FET의 드레인-소스 사이에 단락고장이 발생되면서 브 릿지 정류기내 다이오드도 1개 또는 2개가 단락되었을 때 테스 터로 순방향 전압과 역방향 전압을 각각 인가 시 실험으로 측정 한 저항 값을 보인 것이다. 표 3에서 같은 단락고장 시의 저항값과 비교하면, FET가 단락상태에서 다이오드 D1 또는 D4 단락시역방향 전압 인가할 경우와 다이오드 D2 또는 D3가 단락시순방향 전압 인가할 경우 모두 표 2의 합성저항 값과 동일한 다이오드 등가저항 값으로 된다. 그리고 다이오드 D1 또는 D4 단락시순방향 전압 인가할 경우와 다이오드 D2 또는 D3가 단락시역방향 전압 인가할 경우에는 합성저항 값이  $26\ \Omega$ 으로 표 3의 저항 값 보다 약간 큼을 알 수 있다. 그리고 FET가 단락상태에서 2개 다이오드가 동시에 단락고장 발생 시 실험결과와 이론치의 저항 값을 비교하면  $1\Omega\sim2\Omega$  정도의 오차가 있다.

#### 6. 결 론

본 논문에서는 스위칭모드 전원장치의 입력 필터 단에 간단한 아날로그 테스터기로 순방향으로 +3V를 역방향으로 같은 전압을 인가하면서 합성저항을 측정하여 전원장치회로의 브릿지 정류기내 다이오드와 전력용 FET의 단락고장을 진단하는 기법을 제시하였다. 여기서 전원장치 내의 부품에서 단락고장 시 다양한 합성저항이 나타나며 이 합성저항 값을 이용하여 단락된 소자를 판별한다. 이론 적으로 해석한 합성저항 값과 실제 실험하여 측정한 저항값을 비교한 결과  $1\Omega \sim 2\Omega$  정도의 오차만 발생되므로 전원장치의 각 부분 단락고장 판단에 큰 영향을 주지 않을 것이다. 한편 다이오드 모델 변경 시에도 합성저항이 최대 5.5% 정도만 변동되어 다이오드 단락고장 진단에 거의 영향이 없으며, FET가 오프상태 또는 단락상태 합성저항 값만을 계산하므로 전력용 FET모델에 따라 많이 차이 나는 도통저항  $r_{cls(cm)}$ 값의 변화는 합성저항에 영향을 주지 않는다.

결론적으로 단자에서 순방향전압과 역방향전압을 각각 인가하면서 측정한 저항 범위가  $0 \Omega \sim 1.2 \Omega$ ,  $8.5 \Omega \sim 9.5 \Omega$ ,  $11 \Omega \sim 13 \Omega$ ,  $19 \Omega \sim 28 \Omega$ ,  $44 \Omega \sim 48 \Omega$ , 무한대 저항 인지를 체크한 후, 표 1에서 표 9까지를 참조하여 전원장치의 모든 소자가 정상인지 어떤 다이오드 또는 FET가 단락 고장인지를 쉽게 진단할 수있다. 본 논문에서 제시한 간단한 아날로그 테스터 장비로 쉽게 불량품을 찾는 방법은 산업용 또는 생활가전제품의 PCB 회로고장 검출에도 적용할 수 있을 것이다.

### References

- [1] S. Yang, A. Bryant, P. Mawby, D. Xiang, R. Li, and P. Tavner, "An industry-based survey of reliability in power electronic converter", IEEE Trans. Ind. Appl., vol. 47, no. 3, pp.1441-1451, May, 2011.

- [2] N.E.A.M. Hassanain and J.E. Fletcher, "Steady- state performance assessment of three- and five-phase permanent magnet generators connected to a diode bridge rectifier under open-circuit faults," IET Renewable Power Generation, vol. 4, no. 5, pp. 420-427, 2010.

- [3] M.A. Masrur, Z. Chen, and Y. Murphey, "Intelligent diagnosis of open and short circuit faults in electric drive inverters for real-time applications," IET Power Electron., vol. 3, no. 2, pp. 279-291, Apr. 2008.

- [4] T. Kamel, Y. Biletskiy, and L. Chang, "Open circuit fault diagnosis for the power electronic converter stage using ANFIS algorithm," in Conf. Rec. IEEE-CCECE, May, 2015, pp. 656-662.

- [5] M.G. McArdle and D.J. Morrow, "Noninvasive detection of brushless exciter rotating diode failure," IEEE Trans. Energy Conversion, vol. 19, no. 2, pp. 378-383, June, 2004.

- [6] Z. Huang, Y. Sun, and S. Wang, "Analysis and diagnosis on open-circuit fault of diode rectifier in 12-phase synchronous generator system," in Conf. Rec. EPE-ECCE, 2014, pp. 1-8.

- [7] W. Na, "A feedforward controller for a brushless excitation system during the diode open circuit fault operation," in Conf. Rec. IEEE-PES, 2011, pp. 1-4.

- [8] T. Kamel, Y. Biletskiy, and L. Chang, "On-line diagnosis for rectifier open circuit faults and input voltage unbalance based on the output DC voltage," in Conf. Rec. IEEE-ECCE, 2015, pp.4753-4758.

- [9] M. Rahiminejad, C. Didush, M. Stevenson, and L. Chang, "Open-circuit fault diagnosis in 3-phase uncontrolled rectifier," in Conf. Rec. IEEE-PEDG, 2012, pp. 254-259.

# 저 자 소 개

# 이 재 원 (Jae-Won Lee)

1956년 6월 6일생. 2013년~현재 울산대학교 대학원 전기전자컴퓨터공학과 석사과정. 1980~1981년, 삼성 석유화학 울산공장계전과 강사, 1982~1983년, 동양나이론, 폴리에스터 울산공장계전과 강사, 1984년~현재 울산전자 직업전문학교장, 2015년~현재 노동부 대한민 국산업현장교수단 전자과교수, 전자기능장

## 전 태 원 (Tae-Won Chun)

1959년 1월 30일생. 1981년 부산대 전기공학과 졸업(학사). 1983년 서울대학교 대학원전기공학과 졸업(석사). 1987년 동 대학원전기공학과 졸업(박사), 2005년 버지니아공대 방문교수, 현재 울산대 전기공학부 교수