**JPE 16-3-6**

http://dx.doi.org/10.6113/JPE.2016.16.3.872 ISSN(Print): 1598-2092 / ISSN(Online): 2093-4718

# A Novel PCCM Voltage-Fed Single-Stage Power Factor Correction Full-Bridge Battery Charger

Taizhi Zhang\*, Zhipeng Lu\*, Qinsong Qian\*, Weifeng Sun†, and Shengli Lu\*

\*, †National ASIC System Engineering Research Center, Southeast University, Nanjing, China

#### **Abstract**

A novel pseudo-continuous conduction mode (PCCM) voltage-fed single-stage power factor correction (PFC) full-bridge battery charger is proposed in this paper. By connecting a freewheeling transistor in parallel with an input inductor, the PFC cell can operate in the PCCM with a constant duty ratio. Thus, the dc/dc stage can be designed using this constant duty ratio and the restriction on the duty ratio of the PFC cell is eliminated. As a result, the input current distortion is less and the dc bus voltage becomes controllable over the wide output power range of the battery charger. Moreover, the operation principle of the dc/dc stage is designed to be similar to that of a conventional phase-shifted full-bridge converter. Therefore, it is easy to implement. In this paper, the operation of the new converter is explained, and the design considerations of the controller and key parameters are presented. Simulation and experimental results obtained from a 1 kW prototype are given to confirm the operation of the proposed converter.

Key words: Battery charger, Full-bridge, Power factor correction, Single-stage

# I. INTRODUCTION

In recent years, battery chargers have become a key component for the emergence and acceptance of electrical vehicles. A well-known topology for battery chargers is the two-stage structure. A front stage, which is usually a boost converter, is adopted to perform power factor correction (PFC). A second stage, which is usually a high-efficiency isolated dc/dc converter, is adopted to realize isolation and to control the charging current. Normally, a full-bridge (FB) converter is the most popular topology for the dc/dc converter in battery charger applications (1-5 kW) [1]-[5].

However, the cost and complexity of the overall two-stage converter are increased because an additional converter must be implemented. Therefore, using a single-stage topology to realize the PFC, isolation and dc/dc conversion sounds more attractive. Several single-stage full-bridge topologies can be found in the literature [6]-[21]. Among them, voltage-fed full-bridge converters [13]-[21], which can operate with a

Manuscript received Aug. 8, 2015; accepted Dec. 14, 2015 Recommended for publication by Associate Editor Honnyong Cha. <sup>†</sup>Corresponding Author: swffrog@seu.edu.cn Tel: +86-25-83795811, Fax: +86-25-83795077, Southeast University

Tel: +86-25-83795811, Fax: +86-25-83795077, Southeast University National ASIC System Engineering Research Center, Southeast University, China

constant frequency and do not have a voltage overshoot problem across the dc bus, have been widely studied. In [13]-[20], two inherent duty ratios, the dc/dc stage duty ratio  $D_o$  and the PFC cell duty ratio  $D_i$ , are defined. However,  $D_i$  is restricted by  $D_o$ , and there are only three discontinuous values of  $D_i$  when  $D_o$  is settled. Therefore, distortions of input current are high and the dc bus voltage may become uncontrollable, especially in battery charger applications where the output power varies a lot. In [21], the restriction of the PFC cell duty ratio is weakened by using two controllers, and the PFC cell duty ratio can vary continuously. Nevertheless, the range of  $D_i$  should still be limited to implement the control of the output voltage. Thus, input current distortions inevitably appear due to the limited duty ratio band. In addition, two controllers increase the system complexity.

In this paper, a novel pseudo-continuous conduction mode (PCCM) voltage-fed single-stage full-bridge battery charger topology is proposed. The proposed converter can operate with a constant frequency, less input current distortion and a controllable dc bus voltage. These features are realized by using PCCM control in the PFC cell. It is well known that discontinuous conduction mode (DCM) PFC converters suffer from heavy current stresses, which restrict the power range of DCM PFC converters to the low power range (<250W) [22]. Therefore, the continuous conduction mode (CCM) is the most

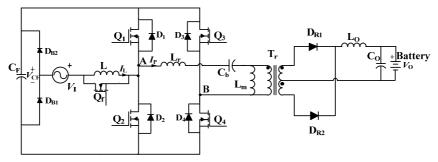

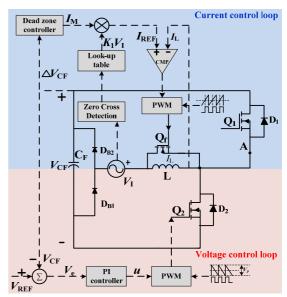

Fig. 1. Proposed PCCM single-stage PFC full-bridge converter for battery charger.

popular modulation method in large power applications such as battery chargers. However, the duty ratio of CCM PFC varies a lot over one ac line cycle which limits the regulation range of the output voltage, as is shown in [21]. In this paper, PCCM control, which can be used to achieve a large output power while having a constant on-time, is adopted here. With a constant on-time, the restriction of the input duty ratio can be eliminated. In addition, the operation of the dc/dc stage is designed to be similar to that of the conventional phase-shifted full-bridge (PSFB) converter which makes it easy to implement.

This paper is organized as follows. The operation of the proposed converter is explained in Section II. The converter characteristics are presented in Section III. Then the design procedure of the proposed battery charger is proposed in Section IV. In Section V, simulation and experimental results obtained from a 1kW single-stage battery charger prototype are given to confirm the operation of the proposed converter. Finally, some conclusions are given in section VI.

# II. CONVERTER DESCRIPTION AND OPERATION PRINCIPLE

A circuit diagram of the proposed single-stage full-bridge converter is shown in Fig. 1. The two bridge legs of the full-bridge converter are composed of four transistors,  $Q_1$ ,  $Q_2$ ,  $Q_3$  and  $Q_4$ .  $Q_1$  and  $Q_2$  are used to perform the same current-shaping function as the switch in a boost converter. The input inductor L is connected to the  $Q_1$ – $Q_2$  leg. The power transformer  $T_r$ , the resonant inductor  $L_r$  (including the leakage inductor), the output diodes  $D_{R1}$  and  $D_{R2}$ , the output filter inductor  $L_O$  and the capacitor  $C_O$  make up a standard full-bridge converter. An energy storage capacitor  $C_F$  is placed across the primary-side dc bus. The freewheeling power switch  $Q_f$  is placed in parallel with the input inductor L.

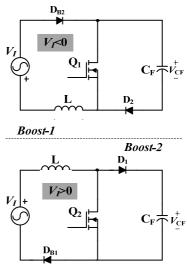

The PFC function can be accomplished by two input boost converters (*Boost-1*, when  $V_I < 0$ ; and *Boost-2*, when  $V_I > 0$ ), as shown in Fig. 2. The operations of the two boost converters *Boost-2* ( $V_I > 0$ ) as an example.

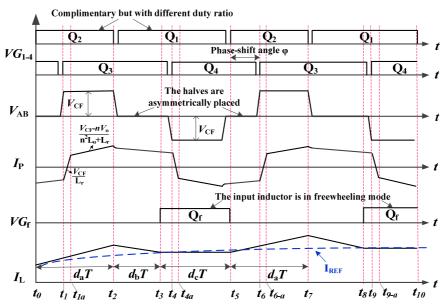

Key waveforms of the proposed converter are shown in Fig. 3.  $d_a$  is the duty ratio of  $Q_2$ , which is the PFC cell duty ratio, and the inductor current  $I_L$  ramps up in the time interval  $d_a$ T. With the PCCM control,  $d_a$  is nearly constant over half a line

Fig. 2. Two input boost converters provided by the proposed topology.

are symmetric. Thus, the operation explanation below takes cycle (typical 100 Hz), and  $V_{CF}$  is regulated to be constant. Obviously,  $V_{CF}$  is larger than  $V_{I}$ . Meanwhile, the operation principle of the dc/dc stage (charging current control stage) is similar to that of the PSFB converter. The duty ratio of Q<sub>4</sub> is equal to that of Q2, which is nearly constant. Meanwhile, the gating signals for Q1 and Q3 are complimentary to those for Q2 and Q<sub>4</sub>, respectively. Whenever the top switch of a converter leg is on, the bottom switch in the same leg is off and vice versa. The charge current is controlled by phase-shifting the gating signals of the switches in the Q<sub>1</sub>-Q<sub>2</sub> leg with respect to those of the  $Q_3$ – $Q_4$  leg.  $\varphi$  is the phase difference between the two legs. Although the transformer primary voltage's positive and negative halves are asymmetrically placed, the voltage-second balance can be achieved. In addition, the time interval  $d_bT$  represents the period when the input inductor current  $I_L$  ramps down and the capacitor  $C_F$  is charged. This happens when both  $Q_2$  and  $Q_f$  are off.  $d_cT$  is the time interval when the switch  $Q_2$  is off, and  $Q_f$  is on. In this interval, the input inductor current is in the freewheeling mode and is kept constant. It should be noted that:

$$d_a + d_b + d_c = 1 \tag{1}$$

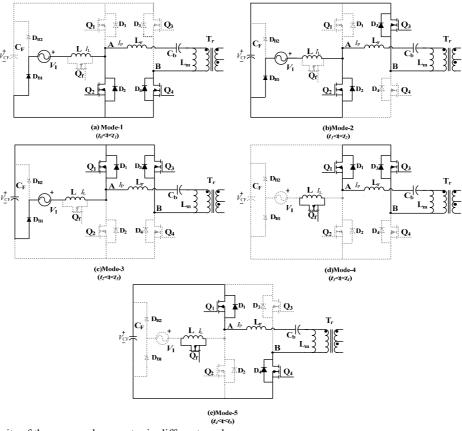

Equivalent circuit diagrams of the operation modes that the converter goes through during a switching cycle are shown in

Fig. 3. Key waveforms of the proposed converter.

Fig. 4. Equivalent circuits of the proposed converter in different modes.

Fig. 4. Since the operation principle of the dc-dc stage is similar to that of the conventional PSFB converter, the output stage, dead-time and duty cycle loss have been neglected here for the sake of simplicity.

The details of each operation mode are described as follows: *Mode 1*( $t_0 < t < t_1$ ): This mode begins when  $Q_2$  is switched on. During this mode,  $Q_2$  and  $Q_4$  are on. The primary voltage  $V_{AB}$

is equal to zero, and the current through the resonant inductor decreases. The transformer primary current during this mode is given by:

$$I_{p}(t) = I_{p}(t_{0}) - \frac{nV_{o}}{n^{2}L_{o} + L_{r}}(t - t_{0})$$

(2)

where n is the turns ratio of the transformer and  $V_o$  is the

battery voltage. No energy has been transferred to the load from  $C_F$  in this period.

Meanwhile, since  $Q_2$  and  $D_{\rm B1}$  are on, the input voltage remains impressed across the input inductor L and its current ramps up. The current through the input inductor can be expressed as:

$$I_L(t) = I_{REF}(t_p) + \frac{\left|V_m \sin \omega t\right|}{I_L}(t - t_0) \tag{3}$$

where  $V_m$  is the peak input voltage.  $I_{REF}(t_p)$  represents the reference of the input current in the previous switching cycle. This is because the inductor current  $I_L$  reaches the reference current  $I_{REF}$  when  $Q_f$  is turned on and  $I_L$  remains constant during  $d_rT$ .

This mode ends when  $Q_4$  is turned off and  $Q_3$  is turned on. It should be noted that the dead-time is neglected here and the ZVS turn-on of the transistors is achieved in the dead-time.

Mode  $2(t_1 < t < t_2)$ : This mode begins when  $Q_3$  is switched on. Actually, two modes are included during this interval. They are the commutation mode and the energy transfer mode. Since the two modes share the same equivalent circuit, as shown in Fig. 4(b), and the commutation mode is relatively short compared with the other modes, the two modes are analyzed together in this section. The commutation mode is the time interval  $[t_1 < t < t_{1a}]$ , as shown in Fig. 3. This interval is known as the duty cycle loss in the standard PSFB converters. During this interval, the dc bus voltage is completely impressed on the resonant inductor  $L_r$  and the primary current starts to commutate with a finite slope.

$$I_{p}(t) = I_{p}(t_{1}) + \frac{V_{CF}}{I}(t - t_{1})$$

(4)

At  $t_{1a}$ , the commutation of the primary current is finished, and the energy transfer mode begins. The energy is transferred from the dc bus to the output through the transformer. The positive voltage of  $V_{CF}$  is impressed across the series combination of the leakage inductor and the equivalent output inductor reflected on the primary side. It should be noted that the magnetizing inductance  $L_{\rm m}$  is much larger than the output filter inductance  $L_{\rm o}$  and is neglected here [21]. Thus, the current in the transformer primary and the output inductor  $L_{\rm o}$  rise during this mode. The transformer primary current can be given by:

$$I_{p}(t) = I_{p}(t_{1a}) + \frac{V_{CF} - nV_{o}}{n^{2}L_{o} + L_{r}}(t - t_{1a})$$

(5)

Meanwhile, a positive input voltage continues to be impressed across the input inductor L in *Mode 2*, and its current can be expressed as:

$$I_L(t) = I_L(t_1) + \frac{\left| V_m \sin \omega t \right|}{L} (t - t_1) \tag{6}$$

At the end of this mode,  $Q_2$  is turned off.

*Mode*  $3(t_2 < t < t_3)$ : This mode begins when  $Q_2$  is switched off and  $Q_1$  is switched on. When  $Q_2$  is turned off, the energy-transfer mode ends and the primary current freewheels

through  $Q_1$  and  $Q_3$ . The transformer primary current during this mode is given by:

$$I_{p}(t) = I_{p}(t_{2}) - \frac{nV_{o}}{n^{2}L_{o} + L_{o}}(t - t_{2})$$

(7)

Meanwhile, this is the capacitor-charging mode ( $d_bT$  interval).  $C_F$  is charged in this interval from the energy stored in L. The voltage across the input inductor L can be given by:

$$V_L = |V_m \sin \omega t| - V_{CF} \tag{8}$$

In addition,  $V_{CF}$  is controlled to be larger than  $V_m$ . Therefore, the input inductor current starts to ramp down and can be expressed as:

$$I_{L}(t) = I_{L}(t_{2}) - \frac{V_{CF} - |V_{m} \sin \omega t|}{I_{L}} (t - t_{2})$$

(9)

This mode ends when the input inductor current reaches the reference current, which means that:

$$I_L(t_3) = I_{REF}(t_3)$$

(10)

At  $t = t_3$ , the freewheeling power switch  $Q_f$  is turned on and the next mode begins.

Mode  $4(t_3 < t < t_4)$ : This mode begins when  $Q_f$  is switched on. The primary current freewheels through  $Q_1$  and  $Q_3$ . The transformer primary current during this mode is given by:

$$I_{p}(t) = I_{p}(t_{3}) - \frac{V_{Cb}}{L_{\nu}}(t - t_{3})$$

(11)

When  $Q_f$  is switched on, the voltage across the input inductor is approximately equal to zero. Thus,  $D_{B1}$  is reverse biased, and the voltage across  $D_{B1}$  is  $(V_{CF}-V_I)$ . Meanwhile, the current through the input inductor does not change.

$$I_I(t) = I_{RFF}(t_3) \tag{12}$$

At the end of this mode,  $Q_4$  is turned on and  $Q_3$  is turned off.

*Mode*  $5(t_4 < t < t_5)$ : This mode begins when  $Q_4$  is switched on. The commutation mode is the time interval  $[t_4 < t < t_{4a}]$  shown in Fig. 3. During this interval, the dc bus voltage is completely impressed on the resonant inductor  $L_r$  and the primary current starts to commutate with a finite slope.

$$I_{p}(t) = I_{p}(t_{4}) + \frac{V_{CF}}{L_{r}}(t - t_{4})$$

(13)

At  $t_{4a}$ , the commutation of the primary current is finished, and the energy transfer mode begins. The energy is transferred from the dc bus to the output through the transformer. The positive voltage of  $V_{CF}$  is impressed across the series combination of the leakage inductor and the equivalent output inductor reflected on the primary side. Thus, the current in the transformer primary and the output inductor  $L_0$  rises during this mode. The transformer primary current can be given by:

$$I_{p}(t) = I_{p}(t_{4a}) + \frac{V_{CF} - nV_{o}}{n^{2}L_{o} + L_{r}}(t - t_{4a})$$

(14)

Meanwhile, a positive input voltage continues to be impressed across the input inductor L in *Mode 5*, and its

current can be expressed as:

$$I_L(t) = I_L(t_4) + \frac{|V_m \sin \omega t|}{I_L}(t - t_4)$$

(15)

This mode ends when  $Q_2$  is turned on and another switching sequence begins.

#### III. FEATURES OF THE PROPOSED CONVERTER

The PCCM converter inherits some characteristics of CCM and DCM operations. They can be illustrated as follows.

Like CCM converters, the PCCM converter has a low inductor current ripple. This is because, according to the operation principle presented in Section II, the inductor current  $I_L$  is reset to  $I_{REF}$  instead of zero in every switching cycle. Meanwhile, the PCCM converter can deliver a larger power by simply boosting the current level of  $I_{REF}$ . In addition, the ratio  $d_a/d_{b_c}$  is almost constant when the output power changes. This is determined by the input and output voltage.

Like DCM converters, the on-time of power the MOSFETs in PCCM converters can be designed to be constant over half of the line cycle. This is realized by introducing a freewheeling period  $d_cT$ . The design and implementation of the dc-dc stage is very simple when the duty ratio of the PFC cell  $d_a$  is constant. In addition, the output power varies with the duty ratio  $d_a$ . Actually,  $d_a$  can be nearly constant over the entire power range with the control method proposed in Section IV. In addition, the output power is mainly regulated by modulating  $I_{REF}$ .

Since the duty ratio of the PFC cell is constant, when compared to other voltage-fed single-stage full-bridge converters, the proposed converter has the following attractive features.

- 1) There is no restriction of the PFC cell duty ratio which is used to shape the input current in the proposed converter.  $d_a$  is nearly constant in the proposed PCCM converter. Therefore, with proper design of the controller and turns ratio of the transformer, the output voltage (or charging current) can be modulated without inducing input current distortions or an uncontrollable dc bus voltage, which are common problems in previous studies.

- 2) The turns ratio of the transformer in the proposed converter can be designed so that it is larger than that of the other voltage-fed single-stage full-bridge converters. Since the duty ratio  $d_a$  in the proposed converter is nearly constant, the turns ratio can be designed to be as large as possible. Meanwhile, in other voltage-fed single-stage converters, in order to achieve a high PF, the PFC cell duty ratio band must be designed wide enough, which means the turns ratio should be designed considering the minimum duty ratio in a wide scope. Therefore, the circulating loss can be reduced in the proposed converter.

- 3) The operation principle of the dc-dc conversion stage is similar to that of a standard phase-shift full-bridge converter.

Fig. 5. PFC controller in the proposed converter.

Therefore, it is easy to implement. In addition, the output diodes can be replaced with synchronous rectifier MOSFETs for high output current applications. This is very difficult for converters that operate with non-standard control methods.

4) Single-ended transformer coupled gate driver circuits [23] can be used as the MOSFET gate driver for the proposed converter. Meanwhile, in other voltage-fed single-stage full-bridge converters, the asymmetric driver signals, which vary over every switching cycle, cause saturation of the pulse-transformer. Driver ICs had to be used in [13]-[21]. The driver ICs, especially ones that can provide isolation [24], are much more expensive than the isolated single-ended transformer-based topology.

## IV. DESIGN CONSIDERATIONS

# A. PFC Controller Design

Fig. 5 shows a schematic of the controller of a PFC cell. Irrelevant components are neglected for the sake of simplicity. A voltage control loop is used to regulate the voltage across the dc bus ( $V_{\rm CF}$ ). A current control loop is used to control the reference current to make the inductor current in the same wave shape as and in phase with the input voltage to achieve unity power factor. Also In addition, the power delivered by the converter can be regulated by the current control loop. Unlike the conventional average current controller of a CCM boost PFC converter, the output of the voltage control loop is no longer the input of the current control loop. Therefore, the voltage loop and the current loop can be designed separately.

In the voltage control loop, the voltage error  $V_e$  between the dc bus voltage  $V_{CF}$  and its reference voltage  $V_{REF}$  are fed back to generate the gating signal of  $Q_2$  or  $Q_1$ . The bandwidth of the voltage control loop is designed to be very narrow. As a result,  $d_a$  changes slowly and is thought to be constant over a half line cycle. According to (3) and (6), the peak inductor current can

be given as:

$$I_L(t) = I_{REF}(t_p) + \frac{\left|V_m \sin \omega t\right|}{L} d_a T \tag{16}$$

where the line voltage and reference current are sinusoidal, and  $d_aT$  and the input inductor L are constant. Thus, the peak inductor current  $I_L(t)$  naturally follows the sinusoidal line-voltage waveform.

A triangle-trailing-edge modulation, as seen in Fig. 5, is adopted for  $Q_2$ .

In the current control loop, a reference current  $I_{REF}$  is produced by multiplying the input voltage  $k_I V_I$  by the desired current amplitude  $I_M$ .

$$I_{REF} = k_1 I_M V_m \sin \omega t \tag{17}$$

where  $k_I$  is a coefficient produced by the controller, and  $k_I V_m \approx 1$ . Thus:

$$I_{REF} \approx I_M \sin \omega t$$

(18)

The input voltage  $V_I$  is implemented by a look-up table with the sensing of the zero cross signal.

The key issue of the current control loop is to obtain  $I_M$ . As mentioned in Section III, the output power is mainly regulated by modulating  $I_{REF}$ . Thus,  $I_M$  should be proportional to the load current of the PFC section  $I_{bus}$  (which is proportional to the load power since the dc bus voltage is constant). Equation (18) can be rewritten as:

$$I_{REF} \approx kI_{bus} \sin \omega t$$

(19)

In order to obtain the desired reference current without sampling the load current  $I_{bus}$ , a dead-zone controller, which was proposed in [25]-[26], is used in this paper. The voltage ripple across  $C_F$  is sensed here, since the difference between the instantaneous input power and the constant output power produces a voltage ripple  $\Delta V_{CF}(t)$  at twice the line frequency. The voltage ripple can be expressed as:

$$\Delta V_{CF}(t) \approx \frac{I_{bus} \sin(4\pi f_{line}t)}{4\pi f_{line}C_F}$$

(20)

From (20), it can be seen that the load current  $I_{bus}$  is directly proportional to the ripple voltage. In the dead-zone controller, the sampled frequency of the output voltage is  $f_a$ , and  $f_a$  is significantly higher than the line frequency. The sampled voltage is then used to calculate the output voltage ripple magnitude  $\Delta V_{CF}[n]$ , which is compared with several preset digital dead-zone reference levels to give the corresponding predefined  $I_M$ .

In order to ensure that the converter operate in the PCCM, which requires  $d_c>0$ , and based on the power conservation of the converter, the following equation should be satisfied:

$$\frac{V_m}{\sqrt{2}} \frac{I_M}{\sqrt{2}} > V_{bus} I_{bus} \tag{21}$$

Thus, based on (18) and (19), the predefined  $I_M$  can be determined as:

$$I_{M} > \frac{8\pi f_{line} C_{F} V_{bus} \Delta V_{CF}}{V_{m}}$$

(22)

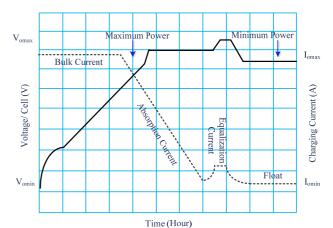

Fig. 6. Simplified adaptive four-step lead-acid battery charging profile.

According to the sensed ripple voltage, one of the predefined values of  $I_M$  will be used. If the dead-zone controller senses a higher voltage ripple, a higher level of  $I_M$  is chosen. Meanwhile, in order to minimize the power loss caused by  $Q_f$ , the controller limits the minimum turn-on time of  $Q_f$  to be less than 5% of the switching period. This is achieved by slightly adjusting  $k_1$ . Therefore,  $d_a$  is almost constant over the entire power range as the ratio  $d_a/d_b$  does not change when the output power changes. The output power is mainly regulated by modulating  $I_{REF}$ .

#### B. Design of the Input Inductor L

The inductor-current ripple of the PCCM operation is much smaller than the DCM operation and larger than the CCM operation. Thus, a medium inductor is needed in the PCCM operation. According to [22], the minimum value of the input inductor for the CCM operation and the maximum value for the DCM operation can be derived as:

$$L_{CCM} > \frac{T}{2G_0(P_{\text{o-min}})} \tag{23}$$

$$L_{DCM} < \frac{T}{2G_e(P_{o-\text{max}})} \left( 1 - \frac{V_m}{V_{CF}} \right) \tag{24}$$

where:

$$G_e = \frac{2P_o}{V_m^2} \tag{25}$$

Meanwhile, the power range of a typical four-step battery charger for a 60V system is shown in Fig. 6 [27]. The value of the input inductor L can be selected based on (23), (24), (25) and Fig. 6.

#### C. Design of the Turns Ratio n

As previously mentioned, the main feature of the proposed converter is that it has no restriction of the PFC cell duty ratio  $d_a$ . In addition,  $d_a$  is nearly constant over the entire power range. Meanwhile, based on the operation principle presented in Section II, the maximum effective duty ratio for the charging current regulation is determined by  $d_a$ . Thus, for designing the turns ratio of the transformer  $T_r$ , it is necessary

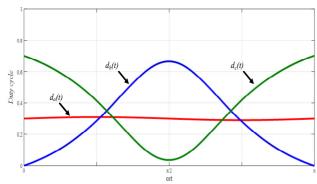

Fig. 7.  $d_a(t)$ ,  $d_b(t)$  and  $d_c(t)$  during half line cycle.

to get the operating range of  $d_a$ .

According to the instantaneous expressions of the input inductor current, the following relation can be obtained:

$$\frac{V_m \left| \sin \omega t \right|}{L} d_a T + \frac{V_m \left| \sin \omega t \right| - V_{CF}}{L} d_b T = I_{REF}(t+T) - I_{REF}(t)$$

(26)

From (19) and (26), the following equation can be deduced:

$$d_b = \frac{V_m |\sin \omega t|}{V_{CF} - V_m |\sin \omega t|} d_a - \frac{kI_{bus}L}{T} \frac{|\sin \omega (t+T)| - |\sin \omega t|}{V_{CF} - V_m |\sin \omega t|}$$

(27)

According to the analysis in Section IV-A, the duty ratio  $d_a$  is almost constant over one line cycle. In order to make the theoretical analysis more clear, the duty ratios  $d_a$ ,  $d_b$  and  $d_c$  over one line cycle can be plotted in a figure. Firstly, based on the assumption that  $d_a$  remains constant at 0.3, the duty ratios  $d_b$  and  $d_c$  can be calculated with (1) and (27). The parameters used for the calculation of  $d_b(t)$  in (27) are obtained from the prototype shown in Section V (Table I). Then, the values of  $d_a(t)$ ,  $d_b(t)$  and  $d_c(t)$  over one half line cycle are plotted in Fig. 7 using Matlab. Actually, the value 0.3 is selected because  $d_a$  is almost equals to 0.3 (0.28 in practice) in the prototype proposed in Section V. In addition, the calculated curves of  $d_b$  and  $d_c$  shown in Fig. 7 are based on the system parameters of the prototype.

In the PCCM operation, it is easy to obtain:

From (27) and (28), the constraint of  $d_a$  can be deduced as:

$$d_a < \frac{V_{CF} - V_m \left| \sin \omega t \right|}{V_{CF}} + \frac{kI_{bus}L}{T} \left( \left| \sin \omega (t+T) \right| - \left| \sin \omega t \right| \right)$$

(29)

Since the switching period T is much smaller than the line period, the following equation can be calculated:

$$|\sin \omega(t+T)| - |\sin \omega t| \approx \omega T \cos \omega t$$

(30)

Therefore, (29) can be rewritten as:

$$d_a < 1 - \frac{V_m \left| \sin \omega t \right|}{V_{CF}} + k I_{bus} L \omega \left| \cos \omega t \right| = 1 - \frac{V_m \left| \sin \omega t \right|}{V_{CF}} + \frac{k P_o L \omega}{V_{CF}} \left| \cos \omega t \right| \quad (31)$$

Since  $d_a$  is constant over half a line cycle, (31) should be satisfied over half a line cycle. According to (27), the envelope of  $d_b(t)$  shown in Fig. 7 increases with a larger  $d_a$ . Meanwhile,  $d_b$  varies during half a line cycle and reaches its maximum value at  $\omega t = \pi/2$  with a constant  $d_a$ . Thus, the available maximum value of  $d_a$  can be deduced as:

$$d_{a-\text{max}} = \left[1 - \frac{V_m |\sin \omega t|}{V_{CF}} + \frac{k P_o L \omega}{V_{CF}} |\cos \omega t|\right]_{\omega t = \frac{\pi}{2}} = 1 - \frac{V_m}{V_{CF}} \quad (32)$$

For  $V_{in}$ =220Vac, and from (32), it can be concluded that  $d_{a\text{-max}}$  is usually smaller than 0.5 because of the limitation of  $V_{CF}$ . Thus, the maximum effective duty ratio for dc/dc regulation is equal to  $d_{a\text{-max}}$  when the phase difference  $\varphi$  is zero.

Meanwhile, the output filter inductor  $L_o$  is designed to work in the CCM mode. Thus, with a constant primary dc bus voltage, the maximum value of the turns ratio n can be deduced considering the maximum effective duty ratio  $d_{a\text{-max}}$  and the maximum battery voltage  $V_{o\text{-max}}$ . The following constraint, based on the standard full-bridge operation, can be placed on n.

$$n < \frac{2d_{a-\max}V_{CF}}{V_{o-\max}} \tag{33}$$

where  $V_{omax}$  can be obtained from Fig. 6. From (32) and (33), the following relation can be obtained:

$$n < 2\frac{V_{CF} - V_m}{V_{o-\text{max}}} \tag{34}$$

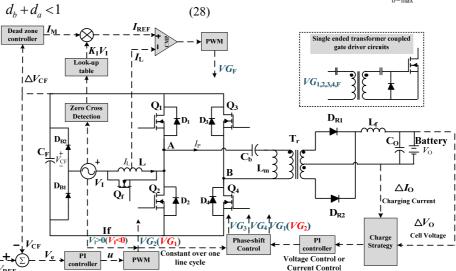

Fig. 8. Simplified schematic of the proposed converter with controllers.

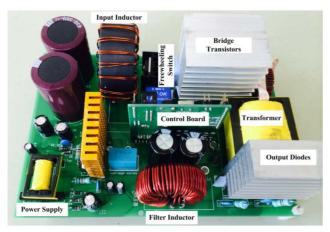

Fig. 9. Physical aspect of the developed prototype.

TABLE I

MAIN PARAMETERS OF THE PROTOTYPE

| Parameter                  | Value                    |

|----------------------------|--------------------------|

| Input Voltage              | 220Vac/50Hz              |

| Output Voltage             | 50~78Vdc                 |

| Bulk Current               | 13A                      |

| Float Current              | 5A                       |

| Maximum Output Power       | 1kW                      |

| Switching Frequency        | 50KHz                    |

| Dc-bus Voltage             | 420Vdc                   |

| Dc-bus Capacitor           | $2{\times}450V/560\mu F$ |

| Input Inductance           | 1.2mH                    |

| Turns Ratio of Transformer | 21:9                     |

| Bobbin of the Transformer  | EE42                     |

| Output Filter Inductance   | 118μΗ                    |

(b) Simulation results.

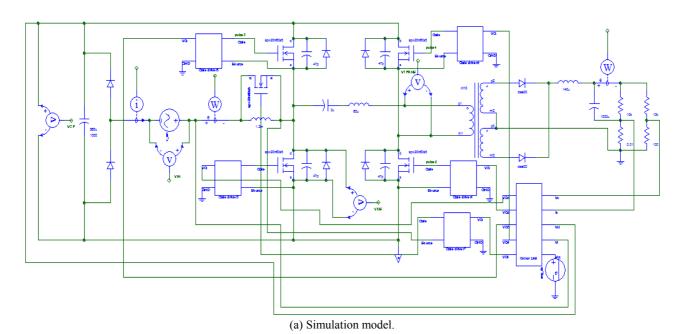

Fig. 10. Simulation model and simulation results of the proposed PCCM converter.

It is well known that a smaller turns ratio means a larger circulating loss in the primary side. Therefore, n should be chosen as large as possible after considering the duty cycle loss and the margin.

#### D. Selection of the Dc Bus Voltage VCF

According to (34), a larger dc bus voltage means a larger turns ratio and less circulating loss. However, the value of the dc bus voltage should be less than 450 V to allow the bulk capacitance at the primary-side dc bus to be implemented with standard 450 V electrolytic capacitors. Therefore, a voltage of 420V is chosen considering the voltage ripple.

#### E. Implementation of the Control Circuit

Fig. 8 shows a simplified schematic of the power converter and the controller. The single-ended transformer coupled gate driver circuit, which can provide isolation, is also presented in Fig. 8.

#### V. SIMULATION AND EXPERIMENTAL VERIFICATIONS

In order to verify the analysis above, a 1 kW voltage-fed single-stage full-bridge battery charger prototype for 60V-90Ah lead-acid batteries is built. The prototype is shown in Fig. 9. A TMS320F2812 is used to realize the controller and the charging strategy.

The main parameters of the prototype are selected based on the design considerations shown in Section IV. The detailed parameters are listed in Table I.

At first, the converter is built in Saber simulation software with the parameters in Table I. This is shown in Fig. 10(a).

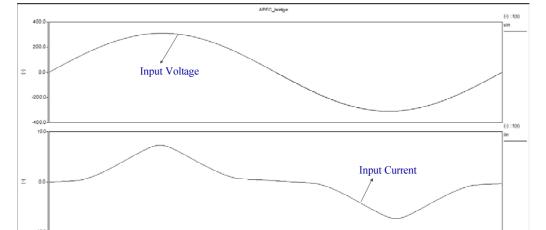

Fig. 10(b) shows the steady-state input voltage and current waveforms of the PCCM voltage-fed single-stage full-bridge converter. The function of power factor correction is well realized.

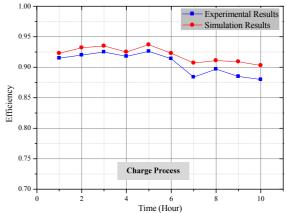

The efficiency of the proposed converter obtained from the simulations is compared to that from the experiments in Fig. 11. The efficiency results are simulated for different load conditions which can be obtained from the charging profile shown in Fig. 6.

As shown in Fig. 11, the maximum error between the simulation and experimental results is less than 2% at the minimum load, and most of the errors are less than 1%. Thus, the simulation results are consistent with the experimental results.

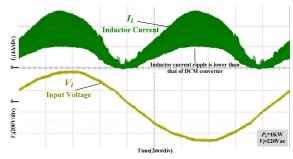

Fig. 12 shows the input voltage  $V_I$  and inductor current  $I_L$  of the proposed battery charger at the maximum load. It can be seen that the inductor current ripple of the proposed converter is lower than that of the DCM converter. Thus, compared to the DCM control, the PCCM control increases the current-handling capability at heavy loads and a larger output power can be achieved.

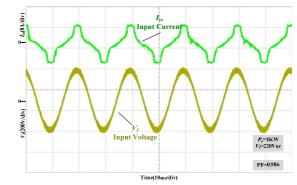

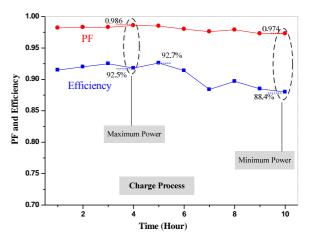

Fig. 13 shows the input voltage and the input current. The input current is slightly distorted, the PF is 0.986, and the THD is 16.1%. Meanwhile, the PF and the overall efficiency during the charging process are plotted in Fig. 14. The power

Fig. 11. Simulation results of the efficiency.

Fig. 12. Experimental waveform of input voltage  $V_I$  and input inductor current  $I_L$ .

Fig. 13. Experimental waveform of input voltage and current.

Fig. 14. PF and the overall efficiency over entire output power range.

Fig. 15. Experimental waveforms of key drive signals. (a) Drive signals waveform of  $Q_2$  and  $Q_f$ . (b) Drive signals waveform of the two legs. (c) Voltage across primary side  $V_{AB}$  and primary current  $I_P$  waveform versus gate drive signals.

factor is kept high over the wide output power range because there is no restriction of the PFC cell duty ratio.

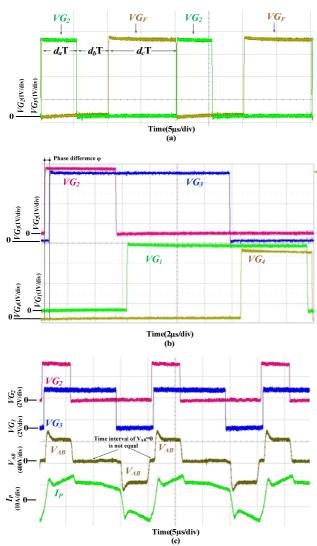

Experimental waveforms of the drive signals of  $Q_2$ ,  $Q_f$ ,  $VG_2$  and  $VG_F$ , over several switching cycles are shown in Fig. 15(a).  $Q_f$  is switched off just before  $Q_2$  is switched on. Fig. 15(b) and (c) show the phase-shifted control of the dc/dc stage. In Fig. 15(b), the driver signals of  $Q_1$ ,  $Q_2$ ,  $Q_3$  and  $Q_4$  are shown. The gating signals for  $Q_1$  and  $Q_3$  are complimentary to those for  $Q_2$  and  $Q_4$ , respectively. It can be seen that the duty ratio of  $Q_2$  is about 0.3 and that the  $Q_1$ - $Q_2$  leg is the leading leg. The driver signals of  $Q_2$  and  $Q_3$  versus the voltage across the primary side and transformer primary current are shown in Fig. 15(c). The experimental waveforms shown in Fig. 15 verify the operating waveforms in Fig. 3.

# VI. CONCLUSION

A novel PCCM voltage-fed single-stage PFC full-bridge

battery charger is proposed in this paper. It combines the attractive features of CCM and DCM converters, which includes the low current ripple through the input inductor and the constant on-time operation. With these features, a large output power can be obtained while, more importantly, the restriction of the PFC cell duty ratio, which leads to input current distortion and an uncontrollable dc bus voltage, is eliminated by the constant on-time operation. The operation principle and features of the proposed charger were explained in detail. Then the design of the new converter was discussed. At last, simulation and experimental results were presented to confirm the feasibility of the battery charger and to verify the converter performance. The PF of the proposed converter is kept higher than 0.97 over the entire power range. In addition, the dc-bus voltage is controlled at 420Vdc, and standard 450 V electrolytic capacitors can be used.

The proposed converter operates without a low-frequency output voltage ripple. Thus, it is also suitable for many other applications. In addition, the overall efficiency of the proposed converter is affected by the freewheeling power switch. If a significant increase in the efficiency is desired, the output diodes can be replaced with synchronous rectifier MOSFETs which is very difficult for other single-stage voltage-fed full-bridge converters.

#### ACKNOWLEDGMENT

This work was supported by the National Nature Science Foundation of China (51277026), Qing Lan Project and Suzhou Application Basic Research Project (SYG201450).

#### REFERENCES

- [1] A. Khaligh and Z. Li, "Battery, ultracapacitor, fuel cell, and hybrid energy storage systems for electric, hybrid electric, fuel cell, and plug-in hybrid electric vehicles: State of the art," *IEEE Trans. Veh. Technol.*, Vol. 59, No. 6, pp. 2806-2814, Jul. 2010.

- [2] F. Musavi, W. Eberle, and W. G. Dunford, "A high-performance single-phase bridgeless interleaved PFC converter for plug-in hybrid electric vehicle battery chargers," *IEEE Trans. Ind. Appl.*, Vol. 47, No. 4, pp. 1833-1843, Jul./Aug. 2011.

- [3] D. S. Gautam, F. Musavi, M. Edington, W. Eberle, and W. G. Dunford, "An automotive on-board 3.3 kW battery charger for PHEV application," *IEEE Trans. Veh. Technol.*, Vol. 61, No. 8, pp. 3466-3474, Oct. 2012.

- [4] T. H. Kim, S. J. Lee, and W. Choi, "Design and control of the phase shift full bridge converter for the on-board battery charger of electric forklifts," in *IEEE 8<sup>th</sup> International Conference on Power Electronics and ECCE Asia (ICPE & ECCE)*, pp. 2709-2716, 2011.

- [5] P. K. Jain, W. Kang, H. Soin, and Y. Xi, "Analysis and design considerations of a load and line independent zero voltage switching full bridge dc/dc converter topology," *IEEE Trans. Power Electron.*, Vol. 17, No. 5, pp. 649-657, Sep. 2002.

- [6] M. G. Egan, D. L. O'Sullivan, J. G. Hayes, M. J. Willers, and C. P. Henze, "Power-factor-corrected single-stage inductive charger for electric vehicle batteries," *IEEE Trans.*

- *Ind. Electron.*, Vol. 54, No. 2, pp. 1217-1226, Apr. 2007. S. Li, J. Deng, and C. C. Mi, "Single-stage resonant battery charger with inherent power factor correction for electric vehicles," IEEE Trans. Veh. Technol., Vol. 62, No. 9, pp. 4336-4344, Nov. 2013.

- [8] H. Wang, Q. Sun, H. S. H. Chung, and S. Tapuchi, "A ZCS current-fed full-bridge PWM converter with self-adaptable soft-switching snubber energy," IEEE Trans. Power Electron., Vol. 24, No. 8, pp. 1977-1991, Aug. 2009.

- [9] S. Jalbrzykowski and T. Citko, "Current-fed resonant full-bridge boost DC/AC/DC converter," IEEE Trans. Ind. Electron., Vol. 55, No. 3, pp. 1198-1205, Mar. 2008.

- [10] J. Burgmeier, and A. K. Rathore, "Extended range ZVS active-clamped current-fed full-bridge isolated DC/DC converter for fuel cell applications: analysis, design, and experimental results," IEEE Trans. Ind. Electron., Vol. 60, No. 7, pp. 2661-2672, Jul. 2013.

- [11] R. Y. Chen, T. J. Liang, J. F. Chen, and R. L. Lin, "Study and implementation of a current-fed full-bridge boost DC-DC converter with zero-current switching for high-voltage applications," IEEE Trans. Ind. Appl., Vol. 44, No. 4, pp. 1218-1226, Jul./Aug. 2008.

- [12] T. Meng, H. Q. Ben, C. Y. Li, and W. Guo, "Investigation and implementation of a passive snubber with a coupled-inductor in a single-stage full-bridge boost PFC converter," Journal of Power Electronics, Vol. 13, No. 2, pp. 206-213, Mar. 2013.

- [13] G. Moschopoulos, "A simple AC-DC PWM full-bridge converter with integrated power-factor correction," IEEE Trans. Ind. Electron., Vol. 50, No. 6, pp. 1290-1297, Dec.

- [14] G. Moschopoulos and J. Shah, "A Comparative study of simple Ac-Dc PWM full-bridge current-fed and voltage-fed converters," Journal of Power Electronics, Vol. 4, No. 4, pp. 246-255, Jul. 2004.

- [15] G. Moschopoulos and P. Jain, "Single-phase single-stage power-factor-corrected converter topologies," IEEE Trans. Ind. Electron., Vol. 52, No. 1, pp. 23-35, Feb. 2005.

- [16] H. S. Ribeiro and B. V. Borges, "Analysis and design of a high efficiency full-bridge single stage converter with reduced auxiliary components," *IEEE Trans. Power* Electron., Vol. 25, No. 7, pp. 1850-1862, Jul. 2010.

- [17] H. S. Ribeiro and B. V. Borges, "New optimized full-bridge single-stage AC/DC converters," *IEEE Trans. Ind. Electron.*, Vol. 58, No. 6, pp. 2397-2409, Jun. 2011.

- [18] P. Das, S. Li, and G. Moschopoulos, "An improved AC–DC single-stage full-bridge converter with reduced DC bus voltage," IEEE Trans. Ind. Electron., Vol. 56, No. 12, pp. 4882-4893, Dec. 2009.

- [19] H. S. Ribeiro and B. V. Borges, "Solving technical problems on the full-bridge single-stage PFCs," IEEE Trans. Ind. Electron., Vol. 61, No. 5, pp. 2264-2277, May 2014.

- [20] H. S. Ribeiro and B. V. Borges, "High-performance voltage-fed AC-DC full-bridge single-stage power factor correctors with a reduced DC bus capacitor," IEEE Trans. Power Electron., Vol. 29, No. 6, pp. 2680-2692, Jun. 2014.

- [21] P. Das, M. Pahlevaninezhad, and G. Moschopoulos, "Analysis and design of a new AC-DC single-stage full-bridge PWM converter with two controllers," IEEE Trans. Ind. Electron., Vol. 60, No. 11, pp. 4930-4946, Nov. 2013

- [22] K. D. Gussemé, D. V. D. Sype, A. V. D. Bossche, and J. Melkebeek, "Digitally controlled boost PFC converters operating in both continuous and discontinuous conduction mode," IEEE Trans. Ind. Electron., Vol. 52, No. 1, pp. 88-97, Feb. 2005.

- [23] L. Balogh, "Design and application guide for high speed MOSFET gate drive circuits," Power Supply Design

- Seminar SEM-1400, Topic 2, Texas Instruments Literature,

- [24] S. Ma, T. Zhao, and B. Chen, "4A isolated half-bridge gate driver with 4.5V to 18V output drive voltage," in 29<sup>th</sup> Annual IEEE Applied Power Electronics Conference and Exposition (APEC), pp. 1490-1493, 2014.

- [25] A. Prodic, D. Maksimovic, and R. W. Erickson, "Dead-zone digital controllers for improved dynamic response of low harmonic rectifiers," IEEE Trans. Power Electron., Vol. 21, No. 1, pp. 173-181, Jan. 2006.

- [26] F. Zhang and J. Xu, "A novel PCCM boost PFC converter with fast dynamic response," IEEE Trans. Ind. Electron., Vol. 58, No. 9, pp. 4207-4216, Sep. 2011.

- [27] F. Musavi, M. Craciun, D. S. Gautam, and W. Eberle, "Control strategies for wide output voltage range LLC resonant DC-DC converters in battery chargers," IEEE Trans. Veh. Technol., Vol. 63, No. 3, pp. 1117–1125, Mar. 2014.

Taizhi Zhang received his B.S. degree in Electrical Engineering from Hangzhou Dianzi University, Hangzhou, China, in 2010. He is presently working towards his Ph.D. degree at Southeast University, Nanjing, China. His current research interests include the ac-dc, dc-dc and single-stage PFC converters applied in LED drivers and battery chargers.

Zhipeng Lu received his B.S. degree in Electric Power Systems and Automation from Nanchang University, Nanchang, China, in 2014. His current research interests include the analysis and design of dc-dc converters, battery chargers and single-stage PFC converters.

Qinsong Qian received his Ph.D. degree in Electronics Engineering from Southeast University, Nanjing, China, in 2012. Since 2012, he has been with the School of Science and Engineering, Electronic Southeast University, where he is presently working as a Lecturer. His current research interests include power device design, simulations, and power converters.

Weifeng Sun received his B.S., M.S., and Ph.D. degrees in Electronic Engineering from Southeast University, Nanjing, China, in 2000, 2003, and 2007, respectively. Since 2006, he has been with the School of Electronic and Engineering, Southeast University, where he is presently working as the Dean of the School of Electronic Science

and Engineering. His current research interests include new power device designs, power ICs, power device models, and power systems.

Shengli Lu received his Ph.D. degree in Information and Physics from Nanjing University, Nanjing, China, in 1994. Since 1994, he has been with the School of Electronic Science and Engineering, Southeast University, Nanjing, China, where he is presently working as a Professor in the National ASIC System Engineering Research Center. His current research interests include

VLSIs and application specific integrated circuits.